allegro常见问题集锦1

allegro常见问题解答

allegro常见问题解答allegro常见问题解答allegro是Cadence 推出的先进 PCB 设计布线工具,下面店铺准备了关于allegro常见问题解答,欢迎大家参考!1 无论哪个版本都经常出现自动退出,提示为非法操作,然后不能存盘,自动退出。

(ALLEGRO)(出现这种情况,主要是操作系统方面的原因,ALLEGRO要求在英文NT或WINDOWS 2000下使用.在中文WINDOWS 2000下,出错概略提高许多。

事实上,设计人员应充分使用Allegro的Autosave 功能,以避免各种情况下引起的数据丢失。

提示:Allegro在异常退出时,会在当前设计目录下产生一个后缀为sav的文件。

用Allegro打开该文件,另存为brd文件即可)2在ALLEGRO中,编辑焊盘时,经常会出现“执行程序错误”而退出程序,且没有备份文件,导致之前的工作白费。

(此问题14.1已经解决,而且同样与操作系统有关)3 在从自动布线器(SPECCTRA)建军回到ALLEGRO后,输出表层的线、孔就与器件成为一个整体,移动器件时,线、孔就附在上面一起移动。

(实际上,这个功能是Cadence应大多数用户要求而添加上的,主要是为了方便移动器件的时候fanout后的引腿和via能跟着一起移动。

如果你实在不愿意这么做,可以执行下面这个Skill程序解决,以后版本将会有选项供用户选择:; The following Skill routine will remove invisible; properties from CLINES and VIAS.; The intent of this Skill program is to provide; users with the ability of deleting the invisible; properties that SPECCTRA/SPIF puts on. This will allow the moving; of symbols without the attached clines/vias once the; design is returned from SPECCTRA if the fanouts were originally; put in during an Allegro session.;; To install: Copy del_cline_prop.il to any directory defined; within your setSkillPath in your; allegro.ilinit. Add a "load("del_cline_prop.il")"; statement to your allegro.ilinit.;; To execute: Within the Allegro editor type "dprop" or; "del cline props". This routine should; only take seconds to complete.;; Deficiencies: This routine does not allow for Window or; Group selection.;; WARRANTIES: NONE. THIS PROGRAM WAS WRITTEN AS "SHAREWARE" AND IS AVAILABLE AS IS; AND MAY NOT WORK AS ADVERTISED IN ALL ENVIRONMENTS. THERE IS NO; SUPPORT FOR THIS PROGRAM.;; Delete invisible cline/via properties.;axlCmdRegister( "dprop" 'delete_cline_prop)axlCmdRegister( "del cline props" 'delete_cline_prop)(defun delete_cline_prop ();; Set the Find Filter to Select only clines(axlSetFindFilter ?enabled (list "CLINES" "VIAS")onButtons (list "CLINES" "VIAS"));; Select all clines(axlClearSelSet)(axlAddSelectAll) ;select all clines and vias(setq clineSet (axlGetSelSet))(axlDBDeleteProp clineSet "SYMBOL_ETCH") ;Remove the property(axlClearSelSet) ;unselect everything4.用贴片焊盘(type=single)做成的package,用toolspadstackmodify design padstack...编辑,发现type变成了blind/buried。

Allegro问提解答

Allegro问提解答Allegro问题集锦1、问:我在产生NC TAPE 文件时提示error,但并没有生成NCTAPE.LOG可供查找错误原茵,望高手帮助!答:NCTAPE.LOG的内容其实也就是执(de0 nei4 rong2 qi2 shi2 ye3 jiu4 shi4 zhi2)行File/Viewlog命令弹出的文本中的内容。

您可以通过这个来查看,您不能产生log文件的原茵可能是软件的关于TEXT 的路径设置有问题。

您可以去SETUP/USER PERFERENCE中的CONFIG_PATH进行查看2、问:问一个入门的问题:从Capture导入的网表是不是要在Capture里把封装定义好?OrCAD里的封装如何查看?答:一般在Capture中需要定义属性(在原理图编辑器中选择物件查看他的属性)中选择Cadence-Allegro/SPECCTRAQuest/APD,然后查看PCB Footprint属性,这个属性一般是用来和Allegro中的封装做对应的,也就是这里填入的就是Allegro封装(请注意这里的封装是指的在Layout时候用到的封装)的名称,导出网络表的时候软件会做自动的抓取到生成的网络表中,这样在Allegro中导入网络表的时候Allegro才知道是抓取哪个元件,封装有两种:一种是在原理图中用的,一种是在Layout (Allegro)时候(_shi2 hou4)用的,我不知道您是希望在ORCAD中查看哪个封装,如果(zhong cha kan na ge feng zhuang _ru guo)是后者的话在Capture中无法看到,但是如果您建立了Capture CIS的Database的话(de0 hua4)就可以看到了。

3、问:Allegro中的封装和OrCAD里的是否一致?答:对不起,我想问问您所指的ORCAD的封装是指原理图的封装还是指ORCAD LAYOUT软件的封装呢,如果您是指的(de feng zhuang ne _ru guo nin shi zhi de)原理图中的封装的话那是两个完全不同的概念,一个是用在原理图中,我们叫他元件的SYMBOL,另一个呢是在进行Layout的时候需要用到的。

Allegro使用问题汇总

allegro使用汇总2010-06-21 15:31:10| 分类: cadence |字号 订阅1.如何在allegro中取消花焊盘(十字焊盘)set up->design parameter ->shape->edit global dynamic shape parameters->Thermal relief connects ->Thru pins ,Smd pins -> full contact2.allegro 中如何设置等长setup -> constraints->electrical->net->routing->Min Max Propagation delays选择要等长的net->右击->create->pin pair->选择pin修改 prop daly 的min 和max项3.如何设置allegro的快捷键修改文件 $inst_dir\share\pcb\text\env 或 $inst_dir\pcbevn\env快捷键定义如下:alias F12 zoom outalias ~R angle 90 (旋转90 度)alias ~F mirror (激活镜相命令)alias ~Z next (执行下一步命令)alias End redisplay(刷新屏幕)alias Del Delete(激活删除命令)alias Home Zoom fit(全屏显示)alias Insert Define grid(设置栅格)alias End redisplayalias Pgdown zoom outalias Pgup zoom inalias F12 custom smoothalias Pgup slidealias Pgdown donealias Home hilightalias End dehilightalias Insert add connectalias Del Delete4.如何在allegro中删除有过孔或布线的层时不影响其他层1.输出specctra的dsn文件allegro->file->export->router->demo.dsn->run2.产生session文件specctra(pcb router)->file->write->session->demo.ses->ok3.删除某一层中的布线和过孔delete(ctrl+D)->..4.删除allegro中的板层setup->cross section->鼠标右键->delete5.导入session文件allegro->file->import->router->demo.ses->run也可先将通过该层的过孔先替换成顶层焊盘,删除该层以后再替换回来5.如何在Allegro中同时旋转多个零件1.Edit->Move 在Options中Rotation的Point选User Pick2 再右键选Term Group 按住鼠标左键不放并拉一个框选中器件 多余的可用Ctrl+鼠标左键点击去掉.3. 选好需整体旋转的器件后 右键complete.4. 提示你Pick orgion 鼠标左键选旋转中心.5 下面右键选rotate 即可旋转了.6.allegro 16.0 透明度设置display->colour/visibility->display->OpenGL->Global transparency->transparent7.allegro Drill hole size is equal or larger than smallest pad size.Pad will be drilled away.提示Drill hole size is equal or larger than smallest pad size.Pad will be drilled away.不用理睬这一提示8.ALLEGRO 如何生成钻孔文件Manufacture -> NC -> Drill Customization->auto generate symbolsManufacture -> NC -> Drill LegendManufacture -> NC ->NC parameters->enhanced excellon format->closeManufacture -> NC -> NC Drill->auto tool select->optimize drill head travel9.CAM350如何正确导入钻带文件导进去后MACRO->PLAY->选择(CAM350--SCRIPTS)PADS_DRILL->选择钻带的REP文件还没测试过,rep文件从哪儿来的呢10.allegro 如何设置route keepin,package keepin1.setup->area->route keepin,package keepin ->画框2.edit ->z-copy->options->package keepin,route keepin->offset->50->点击外框11.allegro 中如何禁止显示shape完全禁止的方法没找到setup->user preference editor->display->display_shapefill->输入一个较大的数shape在显示时就不是那么显眼了set-user preference editor-shape-no shape fill(v)12.如何在allegro设置自定义元件库路径在下面两个位置添加自定义元件的路径Setup->User Preferences Editor->Design_paths->padpathSetup->User Preferences Editor->Design_paths->psmpath1.在allegro中如何修改线宽在Allegro的Setup->constraints里的set standard values中可定义每一层走线的宽度,比如,可以定义VCC和GND的线宽为10 Mil。

Allegro光绘文件出现问题总结

光绘文件出现问题总结目录目录 (1)6.1 PCB里面有钻孔列表,但是Gerber文件中没有钻孔列表 (2)6.2 生成光绘文件时,提示错误Dynamic shapes are out of date ;please updatethem.check for out of date shapes in setup drawing option dialog (2)6.3 钻孔文件在CAM中显示尺寸不正常 (2)6.4导出的PDF中TOP和BOTTOM层有refdes (3)6.5 同样的gerber文件在CAM350中单位不一致? (3)6.6 XXX-1-2.drl文件在CAM350里面不显示 (5)6.7 生成gerber文档时出现【Database has errors:artwork generationcanceled.please run dbdoctor】错误。

(5)6.8生成gerber文件某些层没有外框,但在PDF文档里有。

(5)6.9生成gerber文件时出现警告:Photoplot outline rectangle not found ...using drawing extents (5)6.10 生成gerber文件时,很多警告:WARNING: Segment with same start and endpoints at (67.0201 174.2666) will be ignored. Increasing output accuracy may allow segment to be generated.等 (5)6.11导出gerber文件时提示警告:Photoplot outline rectangle not found …using drawing extents (5)6.12 Cadence Allegro 如何输出异型钻孔文件? (5)6.13如何在CAM350里面检查rou文件? (6)6.14 Out of shapes 错误提醒 (6)第八章其他问题 (8)8.1 cadence16.6 allegro处理铜皮软件就卡死? (8)8.2 Dynamic shapes are out of date;please update them.check for out of dateshapes in setup drawing options dialog. (8)8.3用CAM打开光绘文件时,NC(钻孔)文件的格式跟之前选定的不一样 (8)8.4嘉立创上下单解析失败 (8)第六章光绘文件出现问题总结6.1 PCB里面有钻孔列表,但是Gerber文件中没有钻孔列表原因有两个:可能是没有设置线宽Manufacure-->Artwork-->右侧的Undefined line with:设为非0(如0.1)如果照(1)中设置了线宽还是没有列表,那么manufacture”-->“artwork”,在“NC”(自己命名的钻孔文件)层右键“display for visibility”,这时你看下是否有上面的钻孔表,如果没有,就需要添加。

ALLEGRO常见问题大全

ALLEGRO常见问题大全Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

ALLEGRO 问题累积

Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

直接操作:在Add Shape 后,shape ---parameters 里,Create pin Voids 选中IN line3.倒角Manufacture------dimension/draft――Fillet 圆角Manufacture------dimension/draft――Chamfer 斜角以上操作只对LINE 画的外框有效,而对Shape 无效。

Allegro常见问题点

Q: Allegro中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

直接操作:在Add Shape 后,shape ---parameters 里,Create pin Voids 选中IN line3.倒角Manufacture------dimension/draft――Fillet圆角Manufacture------dimension/draft――Chamfer斜角以上操作只对LINE 画的外框有效,而对Shape 无效。

allegro学习问题总结日志

allegro学习问题总结⽇志Allegro 初学习问题总结1.0 基本功能及常应⽤ (2)1.1 制作⼀个板⼦,对于边框要考虑实际的应⽤,这时需要将边框做成弧形,以免伤⼿。

如图下 (2)1.2 分割覆铜图解 (3)1.3 ALLEGRO PCB制版,遇到的问题? (5)1.3.1焊盘制作 (5)1.3.2 原点定义 (6)1.4.1布局与布线以及细节问题 (7)1.5快捷键设置。

(9)1.6 z-cope 覆铜 (11)1.7 ⽹络属性的修改 (12)1.71 引脚⽹络属性的修改。

(12)1.72 shape⽹络属性的修改。

(12)1.9 DRC 处理 (13)1.91 对于out of date shape 错误如何修改 (14)1.10 BGA布线设置规则 (14)2.0 Cadence layout布局布线常见问题详解 (18)丁辉---2010.6.4--1.0 基本功能及常应⽤1.1 制作⼀个板⼦,对于边框要考虑实际的应⽤,这时需要将边框做成弧形,以免伤⼿。

如图下可以吧直⾓转换为圆弧⾓!选择后点击两边即可。

选择Fillet 之后,在画的长⽅形两边,点击下就可以形成⼀个弧形,弧形的⼤⼩在OPTION ⾥⾯设置。

1.2 分割覆铜图解1.3 ALLEGRO PCB制版,遇到的问题?1.3.1焊盘制作1.制作焊盘时要根据具体尺⼨来,在命名时要能够⼀看就知道什么样的焊盘。

2.在制作封装时候:a)如果要引⽤⾃⼰的做的焊盘,⼀定要在建package sysbol 的⾯板中设置好⾃⼰焊盘以及封装的路径,焊盘和封装各⽤⼀个⽂件夹装起来,避免混乱不清。

(这个路径⼀定要设置对,如果你做了⼀个封装,⽤了别个库的焊盘,此时也应该把另⼀个库的焊盘路径设置出来)b)封装做完后:⼀个要确定做的器件的名称,不然你在PCB调⼊⽹络表的时候就调不进去。

在这⾥⾯设置焊盘的路径,以及封装的路径。

有热风焊盘的时候,也需要添加到⾥⾯去。

ALLEGRO常见问题大全

ALLEGRO常见问题大全Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

allegro常见报错

allegro常见报错#1 Error [ALG0045] multiple pin 3's which have different nets connected for U36: SCHEMATIC1, PMSP3_1POWER (215.90, 193.04).Check for incorrect packaging of all devices in U36.#2 Error [ALG0045] multiple pin 3's which have different nets connected for U36: SCHEMATIC1, PMSP3_1POWER (368.30, 160.02).Check for incorrect packaging of all devices in U36.#3 Error [ALG0045] multiple pin 3's which have different nets connected for U36: SCHEMATIC1, PMSP3_1POWER (388.62, 187.96).Check for incorrect packaging of all devices in U36.这个问题其实有两种情况(主要说第2种):1、在同一个元件里确实有两个编号相同的PIN,除了POWER引脚外。

2、一个元件里有多个子元件,一般电源引脚我们定义为POWER 属性,还给他起一个PIN名,如:POWER 或GND。

如果你联接的时候不是联接到网络名相同的POWER 或GND,则报错:#1 Error [ALG0045] multiple pin 3's which have different nets connected for U36: SCHEMATIC1, PMSP3_1POWER (215.90, 193.04).Check for incorrect packaging of all devices in U36. 你只要改一下引脚步名,就可以解决了。

allegro出光绘文件出现的几个问题

allegro出光绘文件出现的几个问题首先出光绘前要保证没有DRC错误出Gerber时提示如下错误:一:设置好光绘文件参数后,选择check dabase before artwork 后,点击生成光绘时出现错误告警信息:database has errors:artwork generation cancled.please run dbdoctor.可行的解决方法:1.运行内部,或外部dbdoctor ,内部的在tools-database check2.TOOLS-PADSTACK-modify design padstack。

在option中的purge选ALL。

3.place-update symbols-选择器件并选择下方的update symbols padstacks选项4.tools-padstack-refresh上述4种方法过后,基本上能解决问题。

二:WARNING: Shape at (XX XX) contains void at (XX XX)which touches another shape当该层不铺这块铜时可以正常出Gerber.这个主要是敷铜的问题,同一NET的两个独立的shape 重叠就会出现该错误告警。

出 Gerber时 , Allegro不允许2个或更多 Dynamic 类型的形状彼此接触,即使他们用相同的 netname。

解决方法:对动态敷铜与静态敷铜重叠的,可视情况删除掉静态的,或者利用merge shape来将2个分立的shape合并成一块shape。

打开shape boundary 可便于操作。

三:在能成功生成gerber文件时,文件中可能存在的许多告警信息:WARNING: Segment with same start and end points at(67.0201 174.2666) will be ignored. Increasing output accuracy may allow segment to be generated.等这个主要是底片精度设置导致的问题。

利用Allegro画封装和布局时常见错误详解

利⽤Allegro画封装和布局时常见错误详解⼀:焊盘篇1. 问题⼀:⽤padstack editor制作完焊盘后,在pcb editor中找不到焊盘。

解决办法:在Pcb editor中选择set→user preference→paths→Library→分别在padpath和psmpath中加⼊焊盘的路径(选中所对应的上层⽂件夹即可)⼆:⽹表导⼊篇(Cadence中⽣成netlist失败的原因)1. 问题⼀:Unable to open c:\Cadence\PSD_14.2\tools\capture\allerro.cfg for reading.Please correct the above error(s) to proceed.错误原因:allegro.cfg⽂件找不到或allegro.cfg⽂件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的位置不⼀样,allegro.cfg⽂件找不到是理所当然的。

解决办法:点⽣成netlist,点setup,修改路径为capture\allegro.cfa所在路径,把allegro.cfg⽂件的位置选择你现在安装⽬录的⽂件位置。

(⽰例:D:\Cadence\SPB_16.5\tools\capture\allegro.cfg)2.问题⼆:#1 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)#2 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)\#3 ERROR(ORCAP-36055):Illegal character in \hi-am13-mb-v.ooo(a10)\…….错误原因:⾸先确认了是⾮法字符,ORCAD包含的⾮法字符有:”/”、”<”、”>”、”#”、”$”、”(”、”)”。

ALLEGRO常见问题大全解析

ALLEGRO常见问题大全Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

ALLEGRO问题集锦

Cadence Allegro 问题集锦2011-01-20 18:00:591、问:我在产生NC TAPE 文件时提示error,但并没有生成NCTAPE.LOG可供查找错误原因,望高手帮助!答:NCTAPE.LOG的内容其实也就是执行File/Viewlog命令弹出的文本中的内容。

您可以通过这个来查看,您不能产生log文件的原因可能是软件的关于TEXT的路径设置有问题。

您可以去SETUP/USER PERFERENCE中的CONFIG_PATH进行查看2、问:问一个入门的问题:从Capture导入的网表是不是要在Capture里把封装定义好?OrCAD里的封装如何查看?答:一般在Capture中需要定义属性(在原理图编辑器中选择物件查看他的属性)中选择Cadence-Allegro/SPECCTRAQuest/APD,然后查看PCB Footprint属性,这个属性一般是用来和Allegro中的封装做对应的,也就是这里填入的就是Allegro封装(请注意这里的封装是指的在Layout时候用到的封装)的名称,导出网络表的时候软件会做自动的抓取到生成的网络表中,这样在Allegro中导入网络表的时候Allegro才知道是抓取哪个元件,封装有两种:一种是在原理图中用的,一种是在Layout(Allegro)时候用的,我不知道您是希望在ORCAD中查看哪个封装,如果是后者的话在Capture中无法看到,但是如果您建立了Capture CIS的Database的话就可以看到了。

3、问:Allegro中的封装和OrCAD里的是否一致?答:对不起,我想问问您所指的ORCAD的封装是指原理图的封装还是指ORCAD LAYOUT 软件的封装呢,如果您是指的原理图中的封装的话那是两个完全不同的概念,一个是用在原理图中,我们叫他元件的SYMBOL,另一个呢是在进行Layout的时候需要用到的。

Capture 中要做的就是通过PCB Footprint属性进行原理图中的元件的SYMBOL和Allegro的封装进行对应,这样才能顺利的把网络表导入Allegro中。

allegro常见问题集锦1

Allegro 使用中的问题集锦(Q:question A:answer)1. Q:我的ALLEGRO 是14.0版本的,FILE——EXPORT——后面就没有看到SUB DRAWING的命令了。

如果用EDIT——COPY的话又不能把A板的线贴到B板上,我该怎幺办?A: 是不是你启动Allegro 时Cadence Product Choices 没选好,要选PCB Dedign Expert 或Allegro Expert~~~[此贴被apple在2004-06-21 2:12 PM重新编辑]2. Q: 在ALLEGRO中,找个器件好难啊,他只是点亮器件而光标不移动到器件那里。

请问各为大侠,有没办法可以象POWERPCB 那样,查找零件时光标跟着移动?A:确认将组件点亮后,将鼠标移动至右下角的小显示框中,单击左键,光标即可自动转到所点亮的组件处.3. Q: 将logic_edit_enabled打开后,只能删除单个的net, logic_edit_enabled打开".是从何处打开???A: 在14.2中的操作:Setup -> User Preferences Editor -> Misc -> logic_edit_enabled然后可以在LOGIC/NET LOGIC 下删除NET。

4. Q: 想移动组件的某一个PIN ,请问该如何做。

用move 命令,总提示Symbol or drawing must have UNFIXED_PINS property。

A: edit -> properties 选中要move Pin的组件的 symbols,增加 UNFIXED_PINS 属性即可。

5.Q: how can i get rid of the "dynamic length" dialogue box?A: Setup -> User Preferences Editor ->Etch>allegro_etch_length_on6 .Q:请问如何将以删除的PIN NUMBER及SILKSCREEN还原??A:删除此零件,再重新导入~~~或可以直接UPDATE 零件也可以7. Q:从orcad导入后,place->quickplace,但是出来的组件上面很多丝横,就和铺铜一样,怎幺回事?A:把PACKAGE GEOMETRY 的 PLACE_BOUND_TOP 勾掉即可.8. Q:请问在allegro中,怎様画一条没有绿漆的线??A:同样位置再画一根sold mask的线9. Q:如何将走线的尖角过渡改成圆弧?A:可以直接画圆弧上去,记得勾上replace etch,原来的线就没了或使用slide 命令﹐然后在右边的tab option选项中的comers改成arc,再去移动线﹐就可以改成圆弧﹗10.Q: allegro中覆铜的基本步骤是怎样的?A:edit/shape进入shape编辑模式——edit/change net(pick)点上GND net——shape/parameters 设置相关参数(看help)——void/auto进行shape处理——shape/fill退出shape编辑模式。

Allegro89个常见问题集锦

Allegro89个常见问题集锦1. 更新封装答:封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选update symbol padstacks Ignore FIXED property。

2. 如何批量放置VIA?答:比方在TOP层铺了一片铜到地,然后想规则的放置一批VIA 将表面铺铜区连接到地层,能不能自动完成啊?手动放很麻烦也不均与,影响美观Copy Find勾選Via Option填寫數量,間距。

3. Allegro中查看过孔属性及批量替换过孔方法:答:依次单击T ools--Padstack--Modify Design Padstack,然后单击选中某过孔或焊盘,再在右边的Option栏中点Edit按钮即可查看和修改。

依次单击Tools--Padstack--Replace,然后分别在Old 栏跟New栏中填入你想替换的焊盘,按Replace即可。

4. Allegro快捷键设置空格旋转器件答:funckey ' ' iangle 90 #以90度旋转选中的物体funckey ~R iangle 45 #以45度旋转选中的物体空格键90度旋转, Ctrl+R 45度旋转5. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

6. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

7. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->TemporaryHighlight里修改即可,临时修改颜色可以点Display->Assign Color 来实现。

多年碰到的Allegro问题集合

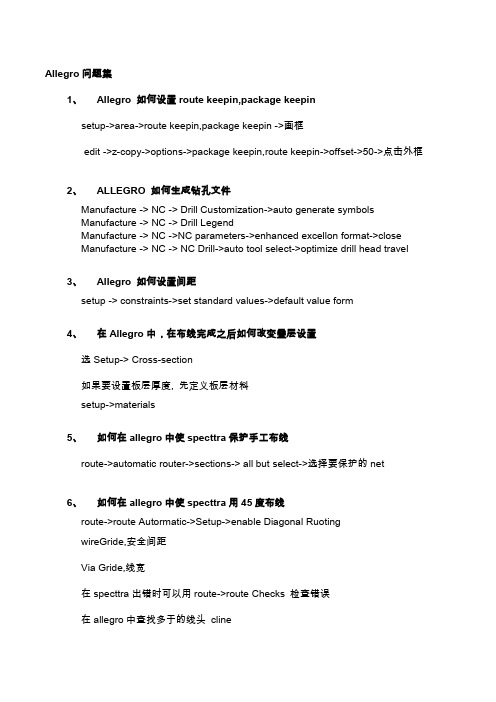

Allegro问题集1、Allegro 如何设置route keepin,package keepinsetup->area->route keepin,package keepin ->画框edit ->z-copy->options->package keepin,route keepin->offset->50->点击外框2、ALLEGRO 如何生成钻孔文件Manufacture -> NC -> Drill Customization->auto generate symbolsManufacture -> NC -> Drill LegendManufacture -> NC ->NC parameters->enhanced excellon format->closeManufacture -> NC -> NC Drill->auto tool select->optimize drill head travel3、Allegro 如何设置间距setup -> constraints->set standard values->default value form4、在Allegro中,在布线完成之后如何改变叠层设置选Setup-> Cross-section如果要设置板层厚度, 先定义板层材料setup->materials5、如何在allegro中使specttra保护手工布线route->automatic router->sections-> all but select->选择要保护的net6、如何在allegro中使specttra用45度布线route->route Autormatic->Setup->enable Diagonal RuotingwireGride,安全间距Via Gride,线宽在specttra出错时可以用route->route Checks 检查错误在allegro中查找多于的线头clineTOOLS -> REPORTS -> Dangling line Report7、Allegro 过孔定义,查找多余的cline创建过孔setup ->vias->auto define bbvia ->create bbvia->input padname->generate自动布线的过孔指定Setup-> Constraints->Physical (lines/vias) rule set->Set Values->Via list property->Name清除多余的clineRout->Gloss->Parameters或查找多余的clineTOOLS->REPORTS->Dangling line Reportcline 连接线line 边框线等8、Allegro 的gloss功能45度角转换rote -> gloss-> parameters-> line smoothing -> okgloss圆弧转换rote -> gloss-> parameters->convert corner to arc-> okgloss泪滴和T型走线rote -> gloss-> parameters->pad and T connection fillet-> okgloss局部gloss功能rote -> gloss-> windows9、在Allegro中如何修改线宽在Allegro的Setup->constraints里的set standard values中可定义每一层走线的宽度,比如,可以定义VCC和GND的线宽为10 Mil。

allegro问题积累

Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

直接操作:在 Add Shape 后,shape ---parameters 里,Create pin Voids 选中 IN line3.倒角Manufacture------dimension/draft――Fillet圆角Manufacture------dimension/draft――Chamfer斜角以上操作只对LINE 画的外框有效,而对Shape 无效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Allegro 使用中的问题集锦(Q:question A:answer)1. Q:我的ALLEGRO 是14.0版本的,FILE——EXPORT——后面就没有看到SUB DRAWING的命令了。

如果用EDIT——COPY的话又不能把A板的线贴到B板上,我该怎幺办?A: 是不是你启动Allegro 时Cadence Product Choices 没选好,要选PCB Dedign Expert 或Allegro Expert~~~[此贴被apple在2004-06-21 2:12 PM重新编辑]2. Q: 在ALLEGRO中,找个器件好难啊,他只是点亮器件而光标不移动到器件那里。

请问各为大侠,有没办法可以象POWERPCB 那样,查找零件时光标跟着移动?A:确认将组件点亮后,将鼠标移动至右下角的小显示框中,单击左键,光标即可自动转到所点亮的组件处.3. Q: 将logic_edit_enabled打开后,只能删除单个的net, logic_edit_enabled打开".是从何处打开???A: 在14.2中的操作:Setup -> User Preferences Editor -> Misc -> logic_edit_enabled然后可以在LOGIC/NET LOGIC 下删除NET。

4. Q: 想移动组件的某一个PIN ,请问该如何做。

用move 命令,总提示Symbol or drawing must have UNFIXED_PINS property。

A: edit -> properties 选中要move Pin的组件的 symbols,增加 UNFIXED_PINS 属性即可。

5.Q: how can i get rid of the "dynamic length" dialogue box?A: Setup -> User Preferences Editor ->Etch>allegro_etch_length_on6 .Q:请问如何将以删除的PIN NUMBER及SILKSCREEN还原??A:删除此零件,再重新导入~~~或可以直接UPDATE 零件也可以7. Q:从orcad导入后,place->quickplace,但是出来的组件上面很多丝横,就和铺铜一样,怎幺回事?A:把PACKAGE GEOMETRY 的 PLACE_BOUND_TOP 勾掉即可.8. Q:请问在allegro中,怎様画一条没有绿漆的线??A:同样位置再画一根sold mask的线9. Q:如何将走线的尖角过渡改成圆弧?A:可以直接画圆弧上去,记得勾上replace etch,原来的线就没了或使用slide 命令﹐然后在右边的tab option选项中的comers改成arc,再去移动线﹐就可以改成圆弧﹗10.Q: allegro中覆铜的基本步骤是怎样的?A:edit/shape进入shape编辑模式——edit/change net(pick)点上GND net——shape/parameters 设置相关参数(看help)——void/auto进行shape处理——shape/fill退出shape编辑模式。

11. Q:怎幺设置参数才能得到THERMAL REILIF 的连接呢?A:在画完铺铜范围以后,菜单会进入铺铜状态这时shape-->parameters...对于负片,在做热漂移焊盘前,必须先定义各类焊盘的FLASH SYMBOL,*.FSM文件,然后加到各类焊盘的铺铜层,再铺铜。

做出光绘文件就能看见连接了。

12.Q:请教如何修改手工铜的角度,还有就是我要在铜箔里挖一个VIA 或一个PIN 的空间,该如何做?????????A:edit-->shape,选取铜箔,点右键done,这时菜单改变了,可以用edit-->vertex 修改顶点的方式修改铜箔边框角度.而挖空间要用到void中的shpe(多边形)或circle(圆形)或Element(零件外形)要不干脆auto一下,自动会帮你挖好13 Q:Regular pad 、Anti-pad 和Thermal pad的区别A:真实焊盘大小、带隔离大小焊盘、花焊盘14.Q:怎幺做方形(或其它非圆形)负片热焊盘?A:做一个方形(或其它非圆形)的shape symbol,然后再在做pad时将shape symbol赋给flash~~15.Q: ALLEGRO中DRC标记的显示,是否可以显示为填充的,也就是像VIA那样实心的。

A:当然可以了setup-->user preferences...勾选Display中的display_drcfill.16. Q:allegro中怎幺加泪滴(teardrop)?A:要先打开所有的走线层,执行命令route->gloss->parameters.., 出现对话框,点选pad and T connection fillet,再点其左边的方格,点选circular pads,pins,vias,T connections./OK/GLOSS 即可。

加泪滴最好在出GERBER之前加。

若要MODIFY板子,则要先删掉泪滴,执行命令EDIT/DELETE,右边的FIND栏中选CLINE,下面的FIND BY NAME 中选property,点more,选FILLET=,/点APPLY/OK即可。

无论加泪滴还是删掉泪滴,一定要先打开所有的走线层,否则,没打开的走线层就不会有执行17. Q:在ALLEGRO里打开的BRD里可导出组件,但是导出的组件如何加到库里?A:File-->Export-->Libraries...再将*.txt拷到你的device库中,*.pad拷到pad库中,其它的拷到你的psm库中。

18.Q: ALLEGRO中有自动存盘系统吗??A:自动存盘需要用户自己设置,具体方法如下:(你没设置前是否有默认目录,找找看)setup>user preferences editerautosave 设定自动存盘autosave_dbcheck: 设置存盘时是否需要数据检查,如果此项设为存盘时需要数据检查则会使存盘时间加长。

autosave_time: 自动存盘时间设置。

默认值为30分钟,自动存盘时间设定范围10~100分钟。

19.Q: 请问在制作组件的时候怎幺定义组件的高度?A:当你铺好place_bound_top层shape以后,再执行Setup-->Areas-->Package Height,点击shape,此时Option面板上就可以输入高度了~~~20Q:为什幺在ALLEGRO的零件PADS显示都是PADS外框线,怎样才能显示整个PADS,请指教!A:Setup-->Drawing Options...Display: Filled pads and cline endcaps 勾选21.Q:请问各位在Padstack Designer中的Padstack Layers的FILMMASK的作用及用法??? A:好象是用于助焊的,大小跟焊盘一样大的22. Q:请问如何设置在走线时,不自动避开A:右边的OPTIONS里面的BUBBLE边上那个框里面先OFF23.Q:在两组插槽中间走了一组排线,由于在CCT中使用无网格步线,所以线与线的间距有大有小,有没有办法将一组线间距调整到等距宽度,这样比较美观。

在Allgeo或CCT中有无此调线的命令?A:In cct, you can use post-route, spread wire and center wire.In allegro, you can use roue-glosss-parameter-ceneter lines between pads.24.Q:请问如何有选择性的更改,如,我只要改一个焊盘,或者我只要改一个器件A:padstack--replace里可以改一个盘,或一个组件,或一类器件,25. Q:如何在内层看到therml孔A:正片可以直接看到呀,负片在光绘文件上就可以看到的。

在setUP\drawing options 中的display 中的thermal pads 打勾就是了26.Q:如何在rename的时候把部分器件保护起来?