DSP期末试卷A

DSP试卷A答案

试卷A一、填空题1.1、指令周期1.2、程序读总线PRDB、程序地址总线PAB、数据读总线DRDB、数据写总线DWDB、数据读地址总线DRAB、数据写地址总线DWAB1.3、外部总线PBUS接口1.4、INTR、NMI、TRAP;片内外设信号;外部中断引脚上的信号1.5、程序存储器;数据存储器1.6、程序存储空间1.7、数据存储空间1.8、40 1.9、10 1.10、999(3E7h)二、简答题2.1、连续的自动排序模式:当触发信号触发SEQ1/SEQ2一组排序器对8个(可以小于8个)的任意通道按其预置好的排序进行转换。

每一轮转换结果被保存到8个结果寄存器,SEQ1的结果寄存器为RESULT0~RESULT7,SEQ2的结果寄存器为RESULT8~RESULT15。

当最后一个通道被转换结束后,即申请中断。

倘若这时CONTRUN位仍然为“1”,则SEQ1/SEQ2重新指向要转换的第一个通道。

重新开始新一轮的转换。

在启动/停止方式下可实现在时间上单个和多个启动信号触发源同步的功能,所不同的是,在排序器完成第一个转换序列之后,在中断服务程序中不需要被复位,也就是说:排序器初始指针不需要指到CONV00就可以被重新触发。

因此一个转换序列之后,排序器指针指到当前的通道。

在这种方式下,CONTRUN位必须被设置为“0”。

2.2、指令流水线由发生在指令执行期间内的一系列总线操作序列组成。

其特点是将指令的执行过程分为4个独立的阶段,即;(1)取指令阶段(Fetch);(2)指令译码阶段(Decode);(3)取操作数阶段(Operand);(4)指令执行阶段(Execute)。

由于上述4个阶段是相互独立的,所以这些操作同一时间段内可以并行进行。

因此,在任何给定的时钟周期内,可以同时有1~4条不同的指令被使能,而每条指令处于不同的执行阶段。

三、读程题3.1对下述指令进行注释,并填出指令执行后相关各寄存器和存储单元的内容: LDP #5 ;设置DP=5(指向0280h~02FFh 区)ADD 9h ,16 ;将数据存储单元0289h 的内容左移16位后加至;累加器。

dsp原理期末考试试卷和答案

dsp原理期末考试试卷和答案**DSP原理期末考试试卷**一、单项选择题(每题2分,共20分)1. DSP芯片中,以下哪个不是其主要特点?A. 高速处理能力B. 低功耗C. 大容量存储D. 可编程性2. 在DSP系统中,以下哪个不是数据转换器的类型?A. A/D转换器B. D/A转换器C. I/O转换器D. V/F转换器3. 以下哪个不是DSP编程语言?A. C语言B. Assembly语言C. Fortran语言D. MATLAB4. DSP芯片中,哪个寄存器用于存储程序计数器?A. PCB. ARC. DRD. SR5. 在DSP中,以下哪个指令不是算术运算指令?A. ADDB. SUBC. MPYD. MOV6. DSP芯片中,以下哪个不是中断类型?A. 外部中断B. 定时器中断C. 串行通信中断D. 算术溢出中断7. 在DSP系统中,以下哪个不是模数转换器(ADC)的特性?A. 分辨率B. 采样率C. 量化误差D. 存储容量8. DSP芯片中,以下哪个不是指令周期的组成部分?A. 取指周期B. 执行周期C. 存储周期D. 写回周期9. 在DSP编程中,以下哪个不是循环控制指令?A. FORB. WHILEC. DOD. JMP10. DSP芯片中,以下哪个不是系统时钟的来源?A. 外部晶振B. 内部RC振荡器C. 外部时钟信号D. 软件生成时钟二、填空题(每题2分,共20分)1. DSP芯片的全称是__________。

2. 在DSP系统中,A/D转换器的分辨率是指能够区分的最小电压变化,通常用__________位来表示。

3. DSP编程中,汇编语言的指令通常由__________和__________两部分组成。

4. 在DSP系统中,__________是一种常用的数字信号处理算法,用于减少信号的频带宽度。

5. DSP芯片的指令集通常包括算术运算、逻辑运算、数据传输和__________等指令。

DSP原理及应用试卷_附答案卷A

课程名称(含档次)DSP原理及应用课程代号专业电子信息工程考试方式(开、闭卷)闭卷一、选择题(本题总分 24 分,每题 2 分)1、下列TI公司的DSP芯片,那种属于浮点型DSP()A、TMS320C54xB、TMS320C55xC、TMS320C62xD、TMS320C67x2、TMS320VC5402DSP有()组数据总线。

A、1B、2C、3D、43、TMS320VC5402型DSP处理器的内核供电电压()伏。

A、5VB、3.3VC、1.8VD、1.2V4、TMS320C54x系列DSP处理器有()个通用I/O引脚。

A、2B、4C、8D、165、TMS320C5402DSP直接寻址中从页指针的位置可以偏移寻址()个单元。

A、7B、8C、64D、1286、链接命令文件用()扩展名表示。

A、.objB、.cmdC、.outD、.asm7、TMS320C5402 DSP内部含有()个辅助寄存器。

A、8B、9C、5D、168、TMS320C54x DSP中,累加器的位数为: ()A、16位B、32位C、40位D、64位9、C54X DSP的流水线是由()级(也即是由多少个操作阶段)组成。

A、 4B、 6C、 8D、 1010、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的那些辅助寄存器如果使用到了是非法的()A、AR1B、AR2C、AR3D、AR411、看门狗的作用是()。

A、降低频率B、PC受到干扰而跑飞时产生复位C、既可以降低频率也可以升高频率D、稳定频率,但不改变频率12、要使DSP能够响应某个可屏蔽中断,下面的说法正确的是()A、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置0B、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置1C、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置0D、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置1二、填空题(本题总分24分,每空1分)1、C54x系列DSP处理器中,实现时钟频率倍频或分频的部件是___ _ ________。

dsp大学期末考试试题及答案

dsp大学期末考试试题及答案一、选择题(每题2分,共20分)1. DSP(数字信号处理)的全称是什么?A. Digital Signal ProcessingB. Digital Sound ProcessingC. Data Signal ProcessingD. Digital Storage Processing答案:A2. 在DSP系统中,以下哪个不是数字滤波器的类型?A. 低通滤波器B. 高通滤波器C. 带通滤波器D. 线性滤波器答案:D3. 下列哪个算法不是用于数字信号处理的?A. FFT(快速傅里叶变换)B. DCT(离散余弦变换)C. JPEG(联合图像专家组)D. MDCT(修改离散余弦变换)答案:C4. 在DSP中,以下哪个是用于实现信号采样的设备?A. ADC(模数转换器)B. DAC(数模转换器)C. CPLD(复杂可编程逻辑器件)D. FPGA(现场可编程门阵列)答案:A5. 下列哪个参数不是描述数字信号的?A. 幅度B. 频率C. 相位D. 电阻答案:D6. 在DSP中,以下哪个指标用于衡量信号的频域特性?A. 幅度谱B. 相位谱C. 功率谱D. 所有选项答案:D7. 下列哪个选项不是DSP系统设计的关键考虑因素?A. 处理速度B. 内存容量C. 电源电压D. 信号带宽答案:C8. 在DSP编程中,以下哪个不是常用的编程语言?A. C语言B. C++语言C. MATLABD. VHDL答案:C9. 下列哪个不是DSP系统的应用领域?A. 音频处理B. 图像处理C. 无线通信D. 机械制造答案:D10. 在DSP系统中,以下哪个是用于实现信号放大的组件?A. 运算放大器B. 滤波器C. 调制器D. 编码器答案:A二、填空题(每题2分,共20分)1. DSP技术在______和______处理中具有广泛应用。

答案:数字信号;模拟信号2. 一个典型的DSP系统包括______、______和______。

dsp期末考试试卷

dsp期末考试试卷一、选择题(每题2分,共20分)1. 在数字信号处理中,离散傅里叶变换(DFT)的主要应用是什么?A. 信号的频谱分析B. 信号的时域分析C. 信号的压缩D. 信号的滤波2. 下列哪个算法不是用于数字滤波器设计?A. 窗函数法B. 巴特沃斯法C. 切比雪夫法D. 快速傅里叶变换法3. 在数字信号处理中,卷积运算通常用于实现哪种类型的滤波器?A. 线性时不变(LTI)滤波器B. 线性时变(LTV)滤波器C. 非线性时不变(NTI)滤波器D. 非线性时变(NTV)滤波器4. 采样定理指出,为了避免混叠现象,采样频率至少应为信号最高频率的多少倍?A. 1倍B. 2倍C. 3倍D. 4倍5. 在数字信号处理中,Z变换通常用于分析哪种类型的系统?A. 连续时间系统B. 离散时间系统C. 线性时不变系统D. 线性时变系统6. 下列哪个选项不是数字信号处理中的调制技术?A. 幅度调制(AM)B. 频率调制(FM)C. 相位调制(PM)D. 时间调制(TM)7. 在数字信号处理中,滤波器的频率响应通常用哪种图表示?A. 幅频图B. 相频图C. 群延时图D. 所有选项8. 离散余弦变换(DCT)通常用于哪种类型的信号处理?A. 语音信号B. 图像信号C. 音频信号D. 视频信号9. 在数字信号处理中,希尔伯特变换用于实现什么功能?A. 信号的滤波B. 信号的调制C. 信号的解调D. 信号的包络检测10. 下列哪个算法不是用于谱估计?A. 周期图法B. 协方差法C. 音乐法D. 快速傅里叶变换法二、填空题(每题2分,共20分)11. 数字信号处理中的奈奎斯特频率是信号最高频率的________倍。

12. 离散时间信号的傅里叶变换(DTFT)是连续的,而离散傅里叶变换(DFT)是________的。

13. 在数字信号处理中,窗函数用于________频谱泄漏。

14. 巴特沃斯滤波器的设计基于________多项式。

dsp技术及应用期末考试题及答案

dsp技术及应用期末考试题及答案一、选择题(每题2分,共20分)1. 数字信号处理(DSP)技术主要应用于以下哪个领域?A. 计算机编程B. 通信系统C. 机械制造D. 农业科学答案:B2. 下列哪个不是数字信号处理的基本步骤?A. 采样B. 量化C. 编码D. 滤波答案:C3. 在数字滤波器设计中,低通滤波器的截止频率通常定义为:A. 滤波器的中心频率B. 滤波器的带宽C. 滤波器的半功率点D. 滤波器的增益答案:C4. 数字信号处理中,傅里叶变换的主要作用是将信号从哪个域转换到哪个域?A. 时域到频域B. 频域到时域C. 空间域到时间域D. 时间域到空间域答案:A5. 下列哪个算法不是用于数字信号处理中的快速傅里叶变换(FFT)?A. Cooley-Tukey算法B. Rader算法C. 快速卷积算法D. 快速排序算法答案:D二、填空题(每空2分,共20分)6. 数字信号处理中,_______ 是指信号在时间上是离散的。

答案:采样7. 在数字信号处理中,_______ 是指信号在幅度上是离散的。

答案:量化8. 一个数字滤波器的阶数是指滤波器中延迟元素的_______。

答案:数量9. 数字信号处理中的窗函数用于_______ 信号,以减少频谱泄露。

答案:截断10. 快速傅里叶变换(FFT)是一种高效的算法,用于计算_______。

答案:离散傅里叶变换(DFT)三、简答题(每题10分,共30分)11. 简述数字信号处理中采样定理的重要性及其内容。

答案:采样定理是数字信号处理中的基本理论,它规定了在不失真地恢复模拟信号的条件下,采样频率应大于信号最高频率的两倍。

这一定理对于信号的数字化和信号的重建至关重要。

12. 解释什么是数字滤波器,并简述其分类。

答案:数字滤波器是一种对数字信号进行滤波处理的系统,它可以通过软件实现,也可以通过硬件实现。

数字滤波器主要分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器,它们分别用于通过或阻止信号的特定频率成分。

dsp期末考试试题及答案

dsp期末考试试题及答案# dsp期末考试试题及答案一、选择题(每题2分,共20分)1. 数字信号处理中的“数字”指的是什么?A. 信号的数字化表示B. 信号的模拟表示C. 信号的频率特性D. 信号的幅度特性答案:A2. FFT算法的主要优点是什么?A. 计算速度快B. 易于编程实现C. 适用于所有类型的信号D. 可以用于实时信号处理答案:A3. 下列哪个不是数字滤波器的设计方法?A. 窗函数法B. 巴特沃斯法C. 卡尔曼滤波D. 切比雪夫法答案:C4. 离散时间信号的傅里叶变换(DTFT)是连续的还是离散的?A. 连续的B. 离散的C. 既连续又离散D. 都不是答案:A5. 采样定理指出,采样频率至少应该是信号最高频率的多少倍?A. 1倍B. 2倍C. 3倍D. 4倍答案:B...(此处省略其他选择题,共10题)二、简答题(每题10分,共20分)1. 解释什么是离散傅里叶变换(DFT)以及它与连续傅里叶变换(FT)的区别。

答案:离散傅里叶变换(DFT)是一种将离散时间信号转换为频域表示的方法。

它是一种离散的变换,意味着输入和输出都是离散的。

DFT通常用于数字信号处理中,可以计算出信号在各个频率上的幅度和相位。

与DFT不同,连续傅里叶变换(FT)是将连续时间信号转换为连续的频域表示,它适用于模拟信号处理。

2. 简述数字滤波器的基本概念及其分类。

答案:数字滤波器是一种对数字信号进行处理的系统,它允许某些频率的信号通过,同时抑制或减少其他频率的信号。

数字滤波器可以根据它们的频率响应特性进行分类,主要分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

每种类型的滤波器都设计用于处理特定频率范围内的信号。

三、计算题(每题15分,共30分)1. 给定一个离散时间信号 x[n] = {1, 2, 3, 4},计算其DFT X[k]。

答案:X[k] = DFT{x[n]} = Σ_{n=0}^{N-1} x[n] * e^(-j * 2π * k * n / N)其中,N=4,计算得到 X[k] 的值。

《DSP原理与应用》期末考试试题

《DSP原理与应用》期末考试试题一、选择题(每题2分,共20分)1、在数字信号处理中,常用的滤波器是()。

A.巴特沃斯滤波器B.贝塞尔滤波器C.拉普拉斯滤波器D.理想滤波器2、在进行傅里叶变换时,如果采样频率为fs,则采样点数为N的信号的离散傅里叶变换的结果中,频域的分辨率是()。

A. fs/NB. 2fs/NC. fs/(2N)D. fs/(2N+1)3、在进行Z变换时,如果时间序列的采样点数为N,则Z变换的收敛域是()。

A. |z|<NB. |z|<N+1C. |z|<N-1D. |z|<N-24、在进行小波变换时,如果小波基为ψ(t),则小波变换的结果是一个()。

A.实数序列B.复数序列C.实数矩阵D.复数矩阵5、在进行离散傅里叶变换时,如果信号的采样点数为N,则其频率分辨率是()。

A. 2π/NB. π/NC. π/(2N)D. π/(N+1)二、填空题(每题3分,共30分)1、在数字信号处理中,常用的滤波器有________、________、________、________。

2、在进行傅里叶变换时,如果采样频率为fs,则采样点数为N的信号的离散傅里叶变换的结果中,频域的分辨率是________。

3、在进行Z变换时,如果时间序列的采样点数为N,则Z变换的收敛域是|z|<________。

4、在进行小波变换时,如果小波基为ψ(t),则小波变换的结果是一个________。

5、在进行离散傅里叶变换时,如果信号的采样点数为N,则其频率分辨率是________。

6、在数字信号处理中,常用的窗函数有________、________、________、________。

7、在进行数字滤波器的设计时,常用的方法有________、________、________。

8、在进行数字信号的分析时,常用的工具包括________、________、________。

《美学原理》期末考试试题及答案一、单项选择题1、下列哪个选项不属于美学的研究范畴?A.绘画、音乐、诗歌等艺术形式的美学原理B.建筑、设计、自然等现实生活中的美学应用C.精神分析学、现象学等其他学科的美学分支D.美食、时尚、旅游等消费领域的美学实践正确答案:C.精神分析学、现象学等其他学科的美学分支。

DSP期末考试题大全(整合版 全3套)

DSP期末考试题(一)一、单项选择题:(每小题2分,共30分)1、下面对一些常用的伪指令说法正确的是:( D )A、.def所定义的符号,是在当前模块中使用,在别的模块中定义的符号;B、.ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

2、要使DSP能够响应某个可屏蔽中断,下面的说法正确的是( B)A、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置0B、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置1C、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置0D、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置13、对于TMS320C54x系列DSP芯片,下列说法正确的是………… ( C )A、 8位DSPB、32位DSPC、定点型DSPD、浮点型DSP4、若链接器命令文件的MEMORY部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DATA: origin=80h, length=200h}则下面说法不正确的是()A、程序存储器配置为4K字大小B、程序存储器配置为8K字大小C、数据存储器配置为512字大小D、数据存储器取名为DATA5、在串行口工作于移位寄存器方式时,其接收由()来启动。

A、RENB、RIC、REN和RID、TR6、执行指令PSHM AR5之前SP=03FEH,则指令执行后SP=( A )A、03FDHB、03FFHC、03FCHD、0400H7、TMS320C54X DSP采用改进的哈佛结构,围绕____A__组_______位总线建立。

A、8,16B、16,8C、8,8D、16,168、TMS320C54X DSP汇编指令的操作数域中, A 前缀表示的操作数为间接寻址的地址。

云南民族大学期末DSP技术A答案

3)程序执行至“MAC *AR3+, *AR4+, A”后AR3,AR4和A中的内容分别是什么?

答:分别为#a+3,#x+3和#40。——2分

4)在以上程序中,一共建立了多少个段?分别是哪些段?在以上.data段内有几个数据,.bss在存储器中保留了几个存储单元?

答:共建立了4个段,

RAM:通常放数据,对应于数据存储器——1分

ROM:通常放程序,对应于程序存储器——1分

区别:

RAM:读写速度快,掉电数据丢失——1分

ROM:读写速度慢,掉电数据不丢失——1分

2.以下指令分别是什么寻址方式?(5分)

1)LD #0F0H,A

立即数寻址——1分

2)LD0F0H,A

绝对地址寻址——1分

3)MVKD DATA1,*AR2其中,DATA1是dmad值

.sect已初始化段

3)——1分

未初始化段:在目标存储器中保留空间,以供程序运行过程中的变量作为临时存储空间使用。

已初始化段:段中的内容都在目标文件中,当加载出西施就放到目标存储器中。

4)——1分

命名段:

.usect

.sect

二、填空题 (每空2分,共32分)

1.阅读以下指令,完成注释中的填空:

LD TEMP1,A;执行完该指令后A=TEMP1

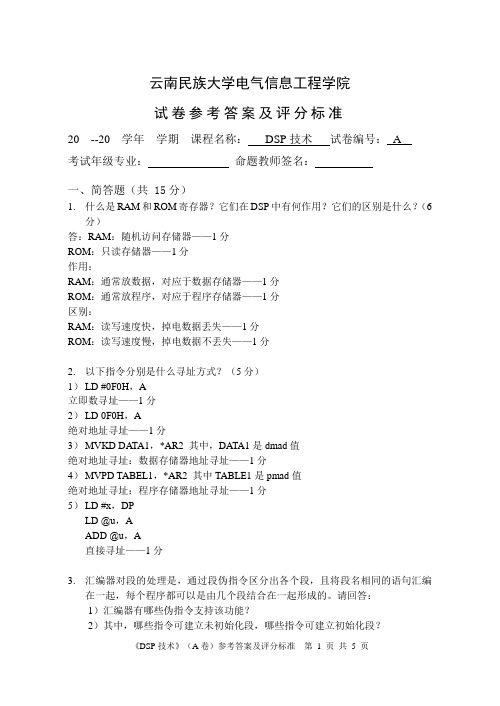

云南民族大学电气信息工程学院

试卷参考答案及评分标准

20--20学年学期课程名称:DSP技术试卷编号:A

考试年级专业:命题教师签名:

一、简答题(共15分)

1.什么是RAM和ROM寄存器?它们在DSP中有何作用?它们的区别是什么?(6分)

答:RAM:随机访问存储器——1分

电子科技大学 DSP期末考试试卷

学院 姓名 学号 任课老师 选课号……………密……………封……………线……………以……………内……………答……………题……………无……………效…………电子科技大学二零零七至二零零 八学年第 1 学期期 期末 考试《数字信号处理》 课程考试题 A 卷 ( 120 分钟) 考试形式: 开卷 考试日期 2008年1月 24 日课程成绩构成:平时 20分, 期中 20分, 实验 20 分, 期末 40分 Test of Digital Signal Processing(Give the answer of the following problems in English as possible as you can )Note: Problem 1 to 5 must be answered. You can choose to solute either one or both of problem6 and 7, if both, the higher score will be accounted .1. Which one of the following comments is not correct ? ( )(a) The DFT can be thought of the sampled version of the DTFT . (b) The FFT is the efficient computation algorithm for the DFT .(c) A linear-phase digital filter can be realized by either FIR or IIR systems .(d) If H(z) is the transfer function of an LPF filter , then H(-z) can be thought of an HPF filter in general .2. Two systems have impulse responses as follows :]1[][][1−+=n n n h δδ ,]1[][][2−−=n n n h δδ, respectively. (1)Determine the DTFTs of h1[n] and h2[n].(2)Determine and sketch their magnitude responses . (3)Which type of linear-phase system are they belong to?(4)If input x[n] = 2cos(πn) ,determine the output sequences of these two systems respectively.3. Consider the system transfer function:23()3148z H z z z +=−+(1) Sketch the pole-zero plot of H(z);(2) Discuss the type of inverse Z-transform (left-sided, right-sided, and two-sided sequences) associated with each of all possible ROCs of H(z). (3) Determine the expression of causal impulse response h[n].4. Figure 4(a ) is identical to Figure 4.2 of our textbook, which illustrates the discrete-time processing of a continuous-time signal. The ideal sampler and ideal interpolator work at the same sampling frequency T F . Assume the discrete-time processing block represents an idealbandpass digital filter with frequency response)(ωj e H illustrated in Figure 4(b ).Let )1502cos(5.1)1252sin()1002cos()(t t t t x a ×+×+×=πππ. (1) If Hz F T 100=, determine []x n , []y n and ()a y t . (2) If Hz F T150=, determine []x n , []y n and ()a y t .Figure 4(a))Figure 4(b)ω544−5−5. Let X[k] be an 8-point DFT of a length-8 real sequence x[n]. The 5 samples of X[k] are given by X[0]=0, X[1]=0, X[2]=4, X[3]=0, X[4]=0.(1) Determine and sketch X[k].(2) Determine the value of ∑=702][n n x .(3) If ]2[][8>+<=k X k G , sketch G[k] and determine the expression of g[n]which is the 8-point IDFT of G[k].ing windowed Fourier series method, design a causal bandpass FIR digital filter withfollowing specifications:center frequency 5kHzpass band edges 3.5 kHz and 6.5 kHzstop band edges 1.5 kHz and 8.5 kHzstop band attenuation 50 dB,passband ripple can be ignored.Sampling frequency F T=20kHz.Please determine the expression of the impulse response of the FIR digital filter designed.7. The normalized transfer function of order-2 lowpass Butterworth analog filter is as follows: 121)(2++=s s s H an .By means of bilinear transform, design an order-2 low-pass IIR digital filter with -3dB cutoff frequency at 1000Hz and sampling frequency at 4000Hz. You are expected to determine the expression of transfer function in closed form and sketch an implement block-diagram in any cannonic form.。

dsp期末考试试题及其答案

dsp期末考试试题及其答案### DSP期末考试试题及其答案#### 一、选择题(每题2分,共20分)1. 在数字信号处理中,DFT(离散傅里叶变换)的主要作用是什么?A. 信号调制B. 信号解调C. 信号滤波D. 频域分析2. 下列哪个不是FIR(有限脉冲响应)滤波器的特点?A. 线性相位B. 无限脉冲响应C. 易于设计D. 稳定的频率响应3. 以下哪个算法是用于快速傅里叶变换的?A. 快速卷积算法B. 快速傅里叶变换(FFT)C. 快速沃尔什变换D. 快速余弦变换4. 在数字滤波器设计中,哪种类型的滤波器可以保证无振铃效应?A. 巴特沃斯滤波器B. 切比雪夫滤波器C. 汉明滤波器D. 理想滤波器5. 下列哪个是数字信号处理中的基本概念?A. 采样B. 量化C. 编码D. 所有选项都是#### 二、简答题(每题10分,共30分)1. 解释什么是窗函数,它在信号处理中的作用是什么?2. 描述IIR(无限脉冲响应)滤波器和FIR滤波器的主要区别。

3. 什么是混叠现象?如何避免它?#### 三、计算题(每题25分,共50分)1. 给定一个离散时间信号 \( x[n] = \{2, 4, 6, 8\} \),请计算其DFT,并说明其频域特性。

2. 设计一个FIR滤波器,其脉冲响应为 \( h[n] = \{1, 2, 3, 4\} \),计算其频率响应,并讨论其滤波特性。

#### 四、分析题(共30分)1. 描述数字信号处理中的去噪技术,并举例说明其在实际应用中的重要性。

#### 参考答案#### 一、选择题1. D2. B3. B4. D5. D#### 二、简答题1. 窗函数是一种在频域中对信号进行加权的技术,它的作用是减少信号的频谱泄漏,提高频谱分析的分辨率。

2. IIR滤波器具有反馈路径,其脉冲响应是无限的,而FIR滤波器没有反馈路径,其脉冲响应是有限的。

3. 混叠现象发生在信号采样频率低于奈奎斯特频率时,可以通过增加采样频率或使用抗混叠滤波器来避免。

dsp期末考试试题开卷

dsp期末考试试题开卷### DSP期末考试试题#### 一、选择题(每题2分,共20分)1. 在数字信号处理中,DFT(离散傅里叶变换)的主要作用是什么?A. 频域分析B. 信号滤波C. 信号放大D. 信号调制2. 下列哪个不是数字滤波器的设计方法?A. 脉冲响应不变法B. 双线性变换法C. 窗函数法D. 傅里叶变换法3. 以下哪个是线性时不变系统的属性?A. 时间可变B. 线性C. 非线性D. 时变4. 采样定理指出,如果信号的最高频率为f_max,那么采样频率至少应为:A. f_maxB. 2f_maxC. 3f_maxD. 4f_max5. FFT(快速傅里叶变换)的主要优点是什么?A. 计算精度高B. 计算速度快C. 易于实现D. 适用于所有信号...(此处省略其他选择题)#### 二、简答题(每题10分,共20分)1. 简述数字滤波器和模拟滤波器的区别,并举例说明数字滤波器的应用场景。

2. 解释什么是过采样和欠采样,并讨论它们在信号处理中的影响。

#### 三、计算题(每题15分,共30分)1. 给定一个离散时间信号 x[n] = {1, 2, 3, 4, 5},请计算其DFTX[k],并画出幅度谱和相位谱。

2. 假设有一个低通滤波器,其理想频率响应为H(ω) = 1 (0 ≤ ω≤ π/3),H(ω) = 0 (π/3 < ω ≤ π)。

请设计一个简单的数字低通滤波器,并给出其脉冲响应 h[n]。

#### 四、分析题(每题15分,共30分)1. 讨论在数字信号处理中,时域分析和频域分析各自的优势和局限性。

2. 描述一个实际的信号处理问题,说明如何使用数字滤波器来解决该问题,并解释所选滤波器类型的理由。

#### 五、综合应用题(共30分)1. 设计一个数字滤波器,用于去除音频信号中的噪声。

请说明所选滤波器的类型,设计过程,以及预期的滤波效果。

2. 给定一段音频信号,使用FFT分析其频谱特性,并讨论如何通过数字滤波器改善其音质。

dsp期末复习题

dsp期末复习题DSP期末复习题一、选择题1. 数字信号处理(DSP)的核心是:A. 模拟信号处理B. 模拟到数字的转换C. 数字到模拟的转换D. 数字信号的数学处理2. 下列哪个不是DSP系统的基本组成部分?A. A/D转换器B. DSP处理器C. D/A转换器D. 电源3. 在DSP中,FIR滤波器和IIR滤波器的主要区别在于:A. 滤波器的阶数B. 滤波器的类型C. 滤波器的系数D. 滤波器的反馈结构4. 下面哪个算法不是用于数字滤波器设计的?A. 窗函数法B. 频率采样法C. 快速傅里叶变换(FFT)D. 帕克-维纳(Parks-McClellan)算法5. FFT算法的主要优点是:A. 计算复杂度低B. 实现简单C. 适用于所有类型的信号D. 可以实时处理信号二、简答题1. 解释数字信号处理中的“过采样”和“欠采样”概念,并简述它们在实际应用中的意义。

2. 描述FIR滤波器和IIR滤波器的设计方法及其主要区别。

3. 简述快速傅里叶变换(FFT)的基本原理,并说明它在数字信号处理中的重要性。

4. 阐述数字信号处理在现代通信系统中的应用。

三、计算题1. 给定一个信号x[n] = {1, 2, 3, 4, 5, 6},求其DFT X[k]。

2. 设计一个FIR滤波器,其脉冲响应满足h[n] = {1, 0.5, 0.25},求其频率响应H(ω)。

3. 利用帕克-维纳算法设计一个带通滤波器,其通带频率为[0.2π, 0.4π],阻带频率为[0.1π, 0.15π]和[0.45π,0.5π],要求最小阶数。

四、论述题1. 论述数字信号处理在音频处理领域的应用,并举例说明。

2. 讨论数字信号处理技术在图像处理中的应用,以及它如何改善图像质量。

五、综合应用题1. 假设你正在开发一个实时音频处理系统,描述你将如何使用DSP技术来实现噪声抑制和回声消除。

2. 设计一个用于视频压缩的DSP算法,简述其基本原理,并讨论可能遇到的挑战。

(完整word版)DSP试题及答案1

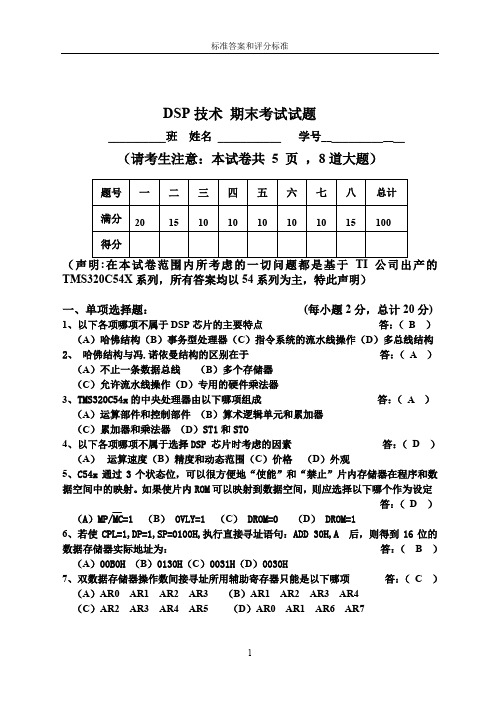

DSP技术期末考试试题__________班姓名___________ 学号_______________(请考生注意:本试卷共 5 页,8道大题)TMS320C54X系列,所有答案均以54系列为主,特此声明)一、单项选择题:(每小题2分,总计20分)1、以下各项哪项不属于DSP芯片的主要特点答:(B )(A)哈佛结构(B)事务型处理器(C)指令系统的流水线操作(D)多总线结构2、哈佛结构与冯.诺依曼结构的区别在于答:(A )(A)不止一条数据总线(B)多个存储器(C)允许流水线操作(D)专用的硬件乘法器3、TMS320C54x的中央处理器由以下哪项组成答:(A )(A)运算部件和控制部件(B)算术逻辑单元和累加器(C)累加器和乘法器(D)ST1和STO4、以下各项哪项不属于选择DSP 芯片时考虑的因素答:(D )(A)运算速度(B)精度和动态范围(C)价格(D)外观5、C54x通过3个状态位,可以很方便地“使能”和“禁止”片内存储器在程序和数据空间中的映射。

如果使片内ROM可以映射到数据空间,则应选择以下哪个作为设定答:(D )(A)MP/MC=1 (B) OVLY=1 (C) DROM=0 (D) DROM=16、若使CPL=1,DP=1,SP=0100H,执行直接寻址语句:ADD 30H,A 后,则得到16位的数据存储器实际地址为:答:( B )(A)00B0H(B)0130H(C)0031H(D)0030H7、双数据存储器操作数间接寻址所用辅助寄存器只能是以下哪项答:(C )(A)AR0 AR1 AR2 AR3 (B)AR1 AR2 AR3 AR4(C)AR2 AR3 AR4 AR5 (D)AR0 AR1 AR6 AR78、以下段定义伪指令中哪个属于未初始化段:答:(C )(A).text (B).data(C).usect(D).sect9、DSP中C语言设计具有兼容性和可移植的优点, C代码的程序入口地址符号为答:(A )(A)_c_int00 (B)start(C)reset (D)_c_int10、在CCS中编译C程序时,必须将运行时间支持库文件添加到工程中,该文件名为:答:(B )(A)rts.src (B)rts.lib(C)rtdx.lib (D)rtdx.h二、填空题:(总计15分) 1.DSP应用系统的设计流程包括4个步骤:算法模拟阶段、____器件选型_______、_____ 软硬件设计____、____调试________.2.TI的三大主力DSP产品系列为: TMS320C2000 、 TMS320C5000 、 TMS320C6000。

(完整word版)【上海师范大学】DSP技术基础期末试卷A(答案)

上海师范大学标准试卷2009 ~2010学年第一学期考试日期2009 年11月20日科目:DSP技术基础(A卷)专业本、专科年级班姓名学号我承诺,遵守《上海师范大学考场规则》,诚信考试。

签名:________________一、填空题(20分)1.典型的实时数字信号处理系统的基本部件包括:抗混叠滤波器、模数转换器、DSP(数字信号处理器)、数模转换器和抗镜像滤波器。

2.存储器结构分为两大类:冯诺依曼结构和哈佛结构。

冯•诺依曼结构的特点是只有一个存储器空间、一套地址总线和一套数据总线;哈佛结构的程序存储器空间和数据存储器空间分开,具有多套地址、数据总线,哈佛结构是并行体系结构,程序和数据存于不同的存储器空间,每个存储器空间独立编址、独立访问。

3.TMS320C55x 的寻址空间为16MB,当CPU从程序空间读取程序代码时,使用24位地址,当访问数据空间时,使用23位的地址。

4.C55x DSP支持三种寻址模式,绝对寻址模式、直接寻址模式和间接寻址模式.5.EHPI的连接方式有两种:非复用方式和复用方式。

6.McBSP属于多通道串口,每个McBSP最多可有128个通道。

每个寄存器控制16个通道,因此128个通道共有8个通道使能寄存器。

7.McBSP的寄存器主要包括三部分:收发通道寄存器、时钟和帧同步寄存器、多通道选择寄存器。

二、简答题(15分)1.简述数字信号处理器的主要特点.答:(1)存储器采用哈佛或者改进的哈佛结构;(2)内部采用了多级流水;(3)具有硬件乘法累加单元;(4)可以实现零开销循环;(5)采用了特殊的寻址方式;(6)高效的特殊指令;(7)具有丰富的片内外设。

2.TMS320C55x DSP 的流水线操作包括多少个阶段?每一阶段完成什么操作?答:两个。

第一阶段是取流水线,即从内存中取出32位的指令包,放入指令缓冲队(IBQ)中,然后为流水线的第二阶段提供48位的指令包。

第二阶段是指执行流水线,这部分的功能是对指令进行解码,完成数据的存取和计算。

DSP期末试卷答案A

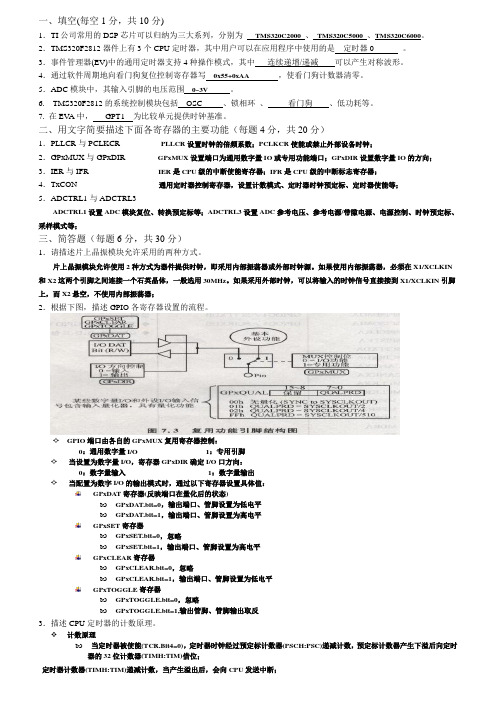

一、填空(每空1分,共10分)1.TI公司常用的DSP芯片可以归纳为三大系列,分别为TMS320C2000、TMS320C5000、TMS320C6000。

2.TMS320F2812器件上有3个CPU定时器,其中用户可以在应用程序中使用的是定时器0 。

3.事件管理器(EV)中的通用定时器支持4种操作模式,其中连续递增/递减可以产生对称波形。

4.通过软件周期地向看门狗复位控制寄存器写0x55+0xAA ,使看门狗计数器清零。

5.ADC模块中,其输入引脚的电压范围0~3V 。

6. TMS320F2812的系统控制模块包括OSC 、锁相环、看门狗、低功耗等。

7. 在EV A中,GPT1 为比较单元提供时钟基准。

二、用文字简要描述下面各寄存器的主要功能(每题4分,共20分)1.PLLCR与PCLKCR PLLCR设置时钟的倍频系数;PCLKCR使能或禁止外部设备时钟;2.GPxMUX与GPxDIR GPxMUX设置端口为通用数字量IO或专用功能端口;GPxDIR设置数字量IO的方向;3.IER与IFR IER是CPU级的中断使能寄存器;IFR是CPU级的中断标志寄存器;4.TxCON 通用定时器控制寄存器,设置计数模式、定时器时钟预定标、定时器使能等;5.ADCTRL1与ADCTRL3ADCTRL1设置ADC模块复位、转换预定标等;ADCTRL3设置ADC参考电压、参考电源/带隙电源、电源控制、时钟预定标、采样模式等;三、简答题(每题6分,共30分)1.请描述片上晶振模块允许采用的两种方式。

片上晶振模块允许使用2种方式为器件提供时钟,即采用内部振荡器或外部时钟源。

如果使用内部振荡器,必须在X1/XCLKIN和X2这两个引脚之间连接一个石英晶体,一般选用30MHz。

如果采用外部时钟,可以将输入的时钟信号直接接到X1/XCLKIN引脚上,而X2悬空,不使用内部振荡器;2.根据下图,描述GPIO各寄存器设置的流程。

DSP期末试卷(含答案)

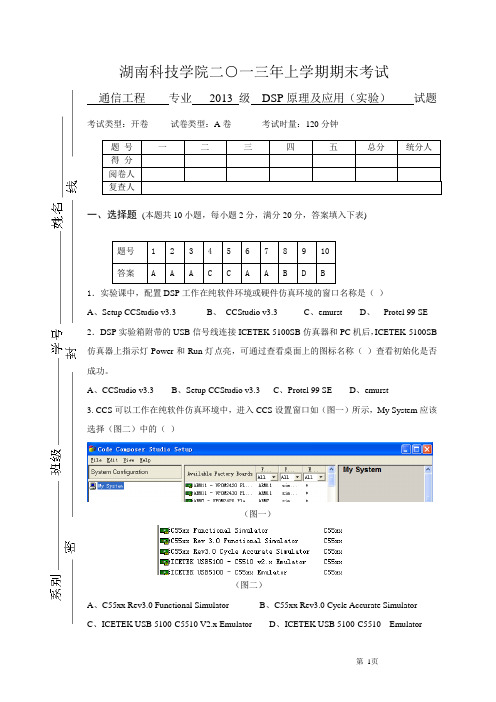

湖南科技学院二○一三年上学期期末考试通信工程专业2013 级DSP原理及应用(实验)试题考试类型:开卷试卷类型:A卷考试时量:120分钟题号一二三四五总分统分人得分阅卷人复查人一、选择题(本题共10小题,每小题2分,满分20分,答案填入下表)题号 1 2 3 4 5 6 7 8 9 10答案 A A A C C A A B D B1.实验课中,配置DSP工作在纯软件环境或硬件仿真环境的窗口名称是()A、Setup CCStudio v3.3B、CCStudio v3.3C、emurstD、Protel 99 SE 2.DSP实验箱附带的USB信号线连接ICETEK-5100SB仿真器和PC机后,ICETEK-5100SB 仿真器上指示灯Power和Run灯点亮,可通过查看桌面上的图标名称()查看初始化是否成功。

A、CCStudio v3.3B、Setup CCStudio v3.3C、Protel 99 SED、emurst3. CCS可以工作在纯软件仿真环境中,进入CCS设置窗口如(图一)所示,My System应该选择(图二)中的()(图一)(图二)A、C55xx Rev3.0 Functional SimulatorB、C55xx Rev3.0 Cycle Accurate SimulatorC、ICETEK USB 5100-C5510 V2.x EmulatorD、ICETEK USB 5100-C5510 Emulator4. 实验中,单步调试的按键是()A、F5B、F 6C、F10D、F115. 在程序中,观察某变量在运行过程的变化,可以选中该变量右键,选择()A、Editor B 、Quick Watch C 、Add to Watch Window D 、Go to…6. 实验中,要想查看寄存器值的变化,可通过“View”菜单中的()项开启内存观察窗口。

A 、MemoryB 、DisassemblyC 、RegisterD 、Watch Window7.实验中,直流电机调速改变占空比的方法是()A、定宽调频法B、调宽调频法C、定频调宽法D、以上答案均不对8. 下面几个选项中,不是C语言开发的优点的是()A、易于开发和维护B、不容易发生流水线冲突C、可移植性强D、优化代码简单9. 下面几个选项中,不是汇编语言开发的缺点的是()A、可读性差B、代码量大C、可移植性差D、容易产生流水线冲突10.C语言程序在执行时,先要调用C标准库中的初始化程序,入口标号为()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

姓名学号专业:班级任课教师:

密封线

仰恩大学2011—2012学年第二学期期末考试试题

DSP技术试卷(A)

适用班级:09通信(开卷)

一、填空(每空1分,共10分)

1.TI公司常用的DSP芯片可以归纳为三大系列,分别为、、。

2.TMS320F2812器件上有3个CPU定时器,其中用户可以在应用程序中使用的是。

3.事件管理器(EV)中的通用定时器支持4种操作模式,其中可以产生对称波形。

4.通过软件周期地向看门狗复位控制寄存器写,使看门狗计数器清零。

5.ADC模块中,其输入引脚的电压范围。

6.TMS320F2812的系统控制模块包括、锁相环、、低功耗等。

7.在EVA中,为比较单元提供时钟基准。

二、用文字简要描述下面各寄存器的主要功能(每题4分,共20分)

1.PLLCR与PCLKCR

2.GPxMUX与GPxDAT

3.IER与IFR

4.TxCON

5.ADCTRL1与ADCTRL3

三、简答题(每题6分,共30分)

1.请描述片上晶振模块允许采用的两种方式。

2.根据下图,描述GPIO各寄存器设置的流程。

3.描述CPU定时器的计数原理。

4.下图是EV中的比较单元产生非对称PWM的波形,请描述其如何产生?

5.在ADC模块中,为什么在读取结果寄存器的值时,需要先将读到的数据右移4位?

四、分析(每小题15分,共30分)

已知OSCCLK=30MHz,SysCtrlRegs.PLLCR=0xA;SysCtrlRegs.HISPCP.all=0x1;

void init_eva()

{

EvaRegs.T1PR=0xFFFF;

EvaRegs.T1CMPR=0x3C00;

EvaRegs.T1CNT=0x0000;

EvaRegs.T1CON.all=0x1042;

EvaRegs.T2PR=0x0FFF;

EvaRegs.T2CMPR=0x03C0;

EvaRegs.T2CNT=0x0000;

EvaRegs.T2CON.all=0x1042;

EvaRegs.GPTCONA.bit.TCMPOE=1;

EvaRegs.GPTCONA.bit.T1PIN=1;

EvaRegs.GPTCONA.bit.T2PIN=2;

EvaRegs.CMPR1=0x8000;

EvaRegs.CMPR2=0xC000;

EvaRegs.CMPR3=0x4000;

EvaRegs.ACTRA.all=0x0666;

EvaRegs.DBTCONA.all=0x0000;//Disable deadband

CONA.all=0xA600;

}

1.请分析SYSCLKOUT、HSPCLK、GPT1的工作时钟分别为多少,需指出它们跟那些寄存器的设置有关?

2.请分析比较单元1产生的PWM波形的周期和占空比,计算过程中需给出相关的公式?

五、计算(共10分)

已知OSCCLK=30MHz;PLLCR[3~0]=1010b;HISPCP=0010b;ADCTRL3[4~1]=0011b;ADCTRL[7]=0b;求ADCCLK,要求写出每一个计算步骤?。