试议3D封装到来时的机遇与挑战

三维集成电路封装技术的研究进展

三维集成电路封装技术的研究进展三维集成电路(3D-IC)封装技术的研究进展概述:三维集成电路(3D-IC)作为一种新型的封装技术,已经引起了广泛的关注。

它通过将多个晶片垂直堆叠以及互连,提供了更高的集成度和性能,同时减少了电路尺寸和功耗。

本文将介绍三维集成电路封装技术的研究进展,包括其原理、优势、挑战以及最新的发展。

一、三维集成电路封装技术的原理:三维集成电路封装技术通过将多个晶片以垂直的方式堆叠在一起,实现了不同功能单元的紧密集成。

这种封装方式在垂直方向上提供了更多的连线资源,并且可以大幅度缩短信号传输路径,从而提高系统的性能和速度。

在三维封装中,上下层之间的互连通过穿插在晶片周围的TSV(Through-Silicon Via,硅通孔)实现。

TSV是一种垂直连接技术,通过在晶片上进行空穴或金属填充,使位于不同晶片之间的电路能够相互连接。

二、三维集成电路封装技术的优势:1. 更高的集成度:通过垂直堆叠多个晶片,三维集成电路封装技术可以在相同尺寸的封装中提供更多的功能单元,从而大幅度提高芯片的集成度。

2. 较低的功耗和延迟:由于信号传输路径更短,三维集成电路封装技术可以降低功耗并减少传输延迟,提高系统的整体性能。

3. 更高的带宽和频率:三维封装中的TSV互连提供了更多的连线资源,可以支持更高的数据传输速率和工作频率。

4. 优化系统面积:三维集成电路封装技术可以减小整个系统的面积,因为堆叠的晶片可以大幅度减小芯片的尺寸。

三、三维集成电路封装技术的挑战:尽管三维集成电路封装技术有诸多优势,但也面临着一些挑战。

以下是一些主要的挑战:1. 温度管理:在三维封装中,不同层之间的热量可能无法有效传导,导致局部热点的形成。

因此,温度管理成为了一个重要的问题,需要采取合适的散热措施。

2. 可靠性和一致性:由于封装中存在多个晶片,在制造过程中需要保证层与层之间的一致性和连接可靠性。

这对于生产商来说是一个挑战,需要严格的工艺控制和质量检测。

3D封装的发展现状及趋势

3D封装的发展现状及趋势作者:李振华加海来源:《科学与财富》2017年第27期摘要:随着国际电子信息行业新的变革,3D封装蓬勃兴起。

本文将从发展现状和未来发展趋势两个方面对当前3D封装技术加以阐述,使大家对3D封装技术的重要性及其意义有大致的了解。

关键词:3D封装,现状,趋势一 3D封装的发展现状3D封装号称是超越摩尔定律瓶颈的最大“杀手锏”,但是对于大部分应用而言,3D封装和2.5D封装工艺仍然太昂贵了,但是可以利用这种工艺的优势并让消费者买单的一些高端应用正在进行这种新工艺的尝试。

不要指望3D封装芯片会很快出现在你的手机上,但在路由器、服务器以及高端的东西上已经开始看到3D 封装芯片的身影。

三星做的一项研究显示,相较于层叠封装设计(就像目前苹果的Ax系列处理器的设计),3D封装和2.5D封装工艺可以做到在封装尺寸下降、功耗下降的同时带宽可以大幅度增长。

在这些高价位的设计中3D封装工艺的价值开始凸显【1】。

业界现在也出现了一些非常高规格的3D封装器件。

最早出现的是Xilinx公司的高端FPGA,但它的出货量非常低,价格也非常高,所以关于让3D封装工艺的价格真正降下来这件事,它并不能提供多少参考价值,而且事实上它也只是2.5D封装的产品,还不是真正的3D 封装。

三星发布了其DDR4 DRAM 3D DIMM模块。

美光的混合存储立方体即将开始正式量产:这个存储器件在四个内存芯片上堆叠一个实现了所有控制逻辑的逻辑芯片。

SK海力士和三星也宣布他们的3D封装内存产品正在进入大批量生产阶段。

AMD(ATI)发布了采用20nm工艺的3D堆叠高带宽内存(HBM),计划在明年第二季度开始供货。

Nvidia也表示将在2016年引入3D封装工艺,英特尔曾表示他们已经掌握了这项技术,但还没有公布任何相关产品,可是别忘了他们是英特尔。

在低端市场上,Matrox已经宣布下一代GPU模块将采用AMD的3D堆叠工艺。

如果想上头条,就得追赶潮流。

三维封装的现在和未来..

三维封装的现在和未来微电子学一班随着便携式电子系统复杂性的增加, 对VLSI集成电路用的低功率、轻型及小型封装的生产技术提出了越来越高的要求。

同样, 许多航空和军事应用也正在朝该方向发展。

为满足这些要求, 现在产生了许多新的3- D 封装技术, 或是将裸芯片, 或是将MCM 沿z 轴叠层在一起, 这样, 在小型化方面就取得了极大的改进同时, 由于z 平面技术总互连长度更短, 会产生寄生电容, 因而系统功耗可降低约30%。

三维(3D)封装技术的分类三维封装的结构类型有3种: 一是埋置型3D封装,即在多层基板底层埋置IC 芯片,顶层组装IC芯片,其间高密度互连; 二是有源基板型3D封装,即在Si或GaAs 衬底上制造多层布线和多种集成电路,顶层组装模拟IC芯片和其它元器件; 三是叠层型3D封装,即把多个裸芯片或封装好芯片或多芯片模块( MCM)沿Z轴叠装、互连,组装成3D封装结构。

由于叠层型3D封装适用范围广,并且工艺相对简单,成本相对较低,已引起国外多家公司的注意,如Actel , IBM, Harris, Mo to rola 等著名公司都在积极开展叠层型3D封装的研究工作。

下面将重点介绍叠层型3D封装。

1.埋置型3D 结构这是一种实施最早( 八十年代) , 也是最为灵活方便的3D, 同时又可作为后布线的芯片互连技术, 能大大减少焊点, 提高电子产品可靠性的电子封装技术。

埋置型3D 结构又可分为基板开槽埋置型和多层布线介质埋置型, 如图1所示。

在混合集成电路( H IC) 多层布线中埋置R、C 元件已经普遍, 而埋置IC芯片和R、C 后的布线顶层仍可贴装各类IC 芯片, 就可构成更高组装密度的3D-MCM 结构。

由于布线密度及功率密度都很高, 所以这种3D-MCM 所使用的基板多为高导热的Si 基板、AIN 基板或金属基板。

上图是AIN 基板多层布线介质埋置IC 的3D-MCM 结构, 制作方法与常规多层布线技术相同。

先进封装技术的发展与机遇-2019年精选文档

先进封装技术的发展与机遇一、前言集成电路(IC)产业已成为国民经济发展的关键,而IC设计、制造和封装测试是IC产业发展的三大产业支柱。

IC封装不但直接影响着IC本身的电性能、机械性能、光性能和热性能,影响其可靠性和成本,还在很大程度上决定着电子整机系统的小型化、多功能化、可靠性和成本。

IC封装越来越受到人们的普遍重视。

本文综述了自1990年代以来迅速发展的先进封装技术,包括球栅阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维(3D)封装和系统封装(SiP)等项技术,并介绍了它们的发展状况和技术特点;同时,叙述了中国封装产业的状况,介绍了国内先进封装的发展趋势。

并对我国快速发展先进封装技术提出了一些思索和建议。

二、先进封装技术的发展回顾IC封装的历史,其发展主要划分为三个阶段。

第一阶段,在1970年代前后,以插装型封装为主,包括最初的金属圆形(TO型)封装,后来的陶瓷双列直插封装(CDIP)、陶瓷-玻璃双列直插封装(CerDIP)和塑料双列直插封装(PDIP)。

尤其是PDIP,由于性能优良、成本低廉又能批量生产而成为主流产品。

第二阶段,在1980年代以后,以表面安装类型的四边引线封装为主。

当时,表面安装技术被称作电子封装领域的一场革命。

一批适应表面安装技术的封装形式,如塑料有引线片式裁体(PLCC)、塑料四边引线扁平封装(PQFP)、塑料小外形封装(PSOP)以及无引线四边扁平封装(PQFN)等封装形式应运而生,迅速发展。

由于密度高、引线节距小、成本低并适于表面安装,使PQFP成为这一时期的主导产品。

第三阶段,在1990年代以后,以面阵列封装形式为主。

1990年代初,IC发展到了超大规模阶段,要求IC 封装向更高密度和更高速度发展,因此IC封装从四边引线型向平面阵列型发展,发明了球栅阵列封装(BGA),并很快成为主流产品。

后来又开发出了各种封装体积更小的CSP,目前仍处于快速发展阶段,详见表1。

3D集成电路技术的现状与未来展望

3D集成电路技术的现状与未来展望在当今科技飞速发展的时代,集成电路作为现代电子技术的核心基石,其发展一直备受关注。

其中,3D 集成电路技术更是以其独特的优势和巨大的潜力,成为了集成电路领域的研究热点和发展趋势。

一、3D 集成电路技术的现状1、技术原理与特点3D 集成电路是通过在垂直方向上堆叠多个芯片层,实现更高的集成度和性能提升。

与传统的平面集成电路相比,它具有更小的尺寸、更低的功耗、更高的带宽和更快的传输速度等显著优点。

2、制造工艺目前,主流的3D 集成电路制造工艺包括晶圆键合、硅通孔(TSV)技术等。

晶圆键合技术能够将不同的晶圆层精确地贴合在一起,而TSV 技术则通过在硅片上制造垂直的通孔,实现各层之间的电连接。

这些先进的制造工艺虽然复杂,但为 3D 集成电路的实现提供了可靠的技术支持。

3、应用领域在高性能计算领域,3D 集成电路使得处理器能够集成更多的核心,大大提高了计算能力。

在移动设备中,它有助于减小芯片面积,延长电池续航时间。

此外,在数据存储、通信等领域也有着广泛的应用。

4、面临的挑战然而,3D 集成电路技术在发展过程中也面临着诸多挑战。

首先是制造工艺的复杂性和成本高昂。

由于需要精确的堆叠和连接技术,制造过程中的良品率较低,导致成本上升。

其次是散热问题,多层堆叠导致热量集中,散热难度加大。

再者,设计和测试的难度也显著增加,需要新的设计方法和测试工具来保障芯片的性能和可靠性。

二、3D 集成电路技术的未来展望1、技术创新未来,我们可以期待在制造工艺上的持续创新,例如更先进的晶圆键合技术、更小直径的 TSV 以及新的材料应用,以进一步提高集成度和性能,降低成本。

2、应用拓展随着 5G 通信、人工智能、物联网等技术的迅速发展,3D 集成电路将在这些领域发挥更大的作用。

例如,在 5G 基站中,实现更高密度的射频芯片集成;在人工智能芯片中,提供更强大的计算能力和更低的功耗。

3、系统级集成未来的 3D 集成电路不仅仅是芯片层面的堆叠,还将实现系统级的集成,包括传感器、处理器、存储器等多种功能模块的一体化,构建出更加智能和高效的系统。

3D封装全解析:概念、设计与前景展望

3D封装全解析:概念、设计与前景展望专家认为:1. 3D封装是必然的发展趋势。

首先,随着芯片越来越复杂,芯片面积、良率和复杂工艺的矛盾难以调和,到一定程度就必须把大的芯片拆解成一些小的芯片。

其次,3D封装可以通过采用成熟工艺去实现一些不需要用到最先进工艺的功能模块,从而降低成本。

2. 在3D封装领域,晶圆厂和封装厂都有各自的优势,这是一块高地,大家可以协同共进。

3. 3D IC未来在中国将呈现爆发式的增长,从需求来看,这也是一个必然的趋势。

对性能有极致追求的应用,势必要用Chiplet或者3D IC 的解决方案。

但应注意,这一趋势的前提是,做大芯片的难度或者良率成本,超过通过Chiplet集成的成本。

01、重塑芯片架构的3D封装远川:如何理解3D封装的概念?2.5D、3D、Chiplet等名词如何理解?朱勇:简而言之,3D封装就是将一颗原来需要一次性流片的大芯片,改为若干颗小面积的芯片,然后通过先进的封装工艺,即硅片层面的封装,将这些小面积的芯片组装成一颗大芯片,从而实现大芯片的的功能和性能。

这种小面积的芯片就是Chiplet,一般翻译成小芯片或芯粒。

2.5D是在二维的平面上,基于硅中介层(Interposer),将Chiplet组成一个大的芯片。

Chiplet之间在硅中介层上通过数据的交互,形成一个系统级的芯片。

而3D则是在三维空间组装芯片,在垂直的方向堆叠更多的小芯片,从而集成更多的功能。

举个例子,如果要一次性做出一个比较大的乐高模型会有一定难度。

我们可以把大的乐高积木拆分成一个个小颗粒,从平面和立体的维度分别把这些小颗粒在乐高的基板上堆叠起来,从而组装成理想的大模型。

这就是3D封装的概念。

代文亮:SoC把所有的功能放在一个大芯片上,规模越做越大,芯片面积也越来越大,良率、工艺都会碰到一些问题。

这种情况下自然而然就会想到将不同工艺、不同小芯片,集成到一个小封装里。

但集成的时候也会遇到问题,例如放在封装基板上,也就是平铺Side by Side 的方式,互连会有瓶颈,间距(Pitch)也可能不够。

试议3D封装到来时的机遇与挑战

挑 战 。

关键 词 :摩 尔定律 ; D 封装 ; 焊 点 自动 光 学 显微 检测( 3 微 MMI 1 中 图分 类 号 : N4 1 T 0 文献 标 识码 :A 文章 编 号 : 0 44 0 (0 00 0 2 —6 1 0 —5 72 1 )7 0 30

Dic so n he Op r unii s a s us i n o t po t te nd Cha l ng s o he le e ft

Absr c :Ag i tt a kg o d o o r Sl w l l s fe t n s , ቤተ መጻሕፍቲ ባይዱa it fr f r ai n wil ta t ans he b c r un fM o e’ a wil o e e f c i e s a v rey o e o m to l ve

/ 年

成技 术 将 加速 C S晶圆 厂 的合 并 以及 向无 晶圆 MO

图 1

摩 尔定律

厂 模 式 转 变 的趋 势 ,最 终 3 封 装 技 术 将 与 S D MT

技 术合 二 为~ 。 -

但是, 进入 新世纪 后 , 实现 等 比例 缩减 的代 价变

为 了延 续摩 尔 定 律 的增长 趋 势 , 片技 术 已进 芯

入“ 越 摩 尔 定 律 ” 3 超 的 D集 成 时代 。 以模 块 化 封

封装工艺的创新与市场趋势

封装工艺的创新与市场趋势咱就说,在如今这个科技飞速发展的时代,封装工艺那可是相当重要啊!它就像是给芯片穿上了一件超级战衣,保护着芯片的同时,还能让它发挥出最大的效能。

我还记得有一次去一家电子厂参观,那场面真是让我大开眼界。

整个车间里,机器轰鸣,工人们都在紧张而有序地忙碌着。

在封装工艺的流水线上,我看到那些小小的芯片,就像等待被赋予新生命的小精灵。

封装工艺的创新,那可真是日新月异。

以前的封装技术,就像是给芯片裹了一层厚厚的棉袄,体积大不说,散热还不好。

但现在可不一样啦!新的封装工艺越来越精细,就像微雕艺术一样。

比如说,晶圆级封装技术,能把芯片做得超级小,就跟指甲盖似的,还能大大提高性能。

还有 3D 封装技术,把芯片一层一层叠起来,就像盖高楼一样,节省了空间,性能还杠杠的。

这些创新可不是凭空出现的,那都是科研人员们日夜钻研的成果。

他们就像一群超级英雄,不断地挑战技术的极限,为的就是让我们的电子产品更轻、更小、更强。

再来说说市场趋势。

随着 5G、人工智能、物联网这些高科技的发展,对封装工艺的需求那是越来越大。

比如说,5G 手机需要更高速、更低功耗的芯片,这就要求封装工艺得跟上步伐,不然手机发热、卡顿,谁还愿意用啊?还有智能汽车,那里面的芯片可多了去了,对封装工艺的稳定性和可靠性要求极高。

市场的竞争也是相当激烈。

各个封装厂都在拼命创新,谁能先推出更牛的封装技术,谁就能抢占市场的先机。

就像一场没有硝烟的战争,大家都在暗暗较劲。

而且,消费者的需求也在不断变化。

以前大家可能只关心电子产品能不能用,现在可不一样了,又要轻薄,又要性能好,还得好看。

这就逼着厂家们在封装工艺上下功夫,不然产品就卖不出去。

未来,封装工艺的创新肯定还会继续。

也许有一天,我们的手机会薄得像一张纸,电脑性能会强到超乎想象。

而这一切,都离不开封装工艺的不断进步。

总之,封装工艺的创新就像是一场永不停歇的赛跑,市场趋势就是那根指挥棒,引导着大家朝着更高、更快、更强的方向前进。

3D封装技术及其发展

电子知识3D封装(5)随着国际电子信息行业新的变革,3D封装蓬勃兴起。

为了在封装之内硬塞进更多功能,芯片制造商被推到了极限。

此外,我们不能忘记更加棘手的互连问题。

采用Z方向封装,或者说3D芯片封装是很好很合理的解决方式。

3D封装的出现,改变了以往先封装后组装的模式,使封装工艺与前道工艺紧密地结合在一起。

为了延续摩尔定律的增长趋势,芯片技术已进入“超越摩尔定律”的3D集成时代。

以模块化封装,晶圆级封装和硅通孔技术为标准的3D封装集成技术将加速CMOS晶圆厂的合并、以及向无晶圆厂模式转变的趋势,最终3D封装技术与SMT技术合二为一。

3D封装发展中的难题:1,减薄:减薄技术面临的首要挑战就是超薄化工艺所要求的<50μm的减薄能力。

2,3D-TSV面临通孔的刻蚀问题。

3,质量评价与检测技术相关设备。

4,实时工艺过程的实时检测问题:这一问题会导致出现高损耗。

3D技术遇到的这些问题现已经解决。

电子发烧友们已经研究出了相应的解决方法与仪器。

许多公司都在寻求密度更高的3D芯片封装。

Amkor、IBM、IMEC、Intel、Qimonda AG、Samsung, STATS ChipPAC、Tessera、德州仪器、Tezzaron、Xanoptix、Ziptronix以及ZyCube 都在研究3D芯片封装。

例如,先进半导体组装和测试服务提供商Amkor技术公司,以及位于比利时的非赢利性的纳米电子和纳米技术研究中IMEC,达成了一个为期两年的合作协议,开发成本效益高的3D集成技术,此技术将基于晶圆级处理技术。

另外IBM和3M公司计划联合开发粘合剂把半导体封装为密集地叠放的芯片塔—3D封装。

使用这种芯片将提高智能手机、平板电脑、计算机和游戏设备的速度。

估计将实现提速1000倍。

可见3D封装技术正一步步走向成熟,正慢慢的成为封装技术的首选。

小编相信3D封装会在检测仪器与接口器件等领域掀起一股革新的潮流,必将为封装技术的发展做出巨大的贡献。

三维封装的现在和未来综述

三维封装的现在和未来微电子学一班随着便携式电子系统复杂性的增加, 对VLSI集成电路用的低功率、轻型及小型封装的生产技术提出了越来越高的要求。

同样, 许多航空和军事应用也正在朝该方向发展。

为满足这些要求, 现在产生了许多新的3- D 封装技术, 或是将裸芯片, 或是将MCM 沿z 轴叠层在一起, 这样, 在小型化方面就取得了极大的改进同时, 由于z 平面技术总互连长度更短, 会产生寄生电容, 因而系统功耗可降低约30%。

三维(3D)封装技术的分类三维封装的结构类型有3种: 一是埋置型3D封装,即在多层基板底层埋置IC 芯片,顶层组装IC芯片,其间高密度互连; 二是有源基板型3D封装,即在Si或GaAs 衬底上制造多层布线和多种集成电路,顶层组装模拟IC芯片和其它元器件; 三是叠层型3D封装,即把多个裸芯片或封装好芯片或多芯片模块( MCM)沿Z轴叠装、互连,组装成3D封装结构。

由于叠层型3D封装适用范围广,并且工艺相对简单,成本相对较低,已引起国外多家公司的注意,如Actel , IBM, Harris, Mo to rola 等著名公司都在积极开展叠层型3D封装的研究工作。

下面将重点介绍叠层型3D封装。

1.埋置型3D 结构这是一种实施最早( 八十年代) , 也是最为灵活方便的3D, 同时又可作为后布线的芯片互连技术, 能大大减少焊点, 提高电子产品可靠性的电子封装技术。

埋置型3D 结构又可分为基板开槽埋置型和多层布线介质埋置型, 如图1所示。

在混合集成电路( H IC) 多层布线中埋置R、C 元件已经普遍, 而埋置IC芯片和R、C 后的布线顶层仍可贴装各类IC 芯片, 就可构成更高组装密度的3D-MCM 结构。

由于布线密度及功率密度都很高, 所以这种3D-MCM 所使用的基板多为高导热的Si 基板、AIN 基板或金属基板。

上图是AIN 基板多层布线介质埋置IC 的3D-MCM 结构, 制作方法与常规多层布线技术相同。

试议3D封装到来时的机遇与挑战

试议3D封装到来时的机遇与挑战刘斌;严仕新【摘要】揭示了在摩尔定律即将失效的大背景下,电子信息产业的开发思维、生产方式将发生一系列变革;阐述了3D封装将是电子产业发展的必然趋势;反映了检测手段的提高是3D封装目前面临的主要难题.分析了我国信息电子产业在此环境下所面临的机遇和挑战.【期刊名称】《电子工业专用设备》【年(卷),期】2010(039)007【总页数】7页(P23-28,42)【关键词】摩尔定律;3D封装;微焊点自动光学显微检测(MMI)【作者】刘斌;严仕新【作者单位】苏州德天光学技术有限公司,江苏,苏州,215000;苏州德天光学技术有限公司,江苏,苏州,215000【正文语种】中文【中图分类】TN401目前,国际电子信息行业正在经历一场新的变革,摩尔定律即将失效,3D封装蓬勃兴起,如果我们能抓住这个机会,对国内相关行业及其发展环境进行大力改革整顿,顺应世界发展潮流,将大大缩小我们同国际先进水平的差距。

1 摩尔定律的失效摩尔定律是由英特尔创始人之一戈登·摩尔(GordonMoore)提出,其内容为:集成电路上可容纳的晶体管数目,约每隔18个月便会增加1倍(见图1),性能也将提升1倍。

这一定律揭示了信息技术进步的速度。

图1 摩尔定律但是,进入新世纪后,实现等比例缩减的代价变得非常高,器件尺寸已接近单个原子,而原子无法缩减。

其次,尽管目前出现了多内核处理器,但日常使用的应用软件无法利用如此强大的处理能力;而建设芯片工厂的天价成本也阻碍摩尔定律的延伸。

摩尔本人也明确表示,摩尔定律只能再延续10年,此后在技术上将会十分困难,在他看来,摩尔定律已经走到尽头。

由此将引起产业内的一系列的变革。

1.1 开发思维的变革与此同时人们逐渐发现,当今微电子产业的发展正在呈现出两个特点:一是更加符合摩尔定律(More Moore),即建立在摩尔定律基础上的CMOS技术将持续高速发展,更高集成度、更大规模的处理器和存储器件将在电子系统中扮演“大脑”的角色;而另一方面,由无源器件、传感器、通讯器件、连接技术等非数字技术的多种技术将会构成一股不容忽视的“超越摩尔定律 (More than Moore也称新摩尔定律)”的新兴封装技术(见图2),在数字化的“大脑”周围构建起电子设备中感知和沟通外部世界的部分[1]。

封装工艺的创新与市场需求分析

封装工艺的创新与市场需求分析好嘞,以下是为您创作的关于“封装工艺的创新与市场需求分析”的文案:在科技飞速发展的当下,封装工艺就像是电子世界里的“幕后英雄”,虽然不那么起眼,但却至关重要。

先来说说封装工艺的创新吧。

记得有一次,我去一家电子厂参观,那场景可真是让我大开眼界。

在生产线上,我看到了最新的封装技术在有条不紊地运作着。

以前那种体积庞大、性能一般的封装方式早已成为过去式。

现在的封装工艺,就像是一场精密的舞蹈,每个环节都精准无误。

比如说,晶圆级封装技术,它能把芯片做得更小更薄,就像把一个大胖子变成了苗条的运动员。

这可不是一件容易的事儿!以前的封装,芯片和外界的连接就像走迷宫,线路又长又复杂,信号传输还容易出问题。

现在呢,晶圆级封装直接在晶圆上完成封装,线路短了,速度快了,性能那叫一个杠杠的!还有 3D 封装技术,这更是让人惊叹不已。

它就像是给芯片盖了一座高楼大厦,一层一层地堆叠起来,大大提高了集成度。

想象一下,以前一个芯片能处理的任务有限,现在通过 3D 封装,多个芯片像叠罗汉一样组合在一起,处理能力瞬间爆表。

我在参观的时候,看到技术人员们专注地调试着设备,眼睛紧紧盯着每一个细节,生怕出一点差错。

他们的认真劲儿,让我深深感受到了创新背后的艰辛和努力。

再来说说市场需求。

如今,电子产品越来越普及,从手机到电脑,从汽车到智能家居,哪里都离不开芯片。

而封装工艺的好坏,直接影响着芯片的性能和成本。

市场对高性能、低功耗、小尺寸的芯片需求越来越大,这就对封装工艺提出了更高的要求。

就拿智能手机来说吧,大家都希望手机越来越薄,性能却越来越好。

这可就苦了芯片厂商和封装厂了,他们得不断创新,才能满足市场的胃口。

比如说,5G 时代的到来,对芯片的速度和散热要求更高了。

封装工艺就得跟上节奏,研发出更好的散热方案,保证芯片在高速运行时不会“发烧”。

另外,汽车电子市场也是封装工艺的一个重要战场。

现在的汽车越来越智能化,自动驾驶、智能座舱等都需要强大的芯片支持。

3D封装的发展动态与前景

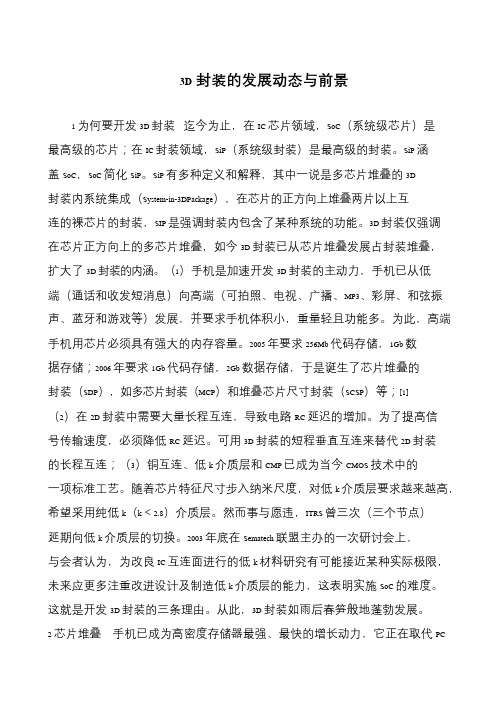

3D封装的发展动态与前景1 为何要开发3D 封装迄今为止,在IC 芯片领域,SoC(系统级芯片)是最高级的芯片;在IC 封装领域,SiP(系统级封装)是最高级的封装。

SiP 涵盖SoC,SoC 简化SiP。

SiP 有多种定义和解释,其中一说是多芯片堆叠的3D 封装内系统集成(System-in-3DPackage),在芯片的正方向上堆叠两片以上互连的裸芯片的封装,SIP 是强调封装内包含了某种系统的功能。

3D 封装仅强调在芯片正方向上的多芯片堆叠,如今3D 封装已从芯片堆叠发展占封装堆叠,扩大了3D 封装的内涵。

(1)手机是加速开发3D 封装的主动力,手机已从低端(通话和收发短消息)向高端(可拍照、电视、广播、MP3、彩屏、和弦振声、蓝牙和游戏等)发展,并要求手机体积小,重量轻且功能多。

为此,高端手机用芯片必须具有强大的内存容量。

2005 年要求256Mb 代码存储,1Gb 数据存储;2006 年要求1Gb 代码存储,2Gb 数据存储,于是诞生了芯片堆叠的封装(SDP),如多芯片封装(MCP)和堆叠芯片尺寸封装(SCSP)等;[1] (2)在2D 封装中需要大量长程互连,导致电路RC 延迟的增加。

为了提高信号传输速度,必须降低RC 延迟。

可用3D 封装的短程垂直互连来替代2D 封装的长程互连;(3)铜互连、低k 介质层和CMP 已成为当今CMOS 技术中的一项标准工艺。

随着芯片特征尺寸步入纳米尺度,对低k 介质层要求越来越高,希望采用纯低k(k<2.8)介质层。

然而事与愿违,ITRS 曾三次(三个节点)延期向低k 介质层的切换。

2003 年底在Sematech 联盟主办的一次研讨会上,与会者认为,为改良IC 互连面进行的低k 材料研究有可能接近某种实际极限,未来应更多注重改进设计及制造低k 介质层的能力,这表明实施SoC 的难度。

这就是开发3D 封装的三条理由。

从此,3D 封装如雨后春笋般地蓬勃发展。

3D封装

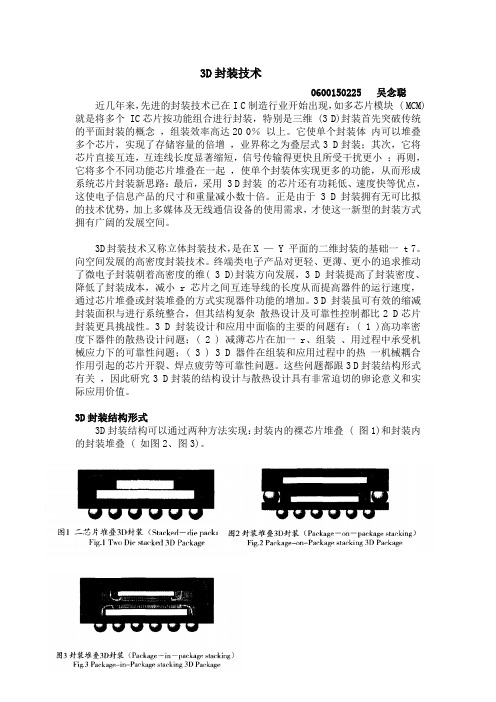

3D封装技术0600150225 吴念聪近几年来,先进的封装技术已在I C制造行业开始出现,如多芯片模块 ( MCM)就是将多个 IC芯片按功能组合进行封装,特别是三维 (3 D)封装首先突破传统的平面封装的概念,组装效率高达20 0%以上。

它使单个封装体内可以堆叠多个芯片,实现了存储容量的倍增,业界称之为叠层式3 D封装;其次,它将芯片直接互连,互连线长度显著缩短,信号传输得更快且所受干扰更小;再则,它将多个不同功能芯片堆叠在一起,使单个封装体实现更多的功能,从而形成系统芯片封装新思路:最后,采用 3 D封装的芯片还有功耗低、速度快等优点,这使电子信息产品的尺寸和重量减小数十倍。

正是由于 3 D封装拥有无可比拟的技术优势,加上多媒体及无线通信设备的使用需求,才使这一新型的封装方式拥有广阔的发展空间。

3D封装技术又称立体封装技术,是在X — Y 平面的二维封装的基础一 t 7。

向空间发展的高密度封装技术。

终端类电子产品对更轻、更薄、更小的追求推动了微电子封装朝着高密度的维( 3 D)封装方向发展,3 D 封装提高了封装密度、降低了封装成本,减小 r芯片之间互连导线的长度从而提高器件的运行速度,通过芯片堆叠或封装堆叠的方式实现器件功能的增加。

3 D 封装虽可有效的缩减封装面积与进行系统整合,但其结构复杂散热设计及可靠性控制都比2 D芯片封装更具挑战性。

3 D封装设计和应用中面临的主要的问题有:( 1 )高功率密度下器件的散热设计问题;( 2 ) 减薄芯片在加一 r、组装、用过程中承受机械应力下的可靠性问题;( 3 ) 3 D 器件在组装和应用过程中的热一机械耦合作用引起的芯片开裂、焊点疲劳等可靠性问题。

这些问题都跟3 D封装结构形式有关,因此研究3 D封装的结构设计与散热设计具有非常迫切的卵论意义和实际应用价值。

3D封装结构形式3D封装结构可以通过两种方法实现:封装内的裸芯片堆叠 ( 图1)和封装内的封装堆叠 ( 如图2、图3)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

试议3D封装到来时的机遇与挑战苏州德天光学技术有限公司摘要:本文揭示了在摩尔定律即将失效的大背景下,电子信息产业的开发思维、生产方式将发生一系列变革;较详尽地阐述了3D封装将是电子产业发展的必然趋势;反映了检测手段的提高是3D封装目前面临的主要难题。

分析了我国信息电子产业在此环境下所面临的机遇和挑战。

关键词:摩尔定律3D封装微焊点自动光学显微检测(MMI)机遇与挑战Discussion on the opportunities and challenges of the 3D package’s comingLiu Bin, Yan ShixinSuzhou Detian Optical Technology Co., Ltd.Abstract: Against the background of Moore’s law will lose effectiveness,a variety of reformation will appear in the development and production mode of electronics and information industry; 3D-TSV will be the inexorable trend of the electronic industry, and the improvement of detection level is the main problem of 3D package. The opportunities and challenges electronics and information industry will be faced with under the circumstances were analyzed.Key Words: Moore’s Law, 3D Package, Micro-joint Automatic Optical Micro-Inspection (MMI), Opportunities and Challenges目前,国际电子信息行业正在经历一场新的变革,摩尔定律即将失效,3D封装蓬勃兴起,如果我们能抓住这个机会,对国内相关行业及其发展环境进行大力改革整顿,顺应世界发展潮流,将大大缩小我们同国际先进水平的差距。

1 摩尔定律的失效摩尔定律是由英特尔创始人之一戈登·摩尔(Gordon Moore)提出来的。

其内容为:集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

这一定律揭示了信息技术进步的速度。

图 1 摩尔定律但是,进入新世纪后,实现等比例缩减的代价变得非常高,器件尺寸已接近单个原子,而原子无法缩减。

其次,尽管目前出现了多内核处理器,但日常使用的应用软件无法利用如此强大的处理能力;而建设芯片工厂的天价成本也阻碍摩尔定律了的延伸。

摩尔本人也明确表示,摩尔定律只能再延续十年,此后在技术上将会十分困难,在他看来,摩尔定律已经走到尽头。

由此将引起产业内的一系列的变革。

1.1 开发思维的变革与此同时人们逐渐发现,当今微电子产业的发展正在呈现出两个特点:一是更加符合摩尔定律(More Moore),即建立在摩尔定律基础上的CMOS技术将持续高速发展,更高集成度、更大规模的处理器和存储器件将在电子系统中扮演“大脑”的角色;而另一方面,由无源器件、传感器、通讯器件、连接技术等非数字技术的多种技术将会构成一股不容忽视的“超越摩尔定律(More than Moore也称新摩尔定律)”的新兴封装技术,在数字化的“大脑”周围构建起电子设备中感知和沟通外部世界的部分[1]。

图 2 新摩尔定律(超越摩尔定律)因此,当今业界的发展趋势不是一味地追求缩小器件的几何尺寸,而是倾向于提供更多的附加功能和特性,从而开辟全新的应用领域,为客户提供多元化服务及开发工具,实现超越摩尔定律的目标。

1.2 生产方式的变革为了延续摩尔定律的增长趋势,芯片技术已进入“超越摩尔定律”的3D集成时代。

以模块化封装,晶圆级封装和硅通孔技术为标准的3D封装集成技术将加速CMOS晶圆厂的合并、以及向无晶圆厂模式转变的趋势,最终3D封装技术将与SMT技术合二为一。

同时,一些MEMS应用也开始采用3D内插器模块平台来整合ASIC和MEMS芯片,此平台还可运用到许多SiP应用中。

这一切都是超越摩尔定律下的生产方式变革。

图 3 3D封装技术首先用于图像传感器,然后将进入半导体各个领域并不断增长可以预知的是,在这一重大变革到来之时,将带来如下产业群的发展:1.新的生产设备群诞生。

如键合机,烧结炉,微打孔机,微检测仪等等。

2.新的器件和材料群的诞生。

如接口器件、散热器件,导电材料等等同时由于生产方式的变革既带来了新的产业群的诞生同时也意未着传统的SMT设备淘汰。

1.3 设计、生产一体化的技术流程目前的制造行业面临着空前的挑战,不能不缩短产品的开发周期,尽可能地、尽快地推出具有更多功能、更好质量的产品,以更低的价格和最快的速度推向市场,并且还必须能够不断地去满足日益增多的客户的个性化的需求,快速地组成生产和销售。

而电子制造产业受摩尔定律影响,其产品更新换代的速率比其他行业更为迅速,这就对行业的各个方面,尤其是研发和设计的环节带来了非常严峻的挑战。

同时也对设计、管理、产业规划提出了更高要求:设计人员要有一体化概念在产品的开发过程中,设计人员通常因为信息来源的问题,很难能够清楚地去掌握现在的原材料的价格、供货周期甚至是产品的生产加工方式以及影响使用性能的重要因素。

因此,开发人员就很难在设计的过程里就去准确地估算产品的成本,可加工性甚至使用性能,使得开发周期增长,产品总成本大为增加。

我国的产品开发人员往往只注重局部功能的实现而忽略了产品的整体性能的提高,并且在这一思维的指导下,开发人员根本不考虑产品的可制造性,根本不会考虑生产设备共用性的问题,这样很难及时地将开发出来的产品,迅速地转化为商品,从而以最快的速度进入市场。

管理人员要有一体化意识但在摩尔定律濒临失效的背景下,电子制造业正迅速向系统化、模块化、多功能化方向,这就对研发人员提出了更高的要求:不仅整个系统开发人员与生产人员之间,而且各个模块开发人员之间也要相互交流合作,才能在最短时间内开发出功能最完善,系统整体性能更好的产品,从而在竞争中立于不败之地。

产业规划人员要有一体化思维电子制造业的发展必须有一个良好的产业链发展的环境。

而在一个国家或地区的发展规划中,产业链上的各部分往往分属于不同的部门,这就要求各部门产业规划人员之间能够充分沟通,对电子制造业产业链进行战略性整合,促进其飞速发展。

2 三维封装的兴起三维封装是将多个芯片垂直连接的一系列方法的统称,到目前为止,三维封装只在引线键合、倒装芯片、模块化封装等特定应用中取得成功。

然而,硅通孔封装技术(TSV)作为备选方案得到了迅猛发展。

硅通孔技术(TSV)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的最新技术。

以TSV为代表的3D集成技术优势有:降低延迟:IBM半导体研发中心副总裁Lisa Su指出:TSV可把芯片上数据需要传输的距离缩短1000倍,并使每个器件的互连性增加100倍。

英特尔计划在未来的万亿赫兹研究型处理器中采用TSV技术。

降低功耗:据报道,IBM在90 nm节点的微处理器50%以上的有源开关功耗都用于驱动互连线,并且90%以上的功率实际上是由10%的长互连线消耗的。

据称,TSV可将硅锗芯片的功耗降低大约40%。

手机和其他一些应用需要更加创新的芯片级封装(CSP)解决方案。

现在系统设计师为了手机和其他很多紧凑型消费品,不得不选择用3D封装来开发z方向上的潜力。

因此,业内人士将TSV 称为继引线键合(Wire Bonding)、TAB 和倒装芯片(FC)之后的第四代封装技术。

据市场研究公司Yole Developpement统计,到2015年,3D-TSV晶圆的出货量将达数百万,并可能对25%的存储器业务产生影响。

2015年,除了存储器,3D-TSV晶圆在整个半导体产业的份额也将超过6%[2]。

图 4 3D技术平台市场细分2.1 3D封装目前所遇到问题对于3D-TSV阵列堆叠,关键要素有通孔形成/填充、晶圆减薄、质量评价与检测技术、凸点形成和芯片与芯片/衬底的键合等。

这些问题的解决将依赖于大量新型设备与工艺的开发。

图 5在设计方案提出之后,设备和材料就成为制造3D-TSV IC的关键因素减薄技术与设备减薄技术面临的首要挑战就是超薄化工艺所要求的<50μm的减薄能力。

在这个厚度上,硅片很难容忍减薄工程中的磨削对硅片的损伤及内在应力,其刚性也难以使硅片保持原有的平整状态。

目前业界的主流解决方案是采用东京精密公司所率先倡导的一体机思路,将硅片的磨削、抛光、保护膜去除、划片膜粘贴等工序集合在一台设备内,硅片从磨片一直到粘贴划片膜为止始终被吸在真空吸盘上,始终保持平整状态,从而解决了搬送的难题。

刻蚀技术与设备TSV制程都面临一个共同的难题:通孔的刻蚀。

目前通常有两种方法:激光钻孔以及深反应离子刻蚀(DRIE)。

激光加工系统供应商Xsil公司为TSV带来了最新解决方案,Xsil称激光钻孔工艺将首先应用到低密度闪存及CMOS传感器中,随着工艺及生产能力的提高,将会应用到DRAM中。

在TSV刻蚀设备领域,Lam Research推出了第一台300mm TSV刻蚀设备2300Syndion,并已发货至客户。

而Aviza针对TSV先进封装也推出了Omegai2L刻蚀系统,日月光(ASE)已宣布将采用此系统研发先进制程技术。

晶圆键合技术与设备EVG公司(奥地利)自2002年起,便致力于针对3D集成开发300mm晶圆键合设备,其首款300mm多反应腔3D键合系统已在2008年完成。

CEA-Leti (法国)及SET(法国)成功开发出新一代高精度(0.5μm)高键合力(4000N)的300mm晶圆器件键合设备FC300[4]。

质量评价与检测技术相关设备可以预见,TSV的特殊性还会给3D IC制造的检测和量测带来前所未有的困难,控制TSV 通孔工艺需要几何尺寸的量测,以及对刻蚀间距和工艺带来的各种缺陷进行检测。

通常TSV 的直径在1μm到50μm,深度在10μm到150μm,深宽比在3到5甚至更高,一颗芯片上的通孔大约在几百甚至上千。

减薄和键合工艺对检测和量测的需求更多。

厚度和厚度均匀度需要测量,工艺中必须监控研磨浆残留、微粒污染、铜微粒、应力引起的开裂、边缘碎片等。

对于键合,无论是芯片至晶圆、还是晶圆之间,在精准的对位的同时,还需要控制表面粗糙程度、表面洁净度和平坦度。