《___数字系统设计___》试卷含答案

专科《硬件描述语言和数字系统设计》_试卷_答案

专科《硬件描述语⾔和数字系统设计》_试卷_答案专科《硬件描述语⾔和数字系统设计》⼀、(共36题,共150分)1. reg类型的数组通常⽤于描述存储器,reg [15: 0] MEM [0:1023];定义存储器字的位数为(2分)A.1024B.16C.16384D.1040.标准答案:B2. 下列关于同步有限状态机的描述错误的是()(2分)A.状态变化只能发⽣在同⼀个时钟跳变沿;B.状态是否变化要根据输⼊信号,只要输⼊条件满⾜,就会⽴刻转⼊到下⼀个状态。

C.在时钟上升沿,根据输⼊信号的变化,确定电路状态D.利⽤同步状态机可以设计出极其复杂灵活的数字逻辑电路系统.标准答案:B3. 关于如下描述,正确的说法是( ) (2分)A.这种描述是错误的B.该电路不可综合C.该电路不可综合,但⽣成的不是纯组合逻辑D.以上说法都不对.标准答案:D4. 下列关于流⽔线的描述错误的是( ) (2分)A.流⽔线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插⼊寄存器,并暂存中间数据的⽅法;B.设计流⽔线⽬的是提⾼数据吞吐率C.流⽔线缩短了在⼀个时钟周期内给的那个信号必须通过的通路长度,从⽽可以提⾼时钟频率D.增加流⽔线长度可以节省更多延迟,流⽔线越长,⾸次延迟越⼤,系统频率就会降低。

.标准答案:D5. 以下关于Top-Down的设计⽅法不正确的描述是( ) (2分)A.Top-Down的设计⽅法⾸先从系统设计⼊⼿;B.Top-Down设计中的系统总体仿真与所选⼯艺有关C.Top-Down的设计⽅法从顶层进⾏功能划分和结构设计D.⾃顶向下的设计⽅法可以早期发现结构上的错误.标准答案:B6. 在verilog中,下列哪些操作⼀定是单bit?()(2分)A.==B.^C.>D.&&.标准答案:A,B,C,D7. 下⾯哪些是verilog的关键字()(2分)A.inputB.assignC.writeD.module.标准答案:A,B,D8. 全球主要的FPGA⼚家有()(2分)A.XilinxB.AlteraC.Broadcom/doc/1830848533687e21ae45a947.html ttice.标准答案:A,B,D9. ⼤规模数字逻辑设计原则,正确的说法有()(2分)A.异步设计原则B.组合时序电路分开原则C.⾯向RTL的原则D.先电路后代码的原则.标准答案:B,C10. 下⾯有关SRAM,DRAM的叙述,正确的有()(2分)A.DRAM存储单元的结构⽐SRAM简单B.DRAM⽐SRAM成本⾼C.DRAM⽐SRAM速度快D.DRAM要刷新,SRAM不刷新.标准答案:A,D11. 阻塞赋值与⾮阻塞赋值的差别及其各⾃的使⽤环境。

数字系统设计II-2014-2015-期末考试试卷

浙江大学20 14–20 15学年秋冬学期《数字系统设计II》课程期末考试试卷课程号:111C0130,开课学院:_信息与电子工程学系_考试试卷:√A卷、B卷(请在选定项上打√)考试形式:√闭、开卷(请在选定项上打√)允许带1张A4 大小的手写资料和计算器入场考试日期:2015 年1月24 日,考试时间:120 分钟诚信考试,沉着应考,杜绝违纪。

考生姓名:学号:所属院系(专业):_This question considers the basic MIPS 5-stage pipeline (IF, ID, EX, MEM, WB). 1)Assume that each of the above steps takes the amount of time specified in theGiven the times for the datapath stages listed above, what would the clock period be for the entire datapath? In a pipelined datapath, assuming no hazards or stalls, how many seconds will it take to execute an instruction?2)Assume that you have the following sequence of pipelined instructions:lw $6, 0($7)add $8, $9, $10sub $11, $6, $8Where will the data operands that are processed during the EX stage of the subtract (sub) instruction come from? (Consider two situations: (1) there is no forwarding, and (2) there is full forwarding.)2. PIPELINE (13 points):Use the following MIPS code fragment:I1: ADDI $3, $0, 100 # $3 = 100I2: ADD $4, $0, $0 # $4 = 0Loop:I3: LW $5, 0($1) # $5 = MEM[$1]I4: ADD $4, $4, $5 # $4 = $4 + $5I5: LW $6, 0($2) # $6 = MEM[$2]I6: SUB $4, $4, $6 # $4 = $4 – $6I7: ADDI $1, $1, 4 # $1 = $1 + 4I8: ADDI $2, $2, 4 # $2 = $2 + 4I9: ADDI $3, $3, -1 # $3 = $3 – 1I10: BNE $3, $0, Loop #if ($3 != 0) goto Loop1) Show the timing of one loop iteration on the 5-stage MIPS pipeline withoutforwarding hardware. Complete the timing table, shown as Table Q2.1in the next page, showing all the stall cycles. Assume that the branch will stall the pipeline for 1 clock cycle only.2) According to the timing diagram of Table Q2.1, compute the number of clockcycles and the average CPI to execute ALL the iterations of the above loop.Table Q2.1 Timing of one loop iteration on the 5-stage MIPS pipeline without forwarding hardware. (F: instruction fetch, D: instruction decode, X: execute, M: memory access, W: write back.) We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle.3 / 103. CACHE (10 points):A 16-byte cache has 8-byte blocks, has 2 sets, and is 2-way set-associative. The cache initially is empty (all valid bits are off: indicated by a blank box in the table below). The cache receives requests in the sequence listed in Table Q3.1. For each address in the sequence (a) split it into the tag, index, and offset; (b) categorize the access as a hit, a compulsory miss, a confict miss, or a capacity miss (You can abbreviate hit=H, Compulsory=O, Confict=F, Capacity=P); (c) show the new contents of the cache after the access----write the tags for each way, and note which way is LRU.The first one is done for you.Table Q3.14. VIRTUAL MEMORY (9 points):Describe the number of bits required in each entry of a TLB that has the following characteristics:· Virtual addresses are 32 bits wide· Physical addresses are 31 bits wide· The page size is 2K bytes· The TLB contains 16 entries of the page table· The TLB is direct-mappedNote:Each entry of the TLB contains the following items:- a valid bit- the physical page number of the desired virtual page- a tag used to see if the desired entry of the page table is stored in the TLB- ignore the “dirty” bit1)Physical page number:2)Tag:3)The number of bits required in each entry of a TLB:5. CHOICE (60 points) (note: only one is correct):(1)Which of the following descriptions is the reason why binary expression is still used incomputer technique. ( )A: It saves components.B: It has fast computing ability.C: It is decided by the physical property of components.D: It has nice convenience in coping with information.(2)Which one is not one of the five classic components of a computer? ( )A: InputB: BusC: MemoryD: Output(3)What is the range of exponent of IEEE 745 single precision? ( )A: 1~254B: -128~126C: -126 ~127D:-127~128(4)Assume a test program A is running on computer A. It consumes 100 seconds totally, 90for CPU and 10 for I/O. Now, the CPU speed improved by 50% and I/O spee d hasn‟t changed. How much time it takes to run program A now? ( )A: 55 secB: 60 secC: 65 secD: 70 sec(5)A simple program is running on a 32-bit computer. x(int), y(short), z are variables in thisprogram. If x = 127 and y = -9, what are the contents in computer memory after executing the assigning statement z = x + y? ( )A: x = 0000007FH, y = FFF9H, z = 0076HB: x = 0000007FH, y = FFF9H, z = 00000076HC: x = 0000007FH, y = FFF7H, z = 0076HD: x = 0000007FH, y = FFF7H, z = 00000076H(6)Which of the following instructions could this single-cycle datapath description bereferring to? ( )Description :Two source registers (ReadReg) and one destination register (WriteReg) are selected, and the values are read from the source registers and sent as input to the ALU.The ALU operation is performed, the result is written to the destination register, and the PC is updated.A: add B: ori C: li D: sll(7)The following commands were used to store the contents of registers $s0 and $s1 onto thestack:addi $sp, $sp, -8sw $s0, 0($sp)sw $s1, 4($sp)# insert various unrelated instructions hereAssuming that neither the stack pointer nor the stack has been changed during the "various unrelated instructions" part, which of the following would allow you to recover the contents of $s0 and $s1 while returning $sp to its original (pre-decremented) value? ( )A: addi $sp, $sp, 8; lw $s0, 4($sp); lw $s1, 0($sp)B: addi $sp, $sp, 8; lw $s0, 0($sp); lw $s1, 4($sp)C: lw $s0, 4($sp); lw $s1, 0($sp); addi $sp, $sp, 8D: lw $s0, 0($sp); lw $s1, 4($sp); addi $sp, $sp, 8(8)How the cache conflict misses will be affected by the following modifications? ( )Assume the baseline cache is set associative.(a). Double the associativity while keep the capacity and line size constant(b). Double the number of sets while keep the capacity and line size constantA: Decrease; IncreaseB: Increase; DecreaseC: Increase; IncreaseD: Decrease; Decrease(9)Which of the following statements about multiplication and division is incorrect? ( ) A: Integer multiplications takes an input two 32-bit values and returns a 64-bit valueB: The result of a multiplication is stored in a read-only (for the programmer at least) "product" registerC: The product of two numbers is accesssed using two separate instructions - mfhi to get bits 0-31 (the rightmost bits), and mflo to get bits 32-63D: The div command stores the quotient and the remainder in the product register, and the two can be accessed using mfhi and mflo(10)Which of the following is generally true about a design with two levels of caches? ( ) A: First-level caches are more concerned about hit time, and second-level caches are more concerned about miss rate.B: First-level caches are more concerned about miss rate, and second-level caches are more concerned about hit time.C: Second-level caches often use lower associativity than first-level caches given the focus of reducing miss rates.D: Second-level caches are as fast as first-level caches.(11)The communication between central system and the outside environment is doneby ( )A: Input-output subsystemB: Control systemC: Memory systemD: Logic system(12)Which of the following statements about flash memory is wrong? ( )A: The information can be either read or written, and the read speed is the same as write speed.B: The storage unit is consist of MOSFET, so it is a semiconductor storage.C: Information will not lose after power down.D: It can be a replacement for the external memory.(13)Which of the following situation will not happen? ( )A: TLB miss, Cache miss, Page missB: TLB miss, Cache hit, Page hitC: TLB hit, Cache hit, Page hitD: TLB hit, Cache hit, Page miss(14)The techniques which move the program blocks to or from the physical memory is calledas ______. ( )A: Paging B: Virtual memory organisation C: Overlays D: Framing(15)The method of synchronising the processor with the I/O device in which the device sendsa signal when it is ready is______. ( )A: Exceptions B: Signal handling C: Interrupts D: DMA(16)Let's say we have an array with 4 integer elements. The address of the first element in thearray is stored in $t0. Which of the following gives us the result of the last element of the array (stored in $t1)? ( )A: addi $t1, $t0, 3; sll $t1, 2;B: addi $t1, $t0, 16C: sll $t0, 2; addi $t1, $t0, 3D: addi $t1, $t0, 12(17)How many total bits are required for a direct-mapped cache with 16KB of data and4-word blocks, assuming a 32-bit address? Take valid bit into consideration. ( )A: 146Kbits B: 147Kbits C: 148Kbits D: 149Kbits(18)Consider a virtual memory system with 32-bit virtual byte address, 4KB/page, 32 bitseach entry. The physical memory is 512MB. Then, the total size of page table needs. ( ) A: 1MB B: about 3MB C: 4MB D: 8MB(19)What is the average time to read or write a 512-byte sector for a typical disk rotating at10,000 RPM? The advertised average seek time is 6 ms, the transfer rate is 50 MB/sec, and the controller overhead is 0.2 ms. Assume that the disk is idle so that there is no waiting time. ( )A: 6.0ms B: 9.0ms C: 9.01ms D: 9.21ms(20)In cache, the replacement strategy includes RAND, FIFO and LRU. Which of thesestrategies is relative to the locality principle? ( )A: RAND B: FIFO C: LRU D: NONE6. CACHE DESIGN (10 points) (Additional Questions)To improve the hit rate for our data cache, we made it 2-way set associative (it was formerly direct mapped). Sadly as a consequence the hit time has gone up, and we are going to use way-prediction to improve it. Each cache set will have a way prediction indicating which way is likely to be accessed.When doing a cache access, the prediction is used to route the data. If it is incorrect, there will be a delay as the correct way is used. If the desired data is not resident in the cache, it is like a normal cache miss. After a cache miss, the prediction is not used since the correct block is already known. Figure Q6.1-A summarizes this process.Figure Q6.1-A: Way-prediction FSMSince there are two ways, only one bit will be used per prediction, and its value will directly correspond to the way. How the predictions are generated or maintained are beyond the scope of this problem. You can assume that at the beginning of a cycle, the selected prediction is available, and determining the prediction is not on the critical path. The diagram of the data portion of our cache is shown in Figure Q.6.1-B.Figure Q6.1-B Data portion of the cacheOur cache has 16 byte lines, is 2-way set associative, and has a total capacity of 4kB.A.Please complete Table Q6.1 with delays across each element of the cache. Usingthe data you compute in Table Q6.1, calculate the critical path delay through this cache (from when the Input Address is set to when the correct data is on the DataYou may assume that the prediction register is correctly loaded at the start of the cycle, and the clk-to-q delay is 100ps. The inverting and non-inverting buffer drivers both have the same delay. You only need to worry about the case of a fast hit (cache hit with correct prediction).B.Now we will study the impact of way prediction on cache hit rate. For thisproblem, the cache is a 128 byte, 2-way set associative cache with 16 bytes per cache line. The cache is byte addressable and uses a least recently used (LRU) replacement policy.Please complete Table Q6.2 showing a trace of memory accesses. In the table, each entry contains the {tag, index} contents of that line, or “-”, if no data is present. You should only fill in elements in the table when a value changes. For simplicity, the addresses are only 8 bits.The first 3 lines of the table have been filled in for you. The initial values marked with a …*‟ are the least recently used ways in that set. For your convenience, the address breakdown for access to the main cache is depicted below.。

数字系统设计 期中考试试卷 及答案

《数字系统设计》期中考试试卷A (闭卷)班级学号姓名成绩一.单项选择题(每题2分,共20分)1.表示任意两位无符号十进制数需要( B )二进制数。

A.6 B.7 C.8 D.92.补码1.1000的真值是( D )。

A.+1.0111 B. -1.0111 C. -0.1001 D. -0. 10003.根据反演规则,F=(A’+C)(C+DE)+E’的反函数为( A )。

A. F'=(AC'+C'(D'+E'))EB. F’=AC+C(D+E)EC. F'=(AC’+C’D’+E’)ED. F’=A’C+C(D+E)E’4.要使JK触发器在时钟作用下的新态与初态相反,JK端取值应为( D )。

A.JK=00 B. JK=01 C. JK=10 D. JK=115.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要( B )个2输入的异或门。

A.2 B. 3 C. 4 D. 56.在下列三个逻辑函数表达式中,( A )是最小项表达式。

A. Y(A,B)=AB’+A’BB. Y(A,B,C)= AB’+A’B +A’BC+AB’CC. Y(A,B,C)=A’BC+AB’C+BC’D. Y(A,B,C,D)=A’B’C’+AC’B+ABC+A’B’C7.采用OC门主要解决了( B )。

A. TTL与非门不能相与的问题B. TTL与非门不能线与的问题C. TTL与非门不能相或的问题D. TTL与非门抗干扰的问题8.逻辑函数F=AB'+CD',其对偶函数F*为( C )。

A. (A’+B’)(C’+D’)B. (A’+B)(C’+D)C. (A+B’)(C+D’)D. (A+B)(C+D)9.逻辑函数Y=(AB+B)CD+(A+B)(B+C)的最简与或形式为( B )。

A. AB+CB. AC+BC. A+BCD. AB+BC+AC10.卡诺图上变量的取值顺序是采用( B )的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)1.Verilog语⾔有什么作⽤?可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型;Verilog HDL的构造性语句可以精确地建⽴信号的模型;2.构成模块的关键词是什么?module,endmodule。

3.为什么说可以⽤Verilog构成⾮常复杂的电路结构?因为Verilog可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型Verilog HDL的构造性语句可以精确地建⽴信号的模型;4.为什么可以⽤⽐较抽象的描述来设计具体的电路结构?因为有可以⽤⽐较抽象描述设计电路结构的语⾔,⽽这种语⾔是适合数字系统设计的语⾔。

5.是否任意抽象的符合语法的Verilog模块都可以通过综合⼯具转变为电路结构?不能。

《数字逻辑与数字系统》期末考试试题(A)

北京邮电大学2008——2009学年第一学期《数字逻辑与数字系统》期末考试试题(A )考试注意事项一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必须按照监考教师指定座位就坐。

二、书本、参考资料、书包等物品一律放到考场指定位置。

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。

四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。

五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。

考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分满分 10 20 10 10 10 12 14 14 得分 阅卷 教师一、选择题(每小题1分,共10分。

)1. )D C B (B )B A (A F ++++==( )A .B B . A+BC . 1D .AB2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。

A .( 10000011)2B .(10100100)2C . (1010011)2D . (11001011)24. 74LS85为四位二进制数据比较器。

如果只进行4位数据比较,那么三个级联输入端a<b 、a>b 、a=b 应为( )。

A . a<b 接地,a>b 接地,a=b 接地B . a<b 接高电平,a>b 接高电平,a=b 接高电平C . a<b 接高电平,a>b 接高电平,a=b 接地5. N 个触发器可以构成能寄存( )位二进制数码的寄存器。

A. NB. 2NC. 2ND. N 26.时序电路中对于自启动能力的描述是( )。

A . 无效状态自动进入有效循环,称为具有自启动能力。

《数字电路与系统设计》第6章习题答案

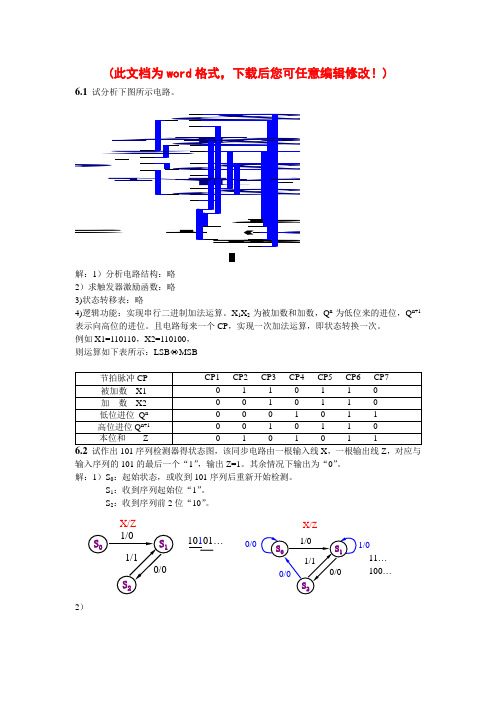

l ee t h e \1210101…X/Z0/01/0X/Z11…100…6.3对下列原始状态表进行化简: (a)解:1)列隐含表: 2)进行关联比较3)列最小化状态表为:a/1b/0b b/0a/0aX=1X=0N(t)/Z(t)S(t)解:1)画隐含表: 2)进行关联比较: 6.4 试画出用MSI 移存器74194构成8位串行 并行码的转换电路(用3片74194或2片74194和一个D 触发器)。

l ee t-h e \r 91行''' 试分析题图6.6电路,画出状态转移图并说明有无自启动性。

解:激励方程:略 状态方程:略状态转移图 该电路具有自启动性。

6.7 图P6.7为同步加/减可逆二进制计数器,试分析该电路,作出X=0和X=1时的状态转移表。

解:题6.7的状态转移表X Q 4nQ 3nQ 2nQ 1nQ 4n +1Q 3n +1Q 2n +1Q 1n +1Z 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 1 1 0 0 0 0 1 1 0 0 1 0 1 1 0 0 1 0 1 1 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 0 0 0 0 1 0 0 0 0 1 1 1 0 0 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 0 0 0 1 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 11 1116.8分析图6.8电路,画出其全状态转移图并说明能否自启动。

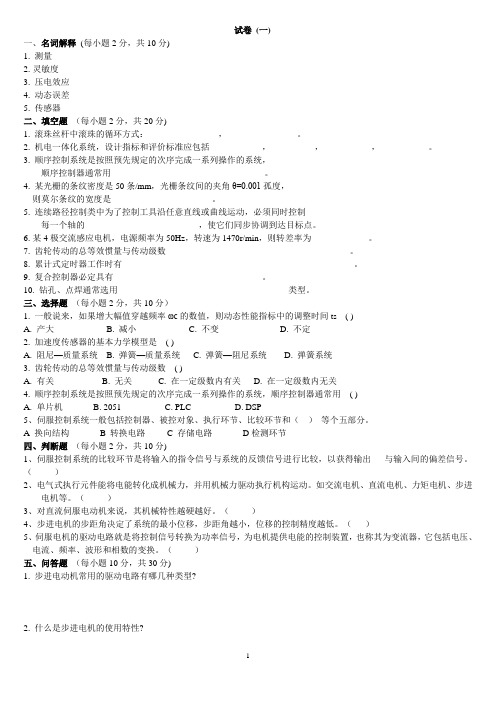

《机电一体化系统设计》期末考试模拟试题(含答案)

试卷(一)一、名词解释(每小题2分,共10分)1. 测量2.灵敏度3. 压电效应4. 动态误差5. 传感器二、填空题(每小题2分,共20分)1. 滚珠丝杆中滚珠的循环方式:________________,________________。

2. 机电一体化系统,设计指标和评价标准应包括__________,__________,__________ ,__________。

3. 顺序控制系统是按照预先规定的次序完成一系列操作的系统,顺序控制器通常用___________________________________。

4. 某光栅的条纹密度是50条/mm,光栅条纹间的夹角θ=0.001孤度,则莫尔条纹的宽度是_______________________。

5. 连续路径控制类中为了控制工具沿任意直线或曲线运动,必须同时控制每一个轴的______________________,使它们同步协调到达目标点。

6.某4极交流感应电机,电源频率为50Hz,转速为1470r/min,则转差率为_____________。

7. 齿轮传动的总等效惯量与传动级数__________________________________________。

8. 累计式定时器工作时有_____________________________________________________。

9. 复合控制器必定具有__________________________________。

10. 钻孔、点焊通常选用_______________________________________类型。

三、选择题(每小题2分,共10分)1. 一般说来,如果增大幅值穿越频率ωc的数值,则动态性能指标中的调整时间ts ( )A. 产大B. 减小C. 不变D. 不定2. 加速度传感器的基本力学模型是A. 阻尼—质量系统B. 弹簧—质量系统弹簧—阻尼系统 D. 弹簧系统3. 齿轮传动的总等效惯量与传动级数( )A. 有关B. 无关C. 在一定级数内有关D. 在一定级数内无关4. 顺序控制系统是按照预先规定的次序完成一系列操作的系统,顺序控制器通常用( )A. 单片机B. 2051C. PLC5、伺服控制系统一般包括控制器、被控对象、执行环节、比较环节和()等个五部分。

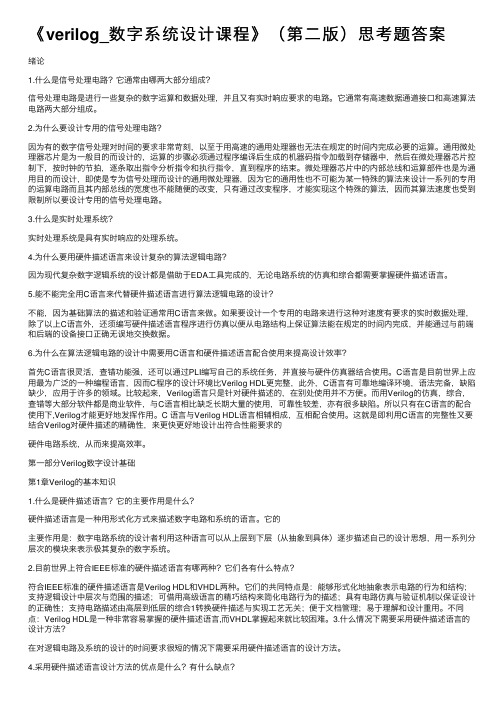

《verilog_数字系统设计课程》(第二版)思考题答案

《verilog_数字系统设计课程》(第⼆版)思考题答案绪论1.什么是信号处理电路?它通常由哪两⼤部分组成?信号处理电路是进⾏⼀些复杂的数字运算和数据处理,并且⼜有实时响应要求的电路。

它通常有⾼速数据通道接⼝和⾼速算法电路两⼤部分组成。

2.为什么要设计专⽤的信号处理电路?因为有的数字信号处理对时间的要求⾮常苛刻,以⾄于⽤⾼速的通⽤处理器也⽆法在规定的时间内完成必要的运算。

通⽤微处理器芯⽚是为⼀般⽬的⽽设计的,运算的步骤必须通过程序编译后⽣成的机器码指令加载到存储器中,然后在微处理器芯⽚控制下,按时钟的节拍,逐条取出指令分析指令和执⾏指令,直到程序的结束。

微处理器芯⽚中的内部总线和运算部件也是为通⽤⽬的⽽设计,即使是专为信号处理⽽设计的通⽤微处理器,因为它的通⽤性也不可能为某⼀特殊的算法来设计⼀系列的专⽤的运算电路⽽且其内部总线的宽度也不能随便的改变,只有通过改变程序,才能实现这个特殊的算法,因⽽其算法速度也受到限制所以要设计专⽤的信号处理电路。

3.什么是实时处理系统?实时处理系统是具有实时响应的处理系统。

4.为什么要⽤硬件描述语⾔来设计复杂的算法逻辑电路?因为现代复杂数字逻辑系统的设计都是借助于EDA⼯具完成的,⽆论电路系统的仿真和综合都需要掌握硬件描述语⾔。

5.能不能完全⽤C语⾔来代替硬件描述语⾔进⾏算法逻辑电路的设计?不能,因为基础算法的描述和验证通常⽤C语⾔来做。

如果要设计⼀个专⽤的电路来进⾏这种对速度有要求的实时数据处理,除了以上C语⾔外,还须编写硬件描述语⾔程序进⾏仿真以便从电路结构上保证算法能在规定的时间内完成,并能通过与前端和后端的设备接⼝正确⽆误地交换数据。

6.为什么在算法逻辑电路的设计中需要⽤C语⾔和硬件描述语⾔配合使⽤来提⾼设计效率?⾸先C语⾔很灵活,查错功能强,还可以通过PLI编写⾃⼰的系统任务,并直接与硬件仿真器结合使⽤。

C语⾔是⽬前世界上应⽤最为⼴泛的⼀种编程语⾔,因⽽C程序的设计环境⽐Verilog HDL更完整,此外,C语⾔有可靠地编译环境,语法完备,缺陷缺少,应⽤于许多的领域。

高中通用技术《系统与设计》练习题(附答案解析)

高中通用技术《系统与设计》练习题(附答案解析)学校:___________姓名:___________班级:_____________一、选择题1.人体系统是()A.白色系统B.自然系统C.封闭系统D.人造系统2.生活中系统随处可见,根据你的理解下列不属于系统的是()A.一堆沙子和水泥B.桥墩C.高层建筑物D.拦河大坝3.抗击新冠疫情是一场没有硝烟的全民战争。

面对疫情,中国再显大国风度,在加强国内防控的同时,还积极开展国际交流,为全球抗疫事业做出了卓越贡献。

当前,境外输入是国内病例增加的一个主要原因,从系统优化的角度分析,下列防控措施不合理的是()A.杜绝境外输入B.延长隔离时间C.固定隔离区域D.加大监测频率4.单车智能机电锁系统。

其工作过程是:用户用智能手机扫描单车上二维码并将信息发送给云端后台控制系统,无线移动通信模块接收到云端后台控制系统发送来的解锁指令后,将指令传给车载中央控制单元,经过处理后,触发电子控制开关,开启机械锁装置控制插销打开,完成单车自动解锁。

单车解锁以后,触发电子控制开锁成功开关,通过车载中央控制单元,不断通过无线移动通信模块上报单车最新定位信息到云端后台管理系统;当用户锁车成功时,触发电子控制锁车成功开关,通过无线移动通信模块通知云端后台管理系统锁车成功,云端后台管理系统停止计时、计费并向用户发送相关信息。

关于单车智能机电锁系统的说法中,不正确的是 ()A.能实现自动锁车、解锁、计时和计费功能,体现了系统的目的性B.智能电锁系统需定期进行检测和维护,体现了系统的动态性C.刮风下雨时,经常出现扫码后不能及时解锁的问题,体现了系统的环境适应性差D.设计时需考虑单车定位准确、便于维护、安装等,还要兼顾成本等因素,体现了系统分析的整体性原则5.汽车是一种很重要的交通工具。

从系统角度看,汽车动力系统属于()A.自然系统B.实体系统C.概念系统D.抽象系统6.设计师设计一款地热毯,需要统筹兼顾电热效应高、电磁效应低、安全可靠、成本低、底层隔热性能好等诸多目标。

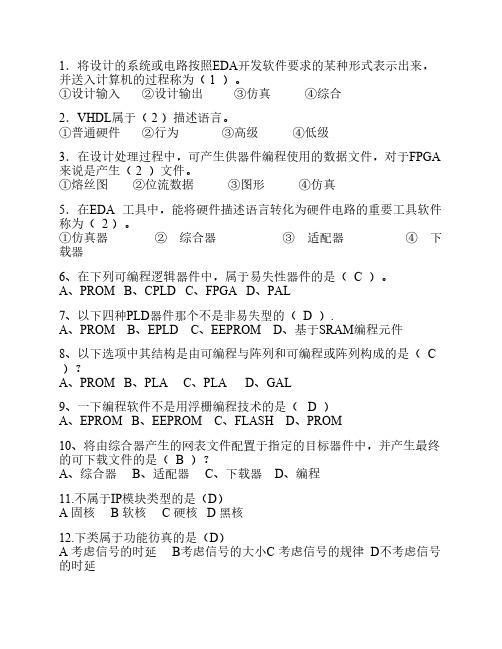

选择题 数字系统设计

1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( 1 )。

①设计输入②设计输出③仿真④综合2.VHDL属于( 2 )描述语言。

①普通硬件②行为③高级④低级3.在设计处理过程中,可产生供器件编程使用的数据文件,对于FPGA 来说是产生( 2 )文件。

①熔丝图②位流数据③图形④仿真5.在EDA 工具中,能将硬件描述语言转化为硬件电路的重要工具软件称为( 2 )。

①仿真器 ② 综合器 ③ 适配器 ④ 下载器6、在下列可编程逻辑器件中,属于易失性器件的是( C )。

A、PROMB、CPLDC、FPGAD、PAL7、以下四种PLD器件那个不是非易失型的( D ).A、PROMB、EPLDC、EEPROMD、基于SRAM编程元件8、以下选项中其结构是由可编程与阵列和可编程或阵列构成的是( C )?A、PROMB、PLAC、PLAD、GAL9、一下编程软件不是用浮栅编程技术的是( D )A、EPROMB、EEPROMC、FLASHD、PROM10、将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件的是( B )?A、综合器B、适配器C、下载器D、编程11.不属于IP模块类型的是(D)A 固核B 软核C 硬核D 黑核12.下类属于功能彷真的是(D)A 考虑信号的时延 B考虑信号的大小C 考虑信号的规律 D不考虑信号的时延13.下类不属于简单PLD的是(B)A PLAB PROMC PALD GAL14、EDA技术发展的第二阶段是(B)A、CADB、CAEC、EDAD、PLD15、(B)指的是以版图形式实现的设计模块。

A、软核B、硬核C、固核D、散核16、可编程逻辑阵列是(C)A、PROMB、PALC、PLAD、GAL17、查找表的原理类似于ROM,其物理结构是静态存储器(SRAM),N个输入项的逻辑函数可以由一个(A)位容量的SRAM来实现。

A、2B、2C、2D、2-118、Quartus Ⅱ进行EDA设计开发过程中的综合、适配属于(D)步骤中。

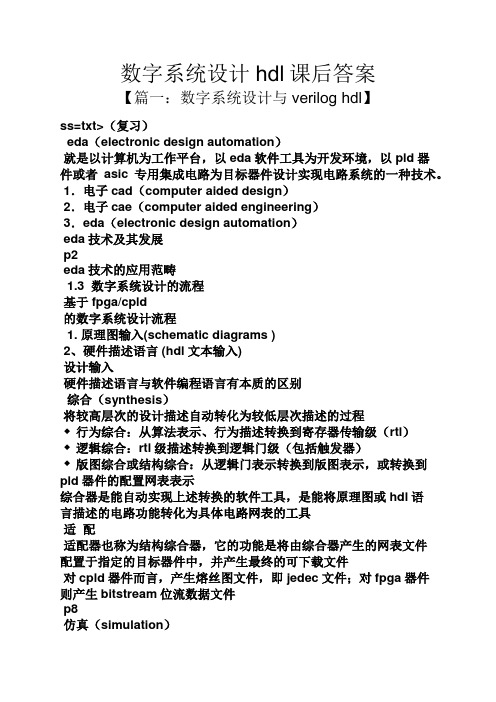

数字系统设计hdl课后答案

数字系统设计hdl课后答案【篇一:数字系统设计与verilog hdl】ss=txt>(复习)eda(electronic design automation)就是以计算机为工作平台,以eda软件工具为开发环境,以pld器件或者asic专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子cad(computer aided design)2.电子cae(computer aided engineering)3.eda(electronic design automation)eda技术及其发展p2eda技术的应用范畴1.3 数字系统设计的流程基于fpga/cpld的数字系统设计流程1. 原理图输入(schematic diagrams )2、硬件描述语言 (hdl文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(rtl)◆逻辑综合:rtl级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到pld器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或hdl语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对cpld器件而言,产生熔丝图文件,即jedec文件;对fpga器件则产生bitstream位流数据文件p8仿真(simulation)功能仿真(function simulation)时序仿真(timing simulation)仿真是对所设计电路的功能的验证p9编程(program)把适配后生成的编程文件装入到pld器件中的过程,或称为下载。

通常将对基于eeprom工艺的非易失结构pld器件的下载称为编程(program),将基于sram工艺结构的pld器件的下载称为配置(configure)。

EDA选择题(含答案)

一、选择题:(20分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是:___D__A. CPLD是基于查找表结构的可编程逻辑器件B. CPLD即是现场可编程逻辑器件的英文简称C. 早期的CPLD是从FPGA的结构扩展而来D. 在Xilinx公司生产的器件中,XC9500系列属CPLD结构2.基于VHDL设计的仿真包括有①门级时序仿真、②行为仿真、③功能仿真和④前端功能仿真这四种,按照自顶向下的设计流程,其先后顺序应该是:_________DA.①②③④ B.②①④③C.④③②①D.②④③①3.IP核在EDA技术和开发中具有十分重要的地位,IP分软IP、固IP、硬IP;下列所描述的IP核中,对于固IP的正确描述为:__________DA.提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路B.提供设计的最总产品——模型库C.以可执行文件的形式提交用户,完成了综合的功能块D.都不是4.下面对利用原理图输入设计方法进行数字电路系统设计,哪一种说法是正确的:__________BA.原理图输入设计方法直观便捷,很适合完成较大规模的电路系统设计B.原理图输入设计方法一般是一种自底向上的设计方法C.原理图输入设计方法无法对电路进行功能描述D.原理图输入设计方法不适合进行层次化设计5.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是:_______DA.PROCESS为一无限循环语句B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动C.当前进程中声明的变量不可用于其他进程D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成6.对于信号和变量的说法,哪一个是不正确的:_________AA.信号用于作为进程中局部数据存储单元B.变量的赋值是立即完成的C.信号在整个结构体内的任何地方都能适用D.变量和信号的赋值符号不一样7.下列状态机的状态编码,_________方式有“输出速度快、难以有效控制非法状态出现”这个特点。

2023年高级软考《系统架构设计师》考试历年真题摘选附带答案

2023年高级软考《系统架构设计师》考试历年真题摘选附带答案第1卷一.全考点综合测验(共20题)1.【单选题】某主机的ip 地址为202.113.25.55 ,子网掩码为255.255.255.240 。

该主机的有限广播地址为()A.202.113.25.255B.202.113.25.240C.255.255.255.55D.255.255.255.2552.【单选题】网络系统生命周期可以划分为5 个阶段,实施这5 个阶段的合理顺序是______。

A.需求规范、通信规范、逻辑网络设计、物理网络设计、实施阶段B.需求规范、逻辑网络设计、通信规范、物理网络设计、实施阶段C.通信规范、物理网络设计、需求规范、逻辑网络设计、实施阶段D.通信规范、需求规范、逻辑网络设计、物理网络设计、实施阶段3.【单选题】面向构件的编程(Component Oriented Programming,COP)关注于如何支持建立面向构件的解决方案。

面向构件的编程所需要的基本支持包括()。

A.继承性、构件管理和绑定、构件标识、访问控制B.封装性、信息隐藏、独立部署、模块安全性C.多态性、模块封装性、后期绑定和装载、安全性D.构件抽象、可替代性、类型安全性、事务管理4.【单选题】某公司拟开发一个扫地机器人。

机器人的控制者首先定义清洁流程和流程中任务之间的关系,机器人接受任务后,需要响应外界环境中触发的一些突发事件,根据自身状态进行动态调整,最终自动完成任务。

针对上述需求,该机器人应该采用( )架构风格最为合适。

A.面向对象B.主程序-子程序C.规则系统D.管道-过滤器5.【单选题】ip 服务的3个主要特点是()A.不可靠、面向无连接和尽最大努力投递B.可靠、面向连接和尽最大努力投递C.不可靠、面向连接和全双工D.可靠、面向无连接和全双工6.【单选题】某公司拟开发一个语音搜索系统,其语音搜索系统的主要工作过程包括分割原始语音信号、识别音素、产生候选词、判定语法片断、提供搜索关键词等,每个过程都需要进行基于先验知识的条件判断并进行相应的识别动作。

数字系统设计与VerilogHDL课后习题

数字系统设计与VerilogHDL课后习题习题11.1现代EDA技术的特点有哪些?1.2什么是T op-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

数字系统设计答案 (2)

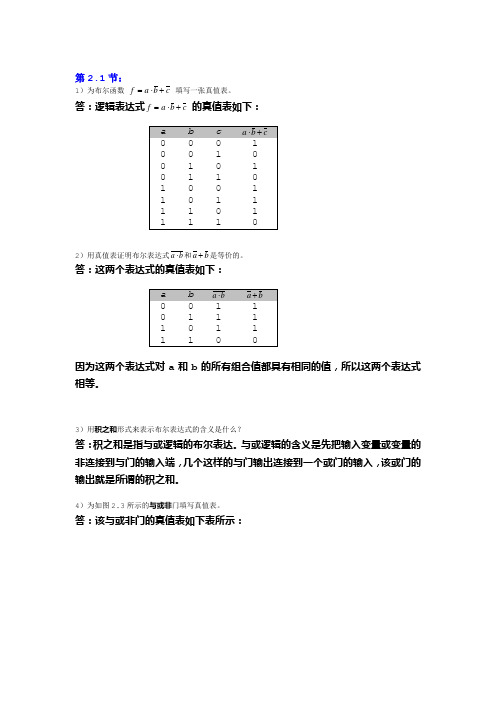

第 2.1 节:1)为布尔函数 f = a ⋅ b + c 填写一张真值表。

的真值表如下: 答:逻辑表达式 f = a ⋅ b + c 的真值表如下: a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1a ⋅b + c1 0 1 0 1 1 1 02)用真值表证明布尔表达式 a ⋅ b 和 a + b 是等价的。

答:这两个表达式的真值表如下: 这两个表达式的真值表如下: a 0 0 1 1 b 0 1 0 1a ⋅ba+b1 1 1 01 1 1 0的所有组合值都具有相同的值, 因为这两个表达式对 a 和 b 的所有组合值都具有相同的值,所以这两个表达式 相等。

相等。

3)用积之和 积之和形式来表示布尔表达式的含义是什么? 积之和积之和是指与或逻辑的布尔表达。

答:积之和是指与或逻辑的布尔表达。

与或逻辑的含义是先把输入变量或变量 的非连接到与门的输入端 几个这样的与门输出连接到一个或门的输入, 的输入端, 连接到一个或门的输入 的非连接到与门的输入端,几个这样的与门输出连接到一个或门的输入,该或 门的输出就是所谓的积之和 积之和。

门的输出就是所谓的积之和。

4)为如图 2.3 所示的与或非 与或非门填写真值表。

与或非答:该与或非门的真值表如下表所示: 该与或非门的真值表如下表所示:a 0 0 0b 0 0 0c 0 0 1d 0 1 0a ⋅b + c ⋅d1 1 10 0 0 0 0 1 1 1 1 1 1 1 10 1 1 1 1 0 0 0 0 1 1 1 11 0 0 1 1 0 0 1 1 0 0 1 11 0 1 0 1 0 1 0 1 0 1 0 10 1 1 1 0 1 1 1 0 0 0 0 05)在数字电路中,为什么要用缓冲器?缓冲器可以用来降低输出的负载, 答:缓冲器可以用来降低输出的负载,当输出必须驱动下一级逻辑门的很多个输 缓冲器可以用来降低输出的负载 入时,其负载是很重的。

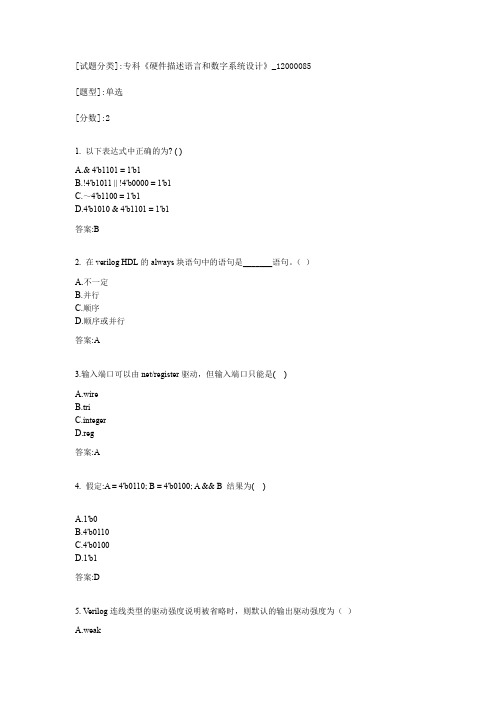

专科《硬件描述语言和数字系统设计》

[试题分类]:专科《硬件描述语言和数字系统设计》_12000085[题型]:单选[分数]:21. 以下表达式中正确的为? ( )A.& 4'b1101 = 1'b1B.!4'b1011 || !4'b0000 = 1'b1C.~4'b1100 = 1'b1D.4'b1010 & 4'b1101 = 1'b1答案:B2. 在verilog HDL的always块语句中的语句是_______语句。

()A.不一定B.并行C.顺序D.顺序或并行答案:A3.输入端口可以由net/register驱动,但输入端口只能是( )A.wireB.triC.integerD.reg答案:A4. 假定:A = 4'b0110; B = 4'b0100; A && B 结果为( )A.1'b0B.4'b0110C.4'b0100D.1'b1答案:D5. Verilog连线类型的驱动强度说明被省略时,则默认的输出驱动强度为()A.weakC.strongD.pull答案:C6. 对于下面的描述,哪一个不属于时序路径?( )A.从输入端口到输出端口B.从输入端口到触发器的时钟端clkC.从输入端口到触发器的数据输入端dD.从触发器的时钟端clk到输出端口答案:B7. 请指出下面两条语句中变量A和Count的类型。

( )A.wire/wireB.wire/regC.reg/regD.reg/wire答案:B8. 在verilog HDL的端口申明语句中,用()关键字申明端口为双向方向?A.inputB.inoutC.outputD.INOUT答案:B9. 请根据以下条语句,从选项中找出正确答案。

()B的二进制值是多少?A.8'b0000 0001B.8'bZZZZ_0000C.8'b1111 1111D.8'b0000 111110. 信号没有定义数据类型时,缺省为( )类型A.wireB.不可用C.regD.tri答案:A11. Verilog HDL 定义了一系列保留字,叫做关键词,指出下列哪一个不属于关键词()A.inputB.taskC.beginD.wire答案:C12.关于如下描述,正确的说法是( )A.该电路不可综合B.以上说法都不对C.这种描述是正确的,生成组合逻辑电路D.该电路不可综合,但生成的不是纯组合逻辑答案:B13.reg类型的数组通常用于描述存储器,reg [15: 0] MEM [1023:0]; 定义存储器字的位数为A.16B.1040C.1024D.16384答案:A14.电平触发always中不完整的的if语句,其综合结果可实现()A.组合逻辑电路B.时序逻辑电路C.条件相或的逻辑电路D.锁存器答案:D15.以下关于Top-Down的设计方法不正确的描述是( )A.Top-Down的设计方法首先从系统设计入手;B.Top-Down的设计方法从顶层进行功能划分和结构设计C.自顶向下的设计方法可以早期发现结构上的错误D.Top-Down设计中的系统总体仿真与所选工艺有关答案:D16. 请问{1,0}与下面哪一个值相等? ( )A.64'h0000000100000000B.2'b10C.2'b00D.64'h000000000002答案:B17.下列关于同步有限状态机的描述错误的是()A.在时钟上升沿,根据输入信号的变化,确定电路状态B.状态是否变化要根据输入信号,只要输入条件满足,就会立刻转入到下一个状态。

数字电路与逻辑设计试卷(有答案)

数字电路与逻辑设计(A 卷)班级 学号 姓名 成绩一.单项选择题(每题1分,共10分)1.表示任意两位无符号十进制数需要( )二进制数。

)二进制数。

)二进制数。

A .6B 6 B..7C 7 C..8D 8 D..92.余3码10001000对应的2421码为(码为( ))。

A .01010101 B.10000101 C.10111011 D.11101011 3.补码1.1000的真值是(的真值是( ))。

A . +1.0111 B. -1.0111 C. -0.1001 D. -0. 1000 4.标准或.标准或--与式是由(与式是由( )构成的逻辑表达式。

)构成的逻辑表达式。

)构成的逻辑表达式。

A .与项相或.与项相或 B. B. B. 最小项相或最小项相或最小项相或 C. C. C. 最大项相与最大项相与最大项相与 D. D. D.或项相与或项相与或项相与 5.5.根据反演规则,根据反演规则,()()E DE C C A F ++×+=的反函数为(的反函数为( ))。

A. E )]E D (C C [A F ×++= B. E )E D (C C A F ×++= C. E )E D C C A (F ×++= D. E )(D A F ×++=E C C6.下列四种类型的逻辑门中,可以用( )实现三种基本运算。

)实现三种基本运算。

)实现三种基本运算。

A. A. 与门与门与门B. B. B. 或门或门或门C. C. 非门非门非门D. D. D. 与非门与非门与非门7. 将D 触发器改造成T 触发器,图1所示电路中的虚线框内应是(所示电路中的虚线框内应是( ))。

图1A. A. 或非门或非门或非门B. B. B. 与非门与非门与非门C. C. C. 异或门异或门异或门D. D. D. 同或门同或门同或门8.实现两个四位二进制数相乘的组合电路,应有( )个输出函数。

《机电一体化系统设计》_A-专科 期末考试试题及参考答案

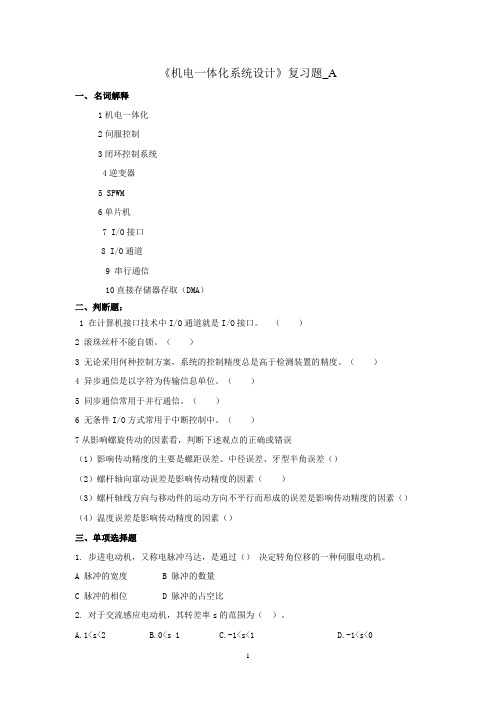

《机电一体化系统设计》复习题_A

一、名词解释

1机电一体化

2伺服控制

3闭环控制系统

4逆变器

5 SPWM

6单片机

7 I/O接口

8 I/O通道

9 串行通信

10直接存储器存取(DMA)

二、判断题:

1 在计算机接口技术中I/O通道就是I/O接口。

()

2 滚珠丝杆不能自锁。

()

3 无论采用何种控制方案,系统的控制精度总是高于检测装置的精度。

()

4 异步通信是以字符为传输信息单位。

()

5 同步通信常用于并行通信。

()

6 无条件I/O方式常用于中断控制中。

()

7从影响螺旋传动的因素看,判断下述观点的正确或错误

(1)影响传动精度的主要是螺距误差、中径误差、牙型半角误差()

(2)螺杆轴向窜动误差是影响传动精度的因素()

(3)螺杆轴线方向与移动件的运动方向不平行而形成的误差是影响传动精度的因素()(4)温度误差是影响传动精度的因素()

三、单项选择题

1. 步进电动机,又称电脉冲马达,是通过()决定转角位移的一种伺服电动机。

A 脉冲的宽度

B 脉冲的数量

C 脉冲的相位

D 脉冲的占空比

2. 对于交流感应电动机,其转差率s的范围为()。

A.1<s<2

B.0<s 1

C.-1<s<1

D.-1<s<0

1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

,考试作弊将带来严重后果!

华南理工大学期末考试

《数字系统设计》试卷

1. 考前请将密封线内各项信息填写清楚;

所有答案请直接答在试卷上(或答题纸上);

.考试形式:开(闭)卷;

本试卷共大题,满分100分,考试时间120分钟

(每小题2分,共16分)

大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理

( C )

CPLD即是现场可编程逻辑器件的英文简称;

CPLD是基于查找表结构的可编程逻辑器件;

早期的CPLD是从GAL的结构扩展而来;

在Altera公司生产的器件中,FLEX10K 系列属CPLD结构;

在VHDL语言中,下列对时钟边沿检测描述中,错误的是( D )

then ...;

then ...;

then ...;

在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确( A )

PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一.

敏感信号参数表中,应列出进程中使用的所有输入信号;

进程由说明部分、结构体部分、和敏感信号参数表三部分组成;

当前进程中声明的信号也可用于其他进程

基于EDA软件的FPGA / CPLD设计流程,以下流程中哪个是正确的:( C )

原理图/HDL文本输入→适配→综合→时序仿真→编程下载→功能仿真→硬件测试

原理图/HDL文本输入→功能仿真→综合→时序仿真→编程下载→适配→硬件测试;

原理图/HDL文本输入→功能仿真→综合→适配→时序仿真→编程下载→硬件测试

原理图/HDL文本输入→适配→时序仿真→编程下载→功能仿真→综合→硬件测试。

关于综合,从输入设计文件到产生编程文件的顺序正确的是:(B)

.逻辑综合→高层次综合→物理综合;

B. 高层次综合→逻辑综合→物理综合;

C. 物理综合→逻辑综合→高层次综合;

D. 高层次综合→逻辑综合→时序综合;

6. 进程中的信号赋值语句,其信号更新是( C )

A. 按顺序完成;

B. 比变量更快完成;

C. 在进程的挂起时完成;

D. 都不对。

7. 下列不属于VHDL基本程序结构是(A)

A..CONFIGURATION定义区

B..ARCHITECTURE定义区

C.USE定义区

D.ENTITY定义区

8.下面对利用原理图输入设计方法进行数字电路系统设计,那一种说法是不正确的_(C)。

A.原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;

B.原理图输入设计方法一般是一种自底向上的设计方法;

C.原理图输入设计方法无法对电路进行功能描述;

D.原理图输入设计方法也可进行层次化设计。

二.简答题(22分)

1. 简述利用EDA技术设计数字系统的特点。

(4分)

2. 什么是信号建立时间?(2分)什么是信号保持时间?(2分)

3. 仿真分为哪几个层次的仿真?(3分)

4. 实验中,对某程序进行编译时出现错误提示:“VHDL Design File “aaa.vhd”must contain an entity of the same name.”(4分)

这是什么原因?如何修改?

5.实验中,如果编译时出现“Can‟t open VHDL “WORK””这样的错误提示。

这又是什么原因,如何修改?(4分)

6.用图示法描述一般时序系统的模型,并作简要说明。

(3分)

三.根据下述VHDL程序段,画出相应的逻辑示意图,并加以简单说明(共10分,每题5分)。

1、Process(clk)

Begin

If (clk =…1‟) then Q<=data; End if;

End process;

2、ENTITY example IS

PORT ( a, b , c, g1, g2a, g2b: IN std_logic;

y: OUT std_logic_vector (7 DOWNTO 0) );

END ENTITY;

ARCHITECTURE behav OF example IS

SIGNAL indata : std_logic_vector(2 DOWNTO 0);

BEGIN

indata<=c & b & a ;

PROCESS( indata, g1, g2a, g2b)

BEGIN

IF (g1='1'and g2a='0' AND g2b='0') THEN

CASE indata IS

WHEN "000"=> y<="11111110";

WHEN "001"=> y<="11111101";

WHEN "010"=> y<="11111011";

WHEN "011"=> y<="11110111";

WHEN "100"=> y<="11101111";

WHEN "101"=> y<="11011111";

WHEN "110"=> y<="10111111";

WHEN "111"=> y<="01111111";

WHEN OTHERS => y<="XXXXXXXX";

END CASE;

ELSE

y<="11111111";

END IF;

END PROCESS;

END behav;

四.综合题(52分)

1. 根据原理图写出相应的VHDL程序:(10分)

2.有一个传输门,根据下述赋值语句和给定的波形,画出对应Z1,Z2,Z3和Z4的波形图。

(4分)

(1)Z1<=Vi ,惯性延时时间为4ns

(2)Z2 <=Vi after 4 ns,惯性延时时间为4ns

(3)Z3 <= TRANSPORT Vi AFTER 3 ns ,惯性延时时间为4ns

(4)Z4<=Vi,传输门的T r=4ns,T f=2ns

3. 根据ASM图画出时序图。

(4分)

4.下面的ASM图含有多少个状态单元,用虚线框加以表示(2分)。

并用双进程状态机描述,请在空白处填入合适语句, 使程序完整正确。

(8分)

Entity traffic is

Port ( reset, clk: in std_logic;

car,timed: in std_logic;

major_green, minor_green:out

std_logic);

end entity;

Architecture asm of traffic is

Begin

seq: process(reset, clk)

begin

end process;

com: process (present_state, car, timed)

begin

start_timer<=…0‟;

case pressent_state is

when G =>

when R=>

major_green<=…0‟;

minor_green<=…1‟;

if (timed=…1‟) then

next_state<=G;

else next_state<=R;

end if ;

end case;

end process ;

End asm;

5.下图所示电路是某数字系统的控制器。

其中Z是系统数据处理器的状态信号;

C1和C2是控制器输出的控作信号。

试画出该控制器的ASM图。

(10分)

6.试编程实现以下功能。

(14分)

如下图所示,某数字系统有三条输入线分别为CLK、CONTROL和DA TA。

有一条输出应答线READY和8位输出总线Z。

从DATA数据线上输入的是8位串行数据。

串行输入数据从低位到高位依次输入。

当系统准备接受新的数据时READY信号置1,并监视输入信号CONTROL。

当CONTROL线在连续二个时钟周期为1时,系统将READY信号恢复为0。

随后的8个时钟由DA TA线依次输入8位数据。

之后一个时钟,再次将READY 信号置1,并将8为数据并行输出到数据总线Z。

《》试卷第 8 页共 8 页。