SystemVerilog语法

systemverilog 可综合 语法

systemverilog 可综合语法-概述说明以及解释1.引言1.1 概述SystemVerilog是一种硬件描述语言,其可综合语法用于描述硬件设计的行为和结构。

可综合语法是指在编写SystemVerilog代码时,能够被综合工具翻译成底层硬件电路,并最终映射到FPGA或ASIC等可编程器件上的语法规则和风格。

因此,可综合语法在硬件设计中起着至关重要的作用。

在硬件设计中,可综合语法使设计工程师能够通过代码描述硬件的功能和结构,包括处理器、逻辑电路、存储器等。

通过使用可综合语法,设计工程师可以更加灵活地实现各种功能和性能要求,同时也能提高设计的可维护性和可重用性。

SystemVerilog的可综合语法特点是其结构化的设计风格,丰富的数据类型和内置的高级语言功能。

与传统的硬件描述语言相比,SystemVerilog提供了更多的抽象层次和编程特性,可以更高效地完成复杂的硬件设计任务。

例如,SystemVerilog支持面向对象的设计方法,可以使用类和对象对设计进行建模和封装。

此外,SystemVerilog还提供了多种数据类型和运算符,使设计工程师可以更方便地处理各种数据和信号。

综上所述,可综合语法在SystemVerilog中具有重要的地位和作用。

通过使用可综合语法,设计工程师能够更加方便地描述和实现各种硬件功能,提高设计的效率和可靠性。

在今后的硬件设计中,可综合语法的应用将更加广泛,并且不断发展和完善,以满足不断变化的设计需求。

1.2 文章结构文章结构部分的内容可以包括以下内容:文章结构的目的是为了给读者提供清晰的导航和理解文章的逻辑框架。

通过合理的结构,读者可以更好地理解文章的目的和内容,并能够有序地阅读和理解整个文档。

本文的结构如下:第一部分是引言部分,用于介绍文章的背景和相关信息。

在引言部分,我们将概述SystemVerilog可综合语法的定义和作用,并介绍本文的结构和目的。

第二部分是正文部分,主要内容是关于SystemVerilog可综合语法的定义和特点。

systemverilog的例子

systemverilog的例子摘要:一、SystemVerilog 简介1.SystemVerilog 的发展历程2.SystemVerilog 在EDA 领域的应用二、SystemVerilog 的基本语法1.数据类型a.整型b.实型c.布尔型d.字符串型2.变量声明与赋值3.运算符与表达式4.控制结构a.顺序结构b.选择结构c.循环结构三、SystemVerilog 的模块与接口1.模块定义2.模块端口声明3.模块实例化4.接口定义与实现四、SystemVerilog 的行为描述1.过程声明2.连续赋值与事件驱动赋值3.函数声明与调用五、SystemVerilog 的仿真与测试1.仿真驱动2.测试序列3.波形查看与分析正文:SystemVerilog 是一种基于Verilog 的硬件描述语言,它被广泛应用于电子设计自动化(EDA)领域,特别是在验证和仿真方面具有显著优势。

本文将简要介绍SystemVerilog 的基本语法、模块与接口、行为描述以及仿真与测试方面的知识。

一、SystemVerilog 简介SystemVerilog 起源于Verilog,是在其基础上进行扩展的一种硬件描述语言。

自1995 年由Cadence 公司推出以来,SystemVerilog 逐渐成为业界标准,被广泛应用于EDA 领域,尤其在验证方面取得了显著成果。

二、SystemVerilog 的基本语法SystemVerilog 提供了丰富的数据类型,包括整型(integer)、实型(real)、布尔型(boolean)和字符串型(string)等。

此外,SystemVerilog 还支持变量声明与赋值、运算符与表达式、以及控制结构(顺序结构、选择结构和循环结构)。

三、SystemVerilog 的模块与接口模块是SystemVerilog 的基本组织单位,用户可以通过模块定义、模块端口声明、模块实例化以及接口定义与实现等方式组织代码。

systemverilog import语法

SystemVerilog是一种硬件描述语言(HDL),它扩展了Verilog HDL并添加了许多新特性。

其中之一就是import语法,它允许用户从其他模块中导入数据和功能。

在本文中,我们将重点介绍SystemVerilog import语法的使用方法和注意事项。

一、import语法概述在SystemVerilog中,import语法用于从其他模块中导入数据和功能,使得代码可以更加模块化和可重用。

通过import语法,我们可以将其他模块中的变量、函数或任务引入当前模块中,无需重复定义,以提高代码的可读性和维护性。

二、import语法的基本用法1. 导入变量使用import语法可以轻松地从其他模块中导入变量。

例如:```verilogimport other_module::*;```这将导入other_module模块中的所有变量,使得它们可以在当前模块中直接使用。

2. 导入函数除了变量,我们还可以使用import语法导入其他模块中的函数。

例如:```verilogimport other_module::func;```这将导入other_module模块中名为func的函数,使得它可以在当前模块中直接调用。

3. 导入任务类似地,import语法也可以用于导入其他模块中的任务。

例如:```verilogimport other_module::task;```这将导入other_module模块中名为task的任务,使得它可以在当前模块中直接调用。

三、import语法的注意事项1. 命名冲突在使用import语法时,需要注意可能出现的命名冲突。

如果当前模块和导入的模块中存在同名的变量、函数或任务,那么在使用时可能会出现歧义,因此需要在导入时进行适当的命名空间管理。

2. 范围限定在使用导入的变量、函数或任务时,需要注意其作用范围。

导入并不意味着可以在任何地方都直接调用,而是需要遵循作用域规则进行访问。

systemverilog条件约束

systemverilog条件约束摘要:1.SystemVerilog 条件约束的概述2.SystemVerilog 条件约束的基本语法3.SystemVerilog 条件约束的应用实例4.SystemVerilog 条件约束的优缺点正文:一、SystemVerilog 条件约束的概述SystemVerilog 是一种用于验证和设计数字电路的硬件描述语言,它是Verilog 的扩展。

在SystemVerilog 中,条件约束是一种重要的概念,可以帮助设计人员对电路行为进行约束和描述。

条件约束主要用于约束信号之间的逻辑关系,可以减少验证时间和提高验证效率。

二、SystemVerilog 条件约束的基本语法SystemVerilog 条件约束的基本语法包括以下几个部分:1.约束声明:使用`constraint`关键字声明一个约束。

2.约束名:约束声明后跟约束名,用于标识约束。

3.条件表达式:表示约束条件的逻辑表达式。

4.约束类型:表示约束的类型,如`POSITIVE`表示肯定约束,`NEGATIVE`表示否定约束。

下面是一个简单的SystemVerilog 条件约束示例:```verilogconstraint c1 (a > b) POSITIVE;```三、SystemVerilog 条件约束的应用实例假设有一个4 位加法器的设计,我们需要约束进位信号`c`在加法操作完成之前保持为0。

可以使用SystemVerilog 条件约束来描述这个要求:```verilogmodule adder_4bit (input [3:0] a,input [3:0] b,output [3:0] sum,output c);constraint c1 (a > b) POSITIVE;constraint c2 (c == 0) POSITIVE;//...其他逻辑实现endmodule```在这个例子中,我们定义了两个约束:`c1`约束表示`a`信号大于`b`信号,`c2`约束表示`c`信号在加法操作完成之前保持为0。

SystemVerilog基本语法总结(上)

SystemVerilog基本语法总结(上)SystemVerilog基本语法总结(上)在总结SV的语法之前,先分享⼀些关于SV的笔试题⽬,这样更显得具有针对性的总结。

a. 验证中,代码覆盖率是指(衡量哪些设计代码在激活触发,⽽哪⼀些则⼀直处于⾮激活状态的统计数据)。

b. SystemVerilog中,从⼀个类派⽣⼀个新类的关键字是(extends)c. SystemVerilog中,仿真器运⾏⼀个⽤例需要建⽴多个⼦线程,这些⼦线程结束时间各不相同,此时需要使⽤(wait fork)语句来等待所有的线程结束d. SystemVerilog中,int_data[]={9,1,8,3,4,4};执⾏data.reverse()操作后,data[]的值应该是({4,4,3,8,1,9})。

执⾏data.rsort()操作后,data[]的值应该是({9,8,4,4,3,1})。

e. SystemVerilog中,使⽤随机函数产⽣随机数赋值给信号a[11:0],随机范围为3~255:($urandom_range(3,255))f. SystemVerilog创建⼀个数据类型为int的动态数组a:(int a[]),创建⼀个数据类型为int的队列b:(int b[$])g. SystemVerilog中,如何在int类型的队列queue的后⾯插⼊数据data:({queue, data})h. SystemVerilog中,rand int src;constrain c_dist{0 :=40, [1:2] :=60};},此时0,1,2的权重分别是多少? 40, 60, 60i. SystemVerilog中,rand bit[5:0]; constraint c_data {data inside {[$:5},[30:$]},那么变量data的取值范围是({[0:5], [30:63]})数据类型l 合并数组和⾮合并数组1)合并数组:存储⽅式是连续的,中间没有闲置空间。

gvim高亮 systemverilog的语法

gvim高亮 systemverilog的语

法

在gVim中高亮SystemVerilog的语法,需要安装一个支持SystemVerilog语法的vim插件。

以下是几个常用的插件:

1. **systemverilog-syntax**: 这是一个简单的SystemVerilog语法

高亮插件,可以在github上找到。

2. **systemverilog-colorscheme**: 这个插件不仅提供了语法高亮,还提供了一组可用的颜色方案。

安装这些插件后,你需要按照以下步骤在gVim中启用它们:

1. 打开gVim,然后进入命令模式(按`:`)。

2. 输入 `:PluginInstall` 然后按回车。

这将自动搜索并安装你设定

的插件。

3. 如果你使用的是systemverilog-colorscheme,你可能还需要在命

令行中输入 `:colorscheme systemverilog` 来选择你喜欢的颜色方案。

以上步骤完成后,你就可以在gVim中看到SystemVerilog的语法高亮了。

注意:如果你在使用这些插件时遇到任何问题,你可能需要检查你的.vimrc文件是否正确配置。

这个文件通常位于你的用户主目录下(例如,在Windows上是C:\Users\YourUsername,在Linux或Mac上是/home/YourUsername)。

在这个文件中,你可以添加或修改设置来定制你的gVim环境。

system verilog 语法

system verilog 语法

使用System Verilog进行硬件设计是一项复杂而充满挑战的任务。

在这个语言中,我们可以描述数字逻辑电路的行为和结构,并对其进行仿真和验证。

System Verilog提供了丰富的语法和特性,使我们能够轻松地设计复杂的电路,并确保其正确性。

在System Verilog中,我们可以使用模块来组织我们的设计。

一个模块代表一个独立的功能单元,可以由多个输入和输出端口组成。

通过连接不同的模块,我们可以构建出整个系统。

每个模块可以包含多个时钟域,以及各种组合逻辑和时序逻辑。

我们可以使用always块来描述时序逻辑,使用if-else语句来描述组合逻辑。

System Verilog还提供了一些方便的特性,如任务和函数。

任务可以在仿真过程中执行一些特定的操作,而函数可以返回一个值。

这些特性可以让我们的设计更加模块化和可重用。

除了描述电路结构和行为外,System Verilog还具有强大的验证功能。

我们可以使用断言来验证设计的正确性,并使用cover语句来检测设计中的覆盖率。

这些功能可以帮助我们发现和解决潜在的问题,确保设计的可靠性。

总的来说,System Verilog是一种强大而灵活的硬件设计语言。

它提供了丰富的语法和特性,使我们能够轻松地描述和验证复杂的数字逻辑电路。

通过合理运用这些特性,我们可以设计出高效、可靠

的硬件系统。

虽然学习和掌握System Verilog可能需要一些时间和经验,但它无疑是现代硬件设计中不可或缺的工具之一。

systemverilog语法和验证相关流程

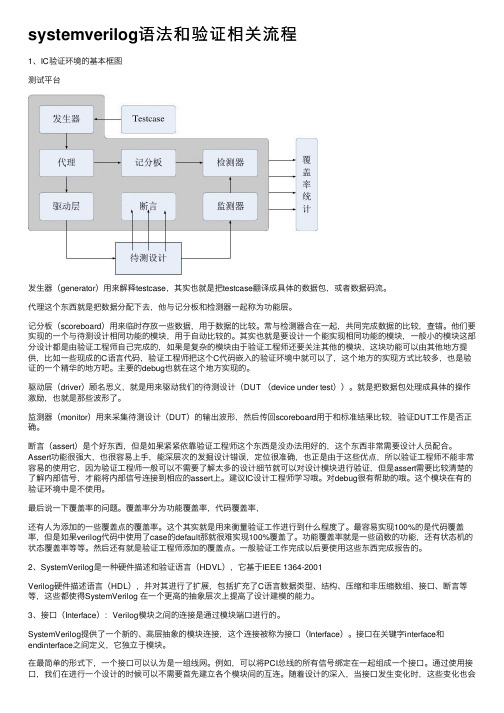

systemverilog语法和验证相关流程1、IC验证环境的基本框图测试平台发⽣器(generator)⽤来解释testcase,其实也就是把testcase翻译成具体的数据包,或者数据码流。

代理这个东西就是把数据分配下去,他与记分板和检测器⼀起称为功能层。

记分板(scoreboard)⽤来临时存放⼀些数据,⽤于数据的⽐较。

常与检测器合在⼀起,共同完成数据的⽐较,查错。

他们要实现的⼀个与待测设计相同功能的模块,⽤于⾃动⽐较的。

其实也就是要设计⼀个能实现相同功能的模块,⼀般⼩的模块这部分设计都是由验证⼯程师⾃⼰完成的,如果是复杂的模块由于验证⼯程师还要关注其他的模块,这块功能可以由其他地⽅提供,⽐如⼀些现成的C语⾔代码,验证⼯程师把这个C代码嵌⼊的验证环境中就可以了,这个地⽅的实现⽅式⽐较多,也是验证的⼀个精华的地⽅吧。

主要的debug也就在这个地⽅实现的。

驱动层(driver)顾名思义,就是⽤来驱动我们的待测设计(DUT (device under test))。

就是把数据包处理成具体的操作激励,也就是那些波形了。

监测器(monitor)⽤来采集待测设计(DUT)的输出波形,然后传回scoreboard⽤于和标准结果⽐较,验证DUT⼯作是否正确。

断⾔(assert)是个好东西,但是如果紧紧依靠验证⼯程师这个东西是没办法⽤好的,这个东西⾮常需要设计⼈员配合。

Assert功能很强⼤,也很容易上⼿,能深层次的发掘设计错误,定位很准确,也正是由于这些优点,所以验证⼯程师不能⾮常容易的使⽤它,因为验证⼯程师⼀般可以不需要了解太多的设计细节就可以对设计模块进⾏验证,但是assert需要⽐较清楚的了解内部信号,才能将内部信号连接到相应的assert上。

建议IC设计⼯程师学习哦。

对debug很有帮助的哦。

这个模块在有的验证环境中是不使⽤。

最后说⼀下覆盖率的问题。

覆盖率分为功能覆盖率,代码覆盖率,还有⼈为添加的⼀些覆盖点的覆盖率。

systemverilog assertion语法

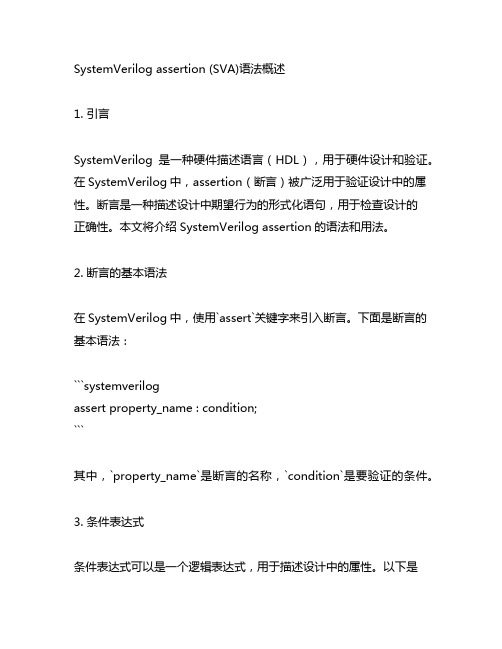

SystemVerilog assertion (SVA)语法概述1. 引言SystemVerilog是一种硬件描述语言(HDL),用于硬件设计和验证。

在SystemVerilog中,assertion(断言)被广泛用于验证设计中的属性。

断言是一种描述设计中期望行为的形式化语句,用于检查设计的正确性。

本文将介绍SystemVerilog assertion的语法和用法。

2. 断言的基本语法在SystemVerilog中,使用`assert`关键字来引入断言。

下面是断言的基本语法:```systemverilogassert property_name : condition;```其中,`property_name`是断言的名称,`condition`是要验证的条件。

3. 条件表达式条件表达式可以是一个逻辑表达式,用于描述设计中的属性。

以下是一个简单的条件表达式:```systemveriloga b |-> c```上面的表达式表示当`a`和`b`同时为真时,`c`必须为真。

4. 断言属性在断言中,可以使用多种属性来描述设计中的行为。

下面是一些常见的断言属性:- ``:指定条件的时序性质。

`(posedge clk)`表示在时钟上升沿检查条件。

- `disable iff`:指定在某些情况下禁用断言。

`disable iff (reset_n == 0)`表示当复位信号为低电平时禁用断言。

- `strong`和`weak`:指定断言的强度。

`strong`断言必须被满足,而`weak`断言可以被忽略。

5. 示例下面是一个使用SystemVerilog assertion的简单示例:```systemverilogmodule dut (input logic a,input logic b,output logic c);assert property_name : (a b) |-> c;endmodule```在上面的例子中,我们定义了一个名为`property_name`的断言,要求当`a`和`b`同时为真时,`c`必须为真。

systemverilog 任务 语法

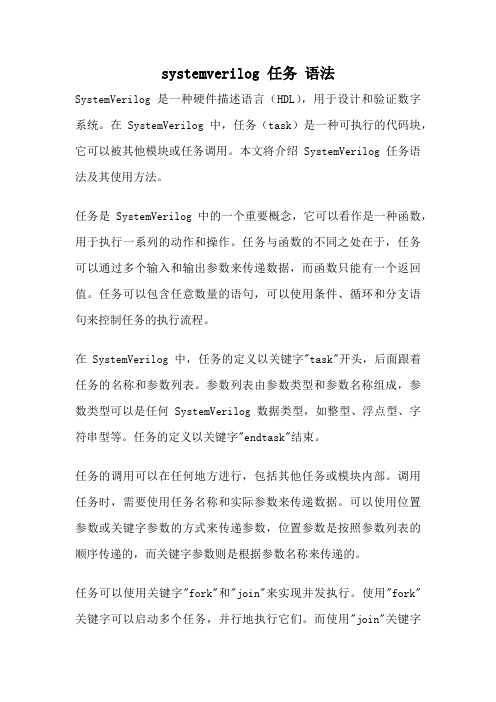

systemverilog 任务语法SystemVerilog是一种硬件描述语言(HDL),用于设计和验证数字系统。

在SystemVerilog中,任务(task)是一种可执行的代码块,它可以被其他模块或任务调用。

本文将介绍SystemVerilog任务语法及其使用方法。

任务是SystemVerilog中的一个重要概念,它可以看作是一种函数,用于执行一系列的动作和操作。

任务与函数的不同之处在于,任务可以通过多个输入和输出参数来传递数据,而函数只能有一个返回值。

任务可以包含任意数量的语句,可以使用条件、循环和分支语句来控制任务的执行流程。

在SystemVerilog中,任务的定义以关键字"task"开头,后面跟着任务的名称和参数列表。

参数列表由参数类型和参数名称组成,参数类型可以是任何SystemVerilog数据类型,如整型、浮点型、字符串型等。

任务的定义以关键字"endtask"结束。

任务的调用可以在任何地方进行,包括其他任务或模块内部。

调用任务时,需要使用任务名称和实际参数来传递数据。

可以使用位置参数或关键字参数的方式来传递参数,位置参数是按照参数列表的顺序传递的,而关键字参数则是根据参数名称来传递的。

任务可以使用关键字"fork"和"join"来实现并发执行。

使用"fork"关键字可以启动多个任务,并行地执行它们。

而使用"join"关键字可以等待所有启动的任务执行完毕后再继续执行下面的语句。

在任务内部,可以使用关键字"disable"来终止任务的执行。

"disable"后面可以跟一个任务名称,表示终止指定的任务;也可以不跟任务名称,表示终止当前的任务。

任务还可以使用关键字"automatic"来声明自动任务。

自动任务的局部变量在每次调用时都会被重新初始化,而不会保留上一次调用的值。

systemverilog constraint 语法

systemverilog constraint 语法SystemVerilog 是一种硬件描述和验证语言,主要用于电子设计自动化 (EDA) 和集成电路设计。

约束是 SystemVerilog 中的一个重要概念,用于定义和限制变量、数组和结构体的值。

以下是 SystemVerilog 约束的基本语法:```systemverilogconstraint constraint_name {expression;}```其中,`constraint_name` 是约束的名称,`expression` 是约束的条件或表达式。

例如,以下是一个简单的约束示例,用于限制一个整数的范围:```systemverilogconstraint integer_range {variable_name > 0 && variable_name < 10;}```在这个示例中,`integer_range` 是约束的名称,`variable_name > 0 && variable_name < 10` 是约束的条件,表示 `variable_name` 的值必须在 1 到 9 之间。

SystemVerilog 还支持一些内置的约束函数,例如 `rand` 和`randc`,用于生成随机数。

例如,以下是一个使用 `rand` 函数的约束示例:```systemverilogconstraint random_num {variable_name = rand();}```在这个示例中,`random_num` 是约束的名称,`variable_name = rand();` 是约束的条件,表示 `variable_name` 的值应该是一个随机数。

需要注意的是,约束可以是静态的或动态的。

静态约束在编译时进行验证,而动态约束在运行时进行验证。

systemverilog 语法

systemverilog 语法SystemVerilog是一个硬件描述语言(HDL),它具有一些基本语法结构,与其他编程语言并无差异。

本文将介绍常见的SystemVerilog 语法。

1. 模块声明SystemVerilog使用模块来描述电路的结构,其中包含了输入端口、输出端口以及内部信号。

下面是一个简单的模块声明示例:module my_module(input input_port, output output_port);// Verilog代码在这里endmodule2. 变量声明变量可分为多种类型:- 整型变量(int):用于整数值。

- 浮点型变量(real):用于浮点值。

- 位变量(bit):只能存储0和1。

- 向量型变量(vector):用于存储多位的值。

下面是声明一个整型变量的示例:int my_variable;3. Control FlowSystemVerilog支持条件和循环语句,使得描述一些分支判断或循环的电路的时候变得更加直观。

- if/else语句:if语句用于条件分支,else语句用于指定当条件不满足时的操作。

下面是if/else语句的基本形式:if (condition) begin// 操作一endelse begin// 操作二end- for循环:for循环让您可以重复执行某些操作,直到满足指定的条件。

下面是for循环语句的一般形式:for(initialization, condition, increment) begin// 操作end其中,初始化指定循环计数器的值,条件指定循环何时结束,增量指定每次循环计数器自增的值。

4. 综合测试(assertions)综合测试是一种在设计中添加的指令,通过检查某些条件是否满足来确保设计的正确性。

可以使用综合测试指令对电路进行严格测试。

下面是一个简单的综合测试指令:assert(signal1 == signal2) else $display("Error");这里的断言语句表示,如果信号signal1不等于信号signal2,则显示错误消息。

systemverilog语法

systemverilog语法

SystemVerilog是一种多范式的语言,它集成了现有的硬件描述语言Verilog和面向

对象的库描述语言SystemC,旨在提供更加强大的抽象级别和更全面的验证,以满足从晶

圆级到软件级到上层应用之间完全的验证问题。

SystemVerilog功能上的增强有助于降低编码工作中的复杂度,从而提高系统编码和

验证效率。

该有限状态机概念可以将所有有限状态机分组矩阵描述为一组引用有限状态机

模块,这样可以更轻松地扩展和完善复杂系统的应用模式。

SystemVerilog还提供了显式和隐式参量,及类似元组、数组和结构之类的数据类型,可以更高效地存储数据,从而提高数据模型的稳定性。

语言的类库模块可以帮助简化系统

编码,消除各种模块、器件和连接设计之间的重复编码工作。

SystemVerilog还提供了针对多任务系统的同步和异步的系统模型,可以帮助节省进

行复杂验证的编码和调试时间,从而减少系统开发周期。

SystemVerilog这一语言的特点

也使它在软件建模和验证上非常有用,有助于模拟所有软件程序的性能,从而提高软件开

发效率。

system verilog语法总结

system verilog语法总结以下是SystemVerilog语法的总结:1. 模块:SystemVerilog程序由一个或多个模块组成,模块是设计的构建块。

模块可以是分层的,可以包含其他模块或模块实例。

2. 端口:模块可以有输入、输出或双向端口。

端口声明指定传入或传出模块的信号的数据类型、方向和大小(如果适用)。

3. 数据类型:SystemVerilog支持各种数据类型,包括整数、实数、布尔值和字符串。

它还提供了数组和结构等复合类型。

4. 变量:在SystemVerilog中,可以使用"reg"或"logic"关键字声明变量。

它们可以是任何支持的数据类型,并且可以使用过程语句赋值。

5. 过程块:SystemVerilog提供了类似"always"、"initial"和"task/function"的过程块。

这些块允许您使用过程语句(如if-else、for循环、while循环等)来定义设计的行为。

6. 连续赋值:连续赋值用于描述模块内的组合逻辑。

它们使用assign关键字,并指定确定左侧信号值的右侧表达式。

7. 运算符:SystemVerilog支持各种运算符,包括算术、位、逻辑、比较和连接运算符。

这些运算符允许您对信号和变量进行操作。

8. 行为建模:SystemVerilog允许使用过程块、任务和函数进行行为建模。

这使您能够使用高级编程结构描述设计的功能。

9. 测试台:测试台是用于验证设计功能的单独模块或一组模块。

它生成输入刺激并监视输出,以确保正确操作。

10. 验证构造:SystemVerilog提供了各种验证构造,如断言、覆盖属性和带有随机刺激生成的测试台。

这些构造有助于验证设计的正确性。

请注意,这只是SystemVerilog语法的简要总结。

根据您的具体要求和用例,还有许多更多的功能和细节可以探索。

systemverilog 断开端口信号连接的语法

systemverilog 断开端口信号连接的语法

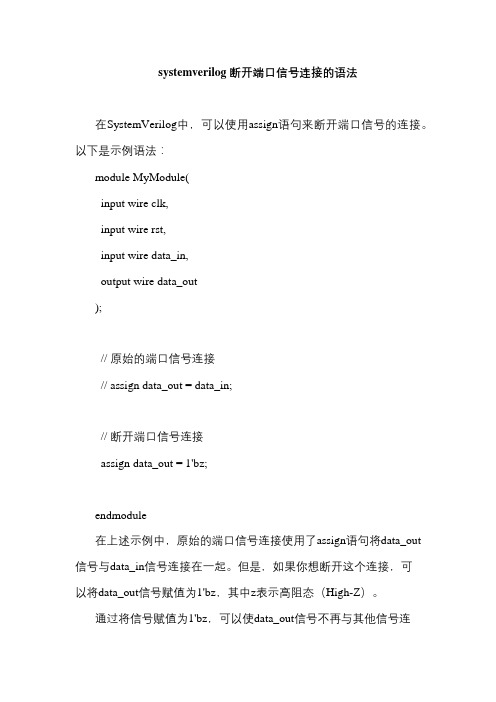

在SystemVerilog中,可以使用assign语句来断开端口信号的连接。

以下是示例语法:

module MyModule(

input wire clk,

input wire rst,

input wire data_in,

output wire data_out

);

// 原始的端口信号连接

// assign data_out = data_in;

// 断开端口信号连接

assign data_out = 1'bz;

endmodule

在上述示例中,原始的端口信号连接使用了assign语句将data_out 信号与data_in信号连接在一起。

但是,如果你想断开这个连接,可

以将data_out信号赋值为1'bz,其中z表示高阻态(High-Z)。

通过将信号赋值为1'bz,可以使data_out信号不再与其他信号连

接,达到断开连接的效果。

需要注意的是,断开端口信号连接的语法可能因具体的应用和设计需求而有所不同。

以上示例仅供参考,实际使用时请根据具体情况进行适当的调整。

system verilog 断言语法

SystemVerilog断言语法指的是在SystemVerilog中使用断言进行验证和调试设计的语法规则。

断言是一种在设计过程中用来描述期望行为或者不期望行为的一种语言工具,通过断言可以对设计进行形式验证,帮助设计人员及时发现设计缺陷,提高设计的可靠性和稳定性。

在SystemVerilog中,断言语法的使用对于提高设计的质量和可维护性非常重要。

一、assert语句在SystemVerilog中,使用assert语句来定义断言。

assert语句是一种在设计中用来描述预期行为或不期望行为的语句。

它采用布尔表达式来描述期望的行为,如果这个布尔表达式为真,则断言通过,如果为假,则会触发一个错误。

assert语句的基本语法如下:assert(property_expression) else $error ("message");其中,property_expression是一个布尔表达式,用来描述预期的行为;message是在断言失败时会打印的错误信息。

二、sequence语句在SystemVerilog中,还可以使用sequence语句来定义一系列时序逻辑,并通过assert语句使用这些时序逻辑来进行断言验证。

sequence语句的基本语法如下:sequence sequence_name;statement1;statement2;...endsequence其中,sequence_name为时序逻辑的名称,statement1、statement2等为时序逻辑的具体内容。

三、property语句property语句用于定义属性,描述一系列信号之间的关系。

它可以用来描述一些复杂的时序逻辑,例如时序关系、状态机转移等。

property语句的基本语法如下:property property_name;(expression1 |-> expression2);endproperty其中,property_name为属性的名称,expression1和expression2为属性的具体描述。

systemverilog $system()用法

systemverilog $system()用法在SystemVerilog中,$system()是一个系统任务,用于执行外部系统命令。

它接受一个字符串参数,表示要执行的系统命令,并且可以返回一个整数值,表示命令的执行结果。

$system()的语法如下:$system("command");其中,"command"是要执行的系统命令。

这个命令可以是任何可以在命令行中执行的命令,比如Linux上的shell命令或Windows上的批处理命令。

$system()任务会将命令发送到系统,然后等待命令执行完毕。

它可以用于执行外部工具、调用脚本文件或者进行任何需要调用系统命令的操作。

$system()的返回值是一个整数,表示命令的执行结果。

返回值的具体含义是系统特定的,可以是一个错误码、返回状态或其他与系统相关的信息。

一般来说,返回值为0表示命令执行成功,非零值表示命令执行失败或出现错误。

下面是一个简单的例子,演示了如何使用$system()来执行外部系统命令,并获取命令的执行结果:module example;reg [31:0] result;initial beginresult = $system("ls -l");$display("Result: %d", result);endendmodule在上面的例子中,$system("ls -l")命令用于执行"ls -l",即列出当前目录下的文件和子目录的详细信息。

通过$result变量获取$system()的返回值,并使用$display()任务打印出来。

请注意,在使用$system()任务时要谨慎,确保执行的命令是安全的,并且不会对系统和设计环境造成任何损害。

systemverilog语法 try_get()

systemverilog语法 try_get()

systemverilog语法中,try_get()方法用于非阻塞地获取一个信

号的值,并将其保存在指定的变量中。

如果信号当前没有变化,则返回0,否则返回1,并将该信号的当前值保存在指定变量中。

try_get()方法的用法示例如下:

```

logic my_signal;

if (my_signal.try_get()) //非阻塞地获取my_signal信号的值并判断是否有变化

$display("The value of my_signal is %d", my_signal); //输出

my_signal信号的值

```

有关try_get()方法的其他说明包括:

- 可以与时序控制语句(如wait)一起使用。

- 如果信号当前没有变化,则try_get()方法不会造成延迟。

- 如果你的仿真工具不支持try_get()方法,那么可以使用$sample()或者$changed()方法来达到类似的效果。

这些是关于try_get()方法的相关参考内容。

systemverilog正则表达式

systemverilog正则表达式(实用版)目录1.SystemVerilog 正则表达式的概述2.SystemVerilog 正则表达式的基本语法3.SystemVerilog 正则表达式的应用实例4.SystemVerilog 正则表达式的优缺点正文【1.SystemVerilog 正则表达式的概述】SystemVerilog 是一种硬件描述语言,主要用于设计和验证数字电路和模拟混合信号电路。

在 SystemVerilog 中,正则表达式是一种字符串操作工具,可以用来检查和处理字符串。

正则表达式在 SystemVerilog 中具有广泛的应用,例如,用来验证字符串是否符合特定的格式或者提取字符串中的特定信息。

【2.SystemVerilog 正则表达式的基本语法】SystemVerilog 正则表达式的基本语法包括以下几个部分:- 字符类:用于匹配某一类字符- [abc]:匹配 a、b 或 c- [^abc]:匹配除 a、b、c 之外的任意字符- [a-zA-Z]:匹配所有英文字母- d:匹配数字,等价于 [0-9]- D:匹配非数字,等价于 [^0-9]- s:匹配空白字符,包括空格、制表符和换行符- S:匹配非空白字符- w:匹配单词字符,包括字母、数字和下划线- W:匹配非单词字符- 量词:用于指定字符或字符类出现的次数-?:出现 0 次或 1 次- *:出现 0 次或多次- +:出现 1 次或多次- {n}:出现 n 次- {n,}:出现 n 次或多次- {n,m}:出现 n 到 m 次- 边界匹配符:用于指定匹配的位置- ^:匹配字符串的开头- $:匹配字符串的结尾- b:匹配单词边界- B:匹配非单词边界- 分组和捕获:用于将正则表达式的一部分组合在一起,以便进行特定操作- (pattern):匹配 pattern 并捕获结果,可以通过回溯变量获取 - (?:pattern):匹配 pattern 但不捕获结果- 反斜杠:用于转义特殊字符或者表示反斜杠本身- :转义特殊字符,例如表示换行符,t表示制表符【3.SystemVerilog 正则表达式的应用实例】SystemVerilog 正则表达式在实际应用中可以用来完成各种任务,例如,验证一个字符串是否符合特定的格式:```assert (strcmp("hello, world!", "hello, world!") == 0);```在这个例子中,我们使用 strcmp 函数来比较两个字符串是否相等,如果相等则说明该字符串符合特定的格式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

11 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types -

User defined types

User defined types are same as found in C language or others. A type can be used before it is defined, provided it is first identified as a type by an empty typedef. Syntax

– can be accessed as pack1.d <= ‘b0;

– the whole struct can be resetted with pack1 <= ‘b0;

• unpacked struct (no “packed” keyword) allow only acces through the named fields (pack1.d <=‘b0);

New features

C type data types like int, typedef, struct, union, enum. Dynamic data types : struct, classes, dynamic queues, dynamic arrays.

New operators and built in methods.

• equivalent to a packed array subdivided into named fields:

– example: 48 bit packed array – can be accessed as pack1[15:0] <= ‘b0; – can access pack1[9:4] <= 15;

dynamic

bit [3:0] nibble[]; integer mem[]; Method new[], size(), delete()

and associative arrays

bit[20:0] array_b[string]; event ev_array[myClass]; Method: num(), delete(); exists()... reduced memory usage, built-in support for searching and sorting

o struct, union, and class data types.

o void data type. o null data type.

o arrays, queue, associative array, dynamic array

4 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Intro_to_SystemVerilog

Amy Wu 12/2013

1 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Content

Intro Data Types Processes SystemVerilog Classes SystemVerilog Interfaces SystemVerilog Program Block SystemVerilog Clocking Random Constraints Functional coverage

o typedef data_type type_identifier variable_dimension o typedef interface_instance_identifier type_identifier o typedef [ enum | struct | union | class ] type_identifier

packed : A packed structure consists of bit fields, which

are packed together in memory without gaps. unpacked : An unpacked structure has an

implementation-dependent packing, normally matching

6 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types -

chandle data types

chandle data type is used for storing the pointer, while using Direct programming

interface(DPI).

7 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types -

string data types -1

string data type is used for storing strings. the size of string data is dynamic. string data types come with build in methods

8 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types String Operators

string data types -2

9 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Enhanced flow control like, foreach, return, break, continue. Semaphores, mailboxes, event extensions. classes for object oriented programming. Assertions. Coverage.

Data Types build in methods

string data types -3

10 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types -

event data types

Syntax : event variable_name [= initial_value] Initial value can be another event variable, And can be null if you want variable_name to be triggered always.

the C compiler. tagged : An Tagged union is a type-checked union.

13 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types -

Hale Waihona Puke Structures and unions types

12 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types found in C language.

Structures and unions types

Structure and union declarations types are same as that

14 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

Data Types - new data types

Queues,

byte q1[$]; // A queue of bytes string names[$] = { "Bob" }; // A queue of strings with one element Method: size(), delete(), pop_front(), pop_back()…..

Data Types -

void and null data values

void and null types value are same as in C language o void is used in functions to return no value. o null is used for comparing a variable to empty value, say comparing a string to empty string.

o reg : User defined vector types.

o wire : User defined vector types.

o integer : 32-bit signed integer.

o time : 64-bit unsigned integer.

o

5 | Presentation Title | December 25, 2018 | AMD SRDC Confidential

15 | Presentation Title | December 25, 2018 | AMD SRDC Confidential