Chipscope实例教程

ChipScope Pro实例教程

ChipScope Pro实例教程宋存杰1. ChipScope Pro简介ChipScope Pro的主要功能是通过JTAG口、在线实时地读出FPGA的内部信号。

基本原理是利用FPGA中未使用的BlockRAM,根据用户设定的触发条件将信号实时地保存到这些BlockRAM中,然后通过JTAG口传送到PC机,显示出时序波形。

一般来说,ChipScope Pro在工作时需要在用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrated Logic Analyzer core),提供触发和跟踪捕获的功能;二是集成控制器核(ICON core,Integrated Controller core),负责ILA核和边界扫描端口的通信,一个ICON核可以连接1~15个ILA核。

ChipScope Pro工具箱包含3个工具:ChipScope Pro Core Generator(核生成器)、ChipScope Pro Core Inserter(核插入器)和ChipScope Pro Analyzer(分析器)。

ChipScope Pro Core Generator的作用是根据设定条件生成在线逻辑分析仪的IP核,包括ICON核、ILA核、ILA/ATC2核和IBA/OPB核等,设计人员在原HDL代码中实例化这些核,然后进行布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定触发条件、观察信号波形。

ChipScope Pro Core Inserter除了不能生成IBA/OPB核和ILA/ATC2核以外,功能与ChipScope Pro Core Generator类似,可以生成ICON核和ILA核,但是它能自动完成在设计网表中插入这些核的工作,不用手工在HDL代码中实例化,在实际工作中用得最多。

下图为ChipScope的两种使用流程图,左侧为使用ChipScope Pro Core Generator流程。

ise_chipscope使用实例详细

ise_chipscope使⽤实例详细在ISE 设计流程中使⽤ChipScope Pro 内核的实例-修正版这⼀节介绍⼀个在ISE设计中使⽤ChipScope Pro Core Inserter和ChipScope Pro Analyzer的例⼦。

1. 在ISE中建⽴⼀个⼯程count4,选择相应的器件,添加代码count4.v,count4.v是⼀个简单的4位记数器,其代码如下:module count4(out,reset,clk);output[3:0] out;input reset,clk;reg[3:0] out;always @(posedge clk)beginif (reset) out<=0;else out<=out+1;endendmodule图5.1 新建⼀个⼯程图5.2 选择器件图5.3 添加代码到⼯程中图5.4 ⼯程概况2.设置管脚约束图5.5 添加管脚约束3.综合注意:综合的时候要保留设计层次,XST缺省设置是将设计打平以取得好的综合效果,Synplifcity缺省设置是保留设计层次。

本例是⽤XST综合的所以需要修改综合设置图5.6 设置 keep hierarchy4. Translate注意:在ISE中做Translate的时候需要设置Preserve Hierarchy on Sub module. 缺省情况下为不设置.图5.7 设置 Preserve Hierarchy on Sub module图5.8 插⼊Core 前的ISE ⼯程窗⼝⽣成⽹表5.通过ChipScope Pro Core Inserter插⼊内核,具体步骤和设置详见第3部分////////////////////////////////////////////////////////////////////// ChipScope Pro Core Inserter的使⽤上⾯介绍的⽅法是使⽤ChipScope Pro Core Generator 产⽣内核,然后在设计中作为元件调⽤,然⽽,我们也可以使⽤ChipScope Pro Core Inserter 直接将内核植⼊EDIF 或者XST ⽹表。

chipscope

1、首先按平时一样用chipscope对数据进行采样!不过为了方便以后导入matlab查看,这里我们建议查

看采样信号要使用bus总线方式,这个不多说了,应该都会的。

2、点击file->export 选项,弹出一个export signals窗口,format选择ascii选项,signals to

Export选择bus plot buses,core默认就行。

3、点击export按钮,保存为.prn后缀文件。

如username.prn.

4、打开matlab软件,我们可以直接打开这个.prn文件进行编辑和查看(如果需要),也可以使用matla

b命令

xlLoadChipScopeData(‘username.prn’);

把之前chipscope导出的bus总线数据导入为malab空间变量,并且空间变量的名字和在chipscope 中bus总线对应信号线的名字一样的。

呵呵,信号变量有了,以后就可以方便进行相关信号分析处理了。

chipscope例程

ChipScope例程ISE13.1简介FPGA的在线调试,一般是在FPGA中嵌入一个类似于逻辑分析仪的模块,在满足触发条件时,对需观测的信号进行采集,并通过JTAG线缆将存储的波形上传至计算机,供调试人员检查。

Xilinx在线调试工具为ChipScope,Altera为SignalTap。

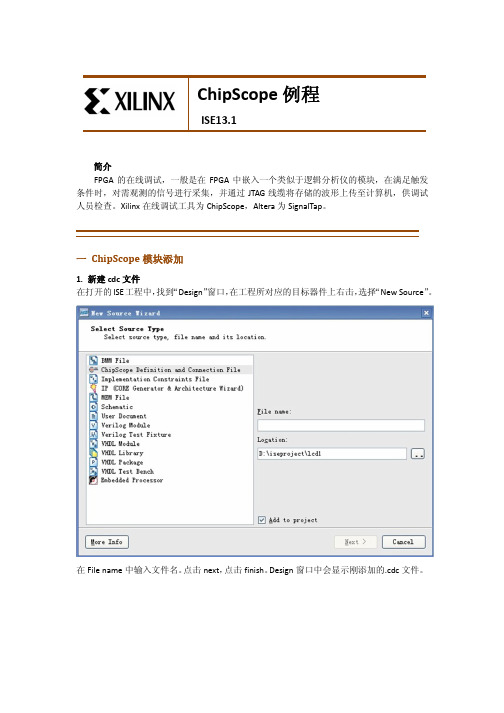

一ChipScope模块添加1. 新建cdc文件在打开的ISE工程中,找到“Design”窗口,在工程所对应的目标器件上右击,选择“New Source”。

在File name中输入文件名。

点击next,点击finish。

Design窗口中会显示刚添加的.cdc文件。

双击*.cdc。

进入编辑界面。

在新的界面中点击next。

在上图所示的界面中,选中“Trigger Parameters”窗口,然后在“Number of Input Ports”后面的下拉列表中选择触发通道的个数。

简单起见这里设为1。

在TRIG0对应的选项中选择位宽(Trigger Width)及触发类型(Match Type)。

点击“Next”,或是中“Capture Parameters”窗口。

在上图中,勾选需要用到的Trigger Port,设置采样深度。

点击“Next”,或是中“Net Connections”窗口。

为clock通道和Trigger通道指定网络标号。

在上图中双击CLOCK PORT。

在“Net Name”对应的列表中找到待指定的信号,也可以在Pattern中输入*clk*,点击Fitter 找到clk信号,选中该信号,然后点击右侧的“make connections”按钮,则该信号便与时钟通道对应起来。

点击OK。

添加成功后会在Net Connection中显示。

双击Trigger Ports。

用相同的方法添加信号。

注意右上角的Net Selection这时要选中Trigger/Data Signals。

所有通道的信号均定完成之后,点击菜单栏的“File”->“Save”,或是在工具栏找到快捷图标,单击保存cdc文件,然后关闭此窗口。

ise_chipscope使用实例

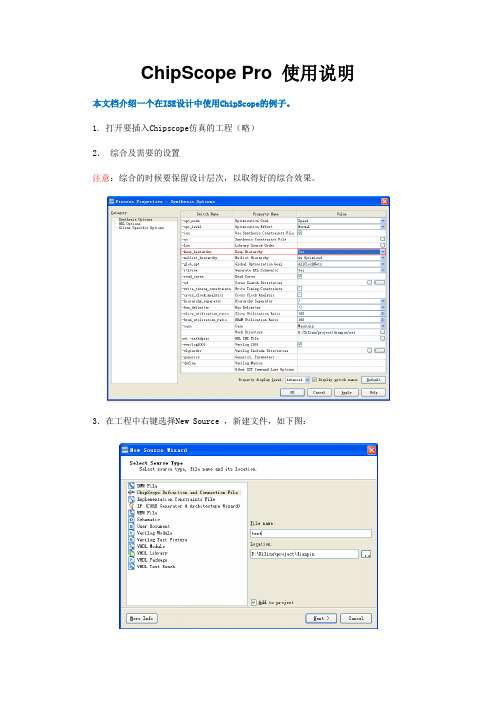

ChipScope Pro 使用说明本文档介绍一个在ISE设计中使用ChipScope的例子。

1. 打开要插入Chipscope仿真的工程(略)2.综合及需要的设置注意:综合的时候要保留设计层次,以取得好的综合效果。

3.在工程中右键选择New Source ,新建文件,如下图:4.双击新建的.cdc文件,启动ChipScope。

1、在DEVICE界面,点击NEXT2、在ICON界面,点击NEXT3、在ILA界面分为3页,如下第一页,在Trigger Width栏填入要触发的数据位宽。

NEXT第二页,Data Depth选择采样深度;Data Same As Trigger为触发条件与采样数据是否相同。

Next第三页,添加时钟触发信号及采样信号。

双击红色CLOCK PORT,选择触发信号关联的时钟信号。

同样双击TRIGGER PORTS关联触发信号(若触发信号TIGGER跟采样信号DATA SIGNALS不同,则分开关联信号)(注,查找信号时,可试用Fitter工具,在Fitter中可以使用通配符*,代表任意个任意字符,帮助快速查找)5.在关联完成所有信号后,点击OK返回。

点击Return to Project Navigator返回ISE。

6.双击Process窗口中的Analyze Design Using Chipscope直到弹出ChipsScpoe工具。

7.选中器件,右键Configure,弹出如下窗口,点击OK。

下载程序后,双击左侧边框打开各窗口。

(注:上方黑色三角表示开始触发采集,黑色方块i代表停止采集,Ti代表无需触发条件满足立即采集。

)系数计算方法:例如,cut_x总线为16位宽,1位符号位、1位整数位、14位小数位,则,试用计算器计算为0.00006103515625。

幅度偏移不需要改,显示精度一般2-4左系数为12右即可。

将所有需要修改格式的总线修改后,双击Bus Plot可打开总线绘图,查看总线波形。

ChipScope的用法

ChipScope的用法实验的背景:用ChipScope检测AD的输出是否正确。

实验板为JNS100,Xilinx版本为12.1,信号源为东方联星信号源,只输出单载波(1575.42Mhz)。

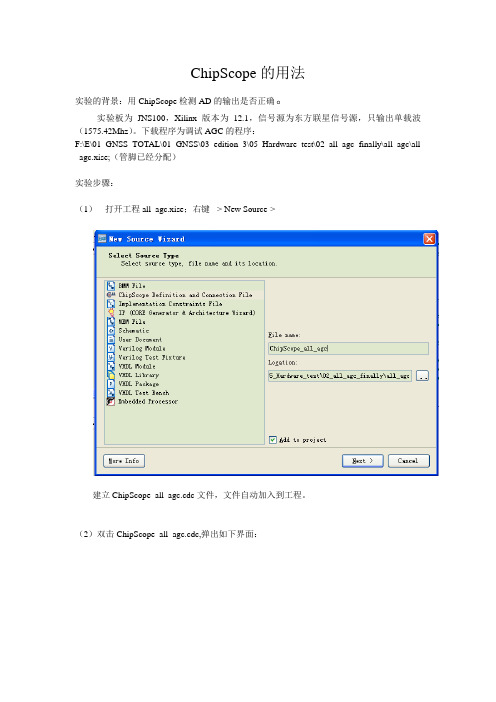

下载程序为调试AGC的程序:F:\E\01_GNSS_TOTAL\01_GNSS\03_edition_3\05_Hardware_test\02_all_agc_finally\all_agc\all _agc.xise;(管脚已经分配)实验步骤:(1)打开工程all_agc.xise;右键-> New Source->建立ChipScope_all_agc.cdc文件,文件自动加入到工程。

(2)双击ChipScope_all_agc.cdc,弹出如下界面:(3)点击Next(4)点击New ILA(Integrated Logic Analyzer Pro cores),进入如下界面:我们在此界面中可以设置;即为所要查看的信号的数目,在此我设置为4,分别用来查看:半秒计数闪灯变量j;红灯闪烁时的电平r_light;GPS的AD输出的8位采样数值:(~(ad_data_gps[7]),ad_data_gps[6:0],注:因为AD输出为偏移二进制码,所以最高位要取反才能转换为二进制补码);GLN的AD输出的8位采样数值。

设置完后界面如下;将产生4个TRIG;再分别设置每个变量的位数(j为25位;r_light为1位,GPS,GLN 的AD输出分别为8位):如下图:(5)点击NEXT:(6)继续点击NEXT,进入信号分配界面:(7)点击,为每个变量建立与实际信号直接的链接关系,如下图:A:首先建立时钟的链接:左键点击NetName中的DSP_AECLKIN_OBUF,然后点击右下角的,即建立起了实际信号与clock之间的连接关系。

B:点击右上角的按钮,进入所需查看的信号的链接。

有图可见:TP0为信号j对应的列表,TP1为信号r_light对应的列表,TP2为信号GPS的AD输出的8位采样数值对应的列表,TP3为信号GLN的AD输出的8位采样数值对应的列表,如下图:(9)分别建立各个信号间的链接关系,最后结果如下所示:(10)分配完之后点击OK返回可以看到,Net Connections中的信号已经有原来的红色变为了黑色,这说明说有的网络都已经建立起了链接关系。

步骤详细-ISE中使用chipscope

说明:核插入器不仅能产生常用的核,还能将其自动插入设计网表,不需要手工在HDL代码中例化,它在很多场合替代了核生成器的功能。

在ISE中直接调用ChipScope的应用实例。

在XC3S500E芯片上实现一个计数器实例,详细介绍如何在ISE中新建ChipScope应用以及观察、分析数据的操作。

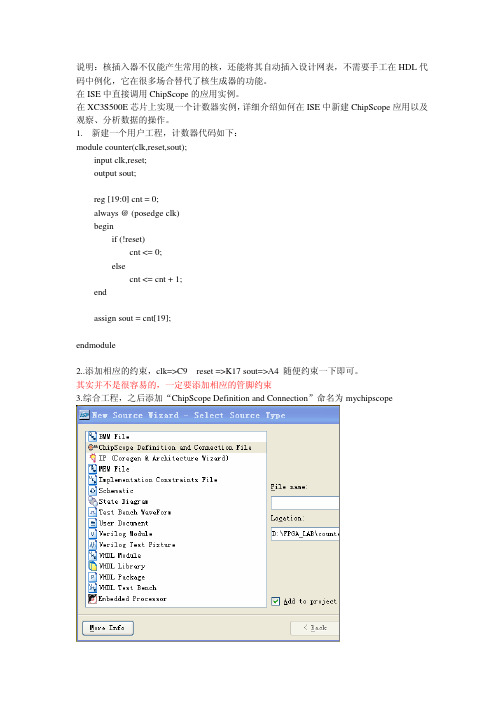

1.新建一个用户工程,计数器代码如下:module counter(clk,reset,sout);input clk,reset;output sout;reg [19:0] cnt = 0;always @ (posedge clk)beginif (!reset)cnt <= 0;elsecnt <= cnt + 1;endassign sout = cnt[19];endmodule2..添加相应的约束,clk=>C9 reset =>K17 sout=>A4 随便约束一下即可。

其实并不是很容易的,一定要添加相应的管脚约束3.综合工程,之后添加“ChipScope Definition and Connection”命名为mychipscope2.在工程区双击mychipscope.cdc文件,即可自动打开ChipScope Pro Inserter软件。

设置参数。

添加触发单元设置触发位宽。

其中触发类型选为Basic,位宽为20bit,设置采样深度为4096。

其中Number of input trigger port---用于设定触发端口数,每个端口ILA核可以支持多路比特数据,最多可有16个端口,具体的比特数取决于用于测试的逻辑资源。

Trigger Width用于设定每个端口的触发比特数。

#Match Units为触发单元的级联数,最多可设置16级,默认选择1级吧。

Sample on Rising Clock Edge--样本在时钟的上升沿进行采样。

选中Data Same As Trigger选项,则数据与触发信号相同,这是一种很常用的模式,可以捕获和采集触发逻辑分析仪的任何数据。

FPGA设计开发软件ISE使用技巧之:典型实例-ChipScope功能演示

FPGA设计开发软件ISE使用技巧之:典型实例-

ChipScope功能演示

6.8 典型实例11:ChipScope 功能演示

6.8.1 实例的内容及目标

1.实例的主要内容

本节通过一个简单的计数器,使用ChipScope 的两种实现流程,基于Xilinx 开发板完成设计至验证的完整过程。

本实例的工作环境如下。

- 设计软件:ISE 7.1i。

- 综合工具:ISE 自带的XST。

- 仿真软件:ModelSim SE 5.8C。

- 在线调试:ChipScope Pro 8.2i。

- 硬件平台:红色飓风II 代Xilinx 开发板。

- 实例内容:计数器。

通过ChipScope Pro 观测计数器的计数值,代码参见本书实例代码的典型实例11 文件夹。

其中count_new 文件夹对应采用流程1 实现的工程,count 文件夹对应用流程2 实现的工程。

使用ChipScope Pro 进行在线调试主要有两种实现流程。

(1)基于ChipScope Pro Core Generator 的实现流程。

- 调用ChipScope Pro Core Generator 生成逻辑分析仪的网表文件。

- 修改用户RTL,插入逻辑分析仪代码。

- 综合,实现,下载bit 配置文件。

- 调用ChipScope Pro Analyzer 观察波形。

(2)基于ChipScope Pro Core Inserter,通过新建资源的实现流程。

- 对工程文件进行综合,生成网表文件。

Chipscope教程

Xilinx的Chipscope类似于Altera的Signaltap。

下面记录一下Chipscope的使用方法。

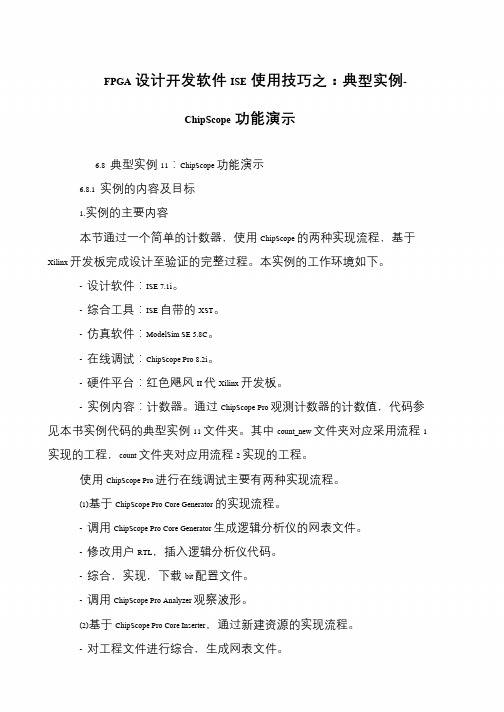

1. 生成Chipscope文件第一步: 打开ISE Design Tools下的CORE Generator工具。

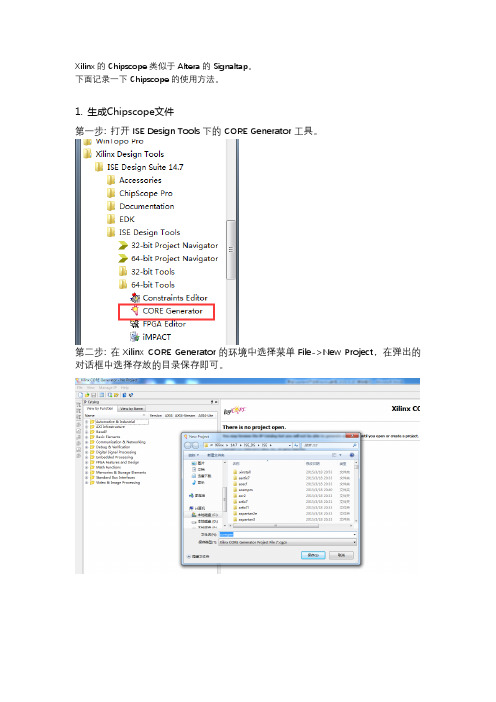

第二步: 在Xilinx CORE Generator的环境中选择菜单File->New Project,在弹出的对话框中选择存放的目录保存即可。

设置如下。

些,呵呵!选完后Apply一下OK关闭。

第五步: 双击IP Catalog窗口的Debug&Verification下的ICON(chipscope Pro –integrated Controller) 。

第六步: 在弹出的窗口中点击Generate就可以了。

第七步: ICON生成完成后,再双击IP Catalog窗口的Debug&Verification下的ILA(Chipscope Pro –Integrate Logic Analyzer)。

第八步: 在ILA的配置可以根据自己的需要来选择,我们这里不强求,我们这里选择一个触发Group,选择数据的采样深度为2048,就是一次采样2048个点,这个深度当然越大越好,但FPGA资源有限啊!设置完后点击Next。

也会用到Chipscope, 这样程序中基本上的信号都能观察了。

设置完后再Generate。

第十步: 这样我们所需的Chipscope文件都已经生成好了,我们可以在eeprom_test 的目录下看到生成的文件,特别要注意下图中我用红色圈出来的文件,如果在其它的工程中我们需要使用Chipscope的话,只要把这四个文件拷过去就好了,不要费老大力气的再重新生成一边。

接下来是Analyzer:点击Open cable按钮建立JTAG连接。

如果开发板和JTAG连接正常的话,Chipscope能找到开发板使用的FPGA芯片。

点击OK把Data Port里的CH0 ~CH7组合成一个组,方法是按Ctrl键,再选择Data port 里的CH0~CH7, 点击右键,选择Move to Bus->New Bus。

9.2.5 ChipScope Pro内核生成器应用实例[共7页]

![9.2.5 ChipScope Pro内核生成器应用实例[共7页]](https://img.taocdn.com/s3/m/4615ae79dd3383c4ba4cd24a.png)

ChipScope Pro 核生成器311Rate 】TDM 速率的乘积。

在【Timing – Asynchronous Sampling 】模式下,每个信号组数据端口的宽度等于(【ATD Pin Count 】ATD 引脚数+1)和【TDMRate 】TDM 速率的乘积。

单击【Next 】,出现ATC2核ATCK 和ATD 引脚参数,如图9-13所示。

图9-13 ATC2核ATCK 和ATD 引脚参数输出时钟(ATCK )和数据(ATD )引脚在ATC2核内例化,因此用户不用在顶层设计中手动设计,只需在内核产生器中指定这些引脚的位置和属性。

这些引脚属性添加在ATC2核的*.NCF 文件中。

在引脚参数表中,可以设置ATCK 和ATD 引脚的位置、I/O 标准、输出驱动和歪斜率。

(6) Pins 选项组。

∙ 【Pin Name 】:ATC 有两类输出引脚:ATCK 和ATD 。

当捕获模式设置成【State - Synchronous Sampling 】模式时,ATCK 引脚用作时钟引脚;当捕获模式设置成【Timing – Asynchronous Sampling 】模式时,ATCK 和ATD 引脚都用作数据引脚。

引脚名称是不能改变的。

∙ 【Pin Loc 】:设置ATCK 或ATD 引脚的位置。

∙ 【IO Standard 】:设置ATCK 或每个ATD 引脚的I/O 标准,标准根据器件和驱动器终端类型而定,它和约束文件中定义的I/O 标准一样。

∙ 【Drive 】:设置引脚输出驱动器的最大输出驱动电流,2~24mA 。

∙ 【Slew Rate 】:设置ATCK 和ATD 引脚的信号斜率,FAST 或SLOW 。

9.2.5 ChipScope Pro 内核生成器应用实例下面通过一个简单8位计数器的例子,了解如何在工程中添加ChipScope Pro 内核生成器的各个IP 核,对FPGA 内部节点和逻辑进行观测。

xilinx的Chipscope的使用方法

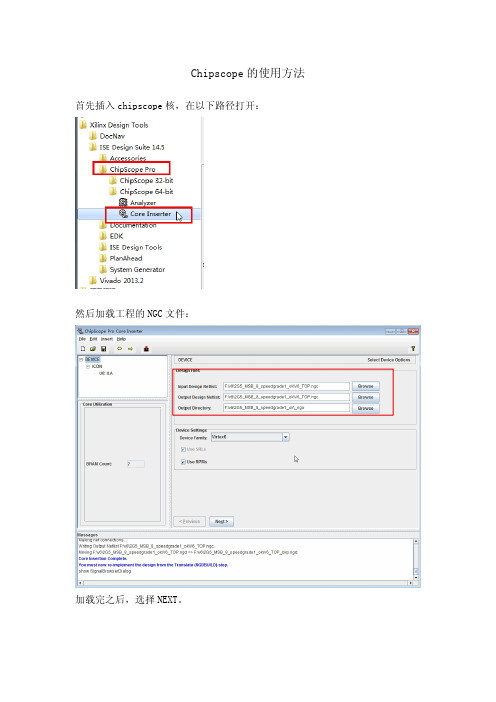

Chipscope的使用方法首先插入chipscope核,在以下路径打开:

然后加载工程的NGC文件:

加载完之后,选择NEXT。

继续next。

这里要选择Trigger的宽度,最大是256,我们一般选择256,以后用多少再返回来修改。

剩下的2项的选择,如下:

然后选择modify connections,

首先选择工程的主时钟,

在选择想要抓取的信号,

选择完后,如果所用的CH少于256,则需要返回之前的地方修改一下,

当所有的信号添加完成后,我们选择insert,加入chipscope核到工程中。

此时,ISE会重新跑一遍synthesize(综合),当执行完后,会产生下面蓝色的信息。

此时,在ISE中执行implement,点击run。

然后,记得保存chipscope,

会保存为.CDC文件,我这里命名保存的是test.cdc。

然后生成bit文件。

这样chipscope核就添加好了。

然后打开ISE中的analyze design using chipscope。

或者这样打开也行,如图:

然后选择连接V6平台,

然后配置V6平台,

选择bit和cdc文件,

这样点击OK,ISE会重新下载一遍工程,然后点击T!,就可以看到需要的信号数据了。

点击这个地方你可以看到想看到的选项,

BUS Plot选项是可以看到数据的波形的,waveform可以看到数据。

Trigger setup是设置触发条件和执行触发的,listing暂时不知道干嘛用的。

实验【chipscope使用】:芯片调试实验

实验:芯片调试实验芯片调试实验实验内容这个实验将指导你通过加入ILA/ICON内核到设计来执行片上查证的过程。

实验目的完成这个实验后,你将能够:●生成一些能在PicoBlaze上运行的任务。

●使用Chipscope-Pro生成ILA 和ICON 内核,将其插入一个PicoBlaze设计中。

●下载位流,在硬件上运行程序。

●执行片上确认,通过Chipscope分析器查看波形。

实验步骤在这个实验中,你将要修正一个以PicoBlaze为目标板的应用软件,使用Chipscope-Pro执行片上确认。

这个实验包括五个主要步骤:●加入一个Chipscope工程文件到设计●修正ILA参数和连接●修正软件,更新设计●对于没有相连的转换输入,分配终端约束●执行片上查证根据以下给出的每条指令,你将找到在以下的实验步骤中,配合每一步操作,我们配有相关的图示。

如果对流程比较熟悉,可以跳过其中的一些操作。

注意:如果在以后你想看这些实验,您可以从Xilinx的大学计划网站/univ上下载相应的文件。

设计总结你将使用Chipscope-Pro插入ICON 和ILA 内核到设计中,ILA内核触发端口从设计中的uar t_rx 和uart_tx 模块实现信号反馈,接着,当文本输入via hyperterminal后,建立的触发端口将捕捉数据。

当缓冲器满的时候,你将看见最终结果列在Chipscope中。

产生一个新的Chipscope-Pro工程步骤1启动ISE™ Project Navigator,打开工程文件。

1.打开Xilinx ISE软件,选择Start → Programs → Xilinx ISE 8.2i → Project Navigator2.选择File → Open ProjectVerilog users: Browse to c:\xup\fpgaflowlabs\verilog\lab4VHDL users: Browse to c: \xup\fpgaflow\labs\vhdl\lab43. 选择chipscope.ise点击Open通过Project Navigator生成一个新的Chipscope-Pro工程1.在Project Navigator中选择Project New Source,打开新的源文件对话框,点击ChipscopeDefinition and Connection,命名为loopback_c s.点击<Next>继续2. 选择loopback作为源文件,点击<next>,然后点击<finish>,一个Chipscope-Pro源文件将被增加到Sources in Project窗口。

ise里用chipscope

Chipscope的使用本来论文都差不多了,但是老师说缺少实验数据,没有办法,自己再加班加点补吧。

好在自己恰好有ChipScope的盘,于是赶快安装上,临阵磨枪,突击看了一晚上,有了一点点概念,这次记一下,下次就不用绞尽脑汁了。

还要感谢King帮忙查找资料。

逻辑分析仪的产生有两种方法:Core Generator(核产生器)和Core Inserter(核插入器),第一种方法产生内核,将这些内核例化后添加到原设计文件,最后综合,实现,下载。

第二种方法不需要修改原文件,它是将生成的内核添加到综合后的网表文件中,所以我们采用第二种方方法。

Core Inserter 的流程为:1)的RTL 综合成Netlist;2)调用Core Inserter 插入逻辑分析仪;3)布置和布局;4)产生bit 文件下载验证。

1. 首先用ISE对所设计的文件进行综合,然后再添加新建文件,选择ChipScope Definition 文件,选择完毕之后,添加到ISE工程。

2.对core Inserter进行配置,选择器件族,其它的默认即可,接下来是选择数据位宽,捕捉对比,进行信号连线等配置,可以根据自己的情况详细设置。

需要注意的是综合的设置需要保存Keep Hierarchy,防止优化过度。

3.按照以前运行ISE的步骤即可,知道最后下载到FPGA开发板,在ISE的最后会有ChipS cope Pro Analyze,然后点击,就运行逻辑分析仪。

然后点击JTAG连接方式,我的是用U SB的,然后选择[Device] configure 进行器件配置。

在window菜单下面可以选择触发设置窗口等选项,然后运行就可以观察你想要的波形了。

搭建Xilinx开发环境(3)…… 使用ChipScope进行调试Xilinx的ChipScope工具就相当于Altera的SignalTap II,能够捕捉FPGA内部的信号,方便了调试过程。

chipscope使用方法

chipscope的学习与使用(1) chipscope有三个主要的功能:1、ChipScope Core Inserter配置ICON核配置ILA核触发参数、捕获参数、网线连接2、ChipScope Pro Analyzer初始化边界扫描链,选择芯片型号配置芯片(JTAG CLOCK)设置触发条件观察信号波形3、ChipScope Pro Generator生成ICON核生成ILA核通过功能1生成了一个CDC文件,在这个CDC文件中需要配置一下触发参数的个数、深度以及连接。

最后工程需要重新run一下。

功能1通过后,可以双击Analyze Design Using ChipScope来启动分析仪,通过分析仪可以查看CDC 文件中配置的连线的波形。

功能3是一个集成功能,它把功能1和功能2集成为一个功能。

功能3需要打开ChipScope Pro Generator软件,在这个软件中新建一个工程,配置芯片型号以及合适的语言(Verilog HDL),配置ICON核和ILA核。

之后在工程中加入这两个文件:xxx_icon.xco和xxx_ila.xco文件在工程.v文件中加入ICON核和ILA核的调用,这时不需要把cdc文件,而且CDC文件需要从工程中移除。

下面是一个小的例子(调用ICON核和ILA核):wire [w_icon-1 : 0] con;wire [w_trig-1 : 0] p_data;xxx_icon u_icon(.CONTROL0(con));xxx_ila u_ila(.CLK(clk),.CONTROL(con),.TRIG0(p_data));最后再打开分析仪就可以来查看波形了,如果需要有时候可以再次加载CDC 文件。

以下是具体的操作说明:ChipScope Pro Generator打开方式:(见图《软件打开》)开始->程序->Xilinx ISE Suite 12.4->ISE Design Tools->CORE Generator打开这个软件后,新建一个工程。

EDK中chipscope使用说明

EDK中使用Chipscope进行硬件调试一、实验内容及目的1. ChipScope Pro简介ChipScope Pro的主要功能是通过JTAG口、在线实时地读出FPGA的内部信号。

基本原理是利用FPGA中未使用的BlockRAM,根据用户设定的触发条件将信号实时地保存到这些BlockRAM中,然后通过JTAG口传送到PC机,显示出时序波形。

图1为ChipScope Pro工作原理示意图图1 chipscope pro工作原理示意图一般来说,ChipScope Pro在工作时需要在用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrated Logic Analyzer core),提供触发和跟踪捕获的功能;二是集成控制器核(ICON core,Integrated Controller core),负责ILA核和边界扫描端口的通信,一个ICON核可以连接1~15个ILA核。

2、实验环境简介本实验的开发环境是在Xilinx公司研发的EDK开发环境,版本是14.2.所用到的开发板是diligent公司生产的型号为ATLYS开发板。

3、实验目的及内容本实验的主要目的是学会在EDK开发环境下使用chipscope pro进行硬件调试。

本实验是在H:\atlys_ziliao\microblaze\led目录下原有点灯的工程上进行的。

新建立一个文件夹H:\atlys_ziliao\microblaze\led_chipscope将H:\atlys_ziliao\microblaze\led 目录下的工程文件拷入到该文件夹下。

本实验的内容是使用chipscope获取GPIO的输出引脚的信号。

硬件连接图如图所示图2 硬件连接示意图二、实验步骤步骤一:用XPS打开原来的点灯工程。

图3 XPS打开原来的LED工程步骤二:在原来的硬件系统中添加ICON与ILA IP核如图所示图4 在原有的硬件系统中添加ICON与ILA IP核步骤三:配置chipscope_icon_0 IP核的参数。

Chipscope 简明教程

Chipscope 简明教程stevechou@一、操作环境本教程假定用户已有安装好仿真、综合、ISE和相应的Chipscope,教程使用的环境如下:仿真:Modelsim 5.8综合:Synplify pro 7.5.1布局:ISE 6.2分析:Chipscope 6.2二、RTL设计及其仿真RTL 源代码参见rtl/lfsr.v,testbench 参见rtl/lfsr_tb.v,其仿真波形如下:三、逻辑分析仪产生逻辑分析仪的产生有两种方法:Core Generator(核产生器)和Core Inserter(核插入器),Core Inserter 的流程为:1)的RTL 综合成Netlist;2)调用Core Inserter 插入逻辑分析仪;3)布置和布局;4)产生bit 文件下载验证。

而Core Generator 的流程为:1)调用Core Generator 产生逻辑分析仪的Netlist;2)修改用户的RTL,插入逻辑分析代码;3)布置和布局;4)产生bit 文件下载验证。

因为使用Core Inserter 需要在网表中搜索信号,相对修改RTL 来说比较麻烦,并且每次修改RTL 后需要重新插入逻辑分析仪,故本教程以Core Generator 流程为例,这样每次修改RTL 后,只需要重新综合、布置和布局即可。

1)从“开始”-->“程序”-->“ChipScope Pro 6.2”--> “ChipScope Pro Core Generator”2)选择ICON,即集成控制器产生3)选择输出目录和设备家族4)选择语言和综合工具5)点击“Generate Core”产生集成控制器6)点击“Start Over”,回到主菜单,选择“ILA”,即产生集成逻辑分析仪7)选择输出目录、设备家族和采样时钟边缘8)在Trigger Width 框填入触发宽度329)选择“Data Same AsTrigger”,即数据端口和触发端口相同;从Data Depth下拉框选择采样深度,“Number of Block RAMs”处将同时显示需要的Block RAM 块数,对于Sparten II 200 来说,共有14 块Block RAM,注意不要超过限制10)选择语言和综合工具11)点击“Generate Core”产生集成逻辑分析仪Chipscope 将在相应目录产生以下主要文件:icon.edn 集成控制器的网表icon.ncf 集成控制器的网表约束文件icon_synplicity_example.v 集成控制器的嵌入例子代码ila.edn 集成逻辑分析仪的网表ila.ncf 集成逻辑分析仪的网表约束文件ila_synplicity_example.v 集成逻辑分析仪的嵌入例子代码用户需要依照例子代码修改RTL 代码,以下示出最后的结果,请特别注意红色部分://-----------------------------------------------------------------//// ICON core wire declarations////-----------------------------------------------------------------wire [35:0] control0;//-----------------------------------------------------------------//// ICON core instance////-----------------------------------------------------------------icon i_icon(.control0(control0));//-----------------------------------------------------------------//// ILA Core wire declarations////-----------------------------------------------------------------wire [31:0] trig0;//-----------------------------------------------------------------//// ILA core instance////-----------------------------------------------------------------ila i_ila(.control(control0), //控制器接口.clk(clk), //采集的时钟.trig0(trig0));assign trig0 = q; //需要采集的信号列表四、综合代码将文件icon_synplicity_example.v、ila_synplicity_example.v和lfsr.v添加到工程中综合:五、 布置、布局和下载电路将icon.edn 、icon.ncf 、ila.edn 和ila.ncf 拷贝到综合器生成 edf 的目录。

学习使用chipscope逻辑分析仪v1.1

学习使用chipscope逻辑分析仪v1.1学习使用chipscope逻辑分析仪帮助FPGA调试*******************文档说明:本文档叙述在ISE10.1工程环境中使用代码例化Chipscope相关核调试核来帮助FPGA 板上调试。

1. 认识ChipscopeChipScope的基本原理是利用FPGA内部的逻辑和BlockRAM,根据用户设定的触发条件将信号实时地保存到BlockRAM中,然后根据用户设定的触发条件将信号实时地保存到BlockRAM中,通过JTAG 口传回到计算机显示波形。

Chipscope安装好之后,有下面几个工具:在ISE中使用Chipscope有两种方法,如下图所示:方法1:使用Core Generator生成自己需要的Chipscope调试核,并在自己的工程中手工代码中例化和连接,然后综合实现。

方法2:使用Core Inserter工具,向自己已经综合的工程的网表中添加Chipscope核并由图形界面帮助连接,然后综合实现。

两种方法比较:方法2简单,但功能有限,不够灵活,有很多内部信号不能从网表中找到;方法1手工连线虽然复杂一点,但是功能强大!可以选择自己工程中的任何信号点连接调试,有了这个法宝,在调试FPGA时候便有了纵横驰骋的感觉。

2. 建立一个简单的工程建立一个ISE工程。

并添加文件,编写如下代码。

绑定引脚约束。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity main isPort (clk : in STD_LOGIC;cnt : out STD_LOGIC_vector(3 downto 0));end main;architecture Behavioral of main issignal counter:std_logic_vector(31 downto 0):=(others =>'0');beginprocess(clk)beginif(clk'event and clk='1')thencounter<=counter+1;end if;end process;cnt<=counter(25 downto 22);end Behavioral;这部分代码非常简单,对时钟做32位计数,并将中间的4位作为输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Chipscope 用法

1、Chipscope基础

(1)原理:

Chipscope可以理解为FPGA中的一个IP核,但是是一种在线调试用的,所以必须以硬件的连接为基础。

在FPGA已经下载程序的情况下,添加我们关心的信号或者接口,将选定了端口Chipscope(不妨理解为一个嵌入的系统)加入到程序后重新布局布线下载到FPGA中,此时我们就可以观察信号和接口的值了。

注意:从图形上看,有点类似于Modelsim的仿真结果,但其本质区别在于Chipscope用的实际的信号波形,而Modelsim仅仅是仿真的结果!

(2)方法:

一般的,我们会按照信号的方向一步一步进行排查验证。

在下载程序之前如果我们已经在Modelsim中进行过了充分的仿真,而下载到板子上之后程序运行结果没有达到预期时,我们可以先考虑将所有的输入输出结果用Chipscope抓出来观察对比,看能不能找到问题所在。

如果输出结果没有达到预期,我们就采用按照信号传输方向排查的方法一步一步检查,如果输出结果和预期一致,我们应该考虑硬件的连接甚至设计是否出了问题,有时候要对总体方案进行重新评审。

2、具体步骤

第一步:新建一个Chipscope 文件,比如命名为test。

第二步:双击打开test.cdc文件,进入Core Insert界面,选择需要观察的信号或者端口

(1)一直按照默认的设置点Next直到出现Trigger Width时进行选择,表示一共需要选择的信号的位数;

(2)Data Depth选项表示一步要采用的深度,可以理解为运行一次能抓到多少个单位的数据(时间单位一般是固定的,且与选择的时钟有关);

同时采用可以选择时钟的上升沿或者下降沿(分别对应Rising和Falling);

(3)Next进入到时钟和信号的连接设置,点击Modify Connections即可进入设置界面(4)Clock Signals表示需要采样的时钟信号,一般选择最高频率的那个时钟,而且尽量避免出现跨时钟域采样信号的情况

(5)Trigger/Data Signals表示需要采用的数据为,在左侧选中后点击右侧的Make Connections即可,把所有关心的信号连接完后点OK返回到设置界面

(6)此时,信号选择完毕,点Return to Project Navigator 并在弹出是否保存的提示框中选择是,返回到ISE环境。

第三步:在返回的ISE环境中点击Configure Target Device 重新布局布线并生成下载文件。

下载文件和普通的下载方式一样,此处不再赘述。

第四步:在Chipscope中抓信号波形进行分析

(1)从ISE环境下双击Analyze Design Using Chipscope进入Chipscope环境,如下图所示

(2)点击“Open Cable/Search JTAG Chain”,如下图所示

在弹出的提示框中点OK

(3)如下图所示右键点击DEV:1并在弹出的选项中选择Configure

在弹出的对话框中选择Select New File

双击对应目录下的.bit文件或者单击后点“打开”

在返回的下图中点击OK

从下面的进度可以看到,当完成到100%时即表示下载成功

(4)下载完成后,开始观察信号,先熟悉下界面

左侧的Trigger Setup表示触发设置

右下的三个选项分别表示如何设置,可以通过单击展开进行设置,一般情况下,我们比较关心的是Match Functions

右上的三个图标分别表示Run,Stop和Trigger Immediate在设置好后直接点三角那个即可开始抓信号

展开Match就会看到如下图所示,对于某个信号的Value如果为X则表示任意值都会采样,如果为1则表示只有在高电平期间才会取样,而R和F则分别代表上升沿和下降沿抓取数据波形,通过这种灵活设置就可以抓取我们想要得到的波形

(5)将第二个信号设置为1,再点击上面提到的三角标志,就进行了采样,选择左侧的Waveform就会在右下出现如下图所示的波形图。

至此,我们已经完整的走过了一遍Chipscope抓波形的过程,如果需要继续分析其他波形,只需按照此流程重新设置一遍即可。

3、小结

正如前面提到的一样,我们一般会先测输入输出信号,输出正确的情况下我们就考虑其他的非FPGA设计因素引起的差错,如果输出错误,我们就考虑按照信号流的顺序,依次进行抓取分析(当然,在小规模的设计中可以一次把所有信号全加进来再依次分析,分析过程和Modelsim中的分析方法相似)。