3.1 MOS逻辑门电路解析

数电课后答案解析康华光第五版(完整)

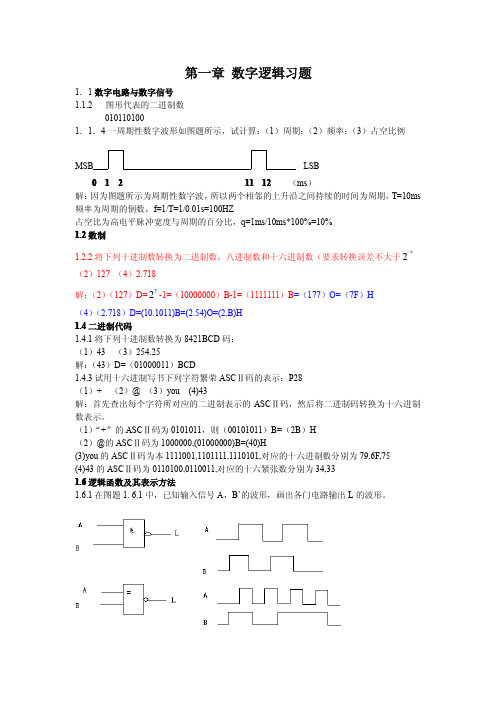

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

《数字电子技术基础(数字部分)》康华光第五版答案

环境下的门电路。

表题 3.1.1 逻辑门电路的技术参数表

V / V OH (min)

V /V OL(max)

V / V IH (min)

V / V IL(max)

逻辑门 A

2.4

0.4

2

0.8

逻辑门 B

3.5

0.2

2.5

0.6

逻辑门 C

4.2

0.2

3.2

0.8

解:根据表题 3.1.1 所示逻辑门的参数,以及式(3.1.1)和式(3.1.2),计算出逻辑门 A 的

课后答案网

2.2.4 已知逻辑函数 L = AB + BC + C A ,试用真值表,卡诺图和逻辑图(限用非门和与非

门)表示

解:1>由逻辑函数写出真值表

A

B

C

L

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

2>由真值表画出卡诺图

3>由卡诺图,得逻辑表达式 L = AB + BC + AC

课后答案网

www.khd课后a答w案.网com

第一章 数字逻辑习题

1.1 数字电路与数字信号 1.1.2 图形代表的二进制数

010110100 1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例

MSB

LSB

012

11 12 (ms)

数电课后答案解析康华光第五版(完整)

数电课后答案解析康华光第五版(完整)第⼀章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的⼆进制数0101101001.1.4⼀周期性数字波形如图题所⽰,试计算:(1)周期;(2)频率;(3)占空⽐例MSB LSB0 1 2 11 12 (ms)解:因为图题所⽰为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空⽐为⾼电平脉冲宽度与周期的百分⽐,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列⼗进制数转换为⼆进制数,⼋进制数和⼗六进制数(要求转换误差不⼤于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4⼆进制代码1.4.1将下列⼗进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试⽤⼗六进制写书下列字符繁荣ASCⅡ码的表⽰:P28(1)+ (2)@ (3)you (4)43解:⾸先查出每个字符所对应的⼆进制表⽰的ASCⅡ码,然后将⼆进制码转换为⼗六进制数表⽰。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的⼗六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的⼗六紧张数分别为34,331.6逻辑函数及其表⽰⽅法1.6.1在图题1. 6.1中,已知输⼊信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与⾮, (b)为同或⾮,即异或第⼆章逻辑代数习题解答2.1.1 ⽤真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

理解NMOS逻辑门电路

VNL =VIL(max)-VOL(max)

3.传输延迟时间

传输延迟时间是表征门电路开关速度 的参数,它说明门电路在输入脉冲波

CMOS电路传输延迟时间

形的作用下,其输出波形相对于输入 波形延迟了多长的时间。

50% 输入

t PHL

50% tPLH

5. 延时功耗积 是速度功耗综合性的指标.延时功耗积,用符号DP表示

6. 扇入与扇出数

扇入数:取决于逻辑门的输入端的个数。

扇出数:在正常工作情况下,能带同类门电路的最大数目。

(a)带拉电流负载

当负载门的个数增加时,总的拉电流将增加,会引起输出 高电压的降低。但不得低于输出高电平的下限值,这就限 制了负载门的个数。

高电平扇出数:

N OH

IOH ( 驱 动 门) I IH (负 载 门)

IOH :驱动门的输出端为高电平电流

IIH :负载门的输入电流为。

(b)带灌电流负载

当负载门的个数增加时,总的灌电流IOL将增加,同时也将引起 输出低电压VOL的升高。当输出为低电平,并且保证不超过输 出低电平的上限值。

N OL

场效应三极管知识

利用电场效应来控制电流的三极管,称为场效应管,也 称单极型三极管。

由金属、氧化物和半导体制成。称为金属-氧化物-半导体 场效应管,或简称 MOS 场效应管。

场效应管特点: 只有一种载流子参与导电; 是一种电压控制器件;

输入电阻高,可达 109 以上; 工艺简单、易集成、功耗小、体积小、成本低。

+5

45 5×10-3 225 ×10-3 2.2 3.4

5

CMOS

VDD=15V +15 12 15×10-3 180 ×10-3 6.5 9.0

3.1 MOS逻辑门电路

D1 Rs vI D2

CP

TP vO

vG = VDD + vDF (3) vI < − vDF D2导通 D1截止 vG = − vDF 导通,

CN

TN

当输入电压不在正常电压范围时,二极管导通, 当输入电压不在正常电压范围时,二极管导通,限制了电容两端 电压的增加,保护了输入电路。 电压的增加,保护了输入电路。 RS和MOS管的栅极电容组成积分网络,使输入信号的过冲电压 管的栅极电容组成积分网络, 延迟且衰减后到栅极。 延迟且衰减后到栅极。

vO /vI TN TP

+5V

v I /vO

−5V到+5V 到

+5V − 5V

υI的变化范围为-5V到+5V。 的变化范围为- 到 。

1)当c=0, c =1时 ) , 时

1 ≥ 1

0 1 0

TP截止 导通 截止 L 0 1

0 1EN

截止 TN 导通 使能EN 使能 1 1 0 输入A 输入 0 1 × 输出L 输出 0 1 高阻

0 1

A EN 1 L

逻辑功能: 逻辑功能:高电平有效的同相逻辑门

3.1.7 CMOS传输门(双向模拟开关) 传输门(双向模拟开关) 传输门

VDD

TN

vO

VO H

VDD = ROFF ≈VDD RON + ROFF

当υI =VOH= VDD时 VGSN =VDD < VTN |VGSP|= 0 > VTP TN管导通; 管导通; TP管截止。 管截止。

TP VDD

此时, 主要降在T 管上, 此时,VDD主要降在 P管上,输 出为高电平V 出为高电平 OL :

逻辑真值表

vI

电子技术基础数字部分第六版

0

VILmax VIHmin 5

VIN /V

输出低电 平

输入高电平的下限值

VIL(min)

输出低电平的上限值

VOH(max)

21

4.CMOS反相器的工作速度 带电容负载

在由于电路具有互补对称的性质,它的开通时间与关 闭时间是相等的。平均延迟时间小于10 ns。

22

3.2.3 其他基本CMOS 逻辑门电路

漏极 VDD

开路输出

VV DD DD

V DD

RR PP

RP

LL

A

A

BB

L

TP1

AA

L

A TN1 B 1

L BB

A

L

B

C 与与 非非 门门 GG 11

与非门 G1

C

D

(a)工作时必须外接电源和电阻;

D

(b)与非逻辑不变

与 非 门 G2

(c) 可以实现线与功能;

LABCD

ABCD 36

(2) 上拉电阻对OD门动态性能的影响

电路 C

v I /v O

TP

+5V 0V

v O /v I

TN

C

逻辑符号

C

v I /v O

TG

C

C

v O /v I

等效电路

υI / υO

υo/ υI

26

1、传输门的结构及工作原理

v I /v O

0V到+5V

C

+5V

TP +5V

0V TN

0V

C

v O /v I

设TP:|VTP|=2V, TN:VTN=2V,

Rp的值愈小,负载电容的充电时间

电子技术基础数字部分第六版

4000系列

速度慢 与TTL不兼容 抗干扰 功耗低

74HC 74HCT

速度加快 与TTL兼容 负载能力强 抗干扰 功耗低

74VHC 74VHCT

速度两倍于74HC 与TTL兼容 负载能力强 抗干扰 功耗低

74LVC 74AUC

低(超低)电压 速度更加快 负载能力强 抗干扰 功耗低

2.TTL 集成电路: 广泛应用于中大规模集成电路

(1) VGS 控制沟道的导电性 vGS=0, vDS0, 等效背靠背连接的两个二极管, iD0。

vGS>0, 建立电场 反型层 vDS>0, iD 0。

沟道建立的最小 vGS 值称为开启电压 VT.

V DS

S

V GS G

D

N

N

P

n-沟 道

B 10

1. N沟道增强型MOS管的结构和工作原理

1. CMOS漏极开路门

1.)CMOS漏极开路门的提出 A

B

输出短接,在一定情况下会产

生低阻通路,大电流有可能导 致器件的损毁,并且无法确定 C

D

输出是高电平还是低电平。

VDD

T P1

TN1

1

与非门 G1

VDD

T P2

0

TN2

与非门 G2

35

(2)漏极开路门的结构与逻辑符号

漏极开路门输出连接

电路

逻辑符号

31

3.3.1 输入保护电路和缓冲电路

采用缓冲电路能统一参数,使不同内部逻辑集成逻辑门电路 具有相同的输入和输出特性。

VDD

vi

基本逻辑

vo

功能电路

输入保护缓冲电路 基本逻辑功能电路 输出缓冲电路

32

电子技术基础(数字)康华光课后答案

(A)

(B)

(C)

(D)

解:对于图题 3.1.12(a)所示的 CMOS 电路,当 EN =0 时, TP2 和TN 2 均导通,

TP1 和 TN1 构成的反相器正常工作,L= A ,当 EN =1 时,TP2 和TN 2 均截止,无论

A 为高电平还是低电平,输出端均为高阻状态,其真值表如表题解 3.1.12 所示, 该电路是低电平使能三态非门,其表示符号如图题解 3.1.12(a)所示。

A

L

00Βιβλιοθήκη 1010

1

0

1

1

高阻

3.1.12(a)

A

L

0

0

0

0

1

1

1

0

高阻

1

1

高阻

3.1.12(b)

EN A

0

0

L 高阻

0

1

高阻

1

0

0

1

1

1

3.1.12(c

A

L

0

0

1

0

1

0

1

0

高阻

1

1

高阻

3.1.12(d)

3.2.2 为什么说 TTL 与非门的输入端在以下四种接法下,都属于逻辑 1:(1)输 入端悬空;(2)输入端接高于 2V 的电源;(3)输入端接同类与非门的输出高电 压 3.6V;(4)输入端接 10kΩ 的电阻到地。 解:(1)参见教材图 3.2.4 电路,当输入端悬空时,T1 管的集电结处于正偏,Vcc 作用于 T1 的集电结和 T2,T3 管的发射结,使 T2,T3 饱和,使 T2 管的集电极 电 位 Vc2=VcEs2+VBE3=0.2+0.7=0.9V , 而 T4 管 若 要 导 通 VB2=Vc2≥VBE4+VD=0.7+0.7=1.4V,故 T4

逻辑门电路

3 逻辑门电路引言在第一章我们介绍了与、或、非三种基本逻辑运算,并引出了逻辑变量与逻辑函数的关系。

在那里,逻辑符号是以黑匣的方式来表示相应的逻辑门,如与、或、非等基本逻辑门。

但是,黑匣法只能建立初步的概念,对于电子设计工作者来说是不够的。

为了正确而有效地使用集成逻辑门电路,用户必须对器件的内部电路,特别是对它的外部特性有所了解。

因此,本章将揭开黑匣的奥秘,讨论了几种通用的集成逻辑门电路,如金属-氧化物-半导体互补逻辑门电路(CMOS①)、晶体三极管逻辑门电路(TTL②)和射极耦合逻辑门电路(ECL③)等的基本原理及特性。

在分析门电路时,着重它们的逻辑功能和外特性,对其内部电路,只作一般介绍。

3.1 MOS逻辑门电路3.1.1 数字集成电路简介CMOS逻辑门电路是在TTL电路之后出现的一种广泛应用的数字集成器件。

按照器件结构的不同形式,可以分为NMOS、PMOS和CMOS三种逻辑门电路。

由于制造工艺的不断改进,CMOS电路已成为占主导地位的逻辑器件,其工作速度已经赶上甚至超过TTL电路,它的功耗和抗干扰能力则远优于TTL。

因此,几乎所有的超大规模存储器,以及PLD器件都采用CMOS工艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,后来发展为4000B系列,其工作速度较慢,与TTL不兼容,但功耗低、工作电压范围宽、抗干扰能力强。

随后出现了高速CMOS器件74HC和74HCT系列。

与4000B 系列相比,其工作速度快、带负载能力强。

74HCT系列与TTL兼容,可与TTL器件交换使用。

另一种新型CMOS系列是74VHC和74VHCT系列,其工作速度达到了74HC和74HCT系列的两倍。

对于54系列产品,其引脚编号及逻辑功能与74系列基本相同,所不同的是54系列是军用产品,适用的温度范围更宽,测试和筛选标准更严格。

近年来,随着便携式设备(如笔记本电脑、数字相机、手机等)的发展,要求使用体积小、功耗低、电池耗电小的半导体器件,因此先后推出了低电压CMOS器件74LVC④系列,以及超低电压CMOS器件74AUC⑤系列,并且半导体制造工艺可以使它们的成本更低、速度更快,同时大多数低电压器件的输入输出电平可以与5V电源的CMOS或TTL电平兼容。

3.1 MOS逻辑门电路

扇出数:是指其在正常工作情况下,所能带同类门电路的最大数目

高电平扇出数:

N OH

IOH ( 驱 动 门) I IH (负 载 门)

IOH :驱动门的输出端为高电平的电流.

IIH :负载门的输入电流。

1.3 MOS开关及其等效电路

vGS

当υI < VT : MOS管截止, 输出高电平 当υI >>VT :MOS管工作在可变电阻区,输出低电平

1 、逻辑门:实现基本逻辑运算和复合逻辑运算的单元电路。

2、 逻辑门电路的分类 分立门电路

逻辑门电路 集成门电路

二极管门电路 三极管门电路 MOS门电路 TTL门电路

NMOS门 PMOS门 CMOS门

1.2 逻辑门电路的一般特性

1. 输入和输出的高、低电平

TTL

高电平

低电平

2.4~5v,典型值3.6v 0~0.4v,典型值0.3v

输出低电平的上限值 VOL(max)

输出高电平的下限值 VOH(min)

2. 噪声容限

定义:在保证输出电平不变的条件下,输入电平允许波动的

范围。它表示门电路的抗干扰能力。

负载门输入高电平时的噪声容限VNH : —当前级门输出高电平的最小值

驱动门

1 vo

噪声

vI

负载门

1

时允许负向噪声电压的最大值。 VNH =VOH(min)-VIH(min)

逻辑门电路

——基本逻辑门 与或、与非 主讲:

基本要求: 1、了解半导体器件的开关特性; 2、熟练掌握基本逻辑门(与、或、与非、或非、 异或门)、三态门、OD门(OC门)和传输门 的逻辑功能; 3、学会门电路逻辑功能分析方法; 4、掌握逻辑门的主要参数及在应用中的接口问题。

电子技术基础(数字部分)第五版答案康华光

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSBLSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于 42. (2)127 (4)2.718解:(2)(127)D=-1=(10000000)B-1=(1111111)B=(177)O=(7F)H 72(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)ABABAB⊕=+(A⊕B)=AB+AB 解:真值表如下ABAB⊕ABABAB⊕AB+AB111111111111由最右边2栏可知,与AB+AB的真值表完全相同。

【资料】逻辑门电路(精)汇编

D

G S

N增强型

D

D

G

G

S P耗尽型

S N耗尽型

场效应管与晶体管的比较

双极型三极管

单极型场效应管

载流子

控制方式

类型

放大参数 输入电阻

输出电阻 热稳定性 制造工艺 对应电极

电子和空穴两种载 流子同时参与导电

电流控制

NPN和PNP

20~200

102 ~104较低

rce很大

差 较复杂 B—E—C

电子或空穴中一种 载流子参与导电

电压控制 N沟道和P沟道

gm 1~5mA/V

107 ~11 04较高

rds很大

好 简单,成本低

G—S—D

§3.3 集成门电路

◆ 集成逻辑门主要有CMOS系列和TTL系列两大类, 目前CMOS系列已成为占主导地位的逻辑器件。

◆ CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体)系列集成逻辑门电路由 NMOS管和PMOS管构成。

噪声容限值越大,抗干扰能力越强。

vO

1

vI

1

驱动门

负载门

VDD VOH(min)

VNH

• 输入高电平噪声容限: VNH=VOH(min)-VIH(min)

VIH(min)

VIL(max)

VNL

VOL(max)

• 输入低电平噪声容限: VNL=VIL(max)-VOL(max)

三、扇入、扇出系数

前后级之间电流的联系。

解:1)NOH=IOH/IIH=4/0.02=200 NOL=IOL/IIL=4/0.4=10

则,扇出系数为10。

mos与门电路

MOS与门电路1. 介绍MOS(Metal-Oxide-Semiconductor)是一种常见的半导体器件,广泛应用于集成电路和逻辑门电路中。

门电路是由多个晶体管组成的电路,用于实现逻辑运算和信号处理。

本文将介绍MOS和门电路的基本原理、分类以及应用。

2. MOS基本原理MOS是由金属-氧化物-半导体构成的结构。

它由一个金属电极、一个氧化物层和一个半导体基片组成。

MOS的工作原理基于电场控制,通过在氧化物层上施加电压,控制半导体中的电荷分布,从而改变电流的流动情况。

MOS有两种基本工作模式:增强型和耗尽型。

增强型MOS(Enhancement MOS)需要在栅极上施加正电压,使得导电性增强,从而形成导通通道。

耗尽型MOS (Depletion MOS)则相反,需要在栅极上施加负电压,使得导电性减弱,从而形成导通通道。

3. 门电路分类门电路是由多个MOS晶体管组成的电路,可以实现逻辑运算和信号处理。

常见的门电路有与门、或门、非门、异或门等。

下面将介绍其中几种常见的门电路。

3.1 与门(AND Gate)与门是最简单的逻辑门之一,它有两个或多个输入信号和一个输出信号。

只有当所有输入信号都为高电平时,输出信号才为高电平;否则,输出信号为低电平。

与门可以用MOS晶体管实现,其中输入信号通过MOS的栅极控制导通通道,输出信号通过MOS的漏极输出。

3.2 或门(OR Gate)或门也是常见的逻辑门之一,它有两个或多个输入信号和一个输出信号。

只要有一个或多个输入信号为高电平,输出信号就为高电平;只有当所有输入信号都为低电平时,输出信号才为低电平。

或门可以通过将多个MOS晶体管的漏极连接在一起实现。

3.3 非门(NOT Gate)非门是最简单的逻辑门之一,它只有一个输入信号和一个输出信号。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

非门可以通过一个MOS晶体管实现,输入信号通过MOS的栅极控制导通通道,输出信号通过MOS的漏极输出。

(完整word版)《电子技术基础》第五版课后答案

第一章数字逻辑习题1.1数字电路与数字信号1。

1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms频率为周期的倒数,f=1/T=1/0。

01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1。

2数制21.2。

2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2。

718)D=(10。

1011)B=(2。

54)O=(2.B)H1。

4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1。

4。

3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@(3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+"的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331。

6逻辑函数及其表示方法1。

6.1在图题1。

6。

1中,已知输入信号A,B`的波形,画出各门电路输出L的波形.解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB A B A B ⊕AB AB A B ⊕ AB +AB 0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

第3章-逻辑门电路

3 逻辑门电路MOS 逻辑门电路3.1.2 求下列情况下TTL 逻辑门的扇出数:(1)74LS 门驱动同类门;(2)74LS 门驱动74ALS 系列TTL 门。

解:首先分别求出拉电流工作时的扇出数N OH 和灌电流工作时的扇出数N OL ,两者中的最小值即为扇出数。

从附录A 可查得74LS 系列电流参数的数值为I OH =,I OL =8mA ,I IH =,I IL =;74ALS 系列输入电流参数的数值为I IH =,I IL =,其实省略了表示电流流向的符号。

(1) 根据(3.1.4)和式()计算扇出数74LS 系列驱动同类门时,输出为高电平的扇出数0.4200.02OH OH IH I mA N I mA=== 输出为低电平的扇出数 8200.4OL OL IL I mA N I mA ===所以,74LS 系列驱动同类门时的扇出数N O 为20。

(2) 同理可计算出74LS 系列驱动74ALS 系列时,有0.4200.02OH OH IH I mA N I mA=== 8800.1OL OL IL I mA N I mA === 所以,74LS 系列驱动74ALS 系列时的扇出数N O 为20。

3.1.4 已知图题所示各MOSFET 管的T V =2V ,忽略电阻上的压降,试确定其工作状态(导通或截止)。

解:图题3.1.4(a )和(c )的N 沟道增强型MOS ,图题(b )和(d )为P 沟道增强型MOS 。

N 沟道增强型MOS 管得开启电压V T 为正。

当GS V <V T 时,MOS 管处于截止状态;当GS V ≥V T ,且DS v ≥(GS V —V T )时,MOS 管处于饱和导通状态。

对于图题3.1.4(a ),GS V =5V ,DS v =5V ,可以判断该MOS 管处于饱和导通状态。

对于图题3.1.4(c ),GS V =0V <V T ,所以MOS 管处于截止状态。

《电子技术基础》数字部分第五版课后答案

第一章数字逻辑习题1.1数字电路与数字信号1.1.2图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0121112(ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制2−1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127(4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43(3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+(2)@(3)you(4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1.6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解:(a)为与非,(b)为同或非,即异或第二章逻辑代数习题解答2.1.1用真值表证明下列恒等式(3)A B AB AB ⊕=+(A⊕B)=AB+AB 解:真值表如下A B A B⊕ABAB A B⊕AB +AB00010110110000101000011111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(2) 上拉电阻对OD门动态性能的影响

Rp的值愈小,负载电容的充电时间 常数亦愈小,因而开关速度愈快。

但功耗大,且可能使输出电流超过允

许的最大值IOL(max) 。

A

Rp的值大,可保证输出电流不能超 B 过允许的最大值IOL(max)、功耗小。 但负载电容的充电时间常数亦愈大, C

开关速度因而愈慢。

1L

T N1

V DD

T P2

T N2

0

L

T N1

3. 异或门电路

A B

=A⊙B

L AB X AB A B

A B A B

AB

4.输入、输出保护电路和缓冲电路

采用缓冲电路能统一参数,使不同内部逻辑集成逻辑门电路 具有相同的输入和输出特性。

vi

基本逻辑

vo

功能电路

输入保护缓冲电路 基本逻辑功能电路 输出缓冲电路

电压传输特性

vO f (vI )

CMOS反相器的工作速度与动态功耗 带电容负载

在电容负载情况下,由于电路具有互补对称的性质, 它的开通时间与关闭时间是相等的。

VDD

VDD

iDP

vI

TP

vO

vI=0V

TN

iDN

CL

平均延迟时间:

iDP

10ns

vO

CL

在动态情况下,CMOS反相器的功耗大大增加

3.1.5 CMOS 逻辑门

+15

12 15×10-3 180 ×10-3 6.5 9.0

15

高速CMOS

+5

8

1×10-3

8 ×10-3

1.0 1.5

5

3.1.3 MOS开关及其等效电路

1. 二极管的开关特性

D

+i

vi

RL

-

Ot~1 时t1刻::vi =vi =VF-,VDR导通

电路电中路电中流电:流 i = ?

反向恢复时间:二极管从 导通转为截止所需的时间

形的作用下,其输出波形相对于输入 波形延迟了多长的时间。

50% 输入

t PHL

50% tPLH

类型 参数

tPLH或 tPHL(ns)

74HC

VDD=5 V

74HCT 74LVC 74AUC VDD=5V VDD=3.3V VDD=1.8V

7

8

2.1

0.9

输出 90%

50%

10%

t

f

90%

50% 10%

+VDD

1

TN1 TN2

+VDD

A

B 0

(2)漏极开路门的结构与逻辑符号

电路

逻辑符号

+VDD

L

TP2

TP1 L

A

A

TN1

A

& LA

BB

TNB2

B

VSS

(a)工作时必须外接电源和电阻;

(b)与非逻辑不变

C

(c) 可以实现线与功能;

D

漏极开路门输出连接

VDD

Rp L

VDD

Rp

A&L B

C& D

L P1 P2 AB CD

输入端保护电路:

二极管导通电压:vDF

D2 ---分布式二极管(iD大)

D1

CP

Rs

vI

VDD

TP vO

(1) 0 < vI < VDD + vDF

D1、D2截止 (2) vI> VDD + vDF

D1导通, D2截止 vG = VDD + vDF

D2

CN

TN

(3) vI < vDF D2导通, D1截止 vG = vDF

驱动 1门

vo

噪声

vI

负载门

1

VNH =VOH(min)-VIH(min)

负载门输入低电平时的噪声容限:

VNL —当前级门输出低电平的最大

值时允许正向噪声电压的最大值。

VNL =VIL(max)-VOL(max)

3.传输延迟时间

传输延迟时间是表征门电路开关速度 的参数,它说明门电路在输入脉冲波

CMOS电路传输延迟时间

0.4 0.5 3.5

HTL

+15 85

30

2550

7

7.5

13

CE10K系列 -5.2 2

25

ECL

CE100K系列 -4.5 0.75

40

50

0.155 0.125 0.8

30

0.135 0.130 0.8

VDD=5V

+5

45 5×10-3 225 ×10-3 2.2 3.4

5

CMOS

VDD=15V

3 逻辑门电路

3.1 MOS逻辑门电路 3.2 TTL逻辑门电路 *3.3 射极耦合逻辑门电路 *3.4 砷化镓逻辑门电路 3.5 逻辑描述中的几个问题 3.6 逻辑门电路使用中的几个实际问题 * 3.7 用VerilogHDL描述逻辑门电路

3. 逻辑门电路

教学基本要求: 1.了解半导体器件的开关特性。 2. 熟 练 掌 握 基 本 逻 辑 门 ( 与 、 或 、 与 非 、 或 非 、 异 或 门)、三态门、OD门(OC门)和传输门的逻辑功能。 3.学会门电路逻辑功能分析方法。 4.掌握逻辑门的主要参数及在应用中的接口问题。

D

电路带电容负载

VDD

Rp L

1

0

CL

当VO=VOL

6. 扇入与扇出数

扇入数:取决于逻辑门的输入端的个数。

扇出数:是指其在正常工作情况下,所能带同类门输入端口 的最大数目

(a)带拉电流负载

当负载门的个数增加时,总的拉

电流将增加,会引起输出高电压

的降低。但不得低于输出高电平

的下限值,这就限制了负载门的

个数

高电平扇出数:

NOH

I OH (驱动门) IIH(负载门)

+10V

0V vI

+VDD

+10V S2 TP

D2

D1 vO

S1 TN

vi vGSN vGSP TN TP vO

0 V 0V -10V 截止 导通 10 V

10 V 10V 0V 导通 截止 0 V

逻辑真值表

逻辑表达式

vI(A)

0 1

vO(L)

1 0

逻辑图

L A

A1 L

2. 电压传输特性和电流传输特性

速度慢 与TTL不兼容 抗干扰 功耗低

74HC 74HCT

速度加快 与TTL兼容 负载能力强 抗干扰 功耗低

74VHC 74VHCT

速度两倍于74HC 与TTL兼容 负载能力强 抗干扰 功耗低

74LVC 74VAUC

低(超低)电压 速度更加快 与TTL兼容 负载能力强 抗干扰功耗低

2.TTL 集成电路: 广泛应用于中、大规模集成电路

3.1 MOS逻辑门

3.1.1 数字集成电路简介 3.1.2 逻辑门的一般特性 3.1.3 MOS开关及其等效电路 3.1.4 CMOS反相器 3.1.5 CMOS逻辑门电路 3.1.6 CMOS漏极开路门和三态输出门电路 3.1.7 CMOS传输门 3.1.8 CMOS逻辑门电路的技术参数

3.1.1 数字集成电路简介

两个串联的

输入管串联输入端增加时低电平抬高 NMOS T1、T2

2. 或非门电路

0B

• 当A、B全为低电平时

0A

输出为高电平

• 当A、B都为高电平时

输出为低电平

• 当A、B中有一个为高电平时

输出为低电平

1B

1A

L AB

思考:三输入“或非”门电路? 负载管串联输入端增加时高电平降低

V DD

T P2 T N2

0 G2 门 vI 范围

输入低电平的上限值 VIL(max)

输入高电平的下限值 VIL(min)

输出高电平的下限值 VOH(min)

输出低电平的上限值 VOH(max)

2. 噪声容限 在保证输出电平不变的条件下,输入电平允许波动的范围。它表

示门电路的抗干扰能力。

负载门输入高电平时的噪声容限: VNH —当前级门输出高电平的最小 值时允许负向噪声电压的最大值。

当输入电压不在正常电压范围时,二极管导通,限制了电容两端电 压的增加,保护了输入电路。

RS和MOS管的栅极电容组成积分网络,使输入信号的过冲电压延 迟且衰减后到栅极。

3.1.6 CMOS漏极开路(OD)门和三态输出门电路

1.CMOS漏极开路门 (1)CMOS漏极开路门的提出

A 输出短接,在一定情况下会产 B 生低阻通路,大电流有可能导 致器件的损毁,并且无法确定 输出是高电平还是低电平。

IBS=IB4

IB3

IB2

IB1

iB=0

A vCE

VCC

4. BJT的开关时间--延时特性

v1 +VB2

O –VB2

iC ICS 0.9ICS

0.1ICS O

tr td

t

t ts

tf

BJT饱和与截止两种状

态的相互转换也是需要

一定的时间才能完成的

开通时间 ton(=td+tr) ----建立基区电荷时间。 关闭时间 toff(= ts+tf) --存储电荷消散的时间.

MOS管工作在可变电阻区, 相当于开关“闭合”, 输出为低电平。

MOS管相当于一个由vGS控制的

无触点开关。

3.1.4 CMOS 反相器

1. CMOS反相器的电路组成

VDD>(VTN VTP )