图像采集系统设计

视频测量中图像采集系统的设计

( eat n f l t n n i ei ,h nagIstt f rnui l I i 啦 D p r t Ee r i E g er g S eyn tue0 Aeoa ta Eln me 0 c o c n n ni c g e ,hnag103 , h a Seyn 104 C i ) n

像分 辨率 也受制 式 限制 。其 次 , 这种 方 法 的 硬件 电

路 复杂 、 本较高 , 成 不利于推广 和普及 使用n 2。 I】

入的是 图像 , 出 的是 从 图像 中提 取 出来 的信息 。 输 被测物体 的光学像 , 首先需要 经过扫 描 , 通过光 学系

CO M S图像 传感器 是近 年发展 起 来 的一 种新 型 固体 图像 传感器 , 由于采用 了相 同的 C S工艺 , MO 因

Ab ta t sr c :W i h e eo me to o u e lcrnc tc niu het h i eo i e a u e n s t te d v lp n fc mp tra ee to i e h q e,t e n q fvd o me s rme ti h nd c u

K e r s i g a c ii o y wo d : ma e d t a q st n; s n o ; vd au e n ;DS a u i e s r i e mes r me t o P

0 引 言

视频测 量在石 油勘 探 、 矿 和农 产 品无损 检测 采 中可 以排 除疲劳等 主观 因素干 扰 , 免人 为 因素造 避

嵌入式高速图像采集系统设计

传统的数 字图像处理通 常以 P C机为平台, 但 这 种方 法处理 速 度 较 慢 , 够 灵 活 。随 着 固体 图像 不

传感 器 C D和 C S的 技 术 工 艺不 断 改进 以及 数 C MO

中的最 高性 能 的定 点 D PC 4C U, 有增 强 型 直 S 6x P 具 接 存储 器存 取控 制器 ( D ) 可 以通过 6 E MA , 4个独 立 的通 道 提供 超过 2 y /e Gbt se的 IO带 宽 ; e / 内部包 括 6 4个 3 2位字 长 的通用 寄存 器 以及 8个 独立 的运 算 单元 , 有两 个 专 用 硬 件 乘 法器 。D 6 2还 具 有 3 具 M4

摘 要: 图像数据 的高速 采集在视觉检测 中具有重要意义 , 提出了一种基于 D P C S图像传 感器的嵌 入式高速 图 S 、MO

像处理系统设 计方案。 以高性能数字信号处理器 T S2D 62 为硬件平 台 , 了图像数据的高速获取 。介绍 M 30 M 4 作 实现 了系统 中图像传 感器 、 存储设备 与 D P的硬件接 口设计及系统的软件流程及传感器控 制方式 , 出了利用 网络接 S 并提 口实现图像数据 向上位机传输 的方法 。 关键词 : S ;M S图像采集 ;D A ; D PC O ; S R M 网络传输

图 1 系统设计框

供了每一个像 素 1 0位的色彩分解力 , 具有接 口简 单, 控制功能丰富和信噪比高等的特点。 在本系统中, 选择 T 公 司的 D 62型 D P作 I M4 S

系 统 的 核 心 处 理 器 选 择 , 公 司 的 兀

T S 2 D 4 。D 4 M 3 0 M6 2 M6 2是 基 于 T S 2 C O o系列 M 3O 6o

无线图像采集系统的设计与实现

( o ee fnomao , SuhC i gi l rl nvr t G a gh u5 4 , C i ) C lg fr t n ot hn A r ut a U iesy un zo 16 2 hn l oI i a c u i, 0 a

中图法分 类号 : P 9 .1 T31 4

文献标 识码 : A

文章编号 :0 07 2 2 1) 10 1 4 10—0 4(0 10 .1O0

De i n a d i p e e t to fwie e si a e c p u i g s se sg n m l m n a i n o r l s m g a t rn y t m

Ab t a t W iee si g a t rn c n q eh s h d a tg s f o v n e c , f x b l y lw o t de s o to o e il sr c : r l s ma ec p u ig t h i u a ea v n a e c n e in e l i i t, o c s a a y c n r l ns mes ca e t o e i n i p v so n t r ga p ia in . A r ls g a t r g s se b s d o ii n mo i i p l t s o n c o wi e si e ma e c p u i y tm a e n ARM r h t cu ei d sg e n lm e td T e r — n a c i t r s e i n da di e mp e n e . h o p p s d s se i cu e wiee s a t r gn d a d r , i g a t i g d i e n o to d l, m a e c mp e so d ta s t o e y t m l d r ls p i o eh r wa e ma ec p u n rv ra dc nr l n c u n r mo u e i g o r s i n a n mi n r mo u e a d we — a e u a — c ie i tr ci n mo u e F rt f l k n so man te m mb d e lto msae f tr d o i d l n b b s d h m n ma h n e a t d l . i al i d f i sr a e e d dp a f r r l e , nt s n o so , i e h

高速CCD图像采集存储系统的硬件设计

第30卷 第6期2007年12月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.6D ec.2007Design of High 2Speed CCD Ima ge D a ta A cquisition H ar d w ar e SystemL I A i 2li n g1,2,Z H A N G Bo 2heng 1,B IA N Ch ua n 2p in g11.Xi ’an Ins ti t ute of Opt ics an d P recisi on Mechanics ,S haanx i Xi ’an 710068,Chi na;2.Gra duate School of Chi nese Academy of Science ,B ei J i n g 100039,Chi naAbstract :A hi gh 2speed ima ge dat a acquisit ion system wa s propo sed .Because of t he large amount of CCD i mage dat a ,t he syst em adopt ed fi bre channel hard di sk to store t he data and fi nally achieve a hi gh speed of850MB/s.Now It ha s been well applied i n t he course of CCD image dat a acquisition.K ey w or ds :CCD Ca mera ;LVDS ;Camlink ;CL FC ;Fi bre Channel EEACC :7220高速CCD 图像采集存储系统的硬件设计李爱玲1,2,张伯珩1,边川平11.中国科学院西安光学精密机械研究所,西安710068;2.中国科学院研究生院,北京100039收稿日期22作者简介李爱玲(832),女,博士研究生,主要研究方向为遥感D 相机图像数据的采集与处理,@;张伯珩(2),博士生导师,主要研究方向为遥感D 相机电路设计摘 要:针对某高速CCD 相机图像数据量大的特点,设计采用L VDS 格式信号输出,转换成Camlink 格式后实现海量数据的高速、稳定传输,提出了一种新型的高速数据采集存储系统的设计方案,该方案采用Fibre Cha nnel 接口硬盘实现对图像数据的高速存储,最高存储速度可达850Mbyte/s ,现已在CCD 相机系统图像采集实验中得到应用.关键词:CCD 相机;LVDS ;Camlink ;CL FC ;Fibr e Channel 中图分类号:TN 911.73 文献标识码:A 文章编号:100529490(2007)0622145203 CC D 相机被广泛应用于光电扫描、空间遥感、非接触工业控制、天文星体跟踪、光学图象处理等领域,CC D 相机所获取的目标信息,是我们所需要的宝贵信息,对其所获取的图像数据进行实时采集、存储和处理,高速、高精度的大量获取目标数据并进行实时信号处理,对目标的检测和识别非常重要.目前国内已有很多科研机构具备自行开发基于PCI 总线采集卡的实力,但在海量数据采集卡的开发方面还有待发展.当前有一种发展趋势是利用成熟的F P G A 技术和大规模集成芯片技术组合,通过高速大容量的FIFO 或者双端口RAM 作为数据缓存器,从而实现数据的高速采集.这种采集卡一般都通过PCI 接口与计算机系统连接,卡上带有PCI 桥控制器,使得使用者能够通过计算机对采集卡方便的进行控制.还有一些采集卡甚至将DMA 控制器和SCS I 控制器等设备都集成在其中,可以将采集到的数据不经过计算机总线而直接存储到SCSI 接口或其他接口的高速硬盘中,真正实现了采集与存储的结合,并且不受计算机系统的限制[1].1 采集系统的设计实现CCD 图像数据的采集与普通视频信号的采集相比,其最大的特点是数据传输速率高,传输通道多.通用的CCD 图像数据采集方法是在计算机中插入高速数据采集卡,采集卡与CCD 相机之间通过点对点物理层接口(如RS 2422、RS 2485)以及其他的数据传输标准进行数据传输,高速数据采集卡接收到数据通过PCI 总线将数据写入计算机内存,然后利用采集卡的存储功能将数据通过IDE (电子集成驱动器)接口写入计算机硬盘.首先,物理层接口无法满足数据的传输速度;其次,传输通道的增多,引起传输导线数量增加,系统功耗、噪声也随之增大;再次,采用通过IDE:20070422:19CC lal op 1942CC .接口来存储数据的方式无法满足数据高速存储的要求,容易引起数据帧的丢失.因此采用新的技术解决多通道、高速CCD图像数据采集成为必然趋势[2].C amlink接口技术为解决这一瓶颈问题提供了可能.本文通过应用Camlink接口技术,提出了一种适用于高速、海量CCD图像数据的采集系统.通过调试,该系统运行正常,完全能满足图像数据稳定、高速传输的要求,并实现图像数据的高速存储.在本系统中,CCD相机输出的数字信号为4通道8bi t并行同步L VDS格式数据,数据时钟为25 MHz,每通道的数据量58.01~87.46Mbyt e/s,如此高的数据吞吐量要求系统设计具有高速传输的特性.根据以上分析要求,设计了采集系统的硬件结构框图如图1所示.图1 采集系统结构框图如图2所示,CCD视频处理电路差分输出采集系统所需的像元时钟DCL K、行同步LVAL等2路信号和4路8bit图像数据,经由MLC(LVDS2Cam2 Li nk信号转换器)转换成符合采集卡接口标准的CamLink Medi um信号格式.然后在CL FC采集卡接口处,该CamLi nk格式的输入数据经过CL FC接收后可以不经过PCI总线,而是直接在磁盘控制器的控制下,存储到Fi ber Cha nnel接口硬盘,使得存储和实时显示同时进行成为可能.通过应用程序可以实现实时显示图像功能,也可以将已存到F C硬盘中图像数据导出到计算机硬盘进行处理和应用.图2 输出信号时序图1.1 数据传输设计Camlink接口采用美国Nat io nal Semiconduc2 tor公司的Cha nnel li nk技术作为基础,Channel 技术是低电压差分信号LVDS技术在数字领域的最新成果,它使用并行2串行的发送和串行2并行的接收,数据传输率可以达到38G如图3所示,发送端将28bit的CMO S/TTL数据转换成4路L VDS数据流,第五路LVDS数据流传送稳定的锁相时钟信号.每一个时钟周期,完成一次28bi t数据的采样和传输.在接收端,数据流被还原为28bi t 的CMO S/TTL数据,接收和发送完全同步.图3 Channel link标准接口模块电路图Camli nk采用数据线复用的方法,实实在在地减少了传输电缆的导线数目.这样可以使电缆加工容易,屏蔽要求降低,电缆接插件体积减小、强度增加,电缆价格也随之降低.单个的Ca mli nk芯片组可以传送高达2.38Gbit/s数据带宽,Camli nk标准允许采用两个这样的芯片组,如此高的数据传输能力不仅能满足目前应用,而且在将来相当长时间内不会落后.在本系统中,为了实现图像数据的高速稳定传输,我们充分利用了Camli nk的以上优点,设计了L VDS2Camlink信号转换器.在本系统中,转换器MLC的结构图如图4所示,ML C首先接收来自信号模拟源的LVDS输出图4 转换器硬件结构图信号,经过LVDS接收器件DS90C032,还原为TTL 信号.Camli nk驱动芯片选用National Semic onductor 公司的DS90CR287,它的输入信号和电源的电压要求均为3.3V,为了做到两种信号的电平匹配,在中间增加了多片IDT74LVCC4245A总线驱动器.I DT74LVCC4245A有两个电源输入端,一端只能加5 V电源,另一端可以加5V或33V,因此当它一端的输入电平是5V信号时,另一端可以是5V或33V 信号I D T LV5是双向器件,在接收端也可6412电 子 器 件第30卷link2.bit/s... .74CC424A以再转换成5V 电平的信号.经过DS 90CR287后,输出的Channel link 信号,最终通过符合Camlink 标准的MDR26接口连接到采集卡.1.2 数据的采集与存储为了保证CCD 图像数据在不出现丢帧现象的同时以更高速度被存储到硬盘,我们采用了I O Indus 2t ries 公司最新的采集卡DVR Express CLFC ,它的突出特点是采用FC 接口硬盘对图像进行存储,最高可以达到850Mbyte/s.其硬件结构如图5所示.图5 CL FC 采集卡结构框图通过符合Camli nk 标准的MDR26接口,Cam 2link 格式的图像数据在接口处被还原为T TL 信号,F PGA 集成了缓存、电平转换、DMA 控制器等功能,完成和PCI 总线之间的数据和控制命令传递.图像数据直接在磁盘控制器的控制下,存储到Fi ber Channel 接口硬盘,这样可以大大的节省图像数据对PCI 总线的占有率,从而提高整个采集系统的速度.FC 技术的应用,使得本系统的采集速度与以往的采集系统相比较得到很大提高.Fiber Channel 光纤通信(FC )是一种通过光纤实现的基于块的数据流传输方式,传输率可达1G bit/s ,多模光纤传输距离为500m ,单模光纤距离为1km.Fiber Channel 技术的最大特点是将网络和设备或服务器和设备的通信协议与物理传输介质隔离开,这样多种协议可以在同一个物理连接上同时传送.FC 传输速度快,它可以提供接近于设备处理速度的吞吐量,提供从266Mbit/s 到4G bit/s 的传输带宽,支持超过10km 的传输距离;它是一种通用传输机制,支持HIPPI\IPI\SCSI \IP\ATM 等多种高级协议.FC 技术对于视频图像和海量数据的存储及传输极为理想,现已成为视频传输与存储领域具有强大生命力的新技术.与SCSI 硬盘接口相比较,FC 接口硬盘有以下优点:Fiber Channel 通道比SCSI 总线有更巨大的存储容量;与SCSI 接口相比,Fiber Channel 接口允许使用更长的电缆,而接口体积更小[6] 根据以上分析,我们对存储部分的设计最终采用了FC 接口技术和RAID3磁盘阵列技术.根据数据量需要,采用了4块日立公司最新推出的FC 接口硬盘组成磁盘阵列,实验证明,存储部分设计很好地满足了整个系统的需要.图6 辨别率靶的采集图像2 结论本系统通过调试,已成功地应用于某高速CCD 相机系统的图像数据采集,如图6所示为该系统采集到的CC D 相机室内拍摄辨别率靶的图像.通过软件对存储数据的恢复分析,数据正确,无丢帧现象,无数据错误.系统通用灵活,稳定可靠,能满足多种CCD 图像数据的实时采集,为多通道高速CC D 图像数据的实时采集提供了解决方案,因而有着广泛的应用前景.参考文献:[1] 李爱玲.数字图像信号的模拟与采集技术研究.中国科学院西安光学精密机械研究所,硕士毕业学位论文,2006.[2] 王琳琅,张伯珩,边川平.多通道、高速CCD 图像数据的实时采集,中国有线电视.2004.12.22224.[3] 达选福,张伯珩,边川平.高速CCD 图像数据存储技术.光子学报,2003.32.139321395.[4] 王冰,靳学明.LVDS 技术及其在多信道高速数据传输中的应用.电子技术应用,2003.3.55256.[5] 林强,熊华刚,张其善.光纤通道综述,计算机应用技术.2006.2.9213.[6] 杨进,魏轶伟,何宁,熊剑平,贾惠波.基于光纤通道的高速数据传输系统主机接口设计,计算机工程与应用.2002.22.1372138,176.[7] 李春兰,陈宇,丁铁夫.探地雷达中PC I 总线高速数据采集卡的设计.电子工程师.2004.7.4223.[8] Camera Li nk Technolo gy B ri ef.Docu m ent ID Number :DD000601,Revi s io n Date :March 28,2001.Subj ect t o Change Wit hout No tice ,Bas l er Vi s io n Technologies.7412第6期李爱玲,张伯珩等:高速CCD 图像采集存储系统的硬件设计.。

基于ARM-Linux的图像采集和无线传输系统设计

X cl P A 7 理 器 连 接 了一 个 6 Mbt N N l载 程序 和 内核 映像 , 并作 为根 文件 系统 ,4 y 6 Mbt e S R M 作 为 内存 , S I 接 无 线 网卡 , S 2连 接 摄 像 头 。 系 D A UB 连 UB

d i1 . 9 9 j i n 1 7 — 4 . 0 0 0 . 1 o :0 3 6 / . s . 6 11 1 2 1 . 5 0 2 s 0

基 于 A M- iu R Ln x的 图像 采 集 和 无 线 传 输 系统 设 计

田泽 康 , 德 华 李

( 中科技 大学 图像 识别 与人 工智 能研 究所 , 汉 4 0 7 ) 华 武 3 0 4

图像采集和传输系统 的硬件系统 由开发板 、 by 30 WeeeV 0 0 U B摄像头 、 S 中兴 MF7 U无线网卡等构成 , 图 2所示 。 63 如

De i n o sg fARM - n x-a e m a e a q iii n - u - s d i g c u sto Li b a d r ls r n m iso s se n wiee s ta s s in y t m

摘 要 : 绍 了一 种 基 于 嵌 入 式 l u 介 i x的 实 时 图 像 监 控 系统 的 设 计 和 实 n 现方 法 。 系统 以 X c l P 2 0处 理 器为 核 心 , 载 US sae XA 7 搭 B摄 像 头 和 无 线 网卡 构 成 硬 件 平 台 。 Ar Liu 以 m- n x为 软 件 平 台 。 该 平 台 上 实 现 了 在 实 时 图像 的 采 集 , E 4压 缩 和 3 无 线 传 输 。M P MP G- G EG- 法 的 采 4算 用减 小 了网 络 的 压 力 。 节 约 了成 本 。 随 着 3 网 络 的 不 断 发 展 , 系 又 G 本 统将在 3 G时代有着广阔的应用前景。 关键 词 :图 像 采 集 ; 入 式 系 统 ; C 嵌 W DMA;A m- iu r Ln x 中 图分 类 号 :T 2 P7 文 献 标 志 码 :A

静态图像信息采集系统设计与实现

人 工 智 能 及 识 别 技 术

Ke r s a r I g pu e Dep i AP ; l pn y wo d :C mea; ma eCa trd; lh ; i ci ig p

l 引言

在工作生活中经常要用到 Q Q等聊 天工具 ,这 些聊 天工具

寸 ) 的图 片 。

()实现图片保存 ,设计 的抓图窗 口如图 1 3 所示 。

下 该 时刻 对 方 的 形 象 。

其实 ,摄像头 作为一个 影像捕 捉工具 ,也经 常应用在 数 据库系统 的照片采集工作中。D lh是数据库开发的利器 ,利 ep i 用它进行数据 库应用系 统前端开发 ,效率相 当高 。那么 ,在 Dl i e h 中如何实现摄像头静 态图像抓取 、裁剪 和保存 功能呢 ? p

文中将提供一个完整的解 决方 案。

2 实现

21 硬 件 .

计算机、摄像头 。

22 软 件 .

图 1

2 . 打开摄像头 .1 3

摄像 头驱动 程序 、后 台数 据库 ( 比如 S LSre2 0 ) Q e r00 、 v 前端开发工具 D lh。 ep i

23 实 施 步 骤 .

Ab t a t s r c :Ca r s u e o c p u e i g s o h o l.D l h s c mmo l s d a h e eo me tt li r n ft e me a i s d t a t r ma e ft e t os e p ii o n y u e s t e d v lp n o n fo to h

电脑编程技巧与维护

静态 图像信息采集 系统 设计与实现

姚 文声

( 济南铁路高级技工学校 ,济南 2 0 ) 5 17 1

图像数据采集系统的设计流程

图像数据采集系统的设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!图像数据采集系统的设计流程一般包括以下几个步骤:1. 需求分析:明确系统的功能和性能要求,例如采集图像的分辨率、帧率、颜色深度等。

基于FPGA的图像采集系统设计与实现

基于FPGA的图像采集系统设计与实现作者:陈法领、罗海波发布时间:2009-03-101、引言视频图像采集是视频信号处理系统的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向发展。

图像采集系统在当今工业、军事、医学各个领域都有着极其广泛的应用,如使用在远程监控、安防、远程抄表、可视电话、工业控制、图像模式识别、医疗器械等各个领域都有着广泛的应用[1]。

本文介绍了一种基于FPGA的图像采集系统,用户可以根据需要对FPGA 内部的逻辑模块和I/O模块重新配置,以实现系统的重构[1][2];而且采用这种设计方案,便于及时地发现设计中的错误,能够有效地缩短研发时间,提高工作效率。

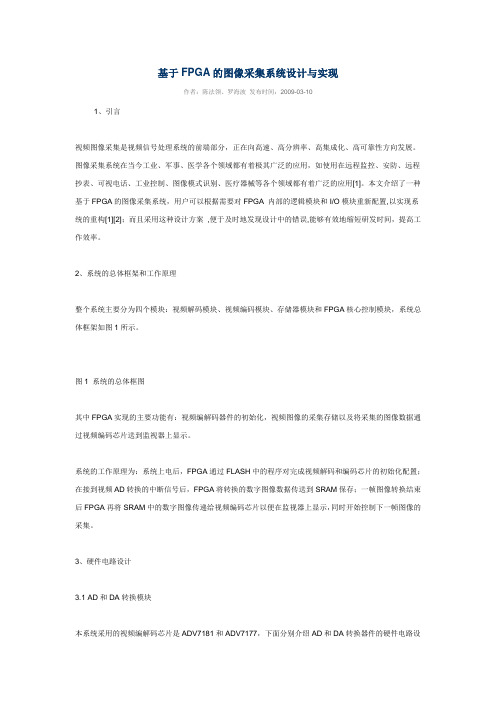

2、系统的总体框架和工作原理整个系统主要分为四个模块:视频解码模块、视频编码模块、存储器模块和FPGA核心控制模块,系统总体框架如图1所示。

图1 系统的总体框图其中FPGA实现的主要功能有:视频编解码器件的初始化,视频图像的采集存储以及将采集的图像数据通过视频编码芯片送到监视器上显示。

系统的工作原理为:系统上电后,FPGA通过FLASH中的程序对完成视频解码和编码芯片的初始化配置;在接到视频AD转换的中断信号后,FPGA将转换的数字图像数据传送到SRAM保存;一帧图像转换结束后FPGA再将SRAM中的数字图像传递给视频编码芯片以便在监视器上显示,同时开始控制下一帧图像的采集。

3、硬件电路设计3.1 AD和DA转换模块本系统采用的视频编解码芯片是ADV7181和ADV7177,下面分别介绍AD和DA转换器件的硬件电路设计。

3.1.1 AD转换模块ADV7181系统是AD公司推出的一款视频解码芯片[3],它具有如下特点:I2C总线接口,6通道模拟视频输入,支持NTSC、PAL、SECAM视频制式,支持多种模拟输入格式和多种数字输出格式。

本系统中选用其中的通道1作为PAL制CVBS视频输入,数据输出可根据需要采用8位或16位的格式输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP实习报告题目:图像采集系统的设计班级:xxx姓名:xxx学号:xxx指导老师:xxxx目录一.实习题目 (3)二.实习背景知识 (3)三.实习内容 (5)四.实习程序功能与结构说明 (8)六.实习心得 (19)一、实习题目图像采集系统的设计二、实习目的:1、熟练掌握数字信号处理的典型设计方法与技术手段;2、熟悉D6437视频输入,输出端的操作及编程。

;3、掌握常用电子仪器设备的使用方法;4、熟悉锐化变换算法。

三、实习背景知识1、计算机2、CCS3.3.软件3、DSP仿真器4、EL_DM6437平台EL-DM6437EVM是低成本,高度集成的高性能视频信号处理开发平台,可以开发仿真达芬奇系列DSP应用程序,同时也可以将该产品集成到用户的具体应用系统中。

方便灵活的接口为用户提供良好的开放平台。

采用该系列板卡进行产品开发或系统集成可以大大减少用户的产品开发时间。

板卡结构框图如图所示:板卡硬件资源:TMS320DM6437 DSP ,可工作在400/600 MHz;2 路视频输入,包括一个复合视频输入及一个S端子视频输入;保留了视频输入接口,可以方便与CMOS影像传感器连接;3 路视频输出,包括2路复合视频,一路S端子输出;128MByte 的DDR2 SDRAM存储器,256MBit的Nor Flash存储器;用户可选的NAND Flash接口;可选的256K字节的I²C E²PROM;1个10M/100Mbps自适应以太网接口;1 路立体声音频输入、1路麦克风输入,1路立体声音频输出;USB2.0高速接口,方便与PC连接;1个CAN总线、1个UART接口、实时时钟(带256Byte的电池保持RAM);4个DIP开关,4个状态指示LED;可配置的BOOT模式;10层板制作工艺,稳定可靠;标准外部信号扩展接口;JTAG仿真器接口;单电源+5V供电;板卡软件资源:完整的DSP示例程序及实验指导书;USB演示软件,及读写示例C++程序;功能概述:EL-DM6437EVM 达芬奇视频开发板通过专用的DDR2存储控制器接口扩展了64MBytes的DDR2 SDRAM,为视频应用带来了高吞吐、高容量存储带宽,并可以扩展到最大256MByte;256MBit的Nor Flash为视频应用程序脱机运行提供了有力的容量保证;板卡通过一个视频解码芯片和CPU连接,使得CPU可以接受外部的复合视频信号输入和S信号输入,信号都是自动检测,大大提高了视频处理的灵活性;CPU还提供视频DAC,通过几个运算放大器即可把DDR2存储器内的数据输出为用户可观察到的信号,非常方便;除此之外,板卡还包括很多资源,包括音频输入输出、10M/100M的自适应以太网接口、USB2.0接口、实时时钟、4位LED 指示和4位DIP开关量输入、CAN总线及UART接口等等一系列功能;最重要的是所有外部存储器接口信号都连接到扩展接口上,用户可以通过设计外部子板扩展自己的功能。

板上还包括灵活的端口复用切换,使得用户可以根据不同场合使用不同的端口配置,最大的利用CPU各种功能。

板卡通过标准接口提供电源输入,采用单5v的供电方式,注意供电电流需要大于1安培,电源调节模块为微处理器及其他外设提供3.3V和1.04/1.2V(对应不同频率CPU)电压。

在使用该系列板卡开发过程中可以通过J1接口连接仿真器。

四、实习内容:1. 连接好电脑和仿真器,EL_DM6437和仿真器;2. 用视频线一头连接板卡的P3或者P5,另一头连接显示器的AV输入,并调制AV模式;注:如果带转接头的话,AV输入应该是黄色端子。

3. 用视频线连接摄像头输出和板卡的F9插座,注意摄像头输出制式为PAL;4. 给EL_DM6437和摄像头上电,打开CCS并连接;5. 打开ColorSharpen文件夹的工程ColorSharpen.pjt,此工程功能为:把摄像头捕捉到的一副图像进行锐化处理,并将之输出到显示器;6.编译源程序7. 下载程序out文件,如果没有就先编译一下Project—》Build;8. 把摄像头对准需要捕捉的图像场地;9. 设置第一个断点,在video_test.c的422行处;10. 点击运行,稍等片刻后程序停止在断点,此时可以从显示器看到图像;11.继续点击运行,如果成功,显示出锐化图像;并显示这时可以发现显示屏显示出摄像头所指影像已被锐化。

11.结束注:1)锐化算法最简单思想是前一个象素取后一象素与本身的差值;五.实习程序与结构说明/** Copyright 2007 by Techshine Incorporated.* All rights reserved.* Author: lyj*//** Video Test**/#include "tvp5146.h"#define COLORBARS 1#define LOOPBACK 0#define SVIDEO_OUT 1#define COMPONENT_OUT 0typedef struct __RGBC{Uint8 Red;Uint8 Green;Uint8 Blue;}RGBCOLOR;void PictureSharpen(Uint32 memaddr);/* ------------------------------------------------------------------------ ** ** vpfe_init( ) ** ** NTSC: ** Width: 720 ** Height: 480 ** ** ** ------------------------------------------------------------------------ */void vpfe_init( Uint32 buffer, Uint32 width, Uint32 height ){//同步、模式设置VPFE_CCDC_SYN_MODE = 0//0x00032F84; // interlaced, with VD pority as negative|(0<<19) //使能SDRAM端口输出到resizer的输入,0=disable|(0<<18) //使能视频口video port,输出到SDRAM,0=disable|(1<<17) //数据写使能,控制CCD列数据是否写入DDR,0=disable|(1<<16) //vd/hd使能,如果hd、vd定义为输出,那么内部产生时序,否则外部产生|(0<<15) //Field状态,表明当前的field状态,0=奇场,1=偶场|(0<<14) //3 tap低通滤波器,0=off|(2<<12) //INPMOD 数据输入模式,0=CCD Raw,1=YCbCr 16bit,2=YCbCr 8bit,3保留|(1<<11) //每个象素的包大小,0=16bit/pixel,1=8bit/pixel|(7<<8) //ccd 数据宽度,只有INPMOD=0(12bit-13bit)时有效// 0=16bit,1=15bit,2=14bit,3=13bit,4=12bit// 5=11bit,6=10bit,7=8bit|(1<<7) //传感器场模式,0=逐行扫描,1=隔行|(0<<6) //CCD数据极性|(0<<5) //外部WEN信号选择,如果VDHDEN=1(16bit),设置此位将使CCD数据加载到DDR// 0=不使用|(0<<4) //场指示器极性,0=正极,1=负极|(0<<3) //HD同步极性,0=正极,1=负极|(1<<2) //VD同步极性,0=正极,1=负极|(0<<1) //场ID方向,0=输入,1=输出|(0); //VD、HD同步方向,0=输入,1=输出VPFE_CCDC_HD_VD_WID = 0; //HD,VD信号脉冲宽度寄存器VPFE_CCDC_PIX_LINES = 0x02CF020D; //每行的水平象素,及一帧的行数//0|(0x2cf<<16) //每行的水平象素719+1=720//|(0x20d) //每帧或每场的半行数525+1=526/** sph = 1, nph = 1440, according to page 32-33 of the CCDC spec* for BT.656 mode, this setting captures only the 720x480 of the* active NTSV video window*/VPFE_CCDC_HORZ_INFO = width << 1; // Horizontal lines//水平象素信息,(31-16)=开始象素,(14-0)=输入到DDR的每行象素个数VPFE_CCDC_HSIZE_OFF = width << 1; // Horizontal line offset// 水平大小,(15-0)=每行的地址偏移,即跳行到DDR2读取数据?// 5 lsb 忽略,最好是256字节的倍数VPFE_CCDC_VERT_START = 0; // Vertical start line// 垂直线开始象素(16-31)=SLV0(Field0),(0-14)=SLV1(Field0)// 设定数据输入到DDR的开始行VPFE_CCDC_VERT_LINES = height >> 1; // Vertical lines(14bit-0)// 垂直线的线数VPFE_CCDC_CULLING = 0xFFFF00FF; // Disable cullng,水平及垂直方向的选择方式//(31-24)=偶场的水平选择,(23-16)=奇场的水平选择// (15-8)=保留,(7-0)=垂直选择模式/** Interleave the two fields*/VPFE_CCDC_SDOFST = 0//0x00000249; //DDR线偏移|(0<<14) //场标志信号翻转,0=正常|(0<<12) //场线偏移,0=+1线,1=+2线,2=+3线,3=+4线,|(1<<9) //偶线和偶场的线偏移,0=+1,1=+2,2=+3,3=+4,4=-1,// 5=-2,6=-3,7=-4,|(1<<6) //奇线和偶场的线偏移,0=+1,1=+2,2=+3,3=+4,4=-1,// 5=-2,6=-3,7=-4,|(1<<3) //偶线和奇场的线偏移,0=+1,1=+2,2=+3,3=+4,4=-1,// 5=-2,6=-3,7=-4,|(1<<0); //奇线和奇场的线偏移,0=+1,1=+2,2=+3,3=+4,4=-1,// 5=-2,6=-3,7=-4,VPFE_CCDC_SDR_ADDR = buffer; //buffer DDR地址,最低5位忽略VPFE_CCDC_CLAMP = 0//; //可选的黑色箝位设置|(0<<31) //CLAMPEN ,CLAMP使能,0=禁止|(0<<28) //采样象素长度,0=1pixel,为2^N(次幂),5-7保留|(0<<25) //采样线长度,0=1 line,为2^N(次幂),5-7保留|(0<<10) //采样的开始象素|(0<<0); //bit4-bit0,平均增益VPFE_CCDC_DCSUB = 0; //CCD数据要减去的值,当CLAMPEN=0时有效VPFE_CCDC_COLPTN = 0xEE44EE44; //调色板设置//0|(0<<30) //第三线调色板,3个象素,0=R,1=Gr,2=Gb,3=B//|(0<<28) //CP3LPC2,象素个数=2//|(0<<26) //CP3LPC1,象素个数=1// |(0<<24) //CP3LPC0,象素个数=0// |(0<<22) //第二线调色板// |(0<<20)// |(0<<18)// |(0<<16)// |(0<<14) //第一线调色板// |(0<<12)// |(0<<10)// |(0<<8)// |(0<<6) //第0线调色板// |(0<<4)// |(0<<2)// |(0<<0);VPFE_CCDC_BLKCMP = 0; //黑色补偿//0|(0<<24) //R红色//|(0<<16) //Gr// |(0<<8) //Gb// |(0<<0); //B蓝色VPFE_CCDC_FPC_ADDR = 0x86800000; //不知道干吗用的VPFE_CCDC_FPC = 0;VPFE_CCDC_VDINT = 0; //VD中断时序,(30-16)=VDINT0,(14-0)=VDINT1 VPFE_CCDC_ALAW = 0; //a 率设置VPFE_CCDC_REC656IF = 0//0x00000003; //rec656接口|(1<<1) //FVH错误纠正使能|(1<<0) ; //Rec656接口使能/** Input format is Cb:Y:Cr:Y, w/ Y in odd-pixel position*/VPFE_CCDC_CCDCFG = 0//0x00000800; //CCD配置寄存器|(0<<15) //使能VSYNC内部的锁存功能,0=使用VSYNC锁存|(0<<13) //MSBINVI,色度输入信号最高位是否在SDRAM中翻转,0=正常|(0<<12) //DDR的字节是否交换,如果字节包已经使能,象素个数必须为偶数// 0=正常|(1<<11) //YCbCr 8bit输入时Y的位置,0=偶像素,1=奇象素|(0<<8) //指定CCD有效范围,0=当WEN为逻辑“与”时内部信号有效,反之为“”|(0<<6) //FID检测,0=VSYNC时序锁存FID信号,1=不锁存,2=VD 边缘锁存,3=VD、HD的相位决定|(0<<5) //CCIR656输入数据宽度,0=8bit,1=10bit|(0<<4) //YCINSWP,YI输入和CI引脚输入交换,0=不交换|0;VPFE_CCDC_FMTCFG = 0; //数据重新格式化、图象口配置//0|(0<<16) //图象口数据准备好频率,跟内核频率有关,0=CoreClock*1/2=75MHz//|(0<<15) //video port 使能// |(0<<12) //video port输入选择,0=bit 15~6// |0;VPFE_CCDC_FMT_HORZ = 0//0x000002D0; //数据重新格式化、图象输入接口水平信息|(0<<16) //bit31~29保留,从HD开始的水平开始象素|(0x2D0<<0) //bit15~13保留,水平方向的象素个数=0x2d0=720|0;VPFE_CCDC_FMT_VERT = 0//0x0000020E; //数据重新格式化、图象输入接口垂直信息|(0<<16) //bit31~29保留,从vd开始的水平开始象素|(0x20e<<0) //bit15~13保留,水平方向的象素个数=0x20e=526|0;VPFE_CCDC_FMT_ADDR0 = 0;VPFE_CCDC_FMT_ADDR1 = 0;VPFE_CCDC_FMT_ADDR2 = 0;VPFE_CCDC_FMT_ADDR3 = 0;VPFE_CCDC_FMT_ADDR4 = 0;VPFE_CCDC_FMT_ADDR5 = 0;VPFE_CCDC_FMT_ADDR6 = 0;VPFE_CCDC_FMT_ADDR7 = 0;VPFE_CCDC_PRGEVEN_0 = 0;VPFE_CCDC_PRGEVEN_1 = 0;VPFE_CCDC_PRGODD_0 = 0;VPFE_CCDC_PRGODD_1 = 0;VPFE_CCDC_VP_OUT = 0//0x041A2D00; //video port输出设置|(0x20d<<17) //被时钟输出到video port的垂直线数=0x20d=525|(0x2d0<<4) //被时钟输出到video port的水平线数=0x2d0=720|(0<<0); //每个输出行的水平开始象素=0VPFE_CCDC_PCR = 0x00000001; // Enable CCDC,bit1=是否busy,bit0=enable//如果禁止的话,CCDC会向DSP发送中断,不需要中断需要配置INTC}/* ------------------------------------------------------------------------ ** ** vpbe_init( ) ** ** NTSC: ** Width: 720 ** Height: 480 ** ** ** ------------------------------------------------------------------------ */void vpbe_init( Uint32 buffer, Uint32 width, Uint32 height, Uint32 colorbar_loopback_mode, Uint32 ntsc_pal_mode, Uint32 output_mode ){Int16 basep_x;Int16 basep_y;RGBCOLOR rc;if ( ntsc_pal_mode == NTSC ){basep_x = 0x7A; // 122basep_y = 0x12; // 18}else{basep_x = 0x84; // 132basep_y = 0x16; // 22}/** Setup VPBE*/VPSS_CLK_CTRL = 0x00000018; // Enable DAC and VENC clock, both at 27 MHz VPBE_PCR = 0; // No clock div, clock enable/** Setup OSD*/VPBE_OSD_MODE = 0//0x000000fc; // osd模式寄存器// 最后8位指定背景色地址(ROM0)|(0<<15) //cb/cr顺序,0=cb/cr,1=cr/cb (修改这个1会把背景变红)|(0<<14) //osd窗口垂直扩展使能,如果使能,bitmap窗口//Y值将延伸为6/5。