行为级建模分析

行为级建模

Page 26

case语句类似于多路选择器,下面使用case语句实现四选一多路选择器。

Page 27

case语句逐位比较表达式的值和候选项的值,每一位的值可能是0,1,x或 z。上例中只考虑0和1的情况,将x和z的情况归结为default。我们也可以将 这部分进行单独的说明,如下:

所有在initial语句内的语句构成了一个initial块。initial块从仿真0时刻开始执 行,在整个仿真过程中只执行一次。 如果一个模块中包括了若干个initial块,则这些initial块从仿真0时刻开始并 发执行,且每个块的执行是各自独立的。 如果在块内包含了多条行为语句,那么需要将这些语句组成一组,一般是 使用关键字begin和end将它们组合为一个块语句;如果块内只有一条语句, 则不必使用begin和end。

7.3时序控制

7.3.1 基于延迟的时序控制 Verilog提供了三种时序控制方法:基于延迟的时序控制、基于事件的时序 控制和电平敏感的时序控制。

基于延迟的时序控制出现在表达式中,它指定了语句开始执行到执行完成 之间的时间间隔。

延迟值可以是数字、标识符或表达式,需要在延迟值前加上关键字#。对于 过程赋值,Verilog提供了三种类型的延迟控制:常规延迟控制、赋值内嵌 延迟控制和零延迟控制。

Page 5

7.1.2 always语句

always语句包括的所有行为语句构成了一个always语句块。该always语句 块从仿真0时刻开始顺序执行其中的行为语句;在最后一条执行完成后,再 次开始执行其中的第一条语句,如此循环往复,直至整个仿真结束。

always语句通常用于对数字电路中一组反复执行的活动进行建模。例如时 钟信号发生器,每半个时钟周期时钟信号翻转一次。在现实电路中只要电 源接通,时钟信号发生器从时刻0就有效,一直工作下去。

Simulink环境下的SAR ADC行为建模与仿真分析

Simulink环境下的SAR ADC行为建模与仿真分析韩笑;孙玲;吴秀山【摘要】逐次逼近型模/数转换器由于电路复杂度较低,且功耗和速度等性能可以随着集成电路工艺的进步而不断提升,在高速、高精度ADC设计中被广泛应用.借助Matlab软件环境下的Simulink工具,该文以14位SAR ADC为例给出了电路的行为级建模方法,分析了SAR ADC采样频率、输入信号频率以及内部时钟之间的关系,充分讨论了Simulink下各模块的具体实现并给出了仿真结果.该分析为SAR ADC的晶体管极电路设计与实现提供了重要参考依据.%The analog-to-digital converter (ADC) of the successive approximation register (SAR) has been widely used in the design of the high-speed and high-precision ADC because its circuit complexity is low,and its performances such as power dissipation and speed can be constantly improved with the improvement of the integrated circuit technique.By virtue of the Simulink tool under Matlab software environment,the 14-bit SAR ADC is taken as an example to give the behavior modeling method of the circuit,and the relationship among the sampling frequency,input signal frequency and internal clock of SAR ADC is analyzed.Each module implemented with Simulink is discussed,and the simulation results are given.The simulation analysis provides an important reference for the design and implementation of the transistor circuit of SAR ADC.【期刊名称】《现代电子技术》【年(卷),期】2017(040)006【总页数】4页(P136-139)【关键词】模/数转换器;逐次逼近型结构;行为级建模;Simulink【作者】韩笑;孙玲;吴秀山【作者单位】南通大学电子信息学院,江苏南通226019;南通大学电子信息学院,江苏南通226019;中国计量学院机电工程学院,浙江杭州 310018【正文语种】中文【中图分类】TN911-34;TN492近年来电子技术发展迅猛,随处可见的电子产品不仅使人们的日常生活变得更加便捷,还丰富了人们的娱乐生活。

连载《fpga线下培训-第6天》【FPGA数据流建模、行为级建模、结构化建模区别】及【Ve。。。

连载《fpga线下培训-第6天》【FPGA数据流建模、⾏为级建模、结构化建模区别】及【Ve。

这篇⽂件记录,FPGA的3种建模⽅式及基本的Verilog HDL语法,内容会根据学习进度,不断更新⼀、FPGA的3种建模⽅式 A、数据流建模(assign)在数字电路中,信号经过组合逻辑时会类似于数据流动,即信号从输⼊流向输出, 并不会在其中存储。

当输⼊变化时,总会在⼀定时间以后体现在输出端 同样,我们可以模拟数字电路的这⼀特性,对其进⾏建模,这种建模⽅式通常被称为数据流建模 1.1、是使⽤连续赋值语句(assign)对电路的逻辑功能进⾏描述,该⽅式特别便于对组合逻辑电路建模 1.2、连续驱动,连续赋值语句是连续驱动的,也就是说只要输⼊发⽣变化,都会导致该语句的重新计算。

1.3、只有线⽹型的变量才能在assign语句中被赋值 1.4、因为assign语句中被赋值的变量,在仿真器中不会存储其值,所以该变量必须是线⽹(Nets)类型,不能是寄存器(reg)类型 1.5、线⽹类型的变量,可以被多重驱动,也就是说可以在多个assign语句中驱动同⼀个net 1.6、reg型变量,不能被不同的⾏为进程(eg:always块)驱动 1.7、建议使⽤assign对组合逻辑建模,这是因为assign语句的连续驱动特点与组合逻辑的⾏为⾮常相似, ⽽且在assign语句中加延时可以⾮常精确地模拟组合逻辑的惯性延时。

1.8、assign语句与⾏为语句块(always和initial)、其它连续赋值语句、门级模型之间是并⾏的。

⼀个连续赋值语句是⼀个独⽴的进程,进程之间是并发的,同时也是交织的 B、⾏为级建模(initial、always) ⾏为⽅式的建模是指采⽤对信号⾏为级的描述(不是结构级的描述)的⽅法来建模。

在表⽰⽅⾯,类似数据流的建模⽅式,但⼀般是把⽤initial 块语句或always 块语句描述的归为⾏为建模⽅式。

基于用户行为分析建立用户偏好模型

基于⽤户⾏为分析建⽴⽤户偏好模型我们经常将个性化推荐的思想简单地抽象为:通过⽤户的⾏为推测出⽤户的兴趣,从⽽给⽤户推荐满⾜他们兴趣的物品。

那我们其实就是要通过⽤户⾏为分析建⽴⼀个⽤户偏好(偏好即兴趣)模型,模型中包含各个⽤户的⼀个或更多个偏好。

插叙⼀段像「⽤户⾏为」,「⽤户兴趣」这样的词,⼤多数⼈都有⼀个默认的感知,甚⾄对于这种词的理解可能已固化为常识,所以我很少见到有⽂章使⽤这些词时解释它们。

我感觉涉及到算法模型时,对这些词的不加限定的宽泛认知就容易影响对算法模型的深⼊理解,会导致感知模糊却不⾃知。

因为不同⼈对这些词的基本理解可能⼀致,但是拓展理解各不相同。

本⽂会作出限定解释,且本⽂所谈⽤户⾏为都是指⽹络(可以是电信⽹络,互联⽹)上的⾏为。

概念解释实体域当我们想基于⽤户⾏为分析来建⽴⽤户偏好模型时,我们必须把⽤户⾏为和兴趣主题限定在⼀个实体域上。

个性化推荐落实在具体的推荐中都是在某个实体域的推荐。

⽐如对于阅读⽹站,实体域包括所有的图书,我们可以称之为图书域。

其他还有,个性化⾳乐推荐,个性化电影推荐,个性化资讯推荐等。

⽤户⾏为⽤户在门户⽹站点击资讯,评论资讯,在社交⽹站发布状态,评论状态,在电商⽹站浏览商品,购买商品,点评商品,以及在其他类型⽹站的种种⾏为都可是⽤户⾏为。

本⽂所指的⽤户⾏为都是指⽤户在某实体域上的⾏为。

⽐如⽤户在图书域产⽣的⾏为有阅读,购买,评分,评论等。

兴趣主题⽤户的兴趣维度,同样是限定在某实体域的兴趣,通常可以以标签的形式来表⽰。

⽐如,对于图书阅读,兴趣主题可以是「悬疑」,「科技」,「情感」等等分类标签。

值得⼀提的是,兴趣主题,只是从⽤户⾏为中抽象出来的兴趣维度,并⽆统⼀标准。

⽐如qq阅读和⾖瓣阅读的图书分类标签⼤不⼀样。

⽽兴趣维度的粒度也不固定,就像门户⽹站有「新闻」,「体育」,「娱乐」等⼀级分类,⽽新闻下有「国内」,「社会」,「国际」⼆级分类,娱乐下有「明星」,「星座」,「⼋卦」⼆级分类。

行为级建模和结构化建模

行为级建模和结构化建模解读一、行为级建模行为级建模是一种系统建模方法,它主要关注系统的动态行为和交互。

这种建模方法特别适合于模拟和分析实时、嵌入式系统。

行为级建模具有以下几个主要特点:1. **重点在动态行为**:行为级模型的主要目标是捕获系统的动态行为,例如系统的响应时间和性能等。

这使得它成为对实时和嵌入式系统进行模拟和性能分析的理想选择。

2. **关注交互**:行为级建模强调系统各部分之间的交互,以及这些交互如何影响系统的整体行为。

这种交互可以包括硬件与硬件、硬件与软件、软件与软件之间的交互。

3. **抽象层次高**:虽然行为级模型详细描述了系统的动态行为,但它通常在一个相对高的抽象层次上工作,以便更有效地理解和分析系统。

这意味着模型可能会忽略一些细节,以简化模型并突出主要的行为特性。

4. **支持多种分析**:由于行为级模型关注动态行为,它可以支持多种分析,如性能分析、可靠性分析、控制系统分析和能源消耗分析等。

二、结构化建模结构化建模是一种更传统的系统建模方法,其重点是系统结构和组成部分之间的关系。

结构化建模主要基于自上而下的设计原则,将系统分解为更小的、更易于管理的部分。

以下是结构化建模的一些关键特点:1. **关注系统结构**:结构化模型强调系统的组成和各部分之间的关系。

这有助于更好地理解系统的整体结构和功能。

2. **分解和模块化**:结构化建模通常将系统分解为多个模块或组件,每个模块执行特定的功能。

这有助于简化设计和分析过程。

3. **顺序和流程**:在这种方法中,通常强调模块之间的顺序和流程关系,而不是并行或并发关系。

4. **强调因果关系**:结构化模型强调事件之间的因果关系,而不是实时交互或并发行为。

5. **易于理解和分析**:由于结构化模型通常更简单、更直观,因此更容易理解和分析。

这对于初步的系统设计阶段尤其有用。

总结:行为级建模和结构化建模是两种不同的系统建模方法,各有其优点和适用场景。

基于MATLAB的功率放大器行为级建模方法研究

电磁特征行为级建模

电磁特征行为级建模1.引言1.1 概述概述电磁特征行为级建模是一种通过分析和描述物体或系统在电磁环境中的行为来为其建立模型的方法。

在不同的电磁场环境中,物体或系统的电磁行为会产生不同的特征,这些特征可以被捕捉和分析,以进一步理解和预测其性能和行为。

传统的建模方法主要依赖于物理模型和经验模型,这些模型通常需要复杂的数学推导和实验数据验证。

然而,随着电磁感应技术的进步和计算能力的提高,电磁特征行为级建模成为一种更加高效和准确的建模方法。

电磁特征行为级建模的核心思想是通过采集和分析物体或系统在电磁环境中的电磁信号,利用机器学习、数据挖掘和模式识别等技术,提取出关键的特征信息,并将其作为建模的基础。

这种方法能够更好地描述物体或系统的电磁行为,同时减少了对物理模型的依赖。

通过建立准确的电磁特征行为级模型,我们可以更好地理解和优化物体或系统在复杂电磁环境下的性能和行为。

本文将首先介绍电磁特征行为的概念和特点,包括电磁信号的产生、传播和感应机制等。

接着,将详细介绍电磁特征行为级建模的方法和技术,包括特征提取、模型训练和评估等方面。

最后,对电磁特征行为级建模的应用前景进行展望,并提出未来的研究方向和挑战。

通过对电磁特征行为级建模的研究和应用,我们可以更好地理解和掌握物体或系统在电磁环境中的行为规律,为电磁感应和应用提供更准确和可靠的模型基础。

这将有助于推动电磁技术在各个领域的应用和发展,提高系统的性能和可靠性。

1.2文章结构文章结构部分的内容应该包括以下内容:在该部分,我们将对本篇文章的结构进行介绍。

本文共分为三个主要部分:引言、正文和结论。

引言部分将首先对电磁特征行为级建模的概念进行概述,说明其在相关领域中的重要性和应用。

接着我们将介绍文章的结构,包括各个章节的内容和顺序。

最后,我们将明确阐述本文的目的,指明我们所探讨的问题和研究的目标。

正文部分将详细介绍电磁特征行为的概念和相关知识。

我们将探讨电磁特征行为的定义、特点和发展趋势,并提供一些实际的案例和应用。

非理想Σ-Δ调制器在SIMULINK下的行为级建模

0 引言

各式各样的便携电子终端设备见证了模拟混合 信号电路的发展。作为连接外部模拟接 口和内部数

字处理 器 的重要组 成 部分 , 模 转换 器 遇 到 了高 分 数

在相同功耗的条件下 , 阶调制器是一个普遍 高

采 用达 到所 需要 的信 噪 比 S R要 求 的方案 。通 常 , N

S a g a ioo gU iesy S a g a 2 04 , hn ) h n h Jatn nvri ,h n h 02 C ia i t i 0

Ab t a t B s d o a iu r c i l o — e l a tr n l ga d mie in l i ut e in, e f s r c : a e n v r sp a t a n i a c s n a ao n x d sg a r i d sg a s t o c n d f o i c c o S MUL NK mo e sa e u e e o m i — o i e a ir ls lt n fd f r n 一 d ltr . I I d l r s d t p r r t o f me d man b h v o a i a o s o i e e t A mo u a o s mu i S mu a o o s to l n l d l sia a c d tu t r ,b tas o ti s Mu t s g i h p n i lt n d e n’ n y i cu e ca sc l s a e sr c u e u o c n an l —t e Nos S a i g i c l i a e

2 1 年第3 02 期

文章编号 :09— 52 2 1 ) 3— 0 2— 5 10 2 5 (0 2 0 07 0 中图分类号 :N 6 T71 文献标识码 : A

宝宝作业-基于Matlab流水线AD转换器行为级模型建模与仿真

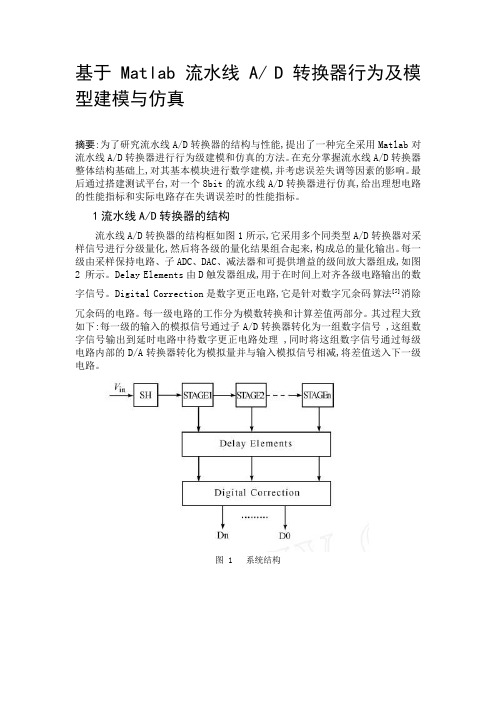

基于 Matlab 流水线 A/ D 转换器行为及模型建模与仿真摘要:为了研究流水线A/D转换器的结构与性能,提出了一种完全采用Matlab对流水线A/D转换器进行行为级建模和仿真的方法。

在充分掌握流水线A/D转换器整体结构基础上,对其基本模块进行数学建模,并考虑误差失调等因素的影响。

最后通过搭建测试平台,对一个8bit的流水线A/D转换器进行仿真,给出理想电路的性能指标和实际电路存在失调误差时的性能指标。

1流水线A/D转换器的结构流水线A/D转换器的结构框如图1所示,它采用多个同类型A/D转换器对采样信号进行分级量化,然后将各级的量化结果组合起来,构成总的量化输出。

每一级由采样保持电路、子ADC、DAC、减法器和可提供增益的级间放大器组成,如图2 所示。

Delay Elements由D触发器组成,用于在时间上对齐各级电路输出的数字信号。

Digital Correction是数字更正电路,它是针对数字冗余码]5[算法消除冗余码的电路。

每一级电路的工作分为模数转换和计算差值两部分。

其过程大致如下:每一级的输入的模拟信号通过子A/D转换器转化为一组数字信号 ,这组数字信号输出到延时电路中待数字更正电路处理 ,同时将这组数字信号通过每级电路内部的D/A转换器转化为模拟量并与输入模拟信号相减,将差值送入下一级电路。

图 1 系统结构图 2 每一级电路的结构各级电路的输出送入延时单元 ,延时单元的输出信号将同时到达数字更正电路 ,数字更正电路的输出便是模数转换的最终结果。

2数字冗余码的概念]5[这是结构最为简单的数字更正技术。

每一级的子A/D转换器多输出一个冗余码 ,这样通过相应的算法,可以消除由于比较器失调带来的误码。

增加一位冗余码意味着增加子A/D转换器的精度。

但这并不意味着将一个n位的子A/D转换器变为n+1位的子A/D转换器。

图3为1.5bit子A/D转换器的传输特性曲线 ,其中0.5bit为冗余码。

14位Single―slope ADC行为级建模与仿真

14位Single―slope ADC行为级建模与仿真摘要:单斜率型模/数转换器以其简单的结构、较高的分辨率和易于集成的优势,在红外焦平面读出电路设计中被广泛应用。

基于Matlab软件环境下的Simulink工具,建立了一个14位Single?slope ADC的系统模型。

其充分讨论Simulink工具下电路各单元模块的具体实现和信号间的时序关系,给出电路的行为级仿真结果,为Single?slope ADC的集成电路设计与实现提供参考。

关键词:单斜模/数转换器;行为级建模;红外焦平面;Simulink;集成电路设计;功能仿真中?D分类号:TN492?34 文献标识码:A 文章编号:1004?373X(2018)16?0104?04Abstract:As the single?slope ADC has the advantages of simple structure,high resolution,and easy integration,it has been widely used in the design of the infrared focal plane read?out circuit. Based on the Simulink tool in the Matlab software environment,a 14?bit single?slope ADC system model is built. The specific implementation utilizing the Simulink tool for each unit module of the circuit and the time sequence relationship among signals are fully discussed. The behavioral simulation results of the circuit are given,whichprovides a reference for the design and implementation of the single?slope ADC integrated circuit.Keywords:Single?slope ADC;behavioral modeling;infrared focal plane;Simulink;integrated circuit design;functional simulation 0 引言红外焦平面成像系统在军事、医疗扫描、空间探测、环境监控以及民用消费电子方面有着广泛的应用[1]。

4?bitFLASHADC行为级建模与仿真

4?bit FLASH ADC⾏为级建模与仿真2019-10-15摘要:基于Matlab/Simulink的平台,设计并实现了⼀种新型的单通道4?bit FLASH ADC⾏为级仿真模型,模型充分考虑到时钟抖动、失调电压、迟滞效应、⽐较器噪声等⾮理想特性,使整个系统更逼近实际电路。

在输⼊信号为1 GHz,采样时钟频率为500 MHz时,对⾮理想模型进⾏时域及频域分析,创建的模型和系统仿真结果可为ADC系统中的误差、静态特性及动态特性研究提供借鉴。

关键词: FLASH ADC; Matlab/Simulink;⾏为级建模;⾮理想特性中图分类号: TN911?34 ⽂献标识码: A ⽂章编号: 1004?373X(2013)22?0120?04ADC是数据采集系统的重要部件,常⽤的⾼速⾼精度ADC主要分为:并⾏ADC(FLASH ADC)、流⽔线ADC(Pipeline ADC)、过采样ADC(Sigma?Delta ADC)等。

在实际电路设计中,ADC采样率和分辨率是⼀对⽭盾,要实现⾼采样率就难以达到⾼分辨率。

FLASH ADC采样率最⾼,常⽤于500 MS/s以上采样率的场合,⽐如超宽带通信,但其分辨率⼀般只能达到4~8位,是常⽤的⾼速数据采集ADC。

1 设计简介在集成电路数模混合设计中,通常采⽤⾃顶向下的设计流程,如图1所⽰。

为了提⾼电路设计效率及仿真速度,对电路进⾏⾏为级建模已经成为设计的重要环节[1]。

本⽂基于Matlab和Simulink[2]⼯具分析FLASH ADC的架构特点并建⽴单通道FLASH ADC的⾏为级模型,充分考虑各⾮理想特性并进⾏仿真分析,为ADC系统指标分配及具体的电路设计提供了有⼒的参考条件。

2 FLASH ADC结构特点图2为FLASH ADC的结构框图[3],参考电压Vref经分压电阻⽹络输出若⼲个参考电压,和输⼊的模拟信号Vin输⼊⾄⽐较器阵列,得到⽐较值组成温度计码,该温度计码值经编码器得到输出的数字信号Data_out。

第六讲 行为级建模.

置Q为0,

置Qb为1ຫໍສະໝຸດ 第五讲 行为建模西安邮电学院通信工程系

过程块(procedural)

过程块是行为模型的基础。一个模块中可以有多个过程块,过程块有两种:

initial块,只能执行一次 always块,循环执行

过程块中有下列部件

过程赋值语句:描述过程块中的数据流 时序控制:控制块的执行及块中的语句时序 高级结构(循环,条件语句等):描述块的功能

连续赋值 输出

output

过程块

Procedural blocks

寄存器类型

register

Continuous assignment

函数

function

双向

inout

参数

parameter

赋值语句

assign

过程块语句

initial block always block

系统任务和函数

System task & function

第五讲 行为建模

西安邮电学院通信工程系

行为建模(描述)

行为级描述是对系统的高抽象级描述。在这个抽象级,注重的是整个系 统的功能而不是实现。 Verilog有高级编程语言结构用于行为描述,包括:initial, always,@, wait, for, while, if else, case 和 forever 等。 Verilog的行为建模是用一系列以高级编程语言编写的并行的、动态的过 程块来描述系统的工作。 D触发器行为 在每一个时钟上升沿, 若Clr不是低电平, 置Q为D值, 置Qb为D值的反 无论何时Clr变低

第五讲 行为建模

西安邮电学院通信工程系

第 五讲 行为建模1

电路行为级建模

电路行为级建模1.引言1.1 概述电路行为级建模是电子电路设计领域中的一个重要概念。

它是通过对电路中各个元件的行为进行描述和建模,从而实现对电路整体性能和行为表现的预测和分析。

与传统的物理级建模相比,电路行为级建模更侧重于描述和分析电路的功能和行为,而不涉及具体元件的物理特性和结构。

在电子电路设计过程中,电路行为级建模具有很大的优势和应用价值。

首先,它可以帮助设计人员在早期阶段对电路进行性能评估和功能验证,从而减少设计周期和成本。

其次,通过建立准确的电路行为模型,可以更好地理解和分析电路的工作原理,帮助设计人员进行优化和改进。

电路行为级建模在不同领域有着广泛的应用。

在通信领域,它可以用于建模和分析调制解调器、射频前端电路等复杂的通信系统。

在数字电路设计中,电路行为级建模可以用于建模和验证处理器、存储器等数字系统的功能和性能。

此外,在模拟电路设计和集成电路设计中,电路行为级建模也是不可或缺的工具。

总之,电路行为级建模在电子电路设计中具有重要的意义和价值。

它通过描述和分析电路的功能和行为,帮助设计人员进行性能评估和功能验证,优化和改进电路设计。

随着电子技术的不断发展,电路行为级建模将继续发挥重要作用,并有望在未来取得更大的突破和应用。

1.2 文章结构本文主要围绕电路行为级建模展开,文章结构如下:第一部分:引言在引言部分,我们将对电路行为级建模进行概述,阐述本文的目的,并说明文章的结构安排。

第二部分:正文2.1 电路行为级建模的定义和背景本节将对电路行为级建模的概念进行详细阐述,并介绍背景知识。

我们将讨论电路行为级建模是如何对电路进行抽象和描述的,以及它在电路设计中的作用和意义。

2.2 电路行为级建模的优势和应用在本节中,我们将探讨电路行为级建模相对于其他建模方法的优势和特点。

我们将分析其在不同领域中的应用案例,包括电路仿真、系统级设计以及嵌入式系统等方面。

第三部分:结论3.1 总结电路行为级建模的重要性和价值在本节中,我们将总结电路行为级建模对于电路设计的重要性和价值。

门级建模 行为建模

门级建模行为建模门级建模和行为建模都是软件工程中常见的建模技术。

它们有着不同的特点和适用范围。

下面就分别介绍一下这两种建模技术。

门级建模门级建模是一种结构化建模技术,它描述了系统的组成部分(也称为子系统)之间的逻辑关系。

这种建模技术通过定义系统中的门,将系统分成多个子系统。

门是指一个可以输入和输出的信号集合。

这样,每个子系统通过一个或多个门与其他子系统进行通信和控制。

在门级建模中,每个门都可以描述为一个逻辑公式,这个逻辑公式可以由基本逻辑运算符(如与、或、非)组成。

门级建模可以用于不同类型的系统的建模。

例如,在电子控制开关的设计中,门可以表示控制信号或保护信号。

在软件系统中,门可以与程序逻辑进行关联。

行为建模行为建模是一种描述系统功能的建模技术。

它对系统提供的服务进行建模,以及系统对外部事件的响应进行建模。

其目的是描述系统的行为,以指导开发者编写具体代码。

行为建模可以是动态的(也称为状态机)或静态的(也称为活动图)。

动态行为建模描述了系统响应事件的过程,它将系统状态作为它的状态转换中的一部分。

静态行为模型描述了系统在处理某些数据时所需要执行的动作。

它的主要原则是描述系统的各个组成部分如何协同工作,以提供所需的功能。

行为建模在软件开发中有着广泛的应用。

它可以用于需求分析、设计和测试。

它还可以被用于资产和流程管理等领域。

总结门级建模和行为建模是两种不同的建模技术,它们各自都有各自的优点和适用范围。

门级建模适用于描述系统的组成部分之间的逻辑关系,而行为建模适用于描述系统的行为和功能。

在实际应用中,开发者可以结合两种技术进行开发,从而获得更好的效果。

对于数据流建模和行为级建模的梳理(重点)

对于数据流建模和⾏为级建模的梳理(重点)数据流建模,输⼊输出的类型⼀般为wire⾏为级建模,输⼊的类型⼀般为reg,输出的类型为wire,因为always其中的等号左边的式⼦的值必须是reg类型的//数据流建模module and2(x1, x2, z1);input x1, x2;output z1;wire x1, x2;wire z1;assign z1 = x1 & x2;endmodule//⾏为级建模module or3(x1,x2,x3,z1);input x1, x2, x3;output z1;wire x1, x2 , x3;reg z1;always @ (x1 or x2 or x3) // always的变量z1必须为reg类型的beginz1 = x1 | x2 | x3;endendmodule从上⾯也能看出:数据流建模,⼀般⽤assign声明描述电路⾏为(连续赋值语句。

因此这⾥的输出必须设置成wire类型)⾏为级建模,⼀般⽤initial 或者always (过程连续赋值语句,因为这⾥有always,输出必须设置成reg类型的)在testbench中,输⼊是reg类型,输出是wire类型://这⾥有for循环类型的module or3_tb;reg x1, x2, x3;wire z1;initialbegin : apply_stimulusreg [3:0] invec;for(invec = 0; invec < 8; invec = invec + 1)begin{x1, x2 ,x3} = invec [3:0];#10 $display ("x1x2x3 = %b , z1 = %b ",{x1, x2, x3}, z1);endendor3 inst(.x1(x1),.x2(x2),.x3(x3),.z1(z1));endmodule//类似于枚举类型的module add_tb;reg x1, x2;wire z1;//diaplay variablesinitial$monitor ("x1 = %b, x2 = %b, z1 = %b", x1, x2, z1);//applayinitialbegin#0 x1 = 1'b0;x2 = 1'b0;#10 x1 = 1'b0;x2 = 1'b1;#10 x1 = 1'b1;x2 = 1'b0;#10 x1 = 1'b1;x2 = 1'b1;#10 $stop;endadd ins(.x1(x1),.x2(x2),.z1(z1)); endmodule当然还有其它类型。

行为级建模方法

module FA_behav2(A, B, Cin, Sum, Cout ); input A,B,Cin; output Sum,Cout; reg Sum, Cout; always @ (A or B or Cin) begin {Count,Sum} = A + B + Cin; end

加上时延控制“#50”产生 一个周期为100的方波信 号31来自两类语句在模块中的使用

32

4.3 语句块

在Verilog HDL中有两类语句块: 1. 串行块(begin-end)

33

4.3.1 顺序语句块(begin-end)

例:用begin-end串行块产生信号波形 'timescale 10ns/1ns module wave1; reg wave ; parameter cycle=10 ; initial begin wave=0 ; #(cycle/2) wave=1 ; #(cycle/2) wave=0 ;

过程赋值语句 过程连续赋值语句

语句块 时序控制语句

高级程序语句

条件分支语句 循环控制语句

7

语句的可综合性比较

类型 过程语句

块语句

语句 initial always begin-end fork-join

可综合性

√ √

持续赋值语句assign

√

赋值语句

过程赋值=、<=

√

条件语句

if-else

√

case

20

4.2.2. always语句

2'b10:out=in2 ;

2'b11:out=in3 ;

default :out=2'bx ;

关于行为建模

关于行为建模“行为建模”包含一组执行模型的多种分析并将分析结果合并到模型中的工具。

“行为建模”能够实现按所需的解决方案来修改模型的设计。

使用“行为建模”工具可以完成下列工作:创建基于模型测量和分析的特征参数。

创建基于模型测量和分析的几何图元。

创建符合特殊要求的测量的新类型。

分析变量尺寸和参数改变时测量参数的行为。

自动查找满足所需的模型行为的尺寸和参数值。

分析指定设计空间内测量参数的行为。

行为建模的基本构建块如下:域点分析特征持续分析显示用户定义分析敏感度、可行性和优化研究优化特征多目标设计研究外部分析运动分析打开保存的分析单击“分析”(Analysis)>“保存的分析”(Saved Analysis)打开已保存的分析,然后使用“保存的分析”(Saved Analysis)对话框来执行下列操作:隐藏或取消隐藏任何保存的分析重新定义选定分析使用过滤器来选取要查看的分析类型删除已保存的分析持续显示Pro/ENGINEER 支持任何域点类型的持续显示(曲线分析、曲面分析或基于域点的用户定义分析)。

如果定义并保存了一个分析,那么这个分析的显示将留在屏幕上。

这个分析显示随着模型几何的改变而更新。

可通过单击“分析”(Analysis)>“保存的分析”(Saved Analysis)来关闭或打开已保存分析的持续显示。

注意:如果以着色模式显示该模型,那么显示的余辉可能是间歇的。

关于配置行为建模可通过设置配置文件选项来定制“行为建模”的某些方面。

“行为建模”的“帮助”提供了按字母顺序排列的配置选项列表。

每一选项包含如下信息:配置选项名称。

缺省和可用的变量或值。

缺省值为斜体。

描述配置选项的简单说明和注释。

设置行为建模配置选项1. 单击“工具”(Tools)>“选项”(Options)。

“选项”(Options)对话框打开。

2. 单击“仅显示从文件载入的选项”(Show only optionsloaded from file) 复选框,查看当前已载入的配置选项,或清除此复选框以查看所有的配置选项。

simplis行为级建模的作用

simplis行为级建模的作用

Simplis行为级建模是一种用于电路仿真的方法,它的作用主

要体现在以下几个方面:

1. 精确性,Simplis行为级建模能够更精确地描述电路元件的

行为,包括非线性、时变和温度效应等。

通过对电路元件进行更细

致的建模,可以提高仿真结果的准确性,使得设计工程师能够更好

地预测电路的性能。

2. 效率,相对于传统的基于SPICE的电路仿真方法,Simplis

行为级建模能够在保证精度的前提下显著提高仿真的速度。

这对于

需要进行大规模电路仿真的工程师来说是非常重要的,可以节省大

量的时间和计算资源。

3. 可靠性,Simplis行为级建模还可以提高电路仿真的可靠性。

通过更准确地描述电路元件的行为,可以减少因为建模不准确而导

致的仿真误差,提高仿真结果的可信度。

4. 应用范围广泛,Simplis行为级建模不仅适用于传统的线性

电路,还可以应用于包括开关电源、电机驱动器、模拟信号处理电

路等在内的多种电路类型。

这使得Simplis行为级建模成为了工程师在各种电路设计领域中的重要工具。

总的来说,Simplis行为级建模在提高仿真精度、提高仿真效率、提高仿真可靠性以及适用范围广泛等方面发挥着重要作用,成为了电路设计工程师不可或缺的工具之一。

泰勒级数行为建模

泰勒级数行为建模

泰勒级数是一种数学方法,用于将一个函数表示为无穷级数形式。

这种方法可以被用来建模许多不同的自然现象和行为。

以下是一些可能用泰勒级数行为建模的例子:

1.弦振动:泰勒级数可以用来近似描述弦的振动行为。

在音乐

中,这种行为被用来合成音符和声音效果。

2.电子电路:泰勒级数可以用来描述电路中的电压和电流行为,

如滤波器和振荡器。

3.天气预测:泰勒级数可以用来近似描述大气中的压力、温度和

湿度等变量的变化,从而预测天气。

4.金融建模:泰勒级数可以用来描述股票价格和利率等变量的变

化,从而预测未来的值。

5.机器人控制:泰勒级数可以用来描述机器人的运动行为,从而

控制其动作。

这些只是泰勒级数应用的一些例子。

实际上,这种数学方法在科学和工程领域中被广泛应用,用来建模各种不同的现象和行为。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. 上述各种类型的位选(例如,addr [ 0 ])。

3. 上述各种类型的域选(例如,addr [ 31 : 16 ])。 上面三种类型的拼接。

Verilog包括两种类型的过程赋值语句:阻塞赋值和非阻塞赋值语句

Page 8

7.2.1 阻塞赋值语句

阻塞赋值语句使用“=”作为赋值符,在一个begin-end块中表现为串行行 为。

always语句声明格式如下:

always <时序控制> <语句>

Page 6

如果一个always语句没有时序控制,则这个always语句将会发成一个 仿真死锁。见下例: always areg = ~areg;

这个always语句将会生成一个0延迟的无限循环跳变过程,这时会发生 仿真死锁。如果加上时序控制,则这个always语句将变为一条非常有用的 描述语句。见下例:

always #half_period areg = ~areg; 这个例子生成了一个周期为:period(=2*half_period) 的无限延续的信号 波形,常用这种方法来描述时钟信号,作为激励信号来测试所设计的电路。

Page 7

7.2 过程赋值语句

过程赋值语句的赋值后,其值将保持不变,直到被其他过程赋值语句赋予新值。 用法: 过程赋值语句的左侧值可以是: 1. reg,整型数、实型数、时间寄存器变量或存储器单元。

注意:不要在同一个always块中混合使用阻塞和非阻塞赋值语句。

Page 10

非阻塞赋值语句的应用

对程序:

如下的特点:

1.在每个时钟上升沿到来时读取in1,in2,in3和reg1,计算右侧表达式的值,该值 由仿真器临时保存。

2.对左值的赋值由仿真器调度到相应的仿真时刻,延迟时间由语句中内嵌的延迟值 确定。在本例中,对reg1的赋值需要等一个时间单位,对reg2的赋值需要等到时钟 信号下降沿到来的时刻,对reg3的赋值需要等一个时间单位; 3.每个赋值操作在被调度的仿真时刻完成。注意,对左侧变量的赋值使用的是由仿 真器保存的表达式“旧值”。在本例中,对reg3赋值使用的是reg1的“旧值”,而 不是在此之前对reg1赋予的新值,reg1的“旧值”是在赋值事件调度时由仿真器保 存的。

Page 11

使用非阻塞赋值来避免竞争

产生了竞争的情况:a = b和b = a,具体执行顺序的先后取决于 所使用的仿真器,因此这段代 码达不到交换a和b值的目的 。 在每个时钟上升沿到来的时候, 仿真器读取每个操作数的值, 进而计算表达式的值并保存在 临时变量中;当赋值的时候, 仿真器将这些保存的值赋予非 阻塞赋值语句的左侧变量。

阻塞(Blocking)赋值方式( 如 b = a; ) ,其中b的值在赋值语句执行完后立刻 就改变的。

x = 0执行完成之后,才会执行y = 1 仿真0时刻执行 仿真时刻15执行 仿真时刻25执行

1.如果右侧表达式的位宽较宽,则将保留从最低位开始的右侧值,把 超过左侧位宽的高位丢弃; 2.如果左侧位宽大于右侧位宽,则不足的高位补0;

HDL语言硬件设计

第七章 行为级建模

7.1 结构化过程语句

在Verilog中有两种结构化的过程语句:initial语句和always语句,它们是 行为级建模的两种基本语句。其他所有的行为语句只能出现在这两种结构 化过程语句里。

与C语言不同,Verilog在本质上是并发而非顺序的。Verilog中的各个执行 流程(进程)并发执行,而不是顺序执行的。

每个initial语句和always语句代表一个独立的执行过程,每个执行过程从仿 真时间0开始执行,并且这两种语句不能嵌套使用。

Page 2

7.1.1 initial语句

所有在initial语句内的语句构成了一个initial块。initial块从仿真0时刻开始执 行,在整个仿真过程中只执行一次。 如果一个模块中包括了若干个initial块,则这些initial块从仿真0时刻开始并 发执行,且每个块的执行是各自独立的。 如果在块内包含了多条行为语句,那么需要将这些语句组成一组,一般是 使用关键字begin和end将它们组合为一个块语句;如果块内只有一条语句, 则不必使用begin和end。

Page 5

7.1.2 always语句

always语句包括的所有行为语句构成了一个always语句块。该always语句 块从仿真0时刻开始顺序执行其中的行为语句;在最后一条执行完成后,再 次开始执行其中的第一条语句,如此循环往复,直至整个仿真结束。

always语句通常用于对数字电路中一组反复执行的活动进行建模。例如时 钟信号发生器,每半个时钟周期时钟信号翻转一次。在现实电路中只要电 源接通,时钟信号发生器从时刻0就有效,一直工作下去。

在这个例子中用initial语句在仿真开始时对各变量进行初始化。 initial begin inputs = 'b000000; //初始时刻为0 #10 inputs = 'b011001; #10 inputs = 'b011011; #10 inputs = 'b011000; #10 inputs = 'b001000; end 从这个例子中,我们可以看到用initial语句来生成激励波形作为 电路的测试仿真信号。

由于initial块语句在整个仿真期间只能执行一次,因此它一般被用于初始化、 信号监视、生成仿真波形等目的。

Page 3

Page 4

initial begin areg=0; //初始化寄存器areg for(index=0;index<size;index=index+1) memory[index]=0; //初始化一个memory end

Page 9

7.2.2 非阻塞赋值语句

非阻塞赋值使用“<=”作为赋值符。

非阻塞(Non_Blocking)赋值方式( 如 b <= a; )。在语句块中,上面语句 所赋的变量并不能立即为下面的赋值语句使用;所赋变量值为上一次赋值得 到的。

仿真0时刻执行 仿真时刻15执行 仿真时刻10执行 仿真0时刻执行 reg_a[2]<= #15 1’b1; reg_b[15:13]<= #10 {x,y,z};