Vivado高效设计案例分享

Vivado实验03_简单4位ALU仿真实验分析

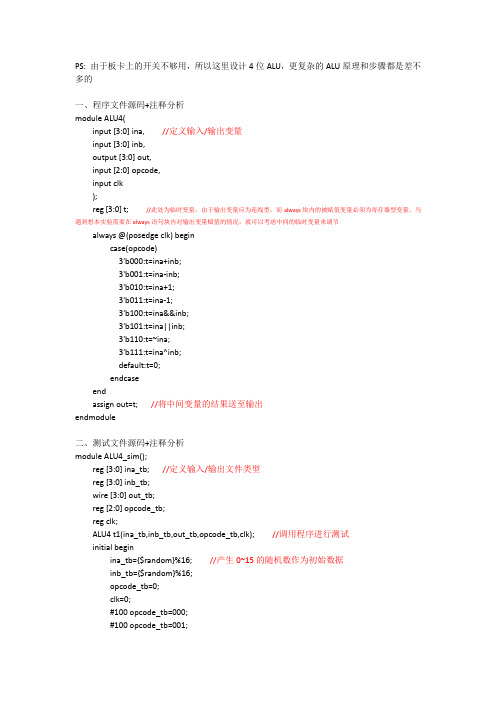

PS: 由于板卡上的开关不够用,所以这里设计4位ALU,更复杂的ALU原理和步骤都是差不多的一、程序文件源码+注释分析module ALU4(input [3:0] ina, //定义输入/输出变量input [3:0] inb,output [3:0] out,input [2:0] opcode,input clk);reg [3:0] t; //此处为临时变量,由于输出变量应为连线型,而always块内的被赋值变量必须为寄存器型变量,当遇到想本实验需要在always语句块内对输出变量赋值的情况,就可以考虑中间的临时变量来调节always @(posedge clk) begincase(opcode)3'b000:t=ina+inb;3'b001:t=ina-inb;3'b010:t=ina+1;3'b011:t=ina-1;3'b100:t=ina&&inb;3'b101:t=ina||inb;3'b110:t=~ina;3'b111:t=ina^inb;default:t=0;endcaseendassign out=t; //将中间变量的结果送至输出endmodule二、测试文件源码+注释分析module ALU4_sim();reg [3:0] ina_tb; //定义输入/输出文件类型reg [3:0] inb_tb;wire [3:0] out_tb;reg [2:0] opcode_tb;reg clk;ALU4 t1(ina_tb,inb_tb,out_tb,opcode_tb,clk); //调用程序进行测试initial beginina_tb={$random}%16; //产生0~15的随机数作为初始数据inb_tb={$random}%16;opcode_tb=0;clk=0;#100 opcode_tb=000;#100 opcode_tb=001;#100 opcode_tb=010;#100 opcode_tb=011;#100 opcode_tb=100;#100 opcode_tb=101;#100 opcode_tb=110;#100 opcode_tb=111;#100 $stop;endalways #50 clk=~clk;endmodule约束文件源码(下板操作需要)## Clock signalset_property PACKAGE_PIN E3 [get_ports clk]set_property IOSTANDARD LVCMOS33 [get_ports clk]##Switchesset_property PACKAGE_PIN J15 [get_ports {ina[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[0]}]set_property PACKAGE_PIN L16 [get_ports {ina[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[1]}]set_property PACKAGE_PIN M13 [get_ports {ina[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[2]}]set_property PACKAGE_PIN R15 [get_ports {ina[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[3]}]set_property PACKAGE_PIN R17 [get_ports {inb[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[0]}] set_property PACKAGE_PIN T18 [get_ports {inb[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[1]}] set_property PACKAGE_PIN U18 [get_ports {inb[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[2]}] set_property PACKAGE_PIN R13 [get_ports {inb[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[3]}] set_property PACKAGE_PIN U12 [get_ports {opcode[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {opcode[0]}] set_property PACKAGE_PIN U11 [get_ports {opcode[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {opcode[1]}] set_property PACKAGE_PIN V10 [get_ports {opcode[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {opcode[2]}] ## LEDsset_property PACKAGE_PIN V15 [get_ports {out[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[0]}]set_property PACKAGE_PIN V14 [get_ports {out[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[1]}]set_property PACKAGE_PIN V12 [get_ports {out[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[2]}]set_property PACKAGE_PIN V11 [get_ports {out[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[3]}]三、仿真结果如下图可以看出当opcode的值依次递增时,ina和inb依次做加,减,加1,减1,逻辑与,逻辑或,逻辑非,逻辑异或等操作,结果存放在out里。

Vivado+Zedboard之流水灯(DOC48页)

Vivado+Zedboard之流水灯(DOC48页)环境:Vivado 2021.2开发板:Zedboard version xc7z020clg484-1实验:使用Vivado和SDK进行Zedboard开发,制作一个简单的流水灯程序以说明软硬件协同设计的方法、开发流程等。

本文将分为三个部分:1. 使用Vivado创建一个工程,并构建一个Zynq嵌入式处理系统2. 在上述基础上,将完成后的硬件导入到SDK中进行软件设计。

3. 最后下载到ZedBoard上进行调试。

1. 使用Vivado创建工程1.1新建工程1.鼠标左键双击Vivado 2021.2图标,打开Vivado 2021.2,显现如下界面:2.单击Create New Project创建一个新的工程:3.单击Next执行下一步;4.选择工程所在的位置,并输入工程名test_led,单击Next;5.在Vivado中新建一个RTL工程,暂不添加文件,单击Next;6. 单击Next执行下一步;7. 单击Next执行下一步;8. 单击Next执行下一步;9.这一步要注意,在左上角Specify处选择Boards,选择ZedBoard Zynq Evaluation and Development Kit version D器件,单击Next;10.单击Finish11.等待软件依照设定新建一个RTL工程。

如此新建工程的步骤就完成了,下面进行硬件设计步骤;1.2硬件设计新建工程的界面如下:1.单击Create Block Design,创建并添加IP核;2.输入工程名led,单击OK;3.等待软件Create Block Design,创建完成后的界面如下:4. Add IP,一样会提示This design is empty.To get started, Add IP from the catalog,单击Add IP会显现IP的名目,假如此处没有提示,能够单击Diagram左边框的Add IP添加;5. 在名目Search中输入ZYNQ7 Processing System;6.双击ZYNQ7 Processing System完成IP核的添加;7.等待软件Add IP,添加完成后的界面如下:8.单击Run Block Automation;9.单击processing_system7_0;10.单击OK;11.等待软件运行,运行后的界面为:12.假如想了解内部的详细结构和进行接口配置,能够双击ZYNQ7 Processing System核,〔此实验不需要设置,假如想直截了当进行下一步实验能够直截了当跳到步骤16〕13.等待软件运行,运行后的界面为:14.单击左侧对应内容能够进行接口配置:15.单击OK完成配置;16.连续添加IP ,单击左侧的Add IP图标:18.双击AXI GPIO添加;19.连续添加IP,单击左侧的Add IP图标,在名目Search中输入AXI BRAM Controller:20.双击AXI BRAM Controller,完成添加;22. 双击Block Memory Generator,完成添加;24. Mode处选择BRAM Controller,Memory Type处选择True Dual Port RAM:25.单击OK完成设置;26.连接the Block Memory Generator to the AXI4 BRAM Controller27.Run Connection Automation 选择/axi_gpio_0/S_AXI:28.单击OK,完成此部分的连接;29. Run Connection Automation again, 选择/axi_gpio_0/GPIO;30.选择leds_8bits,单击OK;31.Run Connection Automation again, 选择/axi_bram_ctrl_0/S_AXI;32.单击OK;33. 修改the range of the AXI BRAM Controller to 64K:34. 单击File选择Save Block Design储存设计〔也能够直截了当Ctrl+S〕1.3硬件处理1. Tools >Validate Design2.等待软件运行,运行后的界面如下:3.单击OK;4.right-click the top-level subsystem design->Generate Output Products5.单击Generate,等待软件运行,运行完成后right-click the top-level subsystem design->Create HDL Wrapper6.单击OK;7. 单击Generate Bitstream,单击Yes,第一进行分析综合和实现;(那个地点也能够直截了当先点击Run Synthesis,然后点击Run Implementation,然后再点击Generate Bitstream)需要等待运行的时刻比较长,本机大致需要15分钟;8.运行完成后,会自动弹出对话框,选择Open Implemented Design,单击OK:9.运行完成后的界面如下:10. 在关联到SDK时,需要将Package和Device都打开,假如运行后只是自动打开了device,需要Open Synthesized Design来打开Package11.单击NO,将Package和Device同时显示出来;打开后的界面如下:12. 单击Open Block Design to invoke the IP integrator design13. 连接micro-usb cable between the PC and the JTAG port of the board, another micro-usb cable between the PC and the UART port of the board,.打开Zedboard板的电源,如以下图所示,打开电源之后POWER灯会亮;14.单击Hardware Manager中的Open Target,那个地点因为曾经在本机上使用过Zedboard,因此会直截了当显示出Localhost,假如是第一次连接Zedboard,要单击Open New Target〔假如直截了当显示出Localhost,能够直截了当点击Localhost进行步骤18〕15.单击Next;〔假如hardware manager中找不到硬件板,这是由于在任务治理器的进程中,hw_server.exe进程一直在执行,需要将其关掉,假如关了之后还检测不到硬件板,那么需要关机之后再开机便可;〕16.选择Local server,单击Next;17.软件会自动检测出Localhost,选择后单击Next;18.单击Finish,自动Open Target;19. 单击Hardware Manager中的Program Device,单击xc7z020_1:20.单击Program将比特流烧写到ZedBoard板上;完成后板上的DONE蓝灯会亮,提示成功:21.单击File中的Export,单击Export Hardware22.单击OK23. 单击File中的launch SDK:24.单击OK;如此在Vivado中的操作就完成了,软件会自动打开SDK:SDK中的软件设计打开后的SDK界面如下:1. 单击File > New > Application Project2.输入工程名zj,单击Next:3. 选择一个空的模板:empty application,单击Finish,等待工作环境的建立:4. 单击led > 右键单击src > new > Source File5.输入工程名zj.c,单击Finish;6. 编写如下程序,Ctrl+S,储存的同时,软件会自动开始编译,在左下角problem处能够看到相应的warning和error;程序如下:#include"xparameters.h"/* Peripheral parameters */#include"xgpio.h"/* GPIO data struct and APIs */#include"xil_printf.h"#include"xil_cache.h"#define GPIO_BITWIDTH 8 /* This is the width of the GPIO */ #define GPIO_DEVICE_ID 0//device id#define LED_DELAY 10000000/* times delay*/#define LED_MAX_BLINK 0x1 /* Number of times the LED Blinks */#define LED_CHANNEL 1 /* GPIO channel*/#define printf xil_printf /* A smaller footprint printf */ XGpio Gpio; /* The Instance of the GPIO Driver */XGpio GpioOutput; /* The driver instance for GPIO Device configured as O/P */int GpioMarquee (u16 DeviceId, u32 GpioWidth){volatile int Delay;u32 LedBit;u32 LedLoop;int Status;/** Initialize the GPIO driver so that it's ready to use,* specify the device ID that is generated in xparameters.h */Status = XGpio_Initialize(&GpioOutput, DeviceId);if (Status != XST_SUCCESS){return XST_FAILURE;}//Set the direction for all signals to be outputsXGpio_SetDataDirection(&GpioOutput, LED_CHANNEL, 0x0);// Set the GPIO outputs to lowXGpio_DiscreteWrite(&GpioOutput, LED_CHANNEL, 0x0);for (LedBit = 0x0; LedBit < GpioWidth; LedBit++){for (LedLoop = 0; LedLoop < LED_MAX_BLINK; LedLoop++) {//Set the GPIO Output to HighXGpio_DiscreteWrite(&GpioOutput, LED_CHANNEL,1 << LedBit);//Wait a small amount of time so the LED is visiblefor (Delay = 0; Delay < LED_DELAY;Delay++);//Clear the GPIO OutputXGpio_DiscreteClear(&GpioOutput, LED_CHANNEL,1 << LedBit);// Wait a small amount of time so the LED is visiblefor (Delay = 0; Delay < LED_DELAY; Delay++);}}return XST_SUCCESS;}int main(void){//Application start/* loop forever*/int cnt=0;while(1){u32 status;status = GpioMarquee (GPIO_DEVICE_ID,GPIO_BITWIDTH);if (status == 0){printf("%d:SUCESS!.\r\n",cnt++);if(cnt>=1000)cnt=0;}elseprintf("FAILED.\r\n");}return XST_SUCCESS;}7. 单击Xilinx Tools > program FPGA将比特流烧写到板上〔在Vivado中就先将比特流烧写到板上有两个缘故:1.假如SDK调试时显现问题,如此能够检测第一是不是Vivado的问题,假如成功烧写,说明板的连接没有问题,同时Vivado软件本身没有问题;2.在之前的调试过程中显现过直截了当Xilinx Tools > program FPGA无法烧写的情形;因此,保险起见,选择在Vivado中就先将比特流烧写到板上〕8.单击Program〔和在Vivado中烧写的现象一样,完成后DONE蓝色指示灯会亮〕注:假如软件本身以及板的连接没有问题,那么那个步骤会在三秒左右完成,假如一直卡在一半的进度,说明SDK和Vivado没有专门好的建立关联;9.在Terminal处,单击带有加号的图标,对串口进行配置:10.在用到串口打印时,需要设置的COM口,为设备治理器中的USB serial port 〔本机为COM5〕,因此要选择COM5,注意波特率为115200:11.右键工程名目中的zj名目,选择Run As > Run Configurations;12.在STDIO Connection中设置COM 5和波特率115200:13.单击Run即可运行程序,看到流水灯的成效,每次跑完一圈会打印:数字:SUCESS!.的消息,数字为流水灯循环的次数。

1位十进制加法器vivado过程

1位十进制加法器vivado过程即刻走进Vivado的世界,我们将探索一种神奇而强大的数字逻辑设备——十进制加法器的设计。

首先,让我们明确一下什么是十进制加法器。

在计算机中,十进制加法器是一种用来执行十进制数字加法运算的电路。

与二进制加法器相比,十进制加法器需要处理更复杂的运算规则,因为我们在日常生活中使用十进制表示数字,而不是二进制。

在这个过程中,我们将使用Vivado,这是一种强大的集成开发环境(IDE),用于设计和开发FPGA(可编程逻辑门阵列)和ASIC(专用集成电路)等数字电子系统。

首先,我们需要创建一个新的Vivado项目。

在Vivado的主界面中,选择"Create New Project"选项,并按照指导完成项目设置。

请确保选择您所需的FPGA器件以及包含所需时钟频率和输入输出等信息。

完成项目设置后,我们需要添加一个新的设计文件。

在左侧"Flow Navigator"窗格中选择"Design Sources"选项,然后右键单击并选择"Add Sources"。

在弹出的对话框中选择"Add or create design sources"选项,并选择VHDL作为设计文件类型。

然后,选择一个适当的文件名,并点击"Finish"按钮。

接下来,我们需要为我们的设计编写VHDL代码。

VHDL是一种硬件描述语言,用于描述数字逻辑电路行为。

在我们的案例中,我们将编写用于实现十进制加法器功能的VHDL代码。

首先,让我们从创建所需的实体开始。

实体是描述一个数字逻辑电路的输入输出接口的VHDL构造。

为了创建我们的十进制加法器实体,我们需要声明输入和输出端口。

例如,我们可以声明两个4位的输入数字(A和B),以及一个5位的输出数字(Sum)。

接下来,我们需要在VHDL代码中定义内部信号和变量。

tcl让vivado更完美

©

Polycom, Inc. All rights reserved.

16

注意事项

如何找到大扇出网线 如何获取经过大扇出网线的时序报告 如何确定BUFG资源是否可用

©

Polycom, Inc. All rights reserved.

17

概要

项目背景 经验分享

Vivado中的Tcl基本知识 Vivado下利用Tcl编辑综合后的网表文件 Vivado下利用Tcl定制丰富的报告 Tcl和Vivado图形界面的交互使用

初始值: 1’b0

get_property INIT [get_cells local_if/data_buffer/raddr_reg]]

©

Polycom, Inc. All rights reserved.

12

设置新插入FF的属性

新插入FF的三个属性

实例化名和实体名

create_cell –ref FDRE $new_FF_name

初始值

set_property INIT $INIT_value [get_cells $new_FF_name]

三个很有用的和属性相关的脚本

report_property, get_properety and set_property

©

Polycom, Inc. All rights reserved.

输出

wbDataForInputReg_reg validForEgressFifo_reg[0]_i_1 wbDataForInput_IBUF_inst

©

Polycom, Inc. All rights reserved.

Vivado设计套件以IP和系统为中心

本文档格式为PDF,如需转换为TXT,可免费下载转换软件:/file/dpikfiut解压密码:/byby777go 新的设计环境可让客户把越来越多的系统功能集成到更少的芯片上,满足客户对更高生产力、产品上市周期、超越可编程逻辑、实现可编程系统集成等要求。

赛灵思打造了颠覆性的全新Vivado设计套件,致力于满足其提出的All Programmable器件的设计需求。

打造全新设计环境 Vivado借鉴ISE设计套件的所有经验、注意事项和关键技术,并充分利用最新EDA算法、工具和技术,打造了这个以IP和系统为中心的、面向未来10年All Programmable器件的全新设计环境。

赛灵思早在1997年就推出了ISE设计套件。

在其后15年的时间里,随着FPGA功能的增强,赛灵思为ISE套件增添了许多新技术,包括多语言综合与仿真、IP集成以及众多编辑和测试实用功能,努力从各个方面改进ISE设计套件。

与ISE相比,Vivado设计套件的优势体现在:确定性的设计收敛;可扩展的数据模型架构、芯片规划层次化,快速综合、多维度分析布局器、功耗优化和分析、简化工程变更单(ECO)、流程自动化,非流程强制化;IP封装器、集成器和目录;Vivado HLS把ELS带入主流;VIVADO仿真器。

生态体系是关键 打造生态体系是赛灵思保证Vivado为客户带来更多价值的关键。

赛灵思在开发Vivado设计套件时充分利用业界标准来提高其易用性,支持已经熟悉的约束条件和接口标准,同时扩展第三方生态体系对IP和工具流程的支持。

Vivado支持的标准包括:AMBA AXI4互联、自由建模库、Synopsys设计约束等。

赛灵思认为,利用All Programmable器件创建系统,设计者将面对的是一套全新的集成以及如何实现设计生产力的问题。

从集成的角度看,包括集成算法C和寄存器传输级(RTL)的IP,混合了DSP、嵌入式、连接和逻辑域,验证模块和“系统”以及设计和IP的重用等。

Vivado实验01_流水灯仿真实验及下板步骤

一、新建工程1. 打开Vivado ,界面如下:2. 点击上述界面中的Create New Project ,弹出新建工程向导,依次点击Next:3.板卡选项分别为Family: Artix-7Sub-Family: Artix-7Package: csg324Speed grade: -1Temp grade: C于是,Part选择xc7a100tcsg324-1,然后下一步点击Next Finish;二、设计文件输入1.如下图,点击输入设计程序:2.如下图,选择新建文件,依次创建4个verilog文件,文件名依次为:clock_div; ctc; s_74ls138; led_light注意:最后一个为顶层文件,文件名与项目的文件名相同,且所有名称中不能出现中文、空格和符号3.双击打开,然后输入依次设计程序:注意:每次输入一个设计程序最好保存一次,保存操作如下图然后重复步骤,将4个设计程序依次输入保存4.添加仿真文件:5.进入仿真,点击 Run Simulation Run Behavioral Simulation6.调节缩小按钮,将间隔调节为1s,方便观察实验结果,然后点击上方运行按钮进行仿真,接着点击弹出的信息条的Background将其隐藏,即可看到完整的仿真循环结果7.仿真结果如下图:三、下板操作1.仿真完成后,先关闭仿真,操作如下图:2.接着进行下一步综合,如下图操作:3.综合处成功后,要进行实现操作,如下图:4.实现成功后进行下一步,管脚约束,操作如下图:注意:此处需用到板卡手册,请使用老师群共享的文件“Nexys4-DDR_rm”,此为配适的较新版本,否则可能出现错误5.约束文件生成后,更改为I/O操作界面:6.此处不能使用默认电压值,否则会报错,更改电压值为,然后将时钟引脚接至E3,复位引脚接至C12,y0至y7输出接至V16、T15、U14、T16、V15、V14、V15、V11,引脚的连接方式有三种,所有操作如下图:7.约束完成后,关闭保存:8.在源程序文档中的约束文件中可以看到刚才操作生成的约束文件,也可以直接在约束文件中直接输入代码来完成管教的约束和更改:9.约束完成后,生成编程文件:10.此时需要连接板卡到电脑,在此之前需要对板卡进行设置:11.连接电脑,打开电源开关,等待驱动安装完成后,打开Hardware Manager Open a new hardware target 在跳出的提示框中一直点击Next,不需更改,直到Finish Program device 选择板卡xc7a100t_0 在跳出的选择框中点击ok,这时就可以观察到仿真结果中的流水灯效果,以上为识别板卡到把编程文件下载到板卡的无脑操作,具体步骤请看下图:12.观察到板卡上的实验结果正确后,实验到此结束,关闭板卡的电源开关,拔出板卡,以上。

vivado 例子

vivado 例子如何使用Vivado进行FPGA开发[FPGA开发简介]FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有高度的可定制性和灵活性,被广泛应用于嵌入式系统、数字信号处理、图像处理等领域。

其中,Vivado是Xilinx公司开发的一款流行的FPGA 开发工具,提供了全面的硬件设计、仿真和综合等功能,本文将一步一步介绍如何使用Vivado进行FPGA开发。

[步骤一:Vivado软件安装]首先,我们需要从Xilinx官网下载并安装Vivado软件。

确保您的计算机符合最低系统要求,并遵循安装向导的步骤进行安装。

安装完成后,打开Vivado软件并选择“Create Project”选项。

[步骤二:创建项目]在“Create Project”对话框中,输入项目名称和路径,并选择项目类型和目标设备。

根据您的需求选择项目类型,比如RTL项目用于硬件设计,或是嵌入式系统项目用于处理器设计。

然后,选择目标设备,即您想要部署到FPGA上的芯片。

点击“Next”继续。

[步骤三:添加设计文件]在“Add Sources”对话框中,添加您的设计文件。

您可以选择从头开始编写Verilog或VHDL代码,也可以导入IP(Intellectual Property)核,即预先设计好的功能模块。

点击“Next”继续。

[步骤四:设置约束]在“Add Constraints”对话框中,添加约束文件。

约束文件用于描述输入输出端口的时序、引脚分配以及外部时钟等信息。

您可以手动编写约束文件,或是使用Vivado自动生成的约束文件。

点击“Next”继续。

[步骤五:综合与实现]在“Default Part”对话框中,选择目标设备的具体型号并点击“Next”。

然后,您需要选择综合(Synthesis)和实现(Implementation)的选项。

综合将设计文件转化为门级网表,实现将门级网表映射到目标设备的逻辑传输表或物理资源。

vivado设计实例

vivado设计实例Vivado设计实例一、时钟分频器设计实例时钟分频器在数字电路设计中起到非常重要的作用,它可以将一个高频时钟信号分频为任意低频时钟信号。

在Vivado中,实现一个时钟分频器非常简单。

首先,我们需要创建一个新的工程,并添加时钟分频器的IP核。

然后,在IP核配置界面中,设置分频比和时钟输入输出端口。

最后,生成Bitstream文件并下载到目标FPGA芯片中即可。

二、状态机设计实例状态机是一种常见的电路设计模块,它根据输入信号的变化来改变其内部状态和输出信号。

在Vivado中,实现一个状态机可以通过HDL语言(如Verilog或VHDL)编写代码来实现。

首先,我们需要创建一个新的工程,并添加设计文件。

然后,在设计文件中编写状态机的逻辑代码,并将其综合为门级电路。

最后,生成Bitstream 文件并下载到目标FPGA芯片中即可。

三、数字信号处理设计实例数字信号处理(DSP)在通信、音频、视频等领域有着广泛的应用。

在Vivado中,实现一个简单的数字信号处理模块可以通过使用FIR滤波器来实现。

首先,我们需要创建一个新的工程,并添加FIR滤波器的IP核。

然后,在IP核配置界面中,设置滤波器的参数和输入输出端口。

最后,生成Bitstream文件并下载到目标FPGA芯片中即可。

四、图像处理设计实例图像处理在计算机视觉、图像识别等领域有着广泛的应用。

在Vivado中,实现一个简单的图像处理模块可以通过使用图像卷积来实现。

首先,我们需要创建一个新的工程,并添加图像卷积的IP核。

然后,在IP核配置界面中,设置卷积核的参数和输入输出端口。

最后,生成Bitstream文件并下载到目标FPGA芯片中即可。

五、高级通信接口设计实例高级通信接口(如PCIe、Ethernet等)在计算机系统中起到连接和传输数据的重要作用。

在Vivado中,实现一个高级通信接口可以通过使用相应的IP核来实现。

首先,我们需要创建一个新的工程,并添加所需的IP核。

vivado 案例

vivado 案例以下是一个使用Vivado软件的案例:案例:设计一个4位二进制加法器1. 打开Vivado软件,创建一个新的工程。

2. 在"工程设置"对话框中,选择一个合适的工程目录,并设置工程名称。

3. 在"选择一个目标设备"对话框中,选择一个适合的FPGA设备。

4. 在"添加源"对话框中,添加一个新的RTL源文件。

命名为"binary_adder.v"。

5. 在"设计源"中输入以下代码:```verilogmodule binary_adder(input [3:0] a,input [3:0] b,output [3:0] sum,output carry);assign sum = a + b;assign carry = (a + b) > 15 ? 1'b1 : 1'b0;endmodule```6. 在"工程概要"视图中,点击"运行合成"以生成综合后的网表文件。

7. 在"工程概要"视图中,点击"运行实现"以生成比特流文件。

8. 在"工程概要"视图中,点击"生成比特流"以生成比特流文件。

9. 将生成的比特流文件下载到FPGA设备中,即可完成设计。

这是一个简单的案例,演示了如何使用Vivado软件设计一个4位二进制加法器。

通过编写Verilog代码,生成综合后的网表文件,并最终生成比特流文件,将其下载到FPGA设备中,实现了二进制加法器的功能。

vivado应用实例 -回复

vivado应用实例-回复Vivado应用实例[Vivado 应用实例] 是一个主题,下面将详细介绍如何使用Vivado 进行开发,并提供一些实例展示。

Vivado 是Xilinx 公司开发的一款集成化设计环境,用于FPGA(可编程逻辑门阵列)设计和验证。

通过Vivado,开发人员可以将自己的设计理念变为现实,并将其部署到支持的FPGA 设备上。

本文将分为以下几个部分进行介绍:1. Vivado 环境的安装和设置2. Vivado 项目的创建与管理3. 设计的综合、实现和生成比特流程4. Vivado IP 的应用5. 运行Vivado simulation1. Vivado 环境的安装和设置首先,我们需要从Xilinx 官方网站下载Vivado 的安装文件,并根据提示完成安装。

安装完成后,我们需要设置Vivado 的环境变量。

在Windows 操作系统中,打开系统属性的高级选项,点击环境变量,找到PATH 变量,在末尾添加Vivado 安装目录的路径。

2. Vivado 项目的创建与管理打开Vivado 工具,选择"Create a new project",输入项目名称和路径,并选择目标设备。

接下来,选择"RTL Project" 类型,并将"Source" 设置为"VHDL" 或"Verilog",视您的设计语言而定。

完成这些步骤后,单击"Next",然后选择需要添加到项目中的源文件。

最后,点击"Finish" 完成项目的创建。

3. 设计的综合、实现和生成比特流程在项目中,我们可以进行设计的综合、实现和生成比特的流程。

在综合阶段,Vivado 将会将您的设计代码转化为电路网表,以便后续处理。

在实现阶段,Vivado 将会将电路网表映射到目标FPGA 设备的资源上,并进行布局和布线。

Vivado设计套件的UltraFast设计方法指南

Vivado设计套件的UltraFast设计方法指南随着科技的不断发展,电子设计自动化(EDA)工具在集成电路设计领域变得越来越重要。

其中,ilinx的Vivado设计套件以其强大的功能和广泛的应用,成为了行业内的佼佼者。

在Vivado设计套件中,UltraFast设计方法是一种高效的设计流程,可以帮助设计师在短时间内完成复杂的设计任务。

一、Vivado设计套件概述Vivado设计套件是ilinx公司推出的一款综合性的EDA工具,专为FPGA设计而优化。

它提供了一套完整的解决方案,包括设计环境、IP核、工具和参考设计等,以支持从概念到实现的整个设计流程。

Vivado设计套件具有高度的可扩展性和灵活性,适用于各种不同的应用场景。

二、UltraFast设计方法简介UltraFast设计方法是Vivado设计套件提供的一种高级设计方法,旨在提高设计效率。

它基于IP封装器、高级综合和生成式综合等技术,提供了一系列的工具和流程,以加速FPGA设计的速度。

UltraFast 设计方法具有以下特点:1、快速实现:通过使用IP封装器和高级综合工具,设计师可以快速地将设计转换为FPGA上的实现。

2、高性能:UltraFast设计方法采用了生成式综合技术,可以在保证功能正确的前提下,生成高效的FPGA实现。

3、易用性:UltraFast设计方法提供了直观的用户界面和简单的流程,使设计师可以轻松地应用该方法。

三、UltraFast设计方法指南下面将介绍如何使用Vivado设计套件的UltraFast设计方法:1、创建新的项目:在Vivado设计中创建一个新的项目,并选择适当的FPGA器件。

2、定义输入和输出:在项目中定义所有的输入和输出端口,以便在设计中使用。

3、使用IP封装器:通过IP封装器,将现有的IP核封装为可重用的组件。

这可以大大减少设计时间和复杂度。

4、应用高级综合:使用高级综合工具,将HDL代码转换为RTL级设计。

vivado应用实例

vivado应用实例

Vivado是一个用于FPGA设计的集成开发环境(IDE),由Xilinx公司开发。

以下是一个简单的Vivado应用实例,用于设计一个简单的数字逻辑门电路:

1. 打开Vivado软件,并创建一个新的工程。

2. 在工程中添加一个Verilog源文件,用于描述数字逻辑门电路的逻辑行为。

例如,可以编写一个简单的AND门电路的Verilog代码。

3. 在Vivado中打开新添加的Verilog源文件,并使用Vivado的仿真工具对代码进行仿真,以确保其功能正确。

4. 在Vivado中创建一个新的IP封装器项目,并将Verilog源文件封装为可重用的IP核。

5. 在IP封装器项目中,配置IP核的参数,例如输入和输出信号的数量和类型。

6. 在IP封装器项目中,使用Vivado的布局和布线工具对IP核进行布局和布线,以生成最终的IP核。

7. 将生成的IP核集成到您的设计中,并在Vivado中进行仿真和调试。

8. 最后,将设计下载到FPGA设备中,并测试其实时性能。

这是一个简单的Vivado应用实例,通过它可以了解如何使用Vivado进行FPGA设计。

当然,Vivado还有许多其他功能和工具,可以根据具体的设计需求进行更深入的学习和应用。

Vivado高效设计案例分享

Vivado高效设计案例分享

首先,在这个页面上啰嗦几句。

左侧列出了软件不同的版本号,大家根据自己的需要选择相应的版本。

中间这一列就是我们需要下载的软件安装包了。

目前,Vivado支持windows和linux操作系统。

大家可以根据自己的操作系统选择对应的版本进行下载安装,也可以选择All OS Vivado and SDK Full Installer(推荐),这个软件包包含了逻辑开发和嵌入式开发所需的全部工具。

友情提醒,大家不闲麻烦的话,可以顺便把Documention Navigator一块下载安装。

这个软件可以帮助我们快速浏览Xilinx的所有文档资料。

接下来,就是老生常谈的话题了——环境搭建。

整个软件的安装过程非常傻瓜式,这里就不浓墨渲染了,有图有真相:

蜗牛的速度,整个安装过程耗时半个小时左右(与你电脑的性能有很大的关系),整个安装过程几乎不需要人为干预,因此这段时间可以泡杯茶享受一下生活。

安装过程中,会跳出窗口让你选择本机已经安装的MatLab,这是做DSP开发用的,大家暂时取消掉(以后使用可以重新配置)。

接近尾声的时候会弹出Xilinx的许可管理器让你安装许可证,相信很多童鞋暂时没有许可文件,所以我们只能无奈的点击X号。

接下来,我们就去Xilinx官网获取试用版的许可文件(前提是你已经注册过Xilinx的账号)。

注:我这里生成的是HLS评估板License,只是示意,大家根据自己的需求生成相应的License。

Vivado高效设计案例分享

Vivado高效设计案例分享------用vivado2013.4 进行zynq 嵌入式系统的设计软件平台:vivado 2013.4硬件平台:zybo 板卡计算机操作系统平台:win7 64位首先安装vivado 2013.4软件。

软件安装完成后,打开软件,构建zynq的嵌入式硬件平台。

操作流程如下:1. 打开软件,双击图标2.出现如下界面:3.点击 Create New Project,创建新的工程。

出现如下创建工程向导,点击next。

4. 创建新工程的名称,工程路径。

选择 create project subdirectory。

点击next,进入下一步。

5.创建一个RTL 工程,选择 Do not specify sources at this time。

点击next。

6. 选择parts,选择zynq芯片包括芯片的封装。

zybo 选用的是xc7z010clg400-1的芯片。

选择好芯片,点击next,进入下一步。

7.点击finish 这样一个RTL new project 工程已经建立好了。

8. RTL 工程建立完毕后,出现如下工程界面。

在这个工程里面,我们需要创建一个block design,点击create block design。

9. 输入设计名称,这里我选择默认的设计名称。

点击ok。

10. 在diagram 对话框里面选择 ADD IP。

11. 选择 zynq7 processing system 。

双击 zynq7 processing system 。

12. 点击run block automation。

并且选择rocessing_system7_0。

13. 点击ok。

14. 双击zynq 系统,进入系统设置。

15. 点击import XPS setting16. 从/Products/Detail.cfm?NavPath=2,400,1198&Prod=ZYBO网站上面可以下到 zybo_zynq——def.xml文件。

vivado模块化设计实例

vivado模块化设计实例Vivado是一款由Xilinx公司开发的集成电路设计工具,用于进行FPGA(现场可编程门阵列)的设计和开发。

在Vivado中,模块化设计是一种常用的设计方法,它可以将复杂的系统划分为多个独立的模块,每个模块负责特定的功能,从而提高设计的可维护性和可扩展性。

本文将以一个实例来介绍Vivado模块化设计的基本原理和步骤。

假设我们要设计一个简单的计数器电路,该电路可以接受外部时钟信号,并在每个时钟周期内将计数值加1。

首先,我们需要将整个电路划分为两个模块:时钟模块和计数器模块。

时钟模块负责接收外部时钟信号,并生成一个稳定的时钟信号,用于驱动计数器模块的工作。

在Vivado中,我们可以使用时钟模块生成器来生成时钟信号。

首先,我们需要在Vivado中创建一个新的工程,并添加一个时钟模块生成器IP核。

然后,我们可以设置时钟模块生成器的参数,如时钟频率、时钟相位等。

最后,我们将时钟模块生成器与FPGA芯片上的时钟资源相连接,以便将生成的时钟信号输出到计数器模块。

计数器模块负责接收时钟信号,并根据时钟信号的变化来更新计数值。

在Vivado中,我们可以使用Verilog或VHDL等硬件描述语言来实现计数器模块。

首先,我们需要在Vivado中创建一个新的源文件,并编写计数器模块的硬件描述代码。

在代码中,我们可以使用寄存器来存储计数值,并在每个时钟周期内根据时钟信号的变化来更新计数值。

最后,我们将计数器模块与时钟模块生成器相连接,并将计数器模块的输出端口连接到FPGA芯片上的LED等外部设备,以便显示计数值的变化。

通过以上步骤,我们已经完成了计数器电路的设计。

接下来,我们可以使用Vivado中的综合工具将设计代码综合为逻辑门级网表,然后使用实现工具将逻辑门级网表映射到目标设备的物理资源,并生成一个比特流文件,用于配置FPGA芯片。

最后,我们可以使用Vivado中的调试工具对设计进行验证和调试,以确保设计的功能和性能符合要求。

vivado仿真例程

在ThinkPHP 6中,你可以使用app()函数动态执行方法。

app()函数返回一个应用实例,你可以通过它来调用控制器、模型等方法。

下面是一个示例,演示如何动态执行方法:

php

use app\controller\ExampleController;

// 创建控制器实例

$controller = app(ExampleController::class);

// 调用控制器方法

$result = $controller->someMethod();

// 输出结果

dump($result);

在上面的示例中,我们首先使用app()函数创建了一个ExampleController控制器的实例。

然后,我们通过调用someMethod()方法来执行控制器中的某个方法。

最后,我们将结果输出到控制台。

请注意,你需要确保ExampleController类存在,并且someMethod()方法在该类中定义。

除了使用app()函数外,你还可以直接使用命名空间来动态执行方法。

例如:

php

use app\controller\ExampleController;

// 调用控制器方法

app(ExampleController::class)->someMethod();

这种方式与上面的示例类似,只是省略了创建控制器实例的步骤,直接通过命名空间来调用方法。

Vivado+Zedboard之入门实例精选

Vivado+Zedboard之入门实例精选继续介绍vivado+zedboard入门实例。

均为参照教程实际操作验证成功的实例,在此拿出来与大家分享。

由于教程中步骤已经非常清晰,本文只是简单介绍实例以及试验时的修正记录,具体的教程及个人实现在我的资源中可以找到。

本次介绍的实例为xilinx官网XUP下关于zedboard的实例。

链接为还是先介绍实验环境:环境:win7 64 vivado 2013.2 (从lab23开始切换为vivado2014.1版本)开发板:zedboard version d xc7z020clg484-1串口软件:SecureCRT1. lab2.2 Adding IP cores in PL监测开关值和键值的实例,读取并实时发送当前开关值和键值;增加了两个GPIO IP用于读取开关值和键值。

本例是一个完整的vivado+zedboard软硬件协同设计,可以了解vivado+zedboard开发流程,对zedboard开发板中的开关、按键的控制和使用以及串口通讯有所了解。

2. lab4.1 Building a Complete Embedded System这个例子很好,一个完整的嵌入式系统的例子。

测试Switch0-7和BTNR,可通过GPIO IP通过PL部分对开关和相应LED操作,也可以通过EMIO直接让PS与BTNR通信。

可以阅读下程序,对开关和按键的初始化、控制和使用原理有所了解,对GPIO和EMIO的读写有所了解。

本例最好选用VHDL语言以为本章其他实例准备。

部分步骤需要调整,已经在lab1.pdf中标注了。

需要解决源码中的xdc的问题:换为BNTR,重新create wrapper。

3. lab5.6 Creating a Processor System Lab非常好的实例,建议对zedboard感兴趣者一定试验下。

一个完整的vivado (block design)、SDK(C、download)、HLS(IP)设计实例,使用了Xilinx的IP、第三方IP、用户HLS设计的IP等,进行软硬件协同设计,软、硬件运行时间效果对比(这一点可以体现硬件甚至FPGA的速度优势)等。

使用VIVADO对7系列FPGA的高效设计心得

使用VIV ADO对7系列FPGA的高效设计心得随着xilinx公司进入20nm工艺,以堆叠的方式在可编程领域一路高歌猛进,与其配套的EDA工具——新一代高端FPGA设计软件VIV ADO也备受关注和饱受争议。

我从2012年开始使用VIV ADO,像所有刚推出的软件一样,在刚推出的时候都会存在一些bug,特别是VIV ADO2013.2\2013.3。

而最新的版本VIV ADO2013.4在32位的电脑上也是经常出现运行缓慢、自动退出或挂起等现象,相信在后面的版本中这些问题会得到很好的解决。

虽然存在一些bug但是它却阻挡不了VIV ADO高效的设计以及良好的布局布线效果。

下面我以我工作中碰到的一个工程为例来和大家分享一下VIV ADO的高效设计带给我们的全新感受!我的工程是一个ADC数据采集的例子,LVDS总线,12根数据线,DDR模式。

根据XILINX给出的xapp585,我将串并转换1:7的设计改成了串并转换1:4。

依然使用了selecTIO资源的ISERDES。

原设计框图如下:[[wysiwyg_imageupload:1348:]]其中CalibraTIonbitslipstatemachine和DeskewControl模块比较复杂并且使用了较多的算法,整个工程在ISE14.2中光综合过程就跑了将近5分钟左右,然后布局布线就更加的慢了。

将近跑了7分钟半。

后来我将整个工程移植到VIV ADO2013.4中,其效率快的让我吃惊,总共加起来不超过5分钟。

在使用VIV ADO的过程中有以下几个亮点,让我感觉效率确实提高不少。

第一,当版本升级后,相应的IP版本也要升级,但是不要担心,VIV ADO在检测到需要更新的IP后会提醒你更新,只要按着它的提示进行操作就可以将所有的IP一起更新,省去了很多麻烦。

第二,调试时,直接从netlist通过markdebug添加NET到ILA中,然后VIV ADO会将相应的约束自动添加到xdc文件中,最后通过VIV ADOLogicAnalyzer来查看波形。

vivado 204b设计实例

vivado 204b设计实例以下是一个vivado 204b的设计实例:实例一:设计一个带有两个输入和两个输出的4位全加器模块。

module fulladder4bit (input [3:0] A, B, // 连接到两个4位输入output [3:0] Sum, // 输出的和output CarryOut // 进位输出);// 分别将每一位的输入和输出连接到四个1位全加器fulladderFA0(.A(A[0]), .B(B[0]), .Ci(1'b0), .Sum(Sum[0]), .Co(wire0)); fulladderFA1(.A(A[1]), .B(B[1]), .Ci(wire0), .Sum(Sum[1]), .Co(wire1)); fulladderFA2(.A(A[2]), .B(B[2]), .Ci(wire1), .Sum(Sum[2]), .Co(wire2)); fulladderFA3(.A(A[3]), .B(B[3]), .Ci(wire2), .Sum(Sum[3]), .Co(CarryOut) );endmodule实例二:设计一个4位加法器模块,其中使用了实例一中设计的4位全加器。

module adder4bit (input [3:0] A, B, // 连接到两个4位输入output [3:0] Sum // 输出的和);// 实例化4个4位全加器fulladder4bitFA0(.A(A[0:0]), .B(B[0:0]), .Sum(Sum[0:0]), .CarryOut(wire0)); fulladder4bitFA1(.A(A[1:1]), .B(B[1:1]), .Sum(Sum[1:1]), .CarryOut(wire1)); fulladder4bitFA2(.A(A[2:2]), .B(B[2:2]), .Sum(Sum[2:2]), .CarryOut(wire2)); fulladder4bitFA3(.A(A[3:3]), .B(B[3:3]), .Sum(Sum[3:3]), .CarryOut(wire3));// 将进位线串联连接起来assign CarryOut = wire3;// 使用4个4位全加器的进位和输出来计算和endmodule这些实例演示了如何使用vivado来设计一个4位全加器和4位加法器。

用Vivado HLS高阶合成重构算法设计有效处理管道

用Vivado HLS高阶合成重构算法设计有效处理管道

目前的应用软件通常包含有复杂的内存访问机制,尤其是在科学计算和数字信号处理领域,内存的管理将十分复杂。

我们利用Vivado HLS设计了一个简单的例子,可以使你在一些棘手的情况下,用它来建造有效处理管道。

HLS试图在由高级语言描述的控制数据流图(CDFG)中获取平。

运算操作以及存储访问的分派与设计是根据他们与目标平台的紧缺资源间的独立性决定的。

对于许多引人关注的算法来说,数据存取依赖于计算结果,内存占用需要使用芯片外RAM。

如今,在内核上使用HLS会创造出数据通路以及许多指令级的并行。

但是当它被激活,且等待输入数据时,它需要频繁停止。

下图展示了当数据设置过大,且需要不断放到单片高速缓冲存储器上时,为实验效果而制造的硬件模块的运行效果。

值得注意的是速度的减慢对所有cache失效潜在因素组合的影响。

然而这不是必须的,因为有一部分计算图的发展是不需要立即使用内存数据的。

这个环节需要被快速推进。

这种在调度执行的额外自由有很多潜在的影响。

图2(c)展示了使用解耦处理管道时的调度执行。

双FIFO的潜在影响忽。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Vivado高效设计案例分享------用vivado2013.4 进行zynq 嵌入式系统的设计

软件平台:vivado 2013.4

硬件平台:zybo 板卡

计算机操作系统平台:win7 64位

首先安装vivado 2013.4软件。

软件安装完成后,打开软件,构建zynq的嵌入式硬件平台。

操作流程如下:

1. 打开软件,双击图标

2.出现如下界面:

3.点击 Create New Project,创建新的工程。

出现如下创建工程向导,点击next。

4. 创建新工程的名称,工程路径。

选择 create project subdirectory。

点击next,进入下一步。

5.创建一个RTL 工程,选择 Do not specify sources at this time。

点击next。

6. 选择parts,选择zynq芯片包括芯片的封装。

zybo 选用的是xc7z010clg400-1的芯片。

选择好芯片,点击next,进入下一步。

7.点击finish 这样一个RTL new project 工程已经建立好了。

8. RTL 工程建立完毕后,出现如下工程界面。

在这个工程里面,我们需要创建一个block design,点击create block design。

9. 输入设计名称,这里我选择默认的设计名称。

点击ok。

10. 在diagram 对话框里面选择 ADD IP。

11. 选择 zynq7 processing system 。

双击 zynq7 processing system 。

12. 点击run block automation。

并且选择rocessing_system7_0。

13. 点击ok。

14. 双击zynq 系统,进入系统设置。

15. 点击import XPS setting

16. 从

/Products/Detail.cfm?NavPath=2,400,1198&Prod=ZYBO网

站上面可以下到 zybo_zynq——def.xml文件。

下载该文件,在这里选择下载的文件。

17.进入MIO Configuration,取消USB0.SD0.I2C0。

进入PS-PL configuration里面,取消FCLK_RESET0_N和M_AXI_GP0 interface,进入Clock configuration,取消FCLK_CLK0.点击OK保存修改设置。

18. 点击Ctrl+S 保存 block 设计。

19 右击你的设计block 。

选择 create HDL wrapper。

20. 选择 let vivado manage wrapper and auto-update。

21. 选择 generate block design。

22点击generate。

这样一个zynq的嵌入处理器系统就完成了。

这里使用vivado 2013.4 设计了一个zynq 的processing system。

今天就写到这了,希望可以跟大家一起共同学习,共同进步。