FPGA乘法器毕业设计开题报告

基于FPGA数字乘法器的设计

的硬件资源较少, 但每个时钟周期内只能完成 8 位乘 1 位的运算, 因此要完成 8 位乘 8 位的运算, 则至少需要 8 个时钟周期, 速度较 慢。其硬件结构框图为:

图 2 移位相加乘法器结构框图 2.2 加法器树乘法器 如果将乘数的 8 位拆开, 则该乘法运算可以写成如下的表达 方式: Y=A×B=( A0+A1×2+A2×22+A3×23+A4×24+A5×25+A6×26+ A7×27 ) ×B=B×A0+B×A1×2+……+B×A6×26+B×A7×27 这样, 就可以将 8 位乘 8 位的运算转换成 8 个 8 位乘 1 位的 运算, 式中的每一项都可以通过与门得到。因此乘法器只需要一个 时钟周期就可以完成乘法运算, 理论上讲速度很快。但是由于使用 了多个加法器, 使其占用的片内资源面积较大, 而且使用多个加法 器必然会产生一定的延迟, 使得时钟频率不会太高。加法器树的结 构框图如图 2 所示: 注: P: 高位补 0 Q: 低位补 0 1*: 高 6 位 补 0, 第 十 位 为 进 位 位 2*: 高 4 位 补 0, 低 2 位 补 0, 第 12 位为进位位 3*: 高 2 位补 0, 低 4 位补 0, 第 14 位 为 进 位 位 4*: 低 6 位 补 0, 最高位为进位位

参考文献: [1]刘 凌,胡 永 生.数 字 信 号 处 理 FPGA 实 现[M].北 京:清 华 大 学 出 版 社 ,2003. [2]段 吉 海,黄 智 伟.基 于 CPLD/FPGA 的 数 字 通 信 系 统 建 模 与 设 计 [M].北 京 :电 子 工 业 出 版 社 ,2004. [3]侯伯亨,顾欣.VHDL 硬件描述语言与数字逻辑电路设计[M] 西 安 :西 安 电 子 科 技 大 学 出 版 社 ,2001. [4]Ma G K,Taylor F J.Multiplier policies for digital signal pro- cessing[J].IEEE A SSP Magazine,1990,7(1):6- 20.

基于FPGA的8位硬件乘法器设计

本科毕业设计基于FPGA的8位硬件乘法器设计摘要VHDL(VHSIC Hardware Description Language)是当今最流行的硬件描述语言之一,能够对最复杂的芯片和最完整的电子系统进行描述。

以硬件描述语言作为设计输入,经过简单的综合与布局,快速烧录至FPGA(Field Programmable Gate Array)上进行测试,是现代IC设计验证的技术主流。

乘法器是处理器进行科学计算和数字信号处理的基本硬件结构,是现代微处理器中的重要部件。

乘法器完成一次乘法操作的周期基本上决定了微处理器的主频。

本文基于FPGA,采用VHDL语言,结合MAX+plusⅡ这个强大的软件平台设计了8位二进制乘法器,并对其进行符号扩展,使其可以统一处理8位带符号数和无符号数。

高速乘法器设计通常分为三个关键步骤:部分积产生、部分积累加和最终结果获得。

本文对部分积产生过程采用改进Booth算法,有效减少部分积加法项;为了统一带符号和无符号数,对部分积进行符号扩展;而对部分积的累加则采取3-2压缩器和4-2压缩器进行压缩;最终结果的获得则以一个根据部分积累加结果到达时间的不同进行延迟优化的选择进位加法器将累加结果和累加进位相加而得。

关键词:乘法器改进Booth算法压缩器选择进位加法器The Circuit Design of 8-bit Hardware Multiplier Based on FPGAKe Xiuyan(College of Engineering, South China Agricultural University, Guangzhou 510642, China) Abstract: VHSIC Hardware Description Language, one of today's most popular hardware description languages, is used to describe the most complex chip and most complete electronic systems.The multiplier is not only the basic hardware structure of the processor for scientific computing and digital signal processing but also an important component of modern microprocessors. This design for 8-bit binary multiplier is based on FPGA, using VHDL language, and proved by the MAX+plusⅡsoftware platform. The multiplicand has an extended sign bit so that the multiplier can unify 8-bit signed and unsigned.High-speed multiplier design is usually divided into three key steps: partial product generation circuit, accumulator and adder. In this paper, the partial product generation process uses the modified Booth algorithm, so that the partial product addition terms can be effectively reduced. The accumulation of partial products takes 3-2 compressor and 4-2 compressor to compress. The final result is obtained with select carry adder.Key words: multiplier the modified Booth algorithm compressor select carry adder目录1 前言 (1)1.1 乘法器的研究背景和意义 (1)1.2 乘法器的研究发展状况 (1)2 总体方案确定 (2)2.1 乘法器设计方案 (2)2.2 硬件描述语言VHDL (3)2.2.1 硬件描述语言 (3)2.2.2 VHDL语言简介 (3)2.2.3 VHDL的基本结构 (4)2.2.4 VHDL的优点 (4)2.3 实验工具MAX+plusⅡ (5)2.3.1 MAX+plusⅡ简介 (5)2.3.2 MAX+plusⅡ的设计流程 (6)2.3.3 MAX+plusⅡ的特点 (6)2.4 现场可编辑门阵列(FPGA) (7)2.4.1 FPGA简介 (7)2.4.2 FPGA的基本结构 (7)2.4.3 FPGA的特点 (8)3 理论分析及设计 (9)3.1 乘法器的数据格式 (9)3.1.1 二进制的表示 (9)3.1.2 无符号数的运算 (9)3.1.3 带符号数的运算 (9)3.1.4 带符号数的符号扩展表示 (9)3.2 乘法器算法 (10)3.2.1 移位相加算法 (10)3.2.2 Booth算法 (11)3.2.3 改进型Booth算法 (12)3.3 加法器 (15)3.3.1 半加器 (15)3.3.2 全加器 (16)3.3.3 串行进位加法器 (16)3.3.4 超前进位加法器 (17)3.3.5 选择进位加法器 (18)3.4 压缩器 (19)4 测试与试验分析 (22)4.1 乘法器的总体结构 (22)4.2 乘法器各个模块的仿真 (23)4.2.1 Booth编码器 (23)4.2.2 Booth译码器 (23)4.2.3 部分积产生电路 (24)4.2.4 压缩器 (25)4.2.5 加法器 (26)4.2.6 顶层文件 (27)5 结论 (28)参考文献 (29)附录 (30)致谢 (33)毕业设计成绩评定表1 前言1.1 乘法器的研究背景和意义微电子技术的迅猛发展,计算机技术的不断进步,带动了集成电路工艺的不断增进,数字芯片的集成度不断提高。

fpga毕业设计开题报告.doc

fpga毕业设计开题报告FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

以下是fpga毕业设计,欢迎阅读。

1选题目的意义和可行性在这个时间就是金钱的年代里,数字电子钟已成为人们生活中的必需品。

目前应用的数字钟不仅可以实现对年、月、日、时、分、秒的数字显示,还能实现对电子钟所在地点的温度显示和智能闹钟功能,广泛应用于车站、医院、机场、码头、厕所等公共场所的时间显示。

随着现场可编程门阵列( field program-mable gate array ,FPGA) 的出现,电子系统向集成化、大规模和高速度等方向发展的趋势更加明显,作为可编程的集成度较高的ASIC,可在芯片级实现任意数字逻辑电路,从而可以简化硬件电路,提高系统工作速度,缩短产品研发周期。

故利用FPGA这一新的技术手段来研究电子钟有重要的现实意义。

设计采用FPGA现场可编程技术,运用自顶向下的设计思想设计电子钟。

避免了硬件电路的焊接与调试,而且由于FPGA的I /O 端口丰富,内部逻辑可随意更改,使得数字电子钟的实现较为方便。

本课题使用Cyclone EP1C6Q240的FPGA器件,完成实现一个可以计时的数字时钟。

该系统具有显示时、分、秒,智能闹钟,按键实现校准时钟,整点报时等功能。

满足人们得到精确时间以及时间提醒的需求,方便人们生活。

2 研究的基本内容与拟解决的主要问题2.1研究的基本内容数字时钟是采用电子电路实现对时间进行数字显示的计时装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度不断提高。

数字时钟系统的实现有很多,可以利用VerilogDHL语言在Quartus II里实现时、分、秒计数的功能。

在芯片内部存储器设24个字节分别存放时钟的时、分、秒信息。

数字时钟首先是秒位(共8位)上按照系统时钟CLK进行计数,存储器内相应的秒值加1;若秒位的值达到60(110000),则将其清零,并将相应的分位(共8位)的值加1;若分值达到60(110000),则清零分位,并将时位(共8位)的值加1;若计数满24(100100)后整个系统从0开始重新进行计数。

【设计】基于FPGA的计算器设计毕业论文

【关键字】设计毕业设计(论文)题目: 基于FPGA 的计算器设计The design of calculator based on FPGA基于FPGA的计算器设计研究生:XX 指导老师:XX摘要本文介绍了一个简单计算器的设计,基于硬件描述语言VHDL采用了现场可编程逻辑器件FPGA进行设计,并在Altera公司的Quartus Ⅱ软件上实现仿真。

系统由键控模块、运算、保存模块和译码显示模块四个部分组成,计算部分为加法器、减法器、乘法器和除法器,保存部分需要3个保存器来实现:内部累加器(acc)、输入寄存器(reg)以及结果暂存器(ans)。

显示部分由四个七段译码管组成,分别来显示输入数字,输入部分采用外接键盘,外部的8个按键他们能以单键和组合键的形式完成0~9999之内的‘加’、‘减’、‘乘’、‘除’、‘符号变换’、‘保存数据’和‘读取数据’等七种功能运算其结构简单,易于实现。

关键词:FPGA;VHDL;计算器;设计The design of calculator based on FPGAGraduate Student: Dongdong Fan Supervisor: Shuxiang SongAbstractThis article describes the design of a simple calculator, the design uses Field Programmable Gate Array FPGA based on VHDL hardware description language to design and Altera's Quartus Ⅱ in software for emulation. This system is componented by the key control module, computing, storage and decoding display module of the four parts, the computing part include adder, subtractor, multiplier and divider,Storage part needs three memory to help achieved: internal accumulator (acc), input register (reg) as well as the results of registers (ans). Display part is made up four decoder of 7 sections, respectively to show the number of input. The 8 keys they can by single combined key forms to be completed addition, multiplication, division arithmetic operator and symbol transform,stored data and read seven function of operation within 0 to 9999 numbers.its structure is simple and easy to implement.Key words:FPGA; VHDL; calclute ; design目录第1章引言1.1 课程设计的目的与意义在人类学会交易的时候,计算也随之产生,而算盘作为计算最实用的工具存在了几千年。

基于fpga八位硬件乘法器课程设计

基于FPGA的八位硬件乘法器课程设计,可以分以下几个步骤进行:

1. 确定设计要求:根据要求,设计一个能对两个八位二进制数进行乘法运算的硬件电路。

需要考虑到输入、输出、各种控制信号等。

2. 确定设计方案:根据设计要求,确定具体的设计方案。

可以使用Verilog语言进行描述,包括输入输出端口的定义、状态转移的描述等。

3. 编写Verilog代码:根据设计方案,编写Verilog代码。

代码需要对各种信号进行定义,并实现相应的逻辑功能。

4. 进行仿真:在编写完代码后,进行功能仿真。

可以使用ModelSim等仿真工具进行验证。

对代码进行仿真测试,在设计出现问题时可以及时进行调试和修改。

5. 进行综合和布局布线:通过综合和布局布线操作,将Verilog代码映射到FPGA芯片上,并生成bit文件,用于烧录到FPGA芯片中。

6. 进行验证:将bit文件烧录到FPGA芯片中,进行验证。

可以通过开发板上的按键等方式,输入两个八位二进制数并进行乘法运算,同时显示结果。

设计八位硬件乘法器需要了解数字电路设计基础知识和Verilog语言的使用。

同时,需要熟练掌握FPGA开发板的使用,以及相关的开发工具(如Quartus II等)的使用。

fpga毕业设计开题报告

fpga毕业设计开题报告fpga毕业设计开题报告FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

以下是fpga毕业设计开题报告,欢迎阅读。

1选题目的意义和可行性在这个时间就是金钱的年代里,数字电子钟已成为人们生活中的必需品。

目前应用的数字钟不仅可以实现对年、月、日、时、分、秒的数字显示,还能实现对电子钟所在地点的温度显示和智能闹钟功能,广泛应用于车站、医院、机场、码头、厕所等公共场所的时间显示。

随着现场可编程门阵列( field program-mable gate array ,FPGA) 的出现,电子系统向集成化、大规模和高速度等方向发展的趋势更加明显,作为可编程的集成度较高的ASIC,可在芯片级实现任意数字逻辑电路,从而可以简化硬件电路,提高系统工作速度,缩短产品研发周期。

故利用FPGA这一新的技术手段来研究电子钟有重要的现实意义。

设计采用FPGA现场可编程技术,运用自顶向下的设计思想设计电子钟。

避免了硬件电路的焊接与调试,而且由于FPGA的 I /O端口丰富,内部逻辑可随意更改,使得数字电子钟的实现较为方便。

本课题使用Cyclone EP1C6Q240的FPGA器件,完成实现一个可以计时的数字时钟。

该系统具有显示时、分、秒,智能闹钟,按键实现校准时钟,整点报时等功能。

满足人们得到精确时间以及时间提醒的需求,方便人们生活。

2 研究的基本内容与拟解决的主要问题2.1研究的基本内容数字时钟是采用电子电路实现对时间进行数字显示的计时装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度不断提高。

数字时钟系统的实现有很多,可以利用VerilogDHL语言在Quartus II里实现时、分、秒计数的功能。

在芯片内部存储器设24个字节分别存放时钟的时、分、秒信息。

数字时钟首先是秒位(共8位)上按照系统时钟CLK进行计数,存储器内相应的秒值加1;若秒位的值达到60(110000),则将其清零,并将相应的分位(共8位)的.值加1;若分值达到60(110000),则清零分位,并将时位(共8位)的值加1;若计数满 24(100100)后整个系统从 0开始重新进行计数。

基于FPGA的乘法器设计

基于FPGA的乘法器设计乘法运算在数字信号处理、图像处理、通信系统等领域中非常常见。

传统的乘法运算通常是通过乘法器件(如芯片)来实现,这样的乘法器件通常是专用定制的,功耗高、成本昂贵。

而基于FPGA的乘法器设计可以通过编程的方式,在硬件级别上实现乘法运算,具有灵活性高、性能可调的优势。

1. 确定乘法算法:乘法运算的算法有很多种,比如简单乘法、Booth 算法、Wallace树算法等。

根据实际需求,选择适合的乘法算法。

2.确定数据位宽:乘法器设计需要根据给定的乘法算法确定输入数据的位宽和输出结果的位宽。

位宽的选择对乘法器的性能有重要影响,过小的位宽可能导致精度不足,过大的位宽则会增加硬件资源的使用。

3.设计乘法核心:乘法核心是乘法器设计的核心部分,根据选择的乘法算法和数据位宽,设计乘法核心的逻辑电路。

乘法核心通常包括乘法器和累加器。

4.优化设计:乘法器的设计需要考虑优化性能和资源利用率。

常见的优化方法包括流水线设计、并行计算、减少不必要的运算等。

5. 编写硬件描述语言(HDL)代码:HDL是一种用于描述硬件电路的语言,比如Verilog和VHDL。

根据设计的乘法器模块,编写HDL代码来描述乘法器的功能和电路结构。

6.仿真和调试:通过利用仿真工具对设计好的乘法器进行功能验证和调试,发现并修复存在的问题。

1.灵活性高:FPGA的可编程性使得乘法器的设计可以根据实际需求进行灵活调整和修改,而不需要重新设计和生产乘法器芯片。

2.性能可调:FPGA的资源(逻辑单元)可以根据需要配置使用,可以通过增加逻辑单元和优化设计来提高乘法器的性能。

3.低功耗:相比于专用乘法器件,基于FPGA的乘法器通常具有更低的功耗,可以在一定程度上减少系统能耗。

4.成本低:由于FPGA是可编程设备,相对于专用乘法器件的生产成本要低,尤其适用于小批量生产和特定需求。

综上所述,基于FPGA的乘法器设计具有灵活性高、性能可调和成本低的优势,能够满足不同领域对于乘法运算的需求。

高性能并行乘法器关键技术研究的开题报告

高性能并行乘法器关键技术研究的开题报告一、选题背景乘法器是数字系统中最常用的基本运算单元之一,高性能并行乘法器的研究具有重要的理论和应用价值。

随着现代计算机系统的发展,计算机的高性能已成为众多应用领域所关注的热点。

高性能乘法器是目前运算器件中的重要一环,因此其研究意义重大。

二、研究的目的和意义高性能并行乘法器是一种基本的运算单元,涉及到很多重要的概念和技术,如冗余算法、位平面计算、留数算法等。

因此,本研究旨在深入研究高性能并行乘法器关键技术,以提高乘法器的运算速度和计算精度,为现代计算机系统提供更强的计算能力和应用服务。

三、研究内容及主要技术难点(一)研究内容1、高性能并行乘法器的基本原理和算法2、冗余算法在高性能并行乘法器中的应用3、位平面计算在高性能并行乘法器中的应用4、留数算法在高性能并行乘法器中的应用5、机器学习在高性能并行乘法器中的应用(二)主要技术难点1、对高性能并行乘法器的原理和算法的深入理解和研究2、冗余算法、位平面计算和留数算法在高性能并行乘法器中的应用3、机器学习在高性能并行乘法器中的应用四、研究方法本研究采用理论研究和实验研究相结合的方法,主要进行以下研究:1、对高性能并行乘法器的基本原理和算法进行理论分析和研究。

2、对冗余算法、位平面计算和留数算法在高性能并行乘法器中的应用进行实验验证和分析。

3、将机器学习应用到高性能并行乘法器中,进行实验验证和分析。

五、研究进度安排本研究将分为三个阶段进行:第一阶段:研究高性能并行乘法器的基本原理和算法,分析其性能指标,进行理论分析,撰写论文。

第二阶段:研究冗余算法、位平面计算和留数算法在高性能并行乘法器中的应用,进行实验验证和分析,撰写论文。

第三阶段:将机器学习应用到高性能并行乘法器中,进行实验验证和分析,撰写论文。

六、预期成果1、深入研究高性能并行乘法器的原理和算法,掌握冗余算法、位平面计算和留数算法在其中的应用。

2、提出一种将机器学习应用到高性能并行乘法器中的新方法。

fpga课程设计乘法器

fpga课程设计乘法器一、课程目标知识目标:1. 让学生掌握FPGA的基本原理和结构,理解乘法器的设计方法。

2. 使学生了解数字信号处理中乘法运算的重要性,掌握乘法器的功能和应用。

3. 帮助学生掌握Verilog HDL语言编程,并能运用该语言设计简单的乘法器电路。

技能目标:1. 培养学生运用FPGA进行数字电路设计的能力,提高实际问题解决能力。

2. 培养学生运用Verilog HDL语言进行编程,实现特定功能的乘法器电路。

3. 培养学生进行团队协作,完成课程设计任务,提高沟通与协作能力。

情感态度价值观目标:1. 培养学生对FPGA技术及其应用的兴趣,激发学生的创新意识。

2. 培养学生严谨、务实的科学态度,养成勤奋、刻苦的学习习惯。

3. 增强学生的国家使命感和社会责任感,认识到我国在FPGA领域的发展潜力。

课程性质:本课程为电子工程与技术专业课程,以实践为主,理论联系实际。

学生特点:学生具备一定的电子电路基础和编程能力,对FPGA技术有一定了解。

教学要求:结合课程特点和学生特点,注重实践操作,提高学生的动手能力和创新能力。

在教学过程中,注重引导学生自主学习,培养团队协作精神。

通过课程学习,使学生能够独立完成乘法器的设计与实现,为后续相关课程打下坚实基础。

二、教学内容1. FPGA基本原理和结构复习:回顾FPGA的内部结构、工作原理以及配置技术,重点理解查找表(LUT)的原理和应用。

相关教材章节:第一章 FPGA概述。

2. 数字乘法器原理:介绍乘法器在数字信号处理中的应用,分析不同类型的乘法器设计方法,如并行乘法器、串行乘法器等。

相关教材章节:第三章 数字乘法器设计。

3. Verilog HDL语言编程基础:复习Verilog HDL的基本语法,重点掌握模块定义、数据类型、运算符和赋值语句等。

相关教材章节:第二章 Verilog HDL基础。

4. 乘法器设计实践:结合实际案例,引导学生利用Verilog HDL语言设计一个简单的乘法器电路,包括设计、仿真和综合。

基于FPGA的乘法器设计综述

信息科学与技术学院电子EDA技术课程设计课程题目:基于FPGA的乘法器设计目录中文摘要 (2)外文摘要 (2)1.绪论 (3)1.1概述 (3)1. 2 VHDL简介 (3)1.3实验平台 (5)2.乘法器初步设计 (6)2.1设计思想 (6)2.2乘法器原理 (6)2.3 乘法器设计流程 (7)3. 乘法器具体设计 (9)3.1右移寄存器的设计 (9)3.2 加法器模块的设计 (9)3.3 乘1模块设计 (10)3.4锁存器模块设计 (11)4. 乘法器仿真 (13)4.1 8位加法器仿真 (13)4.2 乘1模块仿真 (13)4.3 锁存器模块仿真 (14)4.4 8位乘法器仿真 (14)4.5 总仿真图 (15)参考文献 (16)摘要在微处理器芯片中,乘法器是进行数字信号处理的核心,同时也是微处理器中进行数据处理的关键部件,它已经是现代计算机必不可少的一部分。

本文主要是在于如何运用标准硬件描述语言(VHDL)完成十六位乘法器,以及如何做二进制位相乘的运算过程。

该乘法器是由十六位加法器构成的以时序方式设计十六位乘法器,通过逐项移位相加来实现乘法功能,并以Quartus_II9.1软件工具进行模拟,仿真并予以显示。

关键字:乘法器;标准硬件描述语言(VHDL);移位相加;Quartus_II9.1AbstractIn the microprocessor chip, the multiplier is a digital signal processing core microprocessor is also a key component of data processing, it is already an essential part of the modern computer. This article is on how to use standard hardware description language (VHDL) to complete eight multipliers, as well as how to make the process of a binary bit multiplication operation. The multiplier is composed of eight adder to timing approach in designing eight multiplier, achieved by adding the multiplication-by-shift function, and in Quartus_II9.1 software tools for simulation, emulation and be displayed.Keywords: multiplier; standard hardware description language (VHDL); shift sum; Quartus_II9.11.绪论1.1概述本课题的设计来源是基于标准硬件描述语言(Very High Speed Integrated Circuit Hardware Description Language,VHDL)及Quartus_II9.1软件开发工具的进行模拟仿真的16位乘法器,用于实现32位移位相加乘法器的乘法运算功能。

基于FPGA的乘法器设计和实现

基于FPGA的阵列乘法器的设计与实现

基于FPGA的阵列乘法器的设计与实现本文先对乘法器进行了分析,然后用现场可编程门阵列(FPGA)实现了阵列乘法器,并分析了设计原理。

0 引言乘法是运算中的基本算法,应用也最为广泛。

在计算机中乘法最基本的操作就是移位相加,各类乘法最终都要归结为这一点。

早期计算机中为了简化硬件结构,采用串行的移位乘法方案,即多次执行“加法-移位”操作来实现。

这种方法并不需要很多器件。

然而串行方法毕竟太慢,自从大规模集成电路问世以来,出现了各种形式的并行乘法器,一部分即为流水式阵列乘法器。

1 二进制乘法器设有两个不带符号的M×N位二进制整数:点击图片查看大图点击图片查看大图它们的乘积用X和表示,按“手工计算”的方法给出就是:点击图片查看大图从中可以看出,只要a k≠0,输入量X就随着k的位置连续地变化,然后累加X2k。

如果a k=0,就可以忽略相应的转换相加。

以201×9为例,可以知道N=8,X=9,A=11001001。

当k由0开始递增时,对A的a k位进行分析,a0=1,则X20=9;a1=0,则X21=0;…a7=1,则X27=9×128=1152。

同时,将计算结果X2k:9,0,0,72,0,0,576,1152进行累加。

最终各部分结果之和即为201×9的乘积1809。

1.1 移位乘法器移位乘法器计算过程为:将A依次向右移一位,并检查其最低位a0,如果不为零,则将X与部分和相加,然后将X向左移一位;如果为零,则仅仅将X向左移一位。

移位时,X的低端和A的高端均补零。

可以看出由于第一个操作数X是并行形式的,而第二个操作数A是逐位形式的,所以刚才描述的乘法器也称为串行/并行乘法器。

如果两个操作数都是串行的,那么这一结构称为串行/串行乘法器。

这样的乘法器只需要一个全加器,但是计算乘积所需的时间更长。

1.2 阵列乘法器移位乘法器是通过牺牲时间来降低复杂性,还有一种方法通过增加复杂性来换取速度,称之为“阵列”,或者叫并行/并行乘法器。

浮点乘法运算部件的设计的开题报告

浮点乘法运算部件的设计的开题报告

题目:浮点乘法运算部件的设计

一、选题背景和意义

随着现代计算机的发展,计算的精度和速度都有了明显的提高,而浮点乘法运算是计算机进行科学计算、图像处理等应用时常用的运算之一。

因此,浮点乘法运算部件的高效率设计至关重要。

二、研究现状

目前,已有很多学者对浮点乘法运算部件进行了研究和开发,其中以FPGA实现和ASIC实现的设计居多。

这些设计往往要考虑到精度、速度、功耗等多方面的因素,在设计上非常复杂。

三、研究内容和步骤

本课题计划使用Verilog HDL对一个基本的浮点乘法运算部件进行设计与实现。

设计将分为以下步骤:

1.学习Verilog HDL语言的基本语法和面向对象程序设计思路;

2.学习浮点乘法的运算原理和实现方法;

3.根据需求设计浮点乘法运算部件的模型,包括乘法器、阶码部分、尾数部分;

4.编写测试程序对设计的浮点乘法运算部件进行仿真;

5.利用FPGA实现设计,并测试其性能和正确性;

6.完成实验报告和设计文档。

四、预期目标和意义

本课题预期达到以下目标:

1.熟练掌握Verilog HDL语言的使用和基本的面向对象程序设计思路;

2.掌握浮点乘法运算的原理和实现方法;

3.设计出高效、准确的浮点乘法运算部件,并对其进行仿真测试和FPGA实现;

4.在实现过程中加深对FPGA技术的理解和应用技能。

本课题的完成将在理论和实践层面都为浮点乘法运算部件的设计提供新的思路和实现方法,对浮点乘法运算的精度、速度和功耗等方面的优化提供帮助和支持。

同时,课题的完成也将对学术研究和计算机应用方面有所贡献。

4FPGA实验报告8位乘法器—徐艺萍

实验四8位乘法器实验一、实验原理8位乘法器,输入为两个8位信号,输出结果为16位。

module mult8(out, a, b); //8位乘法器源代码parameter size=8;input[size-1:0] a,b; //两个操作数output[2*size-1:0] out; //结果assign out=a*b; //乘法运算符endmodule本实验采用Chipscope-Pro生成VIO/ICON核,并插入到8位乘法器设计中,在线进行观测和调试。

二、实验目的1. 熟悉ISE9.1 开发环境,掌握工程的生成方法;2. 熟悉SEED-XDTK XUPV2Pro 实验环境;3. 了解Verilog HDL语言在FPGA 中的使用;4. 通过掌握8位乘法器的Verilog HDL设计,了解数字电路的设计。

三、实验内容1. 用Verilog HDL语言设计8位乘法器,进行功能仿真验证。

2. 使用chipscope-Pro 生成VIO/ICON 核,在线观测调试。

四、实验准备1. 将USB 下载电缆与计算机及XUPV2Pro 板的J8 连接好;2. 将RS232 串口线一端与计算机连接好,另一端与板卡的J11 相连接;3. 启动计算机,当计算机启动后,将XUPV2Pro 板的电源开关SW11 打开到ON 上。

观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指示灯是否均亮。

若有不亮的,请断开电源,检查电源。

五、实验步骤⑴创建工程及设计输入①在E:\project\目录下,新建名为mult8的新工程;器件族类型(Device Family)选择“Virtex2P”,器件型号(Device)选“XC2VP30 ff896 -7”,综合工具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator”②设计输入并保存。

最新乘法器实验报告

最新乘法器实验报告实验目的:本实验旨在验证乘法器的工作原理,并通过实际操作加深对数字电路中乘法运算实现的理解。

通过构建和测试不同的乘法器电路,我们将分析其性能和适用场景,以及可能的改进方向。

实验设备和材料:1. FPGA开发板2. 集成电路芯片(包括乘法器芯片)3. 示波器4. 电源5. 连接线和面包板6. 计算机辅助设计(CAD)软件7. 数字逻辑分析仪实验步骤:1. 设计一个基本的乘法器电路图,使用CAD软件进行电路模拟。

2. 根据电路图在FPGA开发板上搭建实际电路。

3. 准备测试向量,包括一系列的二进制数值,用于乘法器的输入。

4. 连接电源,使用示波器观察乘法器的输出结果。

5. 对输出结果进行分析,验证其正确性,并记录在实验报告中。

6. 改变输入值,重复步骤4和5,以测试乘法器对不同输入的处理能力。

7. 使用数字逻辑分析仪进一步分析乘法器的性能,包括运算速度和资源消耗。

8. 根据实验结果,提出可能的改进措施和乘法器的应用前景。

实验结果:在本次实验中,我们成功搭建并测试了一个基本的乘法器电路。

通过对不同输入值的测试,我们发现乘法器能够准确地计算出两个二进制数的乘积。

实验数据显示,乘法器的运算速度和资源消耗符合预期,但在处理大数值乘法时存在一定的局限性。

讨论与改进:实验结果表明,所构建的乘法器在处理小数值乘法时表现良好,但在处理大数值时,由于资源限制和运算速度的约束,性能有所下降。

为了改进这一点,可以考虑使用更高效的算法,如Booth算法或Wallace 树算法,来优化乘法器的设计。

此外,通过优化电路布局和使用更高性能的集成电路,也可以提高乘法器的整体性能。

结论:通过本次实验,我们验证了乘法器的基本原理和工作性能,并通过实际操作加深了对其设计和应用的理解。

未来的研究可以集中在提高乘法器的运算速度和减少资源消耗上,以适应更广泛的应用需求。

FPGA乘法器的应用

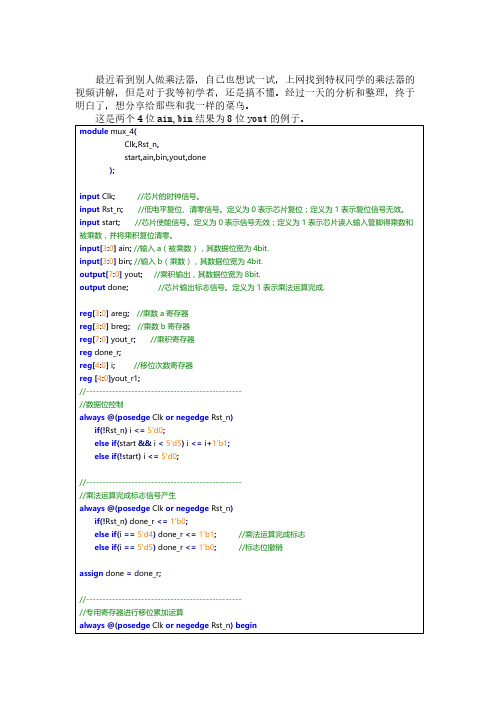

最近看到别人做乘法器,自己也想试一试,上网找到特权同学的乘法器的视频讲解,但是对于我等初学者,还是搞不懂。

经过一天的分析和整理,终于明白了,想分享给那些和我一样的菜鸟。

这是两个4位ain,bin结果为8位yout的例子。

module mux_4(Clk,Rst_n,start,ain,bin,yout,done);input Clk;//芯片的时钟信号。

input Rst_n;//低电平复位、清零信号。

定义为0表示芯片复位;定义为1表示复位信号无效。

input start;//芯片使能信号。

定义为0表示信号无效;定义为1表示芯片读入输入管脚得乘数和被乘数,并将乘积复位清零。

input[3:0] ain;//输入a(被乘数),其数据位宽为4bit.input[3:0] bin;//输入b(乘数),其数据位宽为4bit.output[7:0] yout;//乘积输出,其数据位宽为8bit.output done;//芯片输出标志信号。

定义为1表示乘法运算完成.reg[3:0] areg;//乘数a寄存器reg[3:0] breg;//乘数b寄存器reg[7:0] yout_r;//乘积寄存器reg done_r;reg[4:0] i;//移位次数寄存器reg[4:0]yout_r1;//------------------------------------------------//数据位控制always@(posedge Clk or negedge Rst_n)if(!Rst_n) i <=5'd0;else if(start && i <5'd5) i <= i+1'b1;else if(!start) i <=5'd0;//------------------------------------------------//乘法运算完成标志信号产生always@(posedge Clk or negedge Rst_n)if(!Rst_n) done_r <=1'b0;else if(i ==5'd4) done_r <=1'b1;//乘法运算完成标志else if(i ==5'd5) done_r <=1'b0;//标志位撤销assign done = done_r;//------------------------------------------------//专用寄存器进行移位累加运算always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begin//复位,被乘数,乘数,结果为0areg <=4'd0;breg <=4'd0;yout_r <=8'd0;endelse if(start)begin//启动运算if(i ==5'd0)begin//锁存乘数、被乘数areg <= ain;breg <= bin;endelse if(i >5'd0&& i <5'd4)begin//进行三次移位if(areg[i-1])beginyout_r1=yout_r[6:3]+breg;yout_r ={1'b0,yout_r1,yout_r[2:1]};//累加并移位endelse yout_r <= yout_r>>1;//移位不累加endelse if(i ==5'd4&& areg[3]) yout_r[7:4]<=yout_r[7:4]+breg;//累加不移位endendassign yout = yout_r;endmodule(1)两个n位的数据相乘,结果最多为n+n位;两个4位的数据相乘,结果最多为8位;例如1111X1111=11100001(2)两个n位的数据相乘需要移位n-1次,两个4位的数据相乘需要移位3次,1011X 01111011101110110000--------------------------------------------------------------------- 1001101最后三行的计算是移位的;(3)两个n位数据相加,结果最多为n+1位;两个4位数据相加,结果最多为5位;例如:1111+1111= 11110;这里我认为最难理解的就是专用寄存器进行移位累加运算这一块;接下来就是我自己对这一块的分析。

FPGA课程设计实验报告

合肥工业大学大学实验报告课程名称: FPGA设计实验名称:移位乘法器设计 & 8位Booth乘法器设计*名:**学号: ********班级:电子科学与技术11-1班指导教师:**合肥工业大学电子科学与应用物理学院制移位乘法器一、实验原理移位和相加乘法原理,乘法通过逐项移位相加原理来实现,从被乘数的最低位开始,若为1,则乘数右移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位。

移位乘法器工作流程图二、实验步骤算法主程序module MUL(A,B,data);input [7:0] A;input [7:0] B;output [15:0] data;wire [15:0] data;reg [7:0] D;reg [7:0] A1;reg [7:0] B1;reg C;always @(A or B)beginA1 = A;B1 = B;D = 0;C = 0;repeat(8)beginif(A1[0]==1){C,D} = D + B1;else{C,D} = D + 0;{C,D,A1} = {C,D,A1} >> 1;endendassign data = {D,A1};endmodule移位乘法器测试文件module test;reg [7:0] A;reg [7:0] B;// Outputswire [15:0] data;// Instantiate the Unit Under Test (UUT) MUL uut (.A(A),.B(B),.data(data));initial begin// Initialize InputsA = 0;B = 0;// Wait 100 ns for global reset to finish#20;A = 8'b0000_0010;B = 8'b0000_1101;// Add stimulus hereendendmodule三、实验结果及分析2进制输入输出结果10进制输入输出结果四、体会通过移位乘法器的设计,简单的了解了ISE软件的基本功能,主要菜单选项,以及如何建立一个工程,如何在工程里面写程序和进行编译和综合等。

基于FPGA的流水线乘法器设计

4位乘法器设计开题报告

中国海洋大学青岛学院毕业设计开题报告题目 4位乘法器的设计系(中心)信息工程系年级 2008级专业电子信息工程姓名高吉学号 200802305331指导教师王学玲一、选题依据课题来源、选题依据和背景情况;课题研究目的、学术价值或实际应用价值现代社会在飞速发展,科学技术的发展越来越快。

4位二进制乘法器在十几种的应用相当广泛,是一些计算器的基本组成部分,其远离适用于很多计算器和大型计算机,他涉及到实训逻辑电路如何设计。

分析和工作等方面。

通过次电路更深刻的了解时许逻辑不见的工作原理,从而掌握如何根据需要设计满足要求的各种电路图,解决生活中的实际问题,将知识应用于实践中。

根据课题研究的目地是,绘制出电路的原理图,并且诠释每部分的功能;根据设计的电路图分析所需要的元器件种类和个数;根据技术指标指定实验反感,验证所设计的电路;进行实验数据处理和分析。

研究此课题,目地在于使我们了解4位乘法器在实际中的应用,了解它的具体工作原理以及它的基本电路图,使我们以后可以应用它解决一些实际问题。

通过对4位乘法器的设计,让我们懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。

二、文献综述国内外研究现状、发展动态;查阅的主要文献研究现状乘法器由于它的应用十分广泛,是一些计算器的基本组成部分,被广泛应用于大型计算机中,所以各国科学家对其都进行了积极的研究,现在超级计算机的出现,使的最基本的乘法器又有了更大的发展。

发展前景广阔。

查阅主要文献:1.《VHDL应用与开发实践》著译者: 甘历出版者:科学出版社2.《VHDL与数字电路设计》卢毅赖杰科学出版社 2001年4月3.《VHDL编程与仿真》王毅平张振荣人民邮电出版社 2000年7月4.《数字电路设计与Verllog HDL》张亮人民邮电出版社 2000年10月5.《VHDL简明教程》王小军清华大学出版社6. 《用 VHDL 设计电子线路》边计年等翻译 清华大学出版社7. 《可编程逻辑器件原理、开发与应用》赵曙光 西安电子科技大学出版社 8. 《数字电路设计与Verllog HDL 》张亮 人民邮电出版社 2000年10月 9. 《FPGA 设计及应用》褚振勇 翁木云 西安电子科技大学出版社2002年7月 10. 江国强编著。

高性能专用FPGA算术部件的研究与设计的开题报告

高性能专用FPGA算术部件的研究与设计的开题报告一、选题背景和意义随着计算机科学技术的发展,对于运算速度和效率要求不断提高,高性能的算术部件在处理器、存储器、通信等领域都扮演着非常重要的角色。

然而,传统硬件实现算术部件存在着面积大、功耗高等问题。

因此,现在出现了一种新型的可编程硬件—— FPGA,可以在硬件上实现高度定制化的算术部件,其在可扩展性、可靠性、高性能等方面优于传统硬件。

因此,研究高性能专用FPGA算术部件的设计有着重要的意义。

二、研究目的和内容本文旨在研究和设计高性能专用FPGA算术部件,为实现高性能的计算机、存储器和通信等领域提供支持。

具体目的和内容如下:1. 研究FPGA的基本原理及其应用。

对于FPGA结构、配置和编程等基础知识进行了解,并了解FPGA在算术部件设计中的应用。

2. 分析学术界和工业界对于算术部件设计的研究成果。

了解了已有的研究成果,包括加减乘除、开方、求余、位移、比较等算术运算的FPGA实现方法及其优化技术,为本文的研究提供理论基础。

3. 设计高性能专用FPGA算术部件。

采用现代设计方法和技术,通过重复使用模块和优化算法,设计高效、可靠的算术部件。

4. 实现和测试算术部件。

使用FPGA相关工具进行算术部件的实现,并进行仿真和测试,验证设计的正确性和可靠性。

三、预期成果和研究意义本文预期的成果是设计出高性能的FPGA算术部件,能够实现高效的运算、低功耗和良好的可靠性。

完成本次研究可以为高性能计算、存储器、通信等领域的应用提供支持,帮助提高运算速度和效率,推动科学技术的发展。

同时,也可为FPGA算术部件的研究提供新的思路和方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课题的开发主要应用FPGA技术

ISE、ModelSim、ChipScope Pro软件

XUP Virtex-II Pro开发系统一套

毕业设计开题报告

2.本课题的基本内容,预计可能遇到的困难,提出解决问题的方法和措施

基本内容:

本文介绍基于FPGA的乘法器的设计。说明了乘法器设计原理方法。从原理上来说它属于组合逻辑电路范畴,但是从工程实际设计上来说,它往往是利用时序逻辑设计的方法来实现,属于时序逻辑设计范畴。所以它的设计方法也有两种:组合逻辑设计方法和时序逻辑设计方法。本次实验中我们就利用时序逻辑设计方法来设计一个16位乘法器。本文中的被乘数和乘数都是无符号的整数,对于有符号数的乘法,可以将符号与数据绝对值分开处理,即绝对值相乘,符号异或。并对乘法器进行软件实现和时序仿真。

4.4用ModelSim进行时序仿真

4.5记录仿真波形并分析

预计可能遇到的困难:

做加法运算期间,输出端口信号不稳定,主要是组合逻辑电路缺乏时钟信号,电路不能采集到有效的时间作为触发条件。

解决方法:

采用时序设计方法实现的乘法器,在引入流水线结构后,能够克服上述缺点,并减少了资源的开销。

3.本课题拟采用的研究手段(途径)和可行性分析

毕业设计开题报告

指导教师意见:

(对本课题的深度、广度及工作量的意见和对设计结果的预测)

指导教师:

年月日

教研室审查意见:

教研室负责人:

年月日

通常的乘法计算方法是添加和位移的算法。在并行乘法器当中,相加的部分乘积的数量是主要的参数。它决定了乘法器的性能。设计基于FPGA的乘法器的结构将大大大改善整个处理器系统的速度、面积和功耗等性能指标。

在通信与信号处理系统中,乘法器是数字运算的重要单元,高性能乘法器是完成稿性能实时数据和处理的关键,随着FPGA技术的发展,FPGA以其高度的灵活性和正在越来越多的替代ASIC和DSP用于信号处理的运算,然而常见的FPGA芯片一般不具有现成的乘法运算单元,因而研究基于FPGA的乘法器的设计具有非常重要的意义。

内容提纲:

前言部分:概述FPGA器件的应用状况和发展趋势

第一章:FPGA简介

1.1 FPGA的结构、优点

1.2基于FPGA的数字系统设计流程

1.3基于FPGA的数字调试系统、调试方法

1.4实验平台开发选择、介绍

第二章:乘法器

2.1乘法器应用场合

2.2乘法器算法原理

2.3乘法器结构

2.4乘法器的各种设计方法分析

本课题采用基于FPGA的乘法器的设计,以16*16无符号数时序乘法器为例进行研究。统上数字信号处理的构建在较低速率要求下都是通过专用的DSP来实现的,如果速率高的话,就要使用专用的DSP或者ASIC才能完成。随着FPGA的迅速发展,数字信号处理系统的构建又多了一种选择方案。FPGA是一款半定制集成电路芯片,只需对它编程就能实现设计的功能,而且它还保留了ASIC的封装小、密度高、规模大、高可靠性的特点,还具有较高的设计灵活性和适应性等优点。乘法最基本的操作是移位相加,各类算法最终都是通过这种方式来实现的,本课题基于FPGA的实现给出了仿真、综合和验证。

第三章:基于FPGA的乘法器设计Байду номын сангаас案

3.1时序乘法器算法原理

3.2乘法器设计结构

3.3乘法器设计流程

3.4编写16*16位无符号数时序乘法器的Verilog HDL代码

第四章:FPGA时序乘法器设计实现及仿真

4.1编写乘法器测试代码

4.2用ModelSim进行功能仿真

4.3对时序乘法器进行工程综合、实现,并生成仿真文件

FPGA具有可重复编程、随时修改等独特优点,就与FPGA的乘法器只需在FPGA开发系统上进行编程、修改,对小批量生产企鹅品种多的ASIC电路尤为方便,在产品竞争中可捷足先登,抢先占领市场,这在目前市场竞争越来越激烈,新产品说我不断涌现的市场经济下是极为有利的,也是FPGA得到迅速发展的重要因素。

发展趋势:

国内外研究现状:

乘法器在当今数字信号处理以及其他诸多应用领域中起着十分重要的作用。乘法器作为高性能微处理器,特别是数字信号处理器的关键组成部件,一直是研究的热点。乘法运算一般可以分成三个阶段,第一阶段是部分积阵列的产生,第二阶段是部分积的压缩处理,最后阶段是利用快速进位传递加法器得出乘法运算结果。

当今,半导体市场格局已成三足鼎立之势,FPGA,ASIC和ASSP三分天下。市场统计数据表明,FPGA已经逐步侵蚀ASIC和ASSP的传统市场,并处于快速增长阶段。

随着科学技术的发展,许多研究人员已经开始试图设计一类拥有更高速率和低功耗,布局规律占用面积小,集成度高的乘法器。这样,就能让它们更加适用于高速率,低功耗的大规模集成电路的应用当中。FPGA不断向高集成度、大容量、高速、低功耗、低价位的方向发展,目前最高水平的FPGA已采用65nm、11层铜布线,规模已达到330 000个逻辑单元(可编程逻辑门约660万门)和1 200个用户I/O,速度已达到550MHz。FPGA发展另一个值得注意的方向是IP的利用和可编程系统集成。

毕业设计开题报告

学生姓名:XXX学号:

专业:电子信息科学与技术

设计题目:基于FPGA的乘法器的设计

班级:

指导教师:XXX

2010年3月26日

毕业设计开题报告

1.本课题的研究意义,国内外研究现状、水平和发展趋势

研究意义

随着科技,信息化的快速发展。乘法器,它已经是现代计算机中必不可少的一部分。基于fpga的数字乘法器具有一般模拟乘法器所不能比拟的精确、可靠性高、速度快等优点,在通信系统中的应用非常广泛,尤其是在调制解调过程中,因此设计一种符合要求的高性能数字乘法器就显得尤为重要。乘法器是硬核处理器、DSP、滤波器、高性能微控制器等器件中重要的运算部件之一。它能够提供强大的数学运算以进行实时性信号处理。同时,高性能乘法除了直接用于运算单元外还在图像、语音、加密等信号处理领域扮演着非常重要的角色。