基于VerilogHDL的表决器的设计

Verilog HDL实验报告

HDL实验报告专业电子科学与技术姓名学号指导老师1 实验一Modelsim仿真软件的使用1.1 实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行HDL 程序设计开发。

1.2 实验步骤(1)学习使用Modelsim软件;(2)分析原理及功能;(3)用Verilog HDL编写程序;(4)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

1.3 实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果。

1.4.1 程序module my_xor(ina,inb,out);input ina,inb;output out;assign out=ina^inb;endmodulemodule t_xor;reg ina,inb;wire out;initialbeginina=1'b0;forever #20 ina=~ina;endinitialbegininb=1'b0;forever #10 inb=~inb;endmy_xor tt(.ina(ina),.inb(inb),.out(out));endmodule2 实验二简单组合电路设计2.1 实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法2.2 实验步骤(1)分析原理及功能;(2)根据原理用Verilog HDL编写程序;(3)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

2.3 实验内容设计一个三人表决器(高电平表示通过) ,实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

三人表决器五人表决器的实验报告

三人表决器、五人表决器的实验报告

一 实验目的

1、熟悉Quartus II 软件的基本操作

2、学习使用Verilog HDL 进行设计输入

3、逐步掌握软件输入、编译、仿真的过程 二 实验说明

三人表决器真值表:

输入信号

输出信号

B1 B2 B3 u 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1

1

1

1

逻辑表达式:U=

b1

b2 voter u

b3

本次实验就是要设计一个三人表决器。

该电路应有两个数据输入端口b1,b2,b3,电路的输出端口为voter(u 输出信号)。

三实验要求

1、完成三人表决器的Verilog HDL程序代码输入并进行仿真

2、采用结构描述方式与数据流描述方式

3、完成对设计电路的仿真验证

四、实验过程

(1)三人表决器:

程序代码

仿真结果

五人表决器:

程序代码

仿真结果

五、实验体会

通过三人表决器与五人表决器的设计,使我们更加熟悉Quartus 软件进行数字系统设计的步骤,以及运用Verilog HDL进行设计输入,并掌握三人表决器与五人表决器的逻辑功能与设计原理,逐步理解功能仿真与时序仿真波形。

三人表决器与五人表决器大体相似,并没有太大的区别。

用Verilog+HDL进行FPGA设计的一些基本方法

Dout<=Dout+1;

end

endmodule

f2—2)一个简单的8位计数器电路描述

用Verilog HDL描述时序逻辑电路时需要注意以下两点:

1)在用always语句描述时序逻辑电路时,只可能出现如下

三种形式:

a)always@(posedge Clk):不包含任何异步复位信号.但可

能包含同步复位信号。

3)注意仿真与综合的一致性。在FPGA设计中,对Verilog HDL程序进行的仿真称为功能仿真.功能仿真正确后的程序才 可以拿来进行综合。在整个设计过程中,必须保证综合前后电路 功能不变。要做到这一点,前提条件就是我们在书写Verilog HDD程序时必须遵循一定的规则。

2基本逻辑电路设计

2.1组合逻辑电路设计。 组合逻辑电路是数字系统中的一种最基本的电路类型。这 种电路的特点就是任意时刻的输出仅仅处决与该时刻的输入, 与电路原来的状态无关。在Verilog HDL中,可以使用三种方法 来生成组合逻辑电路:使用连续赋值语句,使用不带时钟触发的

if fDataln==qDl Y3=0; else Y3=1:

ห้องสมุดไป่ตู้

endmodule

(2-一1)一个简单的组合逻辑描述 用Verilog HDL描述组合逻辑电路时需要注意如下几点: 1)连续赋值语句和函数描述的电路只能是组合逻辑电路。

2)在使用用always语句时,所有被读取的变量都必须出现 在always语句的敏感信号列表中.否则会导致仿真与综合的不 一致。

≮穆国自控弼邮局订阅号:82.946 120元/年一93—

圈豳圈圜图豳堕圃豳豳蛋

《微计算机信息>(测控自动化)2004年第20卷第6期

FPGA与CPLD相比。最大的一个特点就是它的寄存器相当 丰富,因此.更加适合设计时序逻辑电路。实际上,由于FPGA内 部延迟的不确定.用FPGA描述的电路大多是时序逻辑电路。

verilog的15个经典设计实例

begin b=a; c=b; end endmodule

【例 5.11】模为 60 的 BCD 码加法计数器

module count60(qout,cout,data,load,cin,reset,clk);

【例 5.6】用 fork-join 并行块产生信号波形

`timescale 10ns/1ns module wave2; reg wave; parameter cycle=5; initial

fork wave=0;

#(cycle) wave=1; #(2*cycle) wave=0; #(3*cycle) wave=1; #(4*cycle) wave=0; #(5*cycle) wave=1; #(6*cycle) $finish; join initial $monitor($time,,,"wave=%b",wave); endmodule

else

out<=out+1;

end

endmodule

//同步复位 //计数

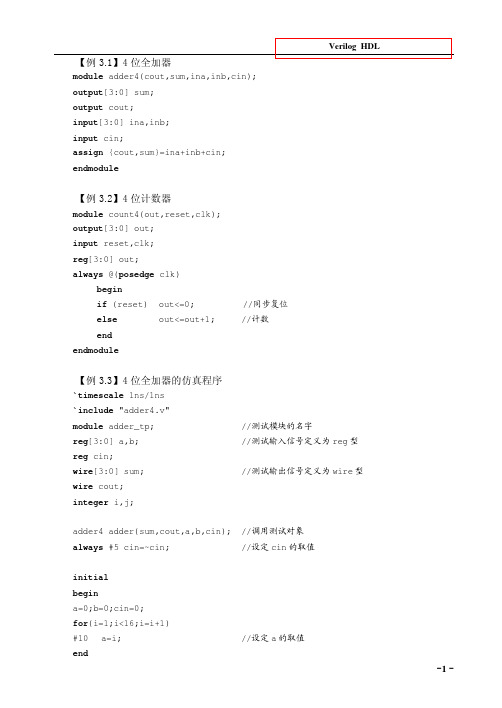

【例 3.3】4 位全加器的仿真程序

`timescale 1ns/1ns `include "adder4.v" module adder_tp; reg[3:0] a,b; reg cin; wire[3:0] sum; wire cout; integer i,j;

output[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

FPGA的Verilog HDL拔河比赛设计

示意图

拔河LED 拔河 显示模块来自按键 模块主控制 电路模块

计分数码管 显示模块

分频

module Divided_Frequency(_10000HzOut,_25HzOut,_50MHzIn); input _50MHzIn; output _10000HzOut,_1HzOut; parameter width1=16,value1=2499; parameter width2=10,value2=499; reg _10000HzOut,_25HzOut; reg [width1-1:0] Count; [width1reg [width2-1:0] Cnt; [width2always @(posedge _50MHzIn) //2500*2*10000Hz=50MHz if (Count==value1) //Binary Counter(0~2499) begin Count <= 15'd0; _10000HzOut <= ~_10000HzOut; end else Count <= Count + 1'b1; always @(posedge _50MHzIn) //100 000*2*25Hz=50MHz if (Cnt==value2) //Binary Counter(0~99999) begin Cnt <= 15'd0; _25HzOut <= ~_25HzOut; end else Cnt <= Cnt + 1'b1; endmodule

//0 //1 //2 //3 //4 //5 //6 //7 ////-

程序示意电路图

演示结束!

always@(seg_in) case(seg_in) //g f e d c b a// 4'd0:segout<=7'b1000000; 4'd1:segout<=7'b1111001; 4'd2:segout<=7'b0100100; 4'd3:segout<=7'b0110000; 4'd4:segout<=7'b0011001; 4'd5:segout<=7'b0010010; 4'd6:segout<=7'b0000010; 4'd7:segout<=7'b1111000; 4'd8:segout<=7'b0111111; default:segout<=7'b1000000; endcase endmodule

10分钟学会PLD设计

10分钟学会PLD设计睿浩电子今天我们将带领大家完成你的第一个PLD设计,即使你从没有接触过PLD,也可以让你可以在十分种之内初步学会PLD设计!不信?呵呵我们慢慢往下看。

实验目的我们分别采用VHDL、Verilog-HDL和原理图输入方式设计一个简单的三人表决器,,并下载到PLD实验板进行实际运行。

三人表决器的功能描述:三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮功能虽然简单,但是大家可以从这个实验中学习到PLD的设计输入,仿真,下载等一个完整过程。

软件准备本次实验采用Max+plusII 10.2 软件,首先我们需要下载免费软件并安装license。

对于WindowsNT/2000/XP,还需要安装下载电缆的驱动程序。

>> 软件安装和license的获取请点击此处>> 安装下载电缆的驱动程序请点击此处硬件准备PC机一台,JX002B型实验板,电源,下载电缆软硬件均准备好以后,就可以开始我们的设计了。

在三种输入方式中,你也可以先只看一种,比如原理图方式或者VHDL方式,然后可以直接看2-4章的内容下面您可以继续学习以下内容:10分钟学会PLD设计1 -设计输入 1.1 采用原理图输入10分钟学会PLD设计1 -设计输入 1.2 采用VHDL语言输入10分钟学会PLD设计1 -设计输入 1.3 采用Verilog语言输入10分钟学会PLD设计2 -设计的编译10分钟学会PLD设计3 -设计的仿真10分钟学会PLD设计4 -下载1 设计输入1.1 采用原理图设计三人表决器我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:L2=SW1SW2+SW1SW3+SW2SW3L1=_L2那么我们可以在MAX+plusII中用原理图实现上面的三人表决器下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:(1)打开MAX+plusII(2)新建一个图形文件:File菜单>new新建文件时选择Graphic Editor file点OK(3)输入设计文件我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以Symbol ->Enter Symbol(或者双击空白处)弹出窗口:在Symbol Name中输入and2,点OK同样可以加入or3、input、output、not对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

Verilog HDL 程序设计教程

《Verilog HDL 程序设计教程》代码例子- 1 -【例3.1】4 位全加器module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule【例3.2】4 位计数器module count4(out,reset,clk);output[3:0] out;input reset,clk;reg[3:0] out;always @(posedge clk)beginif (reset) out<=0; //同步复位else out<=out+1; //计数endendmodule【例3.3】4 位全加器的仿真程序`timescale 1ns/1ns`include "adder4.v"module adder_tp; //测试模块的名字reg[3:0] a,b; //测试输入信号定义为reg 型reg cin;wire[3:0] sum; //测试输出信号定义为wire 型wire cout;integer i,j;adder4 adder(sum,cout,a,b,cin); //调用测试对象always #5 cin=~cin; //设定cin 的取值initialbegina=0;b=0;cin=0;for(i=1;i<16;i=i+1)#10 a=i; //设定a 的取值end程序文本- 2 -initialbeginfor(j=1;j<16;j=j+1)#10 b=j; //设定b 的取值initial //定义结果显示格式begin$monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish;endendmodule【例3.4】4 位计数器的仿真程序`timescale 1ns/1ns`include "count4.v"module coun4_tp;reg clk,reset; //测试输入信号定义为reg 型wire[3:0] out; //测试输出信号定义为wire 型parameter DELY=100;count4 mycount(out,reset,clk); //调用测试对象always #(DELY/2) clk = ~clk; //产生时钟波形initialbegin //激励信号定义clk =0; reset=0;#DELY reset=1;#DELY reset=0;#(DELY*20) $finish;//定义结果显示格式initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out);endmodule【例3.5】“与-或-非”门电路module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,Doutput F; //模块的输出端口为F王金明:《Verilog HDL 程序设计教程》- 3 -wire A,B,C,D,F; //定义信号的数据类型assign F= ~((A&B)|(C&D)); //逻辑功能描述endmodule【例5.1】用case 语句描述的4 选1 数据选择器module mux4_1(out,in0,in1,in2,in3,sel);output out;input in0,in1,in2,in3;input[1:0] sel;reg out;always @(in0 or in1 or in2 or in3 or sel) //敏感信号列表case(sel)2'b00: out=in0;2'b01: out=in1;2'b10: out=in2;2'b11: out=in3;default: out=2'bx;endcaseendmodule【例5.2】同步置数、同步清零的计数器module count(out,data,load,reset,clk);output[7:0] out;input[7:0] data;input load,clk,reset;reg[7:0] out;always @(posedge clk) //clk 上升沿触发beginif (!reset) out = 8'h00; //同步清0,低电平有效else if (load) out = data; //同步预置else out = out + 1; //计数endendmodule【例5.3】用always 过程语句描述的简单算术逻辑单元`define add 3'd0`define minus 3'd1`define band 3'd2`define bor 3'd3`define bnot 3'd4程序文本- 4 -module alu(out,opcode,a,b);output[7:0] out;reg[7:0] out;input[2:0] opcode; //操作码input[7:0] a,b; //操作数always@(opcode or a or b) //电平敏感的always 块begincase(opcode)`add: out = a+b; //加操作`minus: out = a-b; //减操作`band: out = a&b; //求与`bor: out = a|b; //求或`bnot: out=~a; //求反default: out=8'hx; //未收到指令时,输出任意态endcaseendendmodule【例5.4】用initial 过程语句对测试变量A、B、C 赋值`timescale 1ns/1nsmodule test;reg A,B,C;initialbeginA = 0;B = 1;C = 0;#50 A = 1; B = 0;#50 A = 0; C = 1;#50 B = 1;#50 B = 0; C = 0;#50 $finish ;endendmodule【例5.5】用begin-end 串行块产生信号波形`timescale 10ns/1nsmodule wave1;reg wave;parameter cycle=10;initialbegin王金明:《Verilog HDL 程序设计教程》- 5 -wave=0;#(cycle/2) wave=1;#(cycle/2) wave=0;#(cycle/2) wave=1;#(cycle/2) wave=0;#(cycle/2) wave=1;#(cycle/2) $finish ;endinitial $monitor($time,,,"wave=%b",wave); endmodule【例5.6】用fork-join 并行块产生信号波形`timescale 10ns/1nsmodule wave2;reg wave;parameter cycle=5;initialforkwave=0;#(cycle) wave=1;#(2*cycle) wave=0;#(3*cycle) wave=1;#(4*cycle) wave=0;#(5*cycle) wave=1;#(6*cycle) $finish;joininitial $monitor($time,,,"wave=%b",wave); endmodule【例5.7】持续赋值方式定义的2 选1 多路选择器module MUX21_1(out,a,b,sel);input a,b,sel;output out;assign out=(sel==0)?a:b;//持续赋值,如果sel 为0,则out=a ;否则out=b endmodule【例5.8】阻塞赋值方式定义的2 选1 多路选择器module MUX21_2(out,a,b,sel);input a,b,sel;程序文本- 6 -output out;reg out;always@(a or b or sel)beginif(sel==0) out=a; //阻塞赋值else out=b;endendmodule【例5.9】非阻塞赋值module non_block(c,b,a,clk); output c,b;input clk,a;reg c,b;always @(posedge clk) beginb<=a;c<=b;endendmodule【例5.10】阻塞赋值module block(c,b,a,clk); output c,b;input clk,a;reg c,b;always @(posedge clk)beginb=a;c=b;endendmodule【例5.11】模为60 的BCD 码加法计数器module count60(qout,cout,data,load,cin,reset,clk); output[7:0] qout;output cout;input[7:0] data;input load,cin,clk,reset;reg[7:0] qout;always @(posedge clk) //clk 上升沿时刻计数王金明:《Verilog HDL 程序设计教程》- 7 -beginif (reset) qout<=0; //同步复位else if(load) qout<=data; //同步置数else if(cin)beginif(qout[3:0]==9) //低位是否为9,是则beginqout[3:0]<=0; //回0,并判断高位是否为5if (qout[7:4]==5) qout[7:4]<=0;elseqout[7:4]<=qout[7:4]+1; //高位不为5,则加1endelse //低位不为9,则加1qout[3:0]<=qout[3:0]+1;endendassign cout=((qout==8'h59)&cin)?1:0; //产生进位输出信号endmodule【例5.12】BCD 码—七段数码管显示译码器module decode4_7(decodeout,indec);output[6:0] decodeout;input[3:0] indec;reg[6:0] decodeout;always @(indec)begincase(indec) //用case 语句进行译码4'd0:decodeout=7'b1111110;4'd1:decodeout=7'b0110000;4'd2:decodeout=7'b1101101;4'd3:decodeout=7'b1111001;4'd4:decodeout=7'b0110011;4'd5:decodeout=7'b1011011;4'd6:decodeout=7'b1011111;4'd7:decodeout=7'b1110000;4'd8:decodeout=7'b1111111;4'd9:decodeout=7'b1111011; default: decodeout=7'bx;endcaseend程序文本- 8 -endmodule【例5.13】用casez 描述的数据选择器module mux_casez(out,a,b,c,d,select); output out;input a,b,c,d;input[3:0] select;reg out;always @(select or a or b or c or d) begincasez(select)4'b???1: out = a;4'b??1?: out = b;4'b?1??: out = c;4'b1???: out = d;endcaseendendmodule【例5.14】隐含锁存器举例module buried_ff(c,b,a);output c;input b,a;reg c;always @(a or b)beginif((b==1)&&(a==1)) c=a&b;endendmodule【例5.15】用for 语句描述的七人投票表决器module voter7(pass,vote);output pass;input[6:0] vote;reg[2:0] sum;integer i;reg pass;always @(vote)beginsum=0;王金明:《Verilog HDL 程序设计教程》- 9 -for(i=0;i<=6;i=i+1) //for 语句if(vote[i]) sum=sum+1;if(sum[2]) pass=1; //若超过4 人赞成,则pass=1 else pass=0;endendmodule【例5.16】用for 语句实现2 个8 位数相乘module mult_for(outcome,a,b);parameter size=8;input[size:1] a,b; //两个操作数output[2*size:1] outcome; //结果reg[2*size:1] outcome;integer i;always @(a or b)beginoutcome=0;for(i=1; i<=size; i=i+1) //for 语句if(b[i]) outcome=outcome +(a << (i-1));endendmodule【例5.17】用repeat 实现8 位二进制数的乘法module mult_repeat(outcome,a,b);parameter size=8;input[size:1] a,b;output[2*size:1] outcome;reg[2*size:1] temp_a,outcome;reg[size:1] temp_b;always @(a or b)beginoutcome=0;temp_a=a;temp_b=b;repeat(size) //repeat 语句,size 为循环次数beginif(temp_b[1]) //如果temp_b 的最低位为1,就执行下面的加法outcome=outcome+temp_a;temp_a=temp_a<<1; //操作数a 左移一位程序文本- 10 -temp_b=temp_b>>1; //操作数b 右移一位endendendmodule【例5.18】同一循环的不同实现方式module loop1; //方式1integer i;initialfor(i=0;i<4;i=i+1) //for 语句begin$display(“i=%h”,i);endendmodulemodule loop2; //方式2integer i;initial begini=0;while(i<4) //while 语句begin$display ("i=%h",i);i=i+1;endendendmodulemodule loop3; //方式3integer i;initial begini=0;repeat(4) //repeat 语句begin$display ("i=%h",i);i=i+1;endendendmodule【例5.19】使用了`include 语句的16 位加法器王金明:《Verilog HDL 程序设计教程》- 11 -`include "adder.v"module adder16(cout,sum,a,b,cin);output cout;parameter my_size=16;output[my_size-1:0] sum;input[my_size-1:0] a,b;input cin;adder my_adder(cout,sum,a,b,cin); //调用adder 模块endmodule//下面是adder 模块代码module adder(cout,sum,a,b,cin);parameter size=16;output cout;output[size-1:0] sum;input cin;input[size-1:0] a,b;assign {cout,sum}=a+b+cin;endmodule【例5.20】条件编译举例module compile(out,A,B);output out;input A,B;`ifdef add //宏名为addassign out=A+B;`elseassign out=A-B;`endifendmodule【例6.1】加法计数器中的进程module count(data,clk,reset,load,cout,qout);output cout;output[3:0] qout;reg[3:0] qout;input[3:0] data;input clk,reset,load;程序文本- 12 -always @(posedge clk) //进程1,always 过程块beginif (!reset) qout= 4'h00; //同步清0,低电平有效else if (load) qout= data; //同步预置else qout=qout + 1; //加法计数endassign cout=(qout==4'hf)?1:0; //进程2,用持续赋值产生进位信号endmodule【例6.2】任务举例module alutask(code,a,b,c);input[1:0] code;input[3:0] a,b;output[4:0] c;reg[4:0] c;task my_and; //任务定义,注意无端口列表input[3:0] a,b; //a,b,out 名称的作用域范围为task 任务内部output[4:0] out;integer i;beginfor(i=3;i>=0;i=i-1)out[i]=a[i]&b[i]; //按位与endendtaskalways@(code or a or b)begincase(code)2'b00: my_and(a,b,c);/* 调用任务my_and,需注意端口列表的顺序应与任务定义中的一致,这里的a,b,c分别对应任务定义中的a,b,out */2'b01: c=a|b; //或2'b10: c=a-b; //相减2'b11: c=a+b; //相加endcaseendendmodule王金明:《Verilog HDL 程序设计教程》- 13 -【例6.3】测试程序`include "alutask.v"module alu_tp;reg[3:0] a,b;reg[1:0] code;wire[4:0] c;parameter DELY = 100;alutask ADD(code,a,b,c); //调用被测试模块initial begincode=4'd0; a= 4'b0000; b= 4'b1111;#DELY code=4'd0; a= 4'b0111; b= 4'b1101; #DELY code=4'd1; a= 4'b0001; b= 4'b0011; #DELY code=4'd2; a= 4'b1001; b= 4'b0011; #DELY code=4'd3; a= 4'b0011; b= 4'b0001; #DELY code=4'd3; a= 4'b0111; b= 4'b1001; #DELY $finish;endinitial $monitor($time,,,"code=%b a=%b b=%b c=%b", code,a,b,c);endmodule【例6.4】函数function[7:0] get0;input[7:0] x;reg[7:0] count;integer i;begincount=0;for (i=0;i<=7;i=i+1)if (x[i]=1'b0) count=count+1;get0=count;endendfunction【例6.5】用函数和case 语句描述的编码器(不含优先顺序)module code_83(din,dout);input[7:0] din;output[2:0] dout;程序文本- 14 -function[2:0] code; //函数定义input[7:0] din; //函数只有输入,输出为函数名本身casex (din)8'b1xxx_xxxx : code = 3'h7;8'b01xx_xxxx : code = 3'h6;8'b001x_xxxx : code = 3'h5;8'b0001_xxxx : code = 3'h4;8'b0000_1xxx : code = 3'h3;8'b0000_01xx : code = 3'h2;8'b0000_001x : code = 3'h1;8'b0000_000x : code = 3'h0;default: code = 3'hx;endcaseendfunctionassign dout = code(din) ; //函数调用endmodule【例6.6】阶乘运算函数module funct(clk,n,result,reset);output[31:0] result;input[3:0] n;input reset,clk;reg[31:0] result;always @(posedge clk) //在clk 的上升沿时执行运算beginif(!reset) result<=0; //复位else beginresult <= 2 * factorial(n); //调用factorial 函数endendfunction[31:0] factorial; //阶乘运算函数定义(注意无端口列表)input[3:0] opa; //函数只能定义输入端,输出端口为函数名本身reg[3:0] i;beginfactorial = opa ? 1 : 0;for(i= 2; i <= opa; i = i+1) //该句若要综合通过,opa 应赋具体的数值factorial = i* factorial; //阶乘运算end王金明:《Verilog HDL 程序设计教程》- 15 -endfunctionendmodule【例6.7】测试程序`define clk_cycle 50`include "funct.v"module funct_tp;reg[3:0] n;reg reset,clk;wire[31:0] result;initial //定义激励向量beginn=0; reset=1; clk=0;for(n=0;n<=15;n=n+1)#100 n=n;endinitial $monitor($time,,,"n=%d result=%d",n,result);//定义输出显示格式always # `clk_cycle clk=~clk; //产生时钟信号funct funct_try(.clk(clk),.n(n),.result(result),.reset(reset)); //调用被测试模块endmodule【例6.8】顺序执行模块1module serial1(q,a,clk);output q,a;input clk;reg q,a;always @(posedge clk)beginq=~q;a=~q;endendmodule【例6.9】顺序执行模块2 module serial2(q,a,clk); output q,a;程序文本- 16 -input clk;reg q,a;always @(posedge clk) begina=~q;q=~q;endendmodule【例6.10】并行执行模块1 module paral1(q,a,clk); output q,a;input clk;reg q,a;always @(posedge clk) beginq=~q;endalways @(posedge clk) begina=~q;endendmodule【例6.11】并行执行模块2 module paral2(q,a,clk); output q,a;input clk;reg q,a;always @(posedge clk) begina=~q;endalways @(posedge clk) beginq=~q;endendmodule【例7.1】调用门元件实现的4 选1 MUX王金明:《Verilog HDL 程序设计教程》- 17 -module mux4_1a(out,in1,in2,in3,in4,cntrl1,cntrl2); output out;input in1,in2,in3,in4,cntrl1,cntrl2;wire notcntrl1,notcntrl2,w,x,y,z;not (notcntrl1,cntrl2),(notcntrl2,cntrl2);and (w,in1,notcntrl1,notcntrl2),(x,in2,notcntrl1,cntrl2),(y,in3,cntrl1,notcntrl2),(z,in4,cntrl1,cntrl2);or (out,w,x,y,z);endmodule【例7.2】用case 语句描述的4 选1 MUX module mux4_1b(out,in1,in2,in3,in4,cntrl1,cntrl2); output out;input in1,in2,in3,in4,cntrl1,cntrl2;reg out;always@(in1 or in2 or in3 or in4 or cntrl1 or cntrl2) case({cntrl1,cntrl2})2'b00:out=in1;2'b01:out=in2;2'b10:out=in3;2'b11:out=in4;default:out=2'bx;endcaseendmodule【例7.3】行为描述方式实现的4 位计数器module count4(clk,clr,out);input clk,clr;output[3:0] out;reg[3:0] out;always @(posedge clk or posedge clr)beginif (clr) out<=0;else out<=out+1;endendmodule程序文本- 18 -【例7.4】数据流方式描述的4 选1 MUXmodule mux4_1c(out,in1,in2,in3,in4,cntrl1,cntrl2);output out;input in1,in2,in3,in4,cntrl1,cntrl2;assign out=(in1 & ~cntrl1 & ~cntrl2)|(in2 & ~cntrl1 & cntrl2)| (in3 & cntrl1 & ~cntrl2)|(in4 & cntrl1 & cntrl2); endmodule【例7.5】用条件运算符描述的4 选1 MUXmodule mux4_1d(out,in1,in2,in3,in4,cntrl1,cntrl2);output out;input in1,in2,in3,in4,cntrl1,cntrl2;assign out=cntrl1 ? (cntrl2 ? in4:in3):(cntrl2 ? in2:in1); endmodule【例7.6】门级结构描述的2 选1MUXmodule mux2_1a(out,a,b,sel);output out;input a,b,sel;not (sel_,sel);and (a1,a,sel_),(a2,b,sel);or (out,a1,a2);endmodule【例7.7】行为描述的2 选1MUX module mux2_1b(out,a,b,sel);output out;input a,b,sel;reg out;always @(a or b or sel)beginif(sel) out = b;else out = a;endendmodule【例7.8】数据流描述的2 选1MUX module MUX2_1c(out,a,b,sel);output out;王金明:《Verilog HDL 程序设计教程》- 19 -input a,b,sel;assign out = sel ? b : a;endmodule【例7.9】调用门元件实现的1 位半加器module half_add1(a,b,sum,cout);input a,b;output sum,cout;and (cout,a,b);xor (sum,a,b);endmodule【例7.10】数据流方式描述的1 位半加器module half_add2(a,b,sum,cout);input a,b;output sum,cout;assign sum=a^b;assign cout=a&b;endmodule【例7.11】采用行为描述的1 位半加器module half_add3(a,b,sum,cout);input a,b;output sum,cout;reg sum,cout;always @(a or b)begincase ({a,b}) //真值表描述2'b00: begin sum=0; cout=0; end2'b01: begin sum=1; cout=0; end2'b10: begin sum=1; cout=0; end2'b11: begin sum=0; cout=1; end endcaseendendmodule【例7.12】采用行为描述的1 位半加器module half_add4(a,b,sum,cout);input a,b;output sum,cout;程序文本- 20 -reg sum,cout;always @(a or b)beginsum= a^b;cout=a&b;endendmodule【例7.13】调用门元件实现的1 位全加器module full_add1(a,b,cin,sum,cout); input a,b,cin;output sum,cout;wire s1,m1,m2,m3;and (m1,a,b),(m2,b,cin),(m3,a,cin);xor (s1,a,b),(sum,s1,cin);or (cout,m1,m2,m3);endmodule【例7.14】数据流描述的1 位全加器module full_add2(a,b,cin,sum,cout); input a,b,cin;output sum,cout;assign sum = a ^ b ^ cin;assign cout = (a & b)|(b & cin)|(cin & a); endmodule【例7.15】1 位全加器module full_add3(a,b,cin,sum,cout); input a,b,cin;output sum,cout;assign {cout,sum}=a+b+cin; endmodule【例7.16】行为描述的1 位全加器module full_add4(a,b,cin,sum,cout);input a,b,cin;output sum,cout;王金明:《Verilog HDL 程序设计教程》- 21 -reg sum,cout; //在always 块中被赋值的变量应定义为reg 型reg m1,m2,m3;always @(a or b or cin)beginsum = (a ^ b) ^ cin;m1 = a & b;m2 = b & cin;m3 = a & cin;cout = (m1|m2)|m3;endendmodule【例7.17】混合描述的1 位全加器module full_add5(a,b,cin,sum,cout);input a,b,cin;output sum,cout;reg cout,m1,m2,m3; //在always 块中被赋值的变量应定义为reg 型wire s1;xor x1(s1,a,b); //调用门元件always @(a or b or cin) //always 块语句beginm1 = a & b;m2 = b & cin;m3 = a & cin;cout = (m1| m2) | m3;endassign sum = s1 ^ cin; //assign 持续赋值语句endmodule【例7.18】结构描述的4 位级连全加器`include "full_add1.v"module add4_1(sum,cout,a,b,cin);output[3:0] sum;output cout;input[3:0] a,b;input cin;full_add1 f0(a[0],b[0],cin,sum[0],cin1); //级连描述full_add1 f1(a[1],b[1],cin1,sum[1],cin2);full_add1 f2(a[2],b[2],cin2,sum[2],cin3);程序文本- 22 -full_add1 f3(a[3],b[3],cin3,sum[3],cout); endmodule【例7.19】数据流描述的4 位全加器module add4_2(cout,sum,a,b,cin); output[3:0] sum;output cout;input[3:0] a,b;input cin;assign {cout,sum}=a+b+cin; endmodule【例7.20】行为描述的4 位全加器module add4_3(cout,sum,a,b,cin); output[3:0] sum;output cout;input[3:0] a,b;input cin;reg[3:0] sum;reg cout;always @(a or b or cin)begin{cout,sum}=a+b+cin;endendmodule【例8.1】$time 与$realtime 的区别`timescale 10ns/1nsmodule time_dif;reg ts;parameter delay=2.6;initialbegin#delay ts=1;#delay ts=0;#delay ts=1;#delay ts=0;endinitial $monitor($time,,,"ts=%b",ts); //使用函数$time 王金明:《Verilog HDL 程序设计教程》- 23 -endmodule【例8.2】$random 函数的使用`timescale 10ns/1nsmodule random_tp;integer data;integer i;parameter delay=10;initial $monitor($time,,,"data=%b",data); initial beginfor(i=0; i<=100; i=i+1)#delay data=$random; //每次产生一个随机数endendmodule【例8.3】1 位全加器进位输出UDP 元件primitive carry_udp(cout,cin,a,b);input cin,a,b;output cout;table//cin a b : cout //真值表0 0 0 : 0;0 1 0 : 0;0 0 1 : 0;0 1 1 : 1;1 0 0 : 0;1 0 1 : 1;1 1 0 : 1;1 1 1 : 1;endtableendprimitive【例8.4】包含x 态输入的1 位全加器进位输出UDP 元件primitive carry_udpx1(cout,cin,a,b);input cin,a,b;output cout;table// cin a b : cout //真值表0 0 0 : 0;程序文本- 24 -0 1 0 : 0;0 0 1 : 0;0 1 1 : 1;1 0 0 : 0;1 0 1 : 1;1 1 0 : 1;1 1 1 : 1;0 0 x : 0; //只要有两个输入为0,则进位输出肯定为00 x 0 : 0;x 0 0 : 0;1 1 x : 1; //只要有两个输入为1,则进位输出肯定为11 x 1 : 1;x 1 1 : 1;endtableendprimitive【例8.5】用简缩符“?”表述的1 位全加器进位输出UDP 元件primitive carry_udpx2(cout,cin,a,b);input cin,a,b;output cout;table// cin a b : cout //真值表? 0 0 : 0; //只要有两个输入为0,则进位输出肯定为00 ? 0 : 0;0 0 ? : 0;? 1 1 : 1; //只要有两个输入为1,则进位输出肯定为11 ? 1 : 1;1 1 ? : 1;endtableendprimitive【例8.6】3 选1 多路选择器UDP 元件primitive mux31(Y,in0,in1,in2,s2,s1);input in0,in1,in2,s2,s1;output Y;table//in0 in1 in2 s2 s1 : Y0 ? ? 0 0 : 0; //当s2s1=00 时,Y=in01 ? ? 0 0 : 1;? 0 ? 0 1 : 0; //当s2s1=01 时,Y=in1王金明:《Verilog HDL 程序设计教程》- 25 -? 1 ? 0 1 : 1;? ? 0 1 ? : 0; //当s2s1=1?时,Y=in2? ? 1 1 ? : 1;0 0 ? 0 ? : 0;1 1 ? 0 ? : 1;0 ? 0 ? 0 : 0;1 ? 1 ? 0 : 1;? 0 0 ? 1 : 0;? 1 1 ? 1 : 1;endtableendprimitive【例8.7】电平敏感的1 位数据锁存器UDP 元件primitive latch(Q,clk,reset,D);input clk,reset,D;output Q;reg Q;initial Q = 1'b1; //初始化table// clk reset D : state : Q? 1 ? : ? : 0 ; //reset=1,则不管其他端口为什么值,输出都为0 0 0 0 : ? : 0 ; //clk=0,锁存器把D 端的输入值输出0 0 1 : ? : 1 ;1 0 ? : ? : - ; //clk=1,锁存器的输出保持原值,用符号“-”表示endtableendprimitive【例8.8】上升沿触发的D 触发器UDP 元件primitive DFF(Q,D,clk);output Q;input D,clk;reg Q;table//clk D : state : Q(01) 0 : ? : 0; //上升沿到来,输出Q=D(01) 1 : ? : 1;(0x) 1 : 1 : 1;(0x) 0 : 0 : 0;(?0) ? : ? : -; //没有上升沿到来,输出Q 保持原值? (??) : ? : - ; //时钟不变,输出也不变程序文本- 26 -endtableendprimitive【例8.9】带异步置1 和异步清零的上升沿触发的D 触发器UDP 元件primitive DFF_UDP(Q,D,clk,clr,set);output Q;input D,clk,clr,set;reg Q;table// clk D clr set : state : Q(01) 1 0 0 : ? : 0;(01) 1 0 x : ? : 0;? ? 0 x : 0 : 0;(01) 0 0 0 : ? : 1;(01) 0 x 0 : ? : 1;? ? x 0 : 1 : 1;(x1) 1 0 0 : 0 : 0;(x1) 0 0 0 : 1 : 1;(0x) 1 0 0 : 0 : 0;(0x) 0 0 0 : 1 : 1;? ? 1 ? : ? : 1; //异步复位? ? 0 1 : ? : 0; //异步置1n ? 0 0 : ? : -;? * ? ? : ? : -;? ? (?0) ? : ? : -;? ? ? (?0): ? : -;? ? ? ? : ? : x;endtableendprimitive【例8.12】延迟定义块举例module delay(out,a,b,c);output out;input a,b,c;and a1(n1,a,b);or o1(out,c,n1);specify(a=>out)=2;(b=>out)=3;(c=>out)=1;王金明:《Verilog HDL 程序设计教程》- 27 -endspecifyendmodule【例8.13】激励波形的描述'timescale 1ns/1nsmodule test1;reg A,B,C;initialbegin //激励波形描述A = 0;B = 1;C = 0;#100 C = 1;#100 A = 1; B = 0;#100 A = 0;#100 C = 0;#100 $finish;endinitial $monitor($time,,,"A=%d B=%d C=%d",A,B,C); //显示endmodule【例8.15】用always 过程块产生两个时钟信号module test2;reg clk1,clk2;parameter CYCLE = 100;alwaysbegin{clk1,clk2} = 2'b10;#(CYCLE/4) {clk1,clk2} = 2'b01;#(CYCLE/4) {clk1,clk2} = 2'b11;#(CYCLE/4) {clk1,clk2} = 2'b00;#(CYCLE/4) {clk1,clk2} = 2'b10;endinitial $monitor($time,,,"clk1=%b clk2=%b",clk1,clk2); endmodule【例8.17】存储器在仿真程序中的应用module ROM(addr,data,oe);output[7:0] data; //数据信号input[14:0] addr; //地址信号input oe; //读使能信号,低电平有效程序文本- 28 -reg[7:0] mem[0:255]; //存储器定义parameter DELAY = 100;assign #DELAY data=(oe==0) ? mem[addr] : 8'hzz; initial $readmemh("rom.hex",mem); //从文件中读入数据endmodule【例8.18】8 位乘法器的仿真程序`timescale 10ns/1nsmodule mult_tp; //测试模块的名字reg[7:0] a,b; //测试输入信号定义为reg 型wire [15:0] out; //测试输出信号定义为wire 型integer i,j;mult8 m1(out,a,b); //调用测试对象//激励波形设定initialbegina=0;b=0;for(i=1;i<255;i=i+1)#10 a=i;endinitialbeginfor(j=1;j<255;j=j+1)#10 b=j;endinitial //定义结果显示格式begin$monitor($time,,,"%d * %d= %d",a,b,out); #2560 $finish;endendmodulemodule mult8(out, a, b); //8 位乘法器源代码parameter size=8;input[size:1] a,b; //两个操作数output[2*size:1] out; //结果assign out=a*b; //乘法运算符王金明:《Verilog HDL 程序设计教程》- 29 -endmodule【例8.19】8 位加法器的仿真程序`timescale 1ns/1nsmodule add8_tp; //仿真模块无端口列表reg[7:0] A,B; //输入激励信号定义为reg 型reg cin;wire[7:0] SUM; //输出信号定义为wire 型wire cout;parameter DELY = 100;add8 AD1(SUM,cout,A,B,cin); //调用测试对象initial begin //激励波形设定A= 8'd0; B= 8'd0; cin=1'b0;#DELY A= 8'd100; B= 8'd200; cin=1'b1;#DELY A= 8'd200; B= 8'd88;。

Verilog-HDL电路设计

第五章 Verilog-HDL电路设计1.基础知识1.1 模块结构端口定义 module 模块名(输入输出端口列表);端口说明 input 输入端口;output 输出端口;信号说明 wire[n-1:0] x, y, z;reg[n-1] u, v, w;功能定义1.2数据类型reg型wire型1.3基本语句assign语句,过程赋值语句(=和<=)if …else 和case语句for和while语句always和initial块语句1.4建模方法结构建模(门级建模和模块实例化)行为建模(数据流建模和顺序行为建模)2.基本逻辑电路2.1 引例设计实现一个3人表决电路,若3个人中有2人或者超过2人同意,则表决通过;否则表决不通过。

解:①理解题意。

设a, b, c分别代表3个人,同意用1表示,不同意用0表示。

y代表表决结果,1表示通过,0表示不通过。

根据题意,当a,b,c三个中有2个为1,或者3个为1时,y=1;否则y=0。

②根据题意,列真值表:a b c y00000010010001111000101111011111③根据真值表,列输出方程:④化简方程⑤ 根据化简后的方程画出电路图2.1.1 对应①建模①当a, b ,c三个中有2个为1,或者3个为1时,y=1;否则y=0. module decision_1(a,b,c,y);input a,b,c;output y;reg y;always @(a, b, c)if ((a&b==1)|(b&c==1)|(c&a==1)|(a&b&c==1))y = 1;elsey = 0;endmodule2.1.2 对应②建模②真值表a b c y00000010010001111000101111011111module decision_2(a,b,c,y);input a,b,c;output y;reg y;always @(a, b, c)case ({a, b, c})3'b000:y = 0;3'b001:y = 0;3'b010:y = 0;3'b011:y = 1;3'b100:y = 0;3'b101:y = 1;3'b110:y = 1;3'b111:y = 1;endcaseendmodule2.1.3 对应③建模③根据真值表,列输出方程module decision_3(a,b,c,y);input a,b,c;output y;assign y = (~a&b&c)|(a&~b&c)|(a&b&~c)|(a&b&c);endmodule..4 对应④建模④化简方程module decision_4(a,b,c,y);input a,b,c;output y;assign y = (b&c)|(a&c)|(a&b);endmodule..5 对应⑤建模module decision_5(a,b,c,y);input a,b,c;output y;wire ab, bc, ca;and (ab, a, b),(bc, b, c),(ca ,c, a);or (y, ab, bc, ca);endmodule.1 基本组合逻辑电路数字逻辑电路就本质而言,分为组合逻辑和时序逻辑两大类。

VerilogHDL程序设计教程

Verilog HDL程序设计教程红色:做后有错。

粉红色:有疑问。

紫色:第二次仍有错。

绿色:文字错误第1章EDA技术综述 1.1引言1.摩尔定律1.2EDA的发展阶段1.阶段1.3设计方法与设计技术1.两种设计思路2.IP的含义3. IP核的分类。

4. SOC的含义1.4EDA的实现1.实现方法第2章EDA设计软件与设计流程 2.2EDA的设计流程1(FPGA的设计流程 2(综合的定义与类型。

3(仿真的类型第3章Verilog HDL设计初步(P18) 3.2完整的Verilog HDL设计1. 4位全加器的和4位计数器的程序。

2. 4位全加器的仿真程序(1.时间头文件 2.模块名(没有参数)3.参数规定(端口、延时、时钟)4.调用测试对象 5.设置参数(所有的输入端口都应初始化赋值)6.显示设置)。

3.3Verilog模块基本结构剖析 1.端口定义注意事项。

2.逻辑功能定义的几种方式第4章Verilog HDL语言要素(P32)4.1词法1.verilog中的四种基本逻辑状态4.2数据类型1.连线型(Net Type)的特点2.寄存器型(Register Type):定义、与连线型区别(赋值、保值)3.Parameter的使用格式4.3寄存器和存储器1.寄存器定义格式和标矢性2.存储器:定义、格式、位区选择方法4.3运算符1.等式与全等式的区别2.位拼接运算符第5章Verilog HDL行为语句(P45)5.2 Verilog HDL中的过程语句1.always过程语句格式。

2.initial过程语句格式。

5.3 块语句1.块语句。

2.用begin—end产生周期为10的个单位时间的方波.3.用fork—join产生周期为10的个单位时间的方波5.4赋值语句1.分类。

2.阻塞赋值和非阻塞赋值的区别5.5条件语句1.例5.11(模为60的BCD码加法计数器)2.case语句的三种表达形式5.6循环语句1.Verilog HDL中4种类型循环语句。

三人表决器实验

三人表决器实验我们实验采取3种输入方式:原理图方式,VHDL方式,VerilogHDL.你可以只看一种.下面我分别一一介绍三人表决器的功能描述三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LED(高电平亮)显示,如果决议通过那么实验板上L2(黄灯)亮;如果不通过那么实验板上L1(红灯)亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。

1.1 采用原理图设计三人表决器我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:L2=SW1SW2+SW1SW3+SW2SW3L1=_L2那么我们可以在MAX+plusII中用原理图实现上面的三人表决器下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:(1)打开MAX+plusII(2)新建一个图形文件:File菜单>new新建文件时选择Graphic Editor file点OK(3)输入设计文件我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以Symbol ->Enter Symbol(或者双击空白处)弹出窗口:在Symbol Name中输入and2,点OK同样可以加入or3、input、output、not对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

最后的电路图如下图(4)保存文件:保存为majority_voter.gdf,Automatic Extension选.gdf把文件设为当前工程:FILE->PROJECT->SET PROJECT TO CURRENT FILE MAX+PLUS II的标题条将显示新的项目名字至此,程序输入就已经完成了(5)检查编译指定下载的芯片型号指定芯片的管脚(参见10分钟学会PLD设计2 -设计的编译)此时的图形为:下图为SW1放大的图,其中majority_voter@41中前部分为设计的文件名,后面41为EPM7128SLC84-15的41脚,也就是说电路图中SW1被指定到EPM7128SLC84-15的41脚(而实验板上41脚被连接到指拨开关SW1上了,这样电路图上SW1就和实验板上的硬件SW1实现了连接)。

Verilog入门训练4—三人表决器

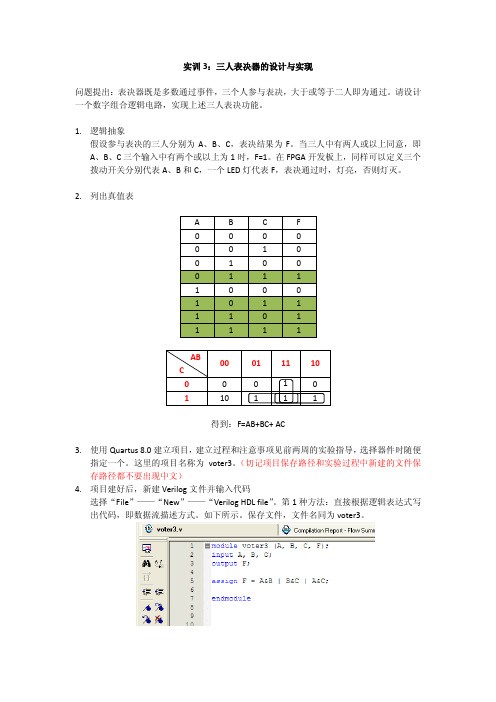

实训3:三人表决器的设计与实现问题提出:表决器既是多数通过事件,三个人参与表决,大于或等于二人即为通过。

请设计一个数字组合逻辑电路,实现上述三人表决功能。

1.逻辑抽象假设参与表决的三人分别为A、B、C,表决结果为F。

当三人中有两人或以上同意,即A、B、C三个输入中有两个或以上为1时,F=1。

在FPGA开发板上,同样可以定义三个拨动开关分别代表A、B和C,一个LED灯代表F,表决通过时,灯亮,否则灯灭。

2.列出真值表得到:F=AB+BC+ AC3.使用Quartus 8.0建立项目,建立过程和注意事项见前两周的实验指导,选择器件时随便指定一个。

这里的项目名称为voter3。

(切记项目保存路径和实验过程中新建的文件保存路径都不要出现中文)4.项目建好后,新建Verilog文件并输入代码选择“File”——“New”——“Verilog HDL file”。

第1种方法:直接根据逻辑表达式写出代码,即数据流描述方式。

如下所示。

保存文件,文件名同为voter3。

5.编译项目。

“Processing”——“Start Compilation”6.功能仿真编译通过后,新建波形仿真文件:“File”——“New”,选择“Vector Waveform File”,如下图所示:在出现的编辑界面左侧右键,选择如下:在“Insert Node or Bus”里选择“Node Finder…”在弹出来的“Node Finder”中,首先在“Filter”中选择“Pins:Unassigned”,然后点击“list”,在“Nodes Found”中会列出所有的引脚,第三步选择全部引脚(鼠标拉),点击“>>”,最后点击“OK”即可。

在回到的“Insert Node or Bus”界面点击“OK”。

这时候会看到所有的引脚会列出来,如下所示,三个输入默认为低电平,输出F状态未知。

由实验原理可知,为了得到A、B、C三个信号不同的组合,设置A为10ns周期信号,B为20ns周期信号,C为40ns周期信号。

数电实验考试 verilogHDL语言及参考程序

题目一:表决器电路设计一、设计任务及原理:所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。

实验中用7个拨动开关来表示七个人,当对应的拨动开关输入为‘1’时,表示此人同意;否则若拨动开关输入为‘0’,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

同时,数码管上显示通过的票数。

二、具体要求:本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能。

拨动开关模块中的K1~K7表示七个人,当拨动开关输入为‘1’时,表示对应的人投同意票,否则当拨动开关输入为‘0’时,表示对应的人投反对票;LED模块中LED1表示七人表决的结果,当LED1点亮时,表示此行为通过表决;否则当LED1熄灭时,表示此行为未通过表决。

同时通过的票数在数码管上显示出来。

在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接使用模块信号对应FPGA管脚说明在以前的实验中都做了详细说明,这里不在赘述。

端口名S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S5 按键开关S5 M15 表示5号抢答者S6 按键开关S6 N16 表示6号抢答者S7 按键开关S7 N15 表示7号抢答者DOUT0 LED模块D1 L14 表决结果亮为通过LEDAG0 数码管模块A段N4 抢答成功者号码显示LEDAG1 数码管模块B段G4LEDAG2 数码管模H4块C段参考答案:module liu(s,dout0,ledag);input [6:0]s;output dout0;output [6:0]ledag;reg [6:0]led;reg [2:0]k;reg clk_en;reg dout;always @(s)begink<=s[1]+s[2]+s[3]+s[4]+s[5]+s[6]+s[0];if(k>=4)begindout<=1;endelsebegindout<=0;endendalways@(k)begincase (k)3'd0:led<=7'b0111111;3'd1:led<=7'b0000110;3'd2:led<=7'b1011011;3'd3:led<=7'b1001111;3'd4:led<=7'b1100110;3'd5:led<=7'b1101101;3'd6:led<=7'b1111101;3'd7:led<=7'b0000111;default:led<=7'b0000000;endcaseendassignledag=led;assigndout0=dout;endmodule题目二:数字电子实验设计题目:彩灯循环电路设计一、设计任务及原理:所谓彩灯循环就是对于一组彩灯(16盏),通过不同的工作模式可按照一定的规律来点亮或者熄灭。

基于VerilogHDL的表决器的设计

基于VerilogHDL的表决器的设计基于V e r i l o g H D L的表决器的设计This model paper was revised by LINDA on December 15, 2012.学生课程实验报告书12 级电通系通信工程专业 03 班学号 312890 姓名2014--2015学年第 2 学期实验项目:基于Verilog HDL的表决器的设计实验时间:实验目的:1、熟悉Verilog HDL的编程。

2、熟悉七人表决器的工作原理。

3、进一步了解实验系统的硬件结构。

实验原理:所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。

实验中用7个按键开关来表示七个人,当对应的按键开关输入为‘1’时,表示此人同意;否则若按键开关输入为‘0’,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

同时,数码管上显示通过的票数。

实验内容:本实验就是利用实验系统中的按键开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能。

按键开关模块中的键1~键7表示七个人,当按键开关输入为‘1’时,表示对应的人投同意票,否则当按键开关输入为‘0’时,表示对应的人投反对票;LED模块中D1表示七人表决的结果,当LED1点亮时,表示此行为通过表决;否则当LED1熄灭时,表示此行为未通过表决。

同时通过的票数在数码管上显示出来。

实验步骤:原理图步骤与实验一相同模式选择键”:按动该键能使实验板产生12种不同的实验电路结构。

本次实验的模式选择到“5”(红色数码管上显示)。

用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。

fpga课程设计8人表决

fpga课程设计8人表决一、教学目标本课程的教学目标是使学生掌握FPGA的基本知识和应用技能,能够独立完成8人表决电路的设计和实现。

具体目标如下:1.知识目标:(1)了解FPGA的基本概念、结构和原理。

(2)掌握VHDL或Verilog硬件描述语言。

(3)熟悉8人表决电路的原理和设计方法。

2.技能目标:(1)能够使用FPGA开发工具进行电路设计和仿真。

(2)能够编写VHDL或Verilog代码实现8人表决电路。

(3)能够进行FPGA编程和硬件测试。

3.情感态度价值观目标:(1)培养学生的创新意识和团队合作精神。

(2)增强学生对电子信息技术的兴趣和热情。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA基础知识:介绍FPGA的基本概念、结构和原理,使学生了解FPGA的特点和应用领域。

2.硬件描述语言:教授VHDL或Verilog硬件描述语言,使学生能够编写代码实现简单的电路。

3.8人表决电路设计:讲解8人表决电路的原理和设计方法,引导学生进行电路设计和仿真。

4.FPGA编程和硬件测试:教授如何使用FPGA编程工具进行编程和硬件测试,使学生能够将设计应用于实际硬件。

三、教学方法为了达到本课程的教学目标,将采用以下教学方法:1.讲授法:讲解FPGA基础知识、硬件描述语言和8人表决电路设计。

2.案例分析法:分析实际案例,使学生更好地理解理论知识。

3.实验法:引导学生进行电路设计和仿真,培养学生的实际操作能力。

4.讨论法:学生进行小组讨论,促进学生之间的交流与合作。

四、教学资源为了支持本课程的教学内容和教学方法,将准备以下教学资源:1.教材:选用权威、实用的教材,如《FPGA设计与应用》、《VHDL与Verilog Primer》等。

2.参考书:提供相关的参考书籍,如《FPGA原理与应用》、《数字集成电路设计》等。

3.多媒体资料:制作课件、教学视频等多媒体资料,以便学生更好地理解理论知识。

4.实验设备:准备FPGA开发板、仿真器等实验设备,供学生进行实际操作。

使用VerilogHDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明[指南]

![使用VerilogHDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明[指南]](https://img.taocdn.com/s3/m/236b285dce84b9d528ea81c758f5f61fb73628db.png)

使用V erilog HDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明综合工具使用synplify pro 7.0仿真工具使用modelsim 5.5e (几个菜单排列与5.6有不同,文中有介绍)布局布线工具及时序仿真模型生成使用maxplusII 10.0一.写在开干之前1.涉及到的文件a.源程序(*.v)用户编写的用于描述所需电路的module (可能有多个文件,多个module相互调用)如果用于综合,则源程序内用于描述的V erilog语言必须是可综合风格的。

否则将只能做功能仿真(前仿真),而不能做综合后的仿真和时序仿真(后仿真)。

b.综合后的V erilog HDL 模型(网表) (*.vm)用综合工具synplify对a 进行综合后生成的电路的V erilog HDL 描述。

由synplify自动生成(必须在Implementation Option —Implementation results选项中选中write mapped verilog netlist后才会生成vm文件)。

此文件用于作综合后的仿真c.布局布线后生成的时序仿真模型(网表) (*.vo)文件使用maxplusII对设计进行布局布线之后,生成的带有布局布线及具体器件延迟特性等参数的电路模型的V erilog HDL描述。

要让maxplusII生成vo文件,必须在maxplusII的compile interface中选中verilog netlist writer。

此文件用于作时序仿真(后仿真)d.测试文件(*.v或*.tf)用户编写的V erilog HDL源程序。

用于测试源程序(a,b,c)中所描述电路。

在测试文件中调用被测试的module,生成被测点路所需的输入信号。

所用V erilog HDL语句不需要是可以综合的,只需语法正确。

如果被测试的模型为a,则对应的仿真为前仿真(功能仿真)如果被测试的模型为b, 则对应的仿真为综合后仿真如果被测试的模型为c, 则对应的仿真为后仿真2.强烈建议a.在写用于综合的源程序时,一个源程序文件里只写一个moduleb.源程序文件名与其内所描述的module名相同(如module myadder 文件名myadder.v)c.为了方便管理文件,为每一个设计都单独创建一个目录,目录内创建source, test子目录分别用于存放源程序(用于综合的)和测试文件。

数电实验考试verilogHDL语言及参考程序

题目一:表决器电路设计一、设计任务及原理:所谓表决器就是对于一个行为;由多个人投票;如果同意的票数过半;就认为此行为可行;否则如果否决的票数过半;则认为此行为无效..七人表决器顾名思义就是由七个人来投票;当同意的票数大于或者等于4时;则认为同意;反之;当否决的票数大于或者等于4时;则认为不同意..实验中用7个拨动开关来表示七个人;当对应的拨动开关输入为‘1’时;表示此人同意;否则若拨动开关输入为‘0’;则表示此人反对..表决的结果用一个LED表示;若表决的结果为同意;则LED被点亮;否则;如果表决的结果为反对;则LED不会被点亮..同时;数码管上显示通过的票数..二、具体要求:本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能..拨动开关模块中的K1~K7表示七个人;当拨动开关输入为‘1’时;表示对应的人投同意票;否则当拨动开关输入为‘0’时;表示对应的人投反对票;LED模块中LED1表示七人表决的结果;当LED1点亮时;表示此行为通过表决;否则当LED1熄灭时;表示此行为未通过表决..同时通过的票数在数码管上显示出来..在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述.. 端口名使用模块信号对应FPGA管脚说明S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S5 按键开关S5 M15 表示5号抢答者S6 按键开关S6 N16 表示6号抢答者S7 按键开关S7 N15 表示7号抢答者DOUT0 LED模块D1 L14 表决结果亮为通过LEDAG0数码管模块A段N4 抢答成功者号码显示LEDAG1数码管模块B段G4LEDAG2数码管模块C段H4参考答案:module lius;dout0;ledag;input 6:0s;output dout0;output 6:0ledag;reg 6:0led;reg 2:0k;reg clk_en;reg dout;always sbegink<=s1+s2+s3+s4+s5+s6+s0;ifk>=4begindout<=1;endelsebegindout<=0;endendalwayskbegincase k3'd0:led<=7'b0111111;3'd1:led<=7'b0000110;3'd2:led<=7'b1011011;3'd3:led<=7'b1001111;3'd4:led<=7'b1100110;3'd5:led<=7'b1101101;3'd6:led<=7'b1111101;3'd7:led<=7'b0000111;default:led<=7'b0000000;endcaseendassignledag=led;assigndout0=dout;endmodule题目二:数字电子实验设计题目:彩灯循环电路设计一、设计任务及原理:所谓彩灯循环就是对于一组彩灯16盏;通过不同的工作模式可按照一定的规律来点亮或者熄灭..我们所要求的彩灯循环电路共分4个节拍;四个节拍按照一定的顺序依次循环执行..二、具体要求:系统设有一个复位键;当按下复位键后;系统从第一节拍开始执行直到第四节拍结束;然后从第一节拍重新开始新的循环..第一节拍:16盏灯Q1~Q16从Q1开始依次点亮;直到Q16为止..每盏灯点亮的时间间隔为一秒;即Q1点亮后;间隔一秒后Q2点亮;然后依次点亮..下面类似间隔时间都为1秒第二节拍:在第一节拍的基础上;16盏灯Q1~Q16从Q16开始依次熄灭;直到Q1为止..每盏灯熄灭的时间间隔为一秒;即Q16熄灭后;间隔一秒后Q15熄灭;然后依次熄灭直到全部熄灭为止..下面类似间隔时间都为1秒第三节拍: 16盏灯Q1~Q16从两端开始依次点亮;即Q1、Q16先点亮;然后Q2、Q15再点亮;直到全部16盏等点亮为止..每盏灯点亮的时间间隔为一秒..第四节拍:在第三节拍的基础上;16盏灯Q1~Q16从中间开始依次熄灭;即Q8、Q9先熄灭;然后Q7、Q10再熄灭;直到全部16盏灯熄灭为止..每盏灯熄灭的时间间隔为一秒..在此实验中数码管、LED、拨动开关与FPGA 的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述.. 端口名使用模块信号对应FPGA管脚说明S1 按键开关S1 R16 表示复位按键Q1 Q1 L14 Q2 Q2 M14Q3 Q3 N14Q4 Q4 N13Q5 Q5 P12 参考答案:module liu2clk;ret;led;input clk;ret;output16:1 led;wire ret_en;reg 16:1led1;reg 5:0i;j;k;l;m;reg 31:0cout;reg clk_en;assignret_en=ret;alwaysposedge clk or negedge ret_enbeginif~ret_enbeginled1<=16'b0000000000000000;i<=0;endelsebeginifclk_enbeginj<=0;k<=0;i<=i+1;ifi<=16begin//dex<=i;//l<=0;//m<=0;led1i<=1;//led1i-j<=0;endelse ifi>16&&i<=32beginj<=k2+1;k<=k+1;led1i-j<=0;//dex<=dex-1;endelse ifi>32&&i<=40begin//dex<=dex+1;//l<=2m+17;led1i-32<=1;led149-i<=1;endelse ifi>40&&i<=48beginled1i-32<=0;led149-i<=0;//dex<=dex-1;endelsebegini<=0;led1<=16'b0000000000000000;endendendendassignled=led1;endmodule题目三:汽车尾灯控制电路设计一、设计任务及原理:假设汽车尾部左右两侧各有3个指示灯;1汽车正常运行时;指示灯全灭..2左转弯时;左侧3个指示灯按照左循环顺序点亮1HZ..3 右转弯时;右侧3个指示灯按照右循环顺序点亮1HZ..4临时刹车时;所有指示灯同时闪烁1HZ..二、具体要求:尾灯与汽车运行状态表开关控制运行状态左尾灯右尾灯S1 S0 D1 D2 D3 D4 D5 D60 0 正常运行灯灭灯灭0 1 左转弯按照D3;D2;D1顺序循环点亮灯灭1 0 右转弯灯灭按照D4;D5;D6顺序循环点亮1 1 临时停车1HZ频率同时闪烁1HZ频率同时闪烁在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述..端口名使用模块信对应FPGA管号脚S1 按键开关S1 R16S2 按键开关S2 P14D1 LED模块D1 L14D2 LED模块D2 M14D3 LED模块D3 N14D4 LED模块D4 N13D5 LED模块D5 P12D6 LED模块D6 N12 脉冲源50MHZ CP J3 参考程序:module lwfclk;ledag;s;input clk;input 1:0s;output5:0ledag;reg5:0led;reg1:0i;j;k;reg31:0cout;reg clk_en;alwaysposedge clkbeginifclk_enbeginifs==2'b00begini<=0;j<=0;k<=0;led<=6'b000000;endelse ifs==2'b01beginled<=6'b000000;k<=0;j<=0;i<=i+1;ifi==2'b01beginled<=6'b001000;endifi==2'b10beginled<=6'b010000;endifi==2'b11beginled<=6'b100000;i<=0;endendelse ifs==2'b10beginled<=6'b000000;k<=0;i<=0;j<=j+1;ifj==2'b01beginled<=6'b000100;endifj==2'b10beginled<=6'b000010;endifj==2'b11beginled<=6'b000001;j<=0;endendelse ifs==2'b11beginled<=6'b000000;i<=0;j<=0;k<=k+1;ifk==2'b01beginled<=6'b000000;endifk==2'b10beginled<=6'b111111;k<=0;endendendendassignledag=led;endmodule题目四:数字电子实验设计题目:抢答器电路设计一、设计任务及原理:抢答器在各类竞赛性质的场合得到了广泛的应用;它的出现;消除了原来由于人眼的误差而未能正确判断最先抢答的人的情况..抢答器的原理比较简单;首先必须设置一个抢答允许标志位;目的就是为了允许或者禁止抢答者按按钮;如果抢答允许位有效;那么第一个抢答者按下的按钮就将其清除;同时记录按钮的序号;也就是对应的按按钮的人;这样做的目的是为了禁止后面再有人按下按钮的情况..总的说来;抢答器的实现就是在抢答允许位有效后;第一个按下按钮的人将其清除以禁止再有按钮按下;同时记录清楚抢答允许位的按钮的序号并显示出来;这就是抢答器的实现原理..二、具体要求:本实验的任务是设计一个四人抢答器;用按键模块的S8来作抢答允许按钮;用S1~S4来表示1号抢答者~4号抢答者;同时用LED模块的LED1~LED4分别表示于抢答者对应的位子..具体要求为:按下S8一次;允许一次抢答;这时S1~S4中第一个按下的按键将抢答允许位清除;同时将对应的LED点亮;用来表示对应的按键抢答成功..数码管显示对应抢答成功者的号码..在此实验中数码管、LED、按键开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里使用模块信号对应FPGA管脚说明不在赘述.. 端口名S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S8 按键开关S12 M15 开始抢答按键DOUT0 LED模块D1 L14 1号抢答者灯DOUT1 LED模块D2 M14 2号抢答者灯DOUT2 LED模块D3 N14 3号抢答者灯DOUT3 LED模块D4 N13 4号抢答者灯LEDAG0数码管模块A段N4 抢答成功者号码显示LEDAG1数码管模块G4B段LEDAG2数码管模块H4C段参考程序:module liu1s1;s2;s3;s4;s8;led;ledag;input s1;s2;s3;s4;input s8;output 6:0ledag;output 3:0led;reg 3:0led;reg k;reg 6:0ledag1;//initial// k<=0;always s8beginifs8==0begin k<=1;led<=4'b0000;ledag1<=7'b0111111;end elsebeginifk==1beginif~s1beginled<=4'b1000;ledag1<=7'b0000110;k<=0;endelse if~s2beginled<=4'b0100;ledag1<=7'b1011011;k<=0;endelse if~s3beginled<=4'b0010;ledag1<=7'b1001111;k<=0;endelse if~s4beginled<=4'b0001;ledag1<=7'b1100110;k<=0;endendendendassignledag=ledag1; endmodule。

数字系统设计(智力竞赛抢答器Verilog HDL建模)

(此文档为word格式,下载后您可任意编辑修改!)课程设计报告课程名称现代数字系统设计设计题目智力竞赛抢答器Verilog HDL建模系别机械与电子工程系班级学生姓名学号任课教师完成时间南湖学院教务办目录一、设计任务与要求 (1)二、方案设计与论证 (1)2.1方案论证 (1)2.2 综合分析 (3)三、模块设计及程序清单 (4)3.1 抢答模块 (4)3.2 锁存模块 (5)3.3 计数模块 (7)3.4 声音警报模块 (9)3.5 声音信号产生模块 (11)四、仿真过程与仿真结果 (12)4.1 仿真过程 (12)4.2 仿真分析 (14)五、结果分析与结论 (16)六、设计心得 (16)七、参考文献 (16)致谢 (17)设计任务起至日期:第17周周一~第19周周一设计题目:智力竞赛抢答器Verilog HDL建模设计要求:1、5组参赛者进行抢答;2、当抢先者按下按钮时,抢答器能准确判断,并以声、光标志(模拟)。

要求声响、光亮时间为3s后自动结束;3、抢答器应具有互锁功能,某组抢答后能自动封锁其他各组进行抢答;4、具有限时功能,分5s、10s、15s三档时间,时间到自动发出声响,且计时时间通过数码管显示(以7段译码输出、动态扫描方式);5、犯规、违章警告信号(如主持人未说“开始抢答”,抢答者按下按钮),以指示灯闪烁标志;6、系统具有一个总复位开关;7、用Verilog HDL对此抢答器进行建模,并在Modelsim SE或Quartus II平台进行仿真测试,给出仿真结果。

智力竞赛抢答器的Verilog HDL建模一、设计任务与要求智力竞赛抢答器Verilog HDL要求有5组参赛者进行抢答,有五个抢答信号进行抢答。

当有抢答选手按下抢答键后系统能够快速准确的判断是那一组选手按下了抢答信号,由于系统比较小,速度比较快一般不会有同时按下的可能,所以只有五种状态,然后系统能够根据这五种状态进行适时的显示和提示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

学生课程实验报告书 12 级电通系

通信工程专业 03 班

学号 312890 姓名

2014--2015学年第 2 学期

实验项目:基于Verilog HDL的表决器的设计

实验时间: 2015.6.07

实验目的:

1、熟悉Verilog HDL的编程。

2、熟悉七人表决器的工作原理。

3、进一步了解实验系统的硬件结构。

实验原理:

所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4时,则认为同意;反之,当否决的票数大于或者等于4时,则认为不同意。

实验中用7个按键开关来表示七个人,当对应的按键开关输入为‘1’时,表示此人同意;否则若按键开关输入为‘0’,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

同时,数码管上显示通过的票数。

实验内容:

本实验就是利用实验系统中的按键开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能。

按键开关模块中的键1~键7表示七个人,当按键开关输入为‘1’时,表示对应的人投同意票,否则当按键开关输入为‘0’时,表示对应的人投反对票;LED 模块中D1表示七人表决的结果,当LED1点亮时,表示此行为通过表决;否则当LED1熄灭时,表示此行为未通过表决。

同时通过的票数在数码管上显示出来。

实验步骤:原理图步骤与实验一相同

模式选择键”:按动该键能使实验板产生12种不同的实验电路结构。

本次实验的模式选择到“5”(红色数码管上显示)。

用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。

观察实验结果是否与自己的编程思想一致

实验现象与结果

当设计文件加载到目标器件后,按实验系统中按键开关模块的键1-键7七位按键开关,如果按键开关的值为“1”(即按键开关的开关置于上端,表示此人通过表决)的个数大于或等于四时LED模块的D1被点亮,否则D1不被点亮。

同时数码管上显示通过表决的人数。

实验程序:

module dee5(K,m_Result,LEDAG);

input [7:1] K;

output m_Result;

output [3:0]LEDAG;

integer i;

reg m_Result;

reg[3:0]LEDAG;

reg [2:0] sum;

always@(K)

begin

sum=0;

LEDAG=0;

for(i=1;i<=7;i=i+1)

if(K[i]) sum=sum+1;

if(sum>=4)

begin m_Result=1;

if(sum==4) LEDAG=4'b0100;

if(sum==5) LEDAG=4'b0101;

if(sum==6) LEDAG=4'b0110;

if(sum==7) LEDAG=4'b0111; end

else m_Result=0;

begin

if(!sum) LEDAG=4'b0000;

if(sum) LEDAG=4'b0001;

if(sum==2) LEDAG=4'b0010;

if(sum==3) LEDAG=4'b0011;

end

end

endmodule

表决器的仿真波形图:

实验现象:当输入大于4个1的时候数码管会显示相应数字,同时LED灯会亮,当输入3个或一下1时,LED灯不亮。

心得体会:通过这次实验是我了解了7人表决器的工作原理,运用老师上课的笔记,轻松的做出了相应的程序。

同时,能更加灵活的运用EDA软件了。

指导教师评语:

实验成绩_______________ 指导教师_______________。