DDR调试步骤

DDR设置步骤

1.设置静态路由RouterA(config)#ip route 172.16.50.0 255.255.255.0 172.16.60.2 RouterA(config)#ip route 172.16.60.2 255.255.255.255 bri02.设置Interesting Traffic804A(config)#dialer-list 1 protocol ip permit804A(config)#int bri0804A(config-if)#dialer-group 13.配置Dialer信息804A#config t804A(config)#int bri0804A(config-if)#ip address 172.16.60.1 255.255.255.0804A(config-if)#no shut804A(config-if)#encapsulation ppp804A(config-if)#dialer-group 1804A(config-if)#dialer-string 8350661或者用804A(config-if)#dialer map ip 172.16.60.2 name 804B 8350661 代替dialer-stringsh run804B#sh runBuilding configuration...Current configuration:!version 12.0no service padservice timestamps debug uptimeservice timestamps log uptimeno service password-encryption!hostname 804B!ip subnet-zero!isdn switch-type basic-ni!interface Ethernet0ip address 172.16.50.10 255.255.255.0no ip directed-broadcast!interface BRI0ip address 172.16.60.2 255.255.255.0no ip directed-broadcastencapsulation pppdialer idle-timeout 300dialer string 8358661dialer load-threshold 2 eitherdialer-group 1isdn switch-type basic-niisdn spid1 0835866201 8358662isdn spid2 0835866401 8358664hold-queue 75 in!ip classlessip route 172.16.30.0 255.255.255.0 172.16.60.1ip route 172.16.60.1 255.255.255.255 BRI0!dialer-list 1 protocol ip permit!可选参数The dialer load-threshold command tells the BRI interface when tobring up the second B channel. The option is from 1–255, where 255 tells theBRI to bring up the second B channel only when the first channel is 100 percent loaded. The second option for that command is in, out, or either. Thiscalculates the actual load on the interface on outbound traffic, inbound traffic,or on the two combined. The default is outbound.The dialer idle-timeout command specifies the number of secondsbefore a call is disconnected after the last interesting traffic is sent. Thedefault is 120 seconds.RouterA(config-if)#dialer load-threshold 125 eitherRouterA(config-if)#dialer idle-timeout 180The dialer load-threshold 125 tells the BRI interface to bring up thesecond B channel if either the inbound or outbound traffic load is 50 percent.The dialer idle-timeout 180 changes the default disconnect time from120 to 180 seconds.Multilink PPP (MP) allows load balancing between the two B channels ina BRI. It is non-vendor specific, and provides packet fragmentation and reassembly, sequencing, and load calculating. Cisco’s MP is based on RFC 1990.The configuration would then look like this:RouterA(config-if)#dialer load-threshold 125 eitherRouterA(config-if)#dialer idle-timeout 180RouterA(config-if)#ppp multilinkNot a tough configuration, but you want to use it nonetheless. This commandwill fragment packets and send them over both lines, which providesa load balancing effect of the data packet. You can verify the multilink isworking with the show ppp multilink command.2个B信道如果要同时激活2条B信道,可以使用dialer load-threshold 1也就是说把流量负载的值设到最小就可以了。

DDR及SPI调试记录

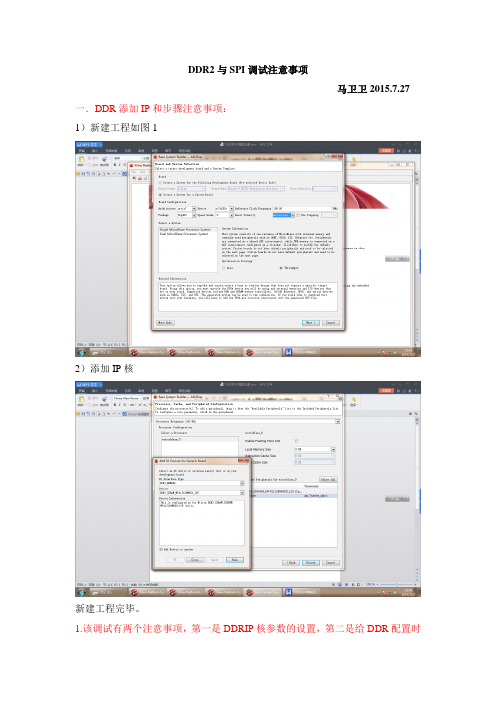

DDR2与SPI调试注意事项马卫卫2015.7.27 一.DDR添加IP和步骤注意事项:1)新建工程如图12)添加IP核新建工程完毕。

1.该调试有两个注意事项,第一是DDRIP核参数的设置,第二是给DDR配置时钟的设置,DDRIP核参数的设置如下图所示:1)2)3)4)此处需要注意,如果选择DDR运行速度是400M,选择2500PS,如果运行速度是200M,徐泽5000ps,datawith根据原理图选择是16灰色部分的4:1导致下个界面datawith选择128然后把DDR的ucf文件添加上即可3.DDR 需要的时钟如下图所示:各个时钟时间的设置有一定的要求:如果mem_clk配置≥400M,那么freq_refclk=400M,如果mem_clk配置<400M,那么freq_refclk=2 * mem_clk,Clk_ref一般设置为200MSync_pulse = (1/16)*mem_clkS_axi的CLK,根据上面灰色部分是4:1和2:1进行配置,如果是4:1,则该参数为0.25倍的mem_clk,如果参数是2:1,改则该参数为0.5倍的mem_clk。

4.时钟配置模块中,如果输入时钟是125M,那么CPU运行到160M需要耗费三个PLL,如果输入时钟为200M,或者100M,那么只需要耗费一个PLL,可节省资源二.SPI调试注意事项:改界面中需要配置的参数含义:如果不用fifo,那么选择false,如果该模块的输入时钟为16M,SPI的时钟要求为2M,那么该ratio配置为16即可,ratio的含义就是AXI的时钟与SPI时钟的比例,下面两个参数是传输数据宽度和连接从IP的个数该界面配置地址即可接口连接方面,首先spisel选择上拉,SCK为SPI输出时钟,SDIO,SIDO是数据输入输出接口,SSN是片选,此处可以直接外接,也可以连接成IO口,由软件进行控制。

(此处由软件进行控制)。

DDR3设计调试

DDR3设计调试DDR3设计配置:1.关于配置寄存器:部分配置寄存器基地址在0x2100_0000#define DDR3_BASE_ADDR (0x21000000)#define DDR_SDCFG (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000008))#define DDR_SDRFC (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000010))#define DDR_SDTIM1 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000018))#define DDR_SDTIM2 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000020))#define DDR_SDTIM3 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000028))#define DDR_PMCTL (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000038))#define RDWR_LVL_RMP_WIN (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000D4)) #define RDWR_LVL_RMP_CTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000D8)) #define RDWR_LVL_CTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000DC))#define DDR_ZQCFG (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000C8))#define DDR_PHYCTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000E4))⼤部分寄存器位于chip-level registers 0x0262_0000 #define DDR3PLLCTL0 (*(unsigned int*)(0x02620330))#define DDR3PLLCTL1 (*(unsigned int*)(0x02620334))#define DATA0_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262040C))#define DATA1_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620410))#define DATA2_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620414))#define DATA3_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620418))#define DATA4_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262041C))#define DATA5_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620420))#define DATA6_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620424))#define DATA7_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620428))#define DATA8_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262042C))#define DATA0_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262043C))#define DATA1_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620440))#define DATA2_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620444))#define DATA3_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620448))#define DATA4_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262044C))#define DATA5_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620450))#define DATA6_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620454))#define DATA7_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620458))#define DATA8_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262045C))#define DDR3_CONFIG_REG_0 (*(unsigned int*)(0x02620404))#define DDR3_CONFIG_REG_12 (*(unsigned int*)(0x02620434))#define DDR3_CONFIG_REG_23 (*(unsigned int*)(0x02620460))#define DDR3_CONFIG_REG_24 (*(unsigned int*)(0x02620464))⼆、KICK Unlock和DDR3 PLL配置初始化DDR3控制器之前必须完成KICK Unlock和DDR3 PLL的配置。

DDR参数详细解释和流程学习

作者:Havis.WangLPDDR5 DRAM工作流程详解 11. 发送地址和命令CPU发送地址和命令:当CPU需要访问LPDDR5中的数据时,首先发送一个地址和相应的命令(读取或写入命令)到内存控制器。

2. 地址解码和行选通行地址选择: LPDDR5根据接收到的行地址(RAS信号)选择特定的行。

行选通延迟(tRCD):从RAS信号发出到CAS信号发出之间的时间延迟。

这段时间内,LPDDR5准备选中的行开始处理。

3. 选中行并准备数据列地址选择和数据准备: LPDDR5接收到列地址(CAS信号),选中特定的列以准备读取或写入数据。

CAS延迟(CL):从CAS信号发出到可以读取或写入数据之间的时间延迟。

这个时间取决于LPDDR5的CL值。

数据传输准备:•DQS(Data Strobe):用于在数据传输时同步和锁存数据的信号。

•DQM(Data Mask):数据屏蔽信号,指示哪些数据位应该被忽略或不处理。

•CK(Clock):时钟信号,用于同步数据传输的时序。

•PREFETCH: LPDDR5采用了32倍prefetch技术,每个存储周期内能够同时传输32个数据位,提高了数据吞吐量。

4. 数据传输和操作时序数据传输和操作时序:•DLL(延迟锁存器):用于控制数据信号的延迟,以确保数据的正确读取和写入。

•SKEW(数据偏移):不同数据信号到达时间的差异,需要通过调整来保持同步。

•Setup Time:数据在有效触发沿到来之前数据保持稳定的时间。

•Hold Time:数据在有效触发沿到来之后数据保持稳定的时间。

5. 预充电和刷新过程预充电和刷新:•预充电(Precharge):在进行下一次读取或写入操作之前,LPDDR5会对未使用的存储单元进行预充电,清空存储单元中的电荷状态。

• 1.2VCC比较刷新过程: LPDDR5在工作时会定期进行行的刷新操作,以保持存储单元的电荷状态,防止数据丢失。

6. 特殊信号处理ODT(On-Die Termination)和ZQ(ZQ Calibration):•ODT:内存总线终端,用于匹配信号阻抗以减少反射和功耗。

xilinx V6 DDR3调试成功经验分享

DDR3 调试DDR3配置:时钟输入400M ,芯片V6 lx240t -2 ff1156 ,突发模式为BL=8,长度为64。

仿真:新建工程,添加用xilinx 生成DDR3核的sim_tb_top 等文件。

进行仿真。

traffic_gen 是xilinx 自带的一个测试DDR 的模块随机的读写DDR ,然后校验读取和写入的数值是不是一样。

如果有错,会拉高tg_compare_error 来报警。

而我们要做的就是自己看懂traffic_gen 向DDR 模块发送的时序,然后去重新编写一个模块来代替traffic_gen 。

traffic_gen 写数据时序图:traffic_gen 读数据时序图:设计读写模块:由于需要代替traffic_gen 模块,所以需要设计数据发送模块(cad_gen_1),命令时序模块(cad_gen_2)和数据校验模块(data_compare ),另外增加异步读写FIFO 来保证读写稳定不出错。

系统模块间信号连接图如下:Example_topDDR3_COREwr_fifoCad_gen_1Wr_endindout Cad_gen_2App_en App_wdf_wren App_wdf_end App_cmdApp_addrPhy_init_done App_rdy App_wdf_rdyRd_enrd_fifodin Wr_enRd_enData_co mparedataRd_en子模块功能cad_gen_1模块负责产要写入DDR3的数据。

先将数据存入写FIFO中。

cad_gen_2模块负责产生命令(app_com),地址(app_addr),控制器写数据有效使能(app_en),写数据使能(app_wdf_wren),写数据结束信号(app_wdf_end)。

data_compare模块负责将从的DDR3核中读出的数据与写入的数据相比较。

从而得出误码率。

子模块接口Cad_gen_1模块信号位宽方向描述Clk 1 Input 外部时钟rst 1 input 复位信号app_rdy 1 Input 由DDR3核输出的核ready信号app_wdf_rdy 1 Input 由DDR3核输出的接收数据ready信号phy_init_done 1 Input 核初始化成功时置1,只有初始化完成以后才能进行相应的读写操作。

利用高带宽混合信号示波器进行DDR验证和调试的技巧

利用高带宽混合信号示波器进行DDR验证和调试的技巧DDR存储器,也称双倍数据率同步动态随机存储器,常用于高级系统的设计,包括计算机、交通运送、家庭消遣系统、医疗设备和消费类产品。

DDR的广泛采纳也推进着DDR存储器自身的研发,在DDR 1和DDR 2逐渐得到普及并成熟运用于某些行业的同时,新的DDR技术也开头浮现在电子产品设计中,如DDR3(第三代DDR技术)和LPDDR(低功耗DDR技术)器件,它们能提供更高的性能。

你可能认为DDR存储器的设计十分简明,但实际上,这些存储器件中更高的数据率和更低的经常会令你感到很难有设计裕量。

此外,DDR接口是最为复杂的高速接口之一,由于每个存储器件上都有无数引脚;DDRII/III DQS、DQ等信号线不是容易的规律1和规律0,还包括高阻态;高速数据传输速率已经达到2.0和PCI-Express等串行技术的数百兆位每秒水平。

这样一来,验证DDR接口成为一项繁杂的任务。

虽然广泛用于DDR接口的高性能物理层验证,但DDR存储器技术的复杂性使常规示波器的验证和调试成为一项挑战。

它可能会限制你进一步测量的能力,如读写数据分别、指令触发、状态机解码和协议调试。

针对此,本文将重点介绍常规示波器验证过程中所遭受的挑战,以及MSO如何应对这些挑战。

验证挑战DDR存储器接口的复杂,不仅体现在它是并行接口,每一根数据信号的传输率达几百兆甚至超过1G比特每秒,而且还体现在DDR存储器控制器和DDR 芯片间大量的信号互连。

一个典型DDR器件有20个以上的信号,包括时钟、6个控制信号、12个地址信号、1个选通信号和8个数据信号。

当启动一项操作时,存储器控制器要通过输出至DDR芯片的控制信号发布指令。

传统示波器惟独4个模拟输入通道,而您可能需要同时衔接全部6个控制信号,来确定发送至 DDR接口的指令类型,更不用说无数时候设计人员需要同时观看时钟、数据选通和数据信号。

第1页共5页。

教你如何调整DDR内存参数

教你如何调整DDR内存参数日期:2006-07-08 上传者:赵磊来源:同样的CPU,同样的频率设置,为什么别人的运行效率就比我的高呢?为什么高手能以较低CPU频率跑出更好的测试成绩呢?问题的关键就是内存参数的调校。

在一般的超频中,只会调整一些基本参数,比如某超频报告中会说到内存运行状态为“520MHz、3-4-4-8 1T”,那么除频率外后5个数字就是基本参数。

还有一系列参数被称之为“小参”,能起到辅助调节作用,当调节基参后仍无法提高频率,或者性能提升不明显后,调整“小参”往往会得到令人意外的惊喜。

以下我们根据基本参数与小参分别介绍调校方法。

基本参数介绍目前的内存还是使用类电容原理来存储数据,需要有充放电的过程,这个过程所带来的延迟是不可避免的。

在BIOS中,所有关于内存调节的参数其实都是在调整这个充放电的时序。

受颗粒品质影响,每种内存的参数几乎都不完全一样。

面对这些参数,我们必须先了解其原理才能在以后的调节中做到信手拈来。

以下我们讲解一些重点参数的含义。

CLCL全称CAS Latency,是数据从存储设备中输出内存颗粒的接口之间所使用的时间。

一般而言是越短越好,但受于制造技术和内存控制器所限,目前的最佳值是2。

从图中,我们能够直观的看到CL值变化,对数据处理的影响。

虽说在单周期内的等待的时间并不长;但在实际使用时,内存每秒要400M次以上的周期循环,此时的性能影响就相当明显了。

RAS与CAS内存内部的存储单元是按照行(RAS)和列(CAS)排成矩阵模式,一个地址访问指令会被解码成行和列两个信号,先是行地址信号,然后是列地址信号,只有行和列地址都准备好之后才可以确定要访问的内存单元。

因此内存读写第一个延迟是RAS到CAS的延迟,从行地址访问允许到读、写数据还有一个准备时间,被称为RAS转换准备时间。

这也就是为什么RAS to CAS参数对性能影响要大于RAS Precharge的原因。

Tras内存预充电和有效指令之间的时间差。

i.MX6DDR参数设置-电脑资料

i.MX6DDR参数设置-电脑资料DDR Stress Test Tool 提供了两种用途,。

首先,它可以用来对校准DDR3,以便于MMDC PHY delay settings和PCB配对,来达到最佳的DRAM新能。

整个过程是全自动的,因此客户可以在较短的时间内让他们的DDR3工作起来。

另外,该工具可以运行内存压力测试,用来验证DDR3的功能和可靠性。

压力测试可以用来验证硬件连接、MMDC寄存器参数和DDR3模式寄存器设置。

测试最重要的目的是让客户验证DDR3在他们的自己的板子上运行稳定。

Calibration在i.MX6处理器上,DDR3需要4个校准过程,这些校准过程微调MMDC PHY等待寄存器校正会在DDR Stress Test Tool 键入DDR3配置。

首先,校准测试会提示DRAM频率。

i.MX6Q和i.MX6D的默认值是528MHz,i.MX6DL、i.MX6S和i.MX6SL的默认值是400MHz。

这是BSP使用的DRAM频率。

按'y'来继续执行校正过程。

这里输入'n'会有一个选项来选择特定的频率。

它仅仅是用来调试。

DRAM频率选择结束后,这个工具会开始校正。

Write Leveling Calibration这是第一个校正,用来微调从i.MX6 processor输出的DRAM clock和write DQS 之间的delay,按'y'来继续执行校正过程。

如果board已经校正并且校正结果已经和融入脚本,按'n'跳过校正。

在按'y'开始校正以后,你需要输入DDR3 Mode Register MR1的值,MR1的值可以在初始化脚本的下列行中找到。

The value 是等号后的两个最高有效字节,i.e. 0x0004 on this example.setmem /32 0x021b001c = 0x00048031 // MMDC0_MDSCR, MR1 write, CS0 The value必须是和DDR初始化脚本中的是同一个。

DDR_test简单操作流程

CPU_ddr_test1、打开secureCRT软件-快速连接:协议:Telnet主机名:NVR的IP端口不用更改:23防火墙:None 点击连接。

2、登陆密码3、执行文件:cpu_ddr_test将执行文件cpu_ddr_test考到U盘根目录里注:如果将该执行文件让研发人员加入到BIN目录下,步骤3、5、6、7不用操作,且将第8步的./去掉。

让研发人员加入到BIN目录下操作简单,不加入到BIN目录下,操作复杂,还得安装Linux虚拟机。

4、# cat /proc/media-mem查询DDR内存使用情况例如:看总内存,查看剩余内存为54MB,则计算源地址与目标地址。

一片DDR内存为2Gb=256MB=(256*1024*1024B)d=0x10000000,一片目标地址=0x10000000+0x80000000=0x90000000,因为测试的ND7016有两片2Gb的DDR,所以两片的目标地址=0xa0000000;剩余内存为54MB=(54*1024*1024B)d=0x3600000一片源地址=0x90000000-0x3600000=0x8ca00000两片源地址=0xa0000000-0x3600000=0x9ca000005、#df 查询磁盘6、# cp /mnt/udisk0/00/cpu_ddr_test /tmp/复制7、#cd /tmp进入8、./cpu_ddr_test 1 (源地址-0x80000000)(目标地址-0x80000000) 0 &执行命令上例中两片内存2Gb的DDR测试命令为:./cpu_ddr_test 1 0x1ca00000 0x20000000 0 &注:源地址到目标地址的范围比较大,可以分割多次测试,间隔为0x400000例如:(1)0x1ca00000 0x1ce00000(2)0x1ce00000 0x1d200000(3)0x1d200000 0x1d600000(4)0x1d400000 0x1da00000(5)0x1da00000 0x1de00000(6)0x1de00000 0x1e200000……(n)0x1fe00000 0x200000009、查看结果:如果没有出错,就会一直不打印东西如下图:如果出错则:第一次出错:源数据是d8222264,出错数据为:d8228284warning:rand addr check at i=8899, addr:d8122264 d8222264 d8322264d8422264!warning:rand data check at i=8899, data:0 d8122264 d8228284 d8322264 d8422264!read error:rand data check read error maybe because of err count = 1!出错次数为count = 1,因此基本上可以断定是DDR在读的过程中出错。

内存参数DDR怎么优化

内存参数DDR怎么优化 电脑内存少导致运⾏变慢,那如何对内存参数进⾏优化设置呢?下⾯是店铺为⼤家介绍内存参数DDR优化的⽅法,欢迎⼤家阅读。

优化内存的延迟参数对PC性能的提⾼有很⼤帮助。

优化内存是通过调节BIOS中⼏个内存时序参数来实现的。

内存参数DDR优化的⽅法 ⼀、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 ⾸先,需要在BIOS中打开⼿动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开⼿动设置,之后会⾃动出现详细的时序参数列表: 1、CL(CAS Latency):“内存读写操作前列地址控制器的潜伏时间”(可能的选项:1.5/2/2.5/3) BIOS中可能的其他描述为:tCL、CAS Latency Time、CAS Timing Delay。

这个参数很重要,内存条上⼀般都有这个参数标记。

在BIOS设置中DDR内存的CAS参数选项通常有“1.5”、“2”、“2.5”、“3”⼏种选择,SDRAM则只有“2”、“3”两个选项。

较低的CAS周期能减少内存的潜伏周期以提⾼内存的⼯作效率。

因此只要能够稳定运⾏操作系统,我们应当尽量把CAS参数调低。

反过来,如果内存运⾏不稳定,可以将此参数设⼤,以提⾼内存稳定性。

2、tRCD(RAS-to-CAS Delay)“⾏寻址⾄列寻址延迟时间”(可能的选项:2/3/4/5) BIOS中的可能其他描述: tRCD、RAS to CAS Delay、Active to CMD等。

数值越⼩,性能越好。

(新)教你如何调整DDR内存参数

教你如何调整DDR内存参数日期:2006-07-08 上传者:赵磊来源:同样的CPU,同样的频率设置,为什么别人的运行效率就比我的高呢?为什么高手能以较低CPU频率跑出更好的测试成绩呢?问题的关键就是内存参数的调校。

在一般的超频中,只会调整一些基本参数,比如某超频报告中会说到内存运行状态为“520MHz、3-4-4-8 1T”,那么除频率外后5个数字就是基本参数。

还有一系列参数被称之为“小参”,能起到辅助调节作用,当调节基参后仍无法提高频率,或者性能提升不明显后,调整“小参”往往会得到令人意外的惊喜。

以下我们根据基本参数与小参分别介绍调校方法。

基本参数介绍目前的内存还是使用类电容原理来存储数据,需要有充放电的过程,这个过程所带来的延迟是不可避免的。

在BIOS中,所有关于内存调节的参数其实都是在调整这个充放电的时序。

受颗粒品质影响,每种内存的参数几乎都不完全一样。

面对这些参数,我们必须先了解其原理才能在以后的调节中做到信手拈来。

以下我们讲解一些重点参数的含义。

CLCL全称CAS Latency,是数据从存储设备中输出内存颗粒的接口之间所使用的时间。

一般而言是越短越好,但受于制造技术和内存控制器所限,目前的最佳值是2。

从图中,我们能够直观的看到CL值变化,对数据处理的影响。

虽说在单周期内的等待的时间并不长;但在实际使用时,内存每秒要400M次以上的周期循环,此时的性能影响就相当明显了。

RAS与CAS内存内部的存储单元是按照行(RAS)和列(CAS)排成矩阵模式,一个地址访问指令会被解码成行和列两个信号,先是行地址信号,然后是列地址信号,只有行和列地址都准备好之后才可以确定要访问的内存单元。

因此内存读写第一个延迟是RAS到CAS的延迟,从行地址访问允许到读、写数据还有一个准备时间,被称为RAS转换准备时间。

这也就是为什么RAS to CAS参数对性能影响要大于RAS Precharge的原因。

Tras内存预充电和有效指令之间的时间差。

ddr3内存超频教程

ddr3内存超频教程DDR3内存超频教程DDR3内存超频是指通过调整内存频率、工作时序等参数,来提高内存的运行速度和性能。

下面是一个简单的DDR3内存超频教程,帮助你了解和进行内存超频。

步骤一:了解你的内存和主板首先,需要了解你使用的DDR3内存的基本信息,包括型号、频率、时序等。

同时,你还需要了解自己的主板支持的内存频率和超频选项,以确保你的内存超频操作不会超出主板的限制。

步骤二:备份重要数据在进行内存超频之前,首先要确保你的数据得到备份,以防止超频过程中出现错误导致数据丢失。

步骤三:进入BIOS设置重启电脑并进入BIOS设置界面。

具体的方法可能因主板型号而有所不同,一般在开机时按下“Delete”、“F2”、“F10”等键进入BIOS设置界面。

步骤四:找到内存设置选项在BIOS设置界面中,找到和内存相关的选项。

一般来说,内存选项可能在“Advanced”、“Overclock”或者“Memory”等菜单下。

你可能会看到一些参数,如“DRAM Frequency”、“CAS Latency”、“RAS to CAS Delay”等。

步骤五:调整内存频率找到“DRAM Frequency”或类似选项,一般默认设置为内存的基准频率,如DDR3 1333MHz。

你可以通过选择更高的频率来超频你的内存。

然而,要注意的是,不同内存和主板都有自己的限制,将频率过高可能导致系统稳定性问题。

步骤六:调整时序参数除了频率,你还可以尝试调整时序参数。

时序参数包括CAS Latency、RAS to CAS Delay、Command Rate等。

调整这些参数可以进一步提高内存的性能,但同样需要谨慎操作,以免导致系统不稳定。

步骤七:保存设置并退出BIOS经过调整后,确认你的超频设置无误后,保存设置并退出BIOS界面。

在保存设置时,一般会有提示告诉你是否确定保存。

步骤八:测试稳定性重启电脑后,你可以使用一些内存稳定性测试软件,如Memtest86+,来测试你的内存超频是否稳定。

DDR2调试记录

DDR2调试记录1.1 硬件环境硬件设计参考xilinx官方开发板ML555设计,硬件板子为公司简化版ML555光口板,主控芯片为XILINX公司的VIRTEX5‐xc5vlx50t‐ff1136,板子支持两组DDR2模块,单个模块由4片MT47H128M8HQ‐3IT组成,单片数据位宽为8BIT,4片DDR2组成32bit总位宽.但是FPGA内部实现方式由一片MT47H128M16XX‐37E取代两片MT47H128M8HQ‐3IT,这样两片MT47H128M8HQ‐3IT共用一组控制线,FPGA内部配置的数据宽度为32BIT,由两片MT47H128M16XX‐37E实现,具体的硬件电路细节为时钟2转4其他控制总线直接一分二,参考电路图即可.1.2软件配置直接例化IPCORE,本设计采用无TESTBENCH,无PLL的方式.系统的结构如下图所示,其中dcm4ddr2为时钟输出模块,内部例化两个DCM ,第一个DCM产生200M时钟,第二个DCM直接输出200M时钟以及其他相关时钟;ddr2_test_control为自定义模块,产生测试信号;ddr2_corgen为系统例化IP.ISE结构层次RTL视图1.2.1 dcm4ddr2模块本模块的作用是生成200M时钟,以及用户时钟,以及DDR2所需要的各种相位时钟和复位信号.RTL视图即端口引脚说明,如下图所示其内部结构如下图所示所有时钟输出均上BUFG,第二个DCM输出的LOCK信号作为DDR2控制器的复位信号,不过最新版本的UG086推荐使用PLL方式,相信结构会更加精简.1.2.2 ddr2_test_control模块本模块实现对例化IP核的控制.内部由状态机实现对IP核控制信号,读写数据信号,地址信号的输出以及输入数据采集,采用chipscope观察,测试机理为:先对DDR2执行一个burst写操作,然后执行相同地址的同样长度的burst读操作,对比写入的数据是否和读出的数据一致.例程采用的时钟为200M时钟,与DDR2的工作时钟一致,所以没有添加任何FIFO.将来使用时,若用户时钟不为200M时,需要从读写端分别添加两个FIFO实现切换工作.1.2.3 DDR2 IP核的例化Step1:是用core gen工具,新建工程,利用MIG模块生成DDR2控制器IP核.选定芯片,以及硬件描述语言Step2:搜索MIG,并打开MIG,见下图 ,并点击nextStep,本设计例化一个控制器,所以默认选项即可,直接nextStep3:直接nextStep4:直奔主题Step5:重要的一步,DDR2工作在200M(双沿400M),因此周期选择5000PS,虽然外部的DDR2硬件是8BIT位宽,但是在这里选择的硬件型号却选择为16bit位宽,而用户数据位宽选择32BIT,这样对于FPGA来说相当于两片16bit的芯片组成的存储结构.两片8bit的存储芯片共用控制线.使能MASK功能Step6:按照下图配置,选择不同的工作模式可以.例程1采用burst4的传输模式,直接在Step7:禁用PLL,下面的差分单端时钟自动变灰,这样,就需要外围时钟产生模块产生单端(FPGA parameter 中修改参数即可,这些参数都可变.next内部的)时钟了,通过查阅UG086文档,推荐使用PLL,这样,1.2.1的内容可以忽略.Step8:连点两次next,跳到如下界面,本界面支持两种方式的UCF配置,第一支持XILINX推荐的方式,这样的方式显然适合先做FPGA逻辑验证,然后再画PCB板,UCF配置自由灵便,.第二种就是固定模式的,本人此次调试就采用如下模式,直接利用已有资源,读取UCF文件(read ucf file选型),配置信息自动加载进去,稍作修改(INI_DONE,ERROR RST等信号)即可投入使用.见下图选中FIXED PIN OUT选项,直接nextStep9选中想要的文件后,即可得到下图点击readucf,并且找到你所需要的UCF文件见下图点击打开即可得到下图有几个信号需要你添加IO,随便填上,先过了这一关,一会UCF生成后再来收拾这些无关紧要的信号Step10:一路next,直到最后生成.关闭congen1.3 调试过程IP核生成的文档结构如下图所示我们最关心的当属user_design文件夹,rtl中的所有文件是毫无疑问要添加到工程中的,另外一个重要的文件为par文件夹中的ucf文件,前面说过,要做稍微的修改,至于修改哪些视硬件结构而定,例如本应用中只需要一个CS片选即可,那么cs1应当忽略,另外inidone不需要输出,err也不需要输出,应当去掉,DDR2的复位为内部输入,不需要外部输入,因此也去掉,否则综合实现的过程中一定会报错.1.3.1成功的INI_DONE信号这是成功的第一步,如果ini_done一直为低,那后续工作无法开展.1.3.2 burst4调试结果ddr2_test_control模块中一个burst(BL=4)写入内容如下:Chipscope读出的数据如下图所示从图中可以看出DDR2控制器输出的rd_data_valid与写入的数据一直,调试成功1.3.3 burst8调试结果将BL改为8,写入的内容如下:Chipscope调试结果如下图所示:1.4调试中的几个小问题1.4.1.Four bursts(BL=4)的错误理解由于看文档的不仔细,在查阅UG086 P384的时候,错误的理解为此时序图为一个burst的传输,实际上该图突发传输了4次,同理P386的读burst也是4次.xinlinx这个地方为什么不写成3次,或者5次,如果是这样,一定不会误导本人….浪费了两天时间..1.4.2.mask信号在看原设计的时候,由于是用vhdl写的,所以看起来很费劲,我只看了RTL视图,原设计RTL 视图mask信号浮空不接,因此我在设计中直接将mask置0.后来才知道mask信号的意义.1.4.3 地址信号本应用的DDR2地址参数配置如下:parameter BANK_WIDTH = 3, // # of memory bank addr bits.parameter COL_WIDTH = 10, // # of memory column bits.parameter ROW_WIDTH = 14, // # of memory row and # of addr bits.parameter CS_WIDTH = 2, // # of total memory chip selects.按照UG086对于用户接口地址总线的说明,这样实际的地址宽度为2+3+10+14为29bit,未使用的地址应当置1.因此DDR2的地址0对应的地址总线数据为(3’b111,28’d0)。

理解DDR3及调试

DDR2/DDR3 比较之layout

DDR3 layout analyze

DDR3 之Write leveling

DDR3 之Write leveling 实现方式

DDR3 测试之读写分离

• DDR3写操作时,DQS write preamble 在一个clk周期内先高后低,如下 图所示:

DQ读写波形有较大overshoot

• 如下图,当写时DQS,DQ上存在较大的振铃。 • 此时DRAM端ODT设置为120ohm.

DQ写波形有较大overshoot(续)

• 将DRAM测ODT修改为60ohm后测试波形如下:

DQS读信号回沟位置调整

• 当测试读信号时,DQS上升沿会存在回沟,如下图所示,此回沟可导 致DQS误触发可使用调整CPU内部ODT的方式进行调整。<此回沟的形 成与测量点也有关系。>

DDR3 测试之读写分离(续)

• DDR3读操作时,DQS read preamble为一个clk周期的低电平,如下图 所示:

DБайду номын сангаасR2/DDR3 比较之CWL

• CWL:CAS write latency, it’s only defined in DDR3. In DDR2, WL = RL-1.

DDR 参数之CL

• CL:CAS Latency

1. CAS latency is the delay, in clock cycles, between the internal Read command and availability of the first bit of output data. 2. programmable CAS Latency 5,6,7,8,9,10,11,12,13 3. CL is only decided by DRAM . Ps, BL: Burst length

ddr3初始化和校准流程

ddr3初始化和校准流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!DDR3(Double Data Rate 3)是一种计算机内存技术,以下是 DDR3 初始化和校准的一般流程:1. 上电和复位:将 DDR3 内存模块插入主板插槽,并确保电源供应正常。

主板DDR内存时序设置(全)

挖掘电脑潜在动力主板DDR内存时序设置指南DDR内存既然叫做双倍速率SDRAM(Dual date rate SDRSM),就是说是SDRAM的升级换代产品。

从技术上分析,DDR SDRAM最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR的数据传输速率为传统SDRAM的两倍。

那么大家就应该知道了,我们所说的DDR400,DDR333,DDR266,他们的工作频率其实仅为那些数值的一半,也就是说DDR400工作频率为200MHz。

FSB与内存频率的关系首先请大家看看表一:FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。

FSB/MEM比率实际运行频率1/01200MHz1/02100MHz2/03133MHz3/04150MHz3/05120MHz5/06166MHz7/10140MHz9/10180MHz对于大多数玩家来说,FSB和内存同步,即1:1(DFI 用1/01表示)是使性能最佳的选择。

而其他的设置都是异步的。

同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。

如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

表2更详尽列出了FSB与不同速度的DDR内存之间正确的设置关系强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。

Command Per Clock(CPC)可选的设置:Auto,Enable(1T),Disable(2T)。

Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。

由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。

DDR2内存时序调节方法

DDR2内存时序调节方法DDR2内存已经成为目前绝大部分用户的标配产品,而如何合理设置DDR2的参数就成为了不少用户(尤其是菜鸟用户)的最想了解的地方。

当你超频的时候,如何平衡内存频率和参数之间的关系;究竟如何合理选取内存频率,什么参数才是带来最高性能呢?相信这些问题是目前最多用户最想了解。

其实要了解这些东西,首先要明白DDR2内存在BIOS中的参数设置情况。

因为要提高系统整体性能,并不只是简单超频CPU外频,调高内存频率这么简单,将一大堆数字合理地分配和组合才是最为重要的。

目前市场上销售的DDR2内存主要按频率来划分,譬如DDR2 533、DDR2 667、DDR2 800就是消费者最常见的产品(注:部分厂商推出DDR2 1000高频DDR2内存,但这些DDR2内存在市场上并不多见,而价格昂贵,所以我们就暂时不讨论一些超频型DDR2内存)。

在这三款内存产品当中,就数DDR2 667内存最为多人购买,因为它同时具备了性能、价格、兼容性这些特点,而DDR2 533已经逐步被DDR2 667所取代。

如果您的内存为镁光D9颗粒,请直接参考本站《镁光小D9内存超频调教全攻略》,如果您是DDR内存,请参考本站《教你如何调整DDR内存参数》至于目前频率较高DDR2 800也逐渐成为玩家购买的对象,因为Intel双核心平台对高频DDR2内存有着极大需求,要发挥酷睿2最大威力,一条高频率、可运行高参数的DDR2内存是非常重要的。

鉴于AMD AM2处理器内置了DDR2内存控制器,所以AM2平台的DDR2设置方法与Intel平台有着不同。

最稳当的DDR2内存设置方法,就是在主板BIOS当中将DDR2的设置参数设为By SPD,而这个选项也是最安全的DDR2内存设置方法。

不过这个设置最大缺点是,没有将内存的潜力发挥出来,只是用安全换来相对较低的性能。

如果你想超频手中的DDR2,那么By SPD选项将不是你的设置的地方,手动调整才是你的手段。