FPGA cpld--串口程序

基于fpga的串口设计及实现

基于fpga的串口设计及实现

基于FPGA的串口设计及实现是一个涉及数字电路设计和通信协

议的复杂课题。

首先,让我们从串口通信的基本原理开始。

串口通信是一种通过串行传输数据的通信方式,它使用一个或

多个数据线(通常是一对)来逐位地传输数据。

常见的串口通信标

准包括RS-232、RS-485、UART等。

在FPGA中实现串口通信,需要

考虑以下几个方面:

1. 串口通信协议选择,根据具体的应用场景和需求,选择合适

的串口通信协议。

例如,UART是一种常见的串口通信协议,它使用

起始位、数据位、校验位和停止位来传输数据。

2. 串口通信接口设计,在FPGA中设计串口通信接口,需要考

虑数据的发送和接收,时钟信号的同步等问题。

通常需要使用FPGA

的IO资源来实现串口通信接口。

3. 串口通信协议的实现,在FPGA中实现选择的串口通信协议,包括数据的发送和接收、时序控制、校验等功能。

这通常需要使用Verilog或VHDL等硬件描述语言进行开发。

4. 硬件调试和验证,设计完成后,需要进行硬件调试和验证,包括时序分析、波形仿真等工作,确保串口通信的稳定和可靠。

在实际的FPGA串口设计中,还需要考虑时钟频率、数据传输速率、数据格式、数据校验、中断处理等问题。

此外,还需要考虑FPGA与外部设备的接口,如与传感器、显示器、存储器等设备的接口设计。

总之,基于FPGA的串口设计及实现涉及到硬件设计、数字电路设计、通信协议等多个方面的知识,需要综合考虑各种因素,进行全面的设计和实现。

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

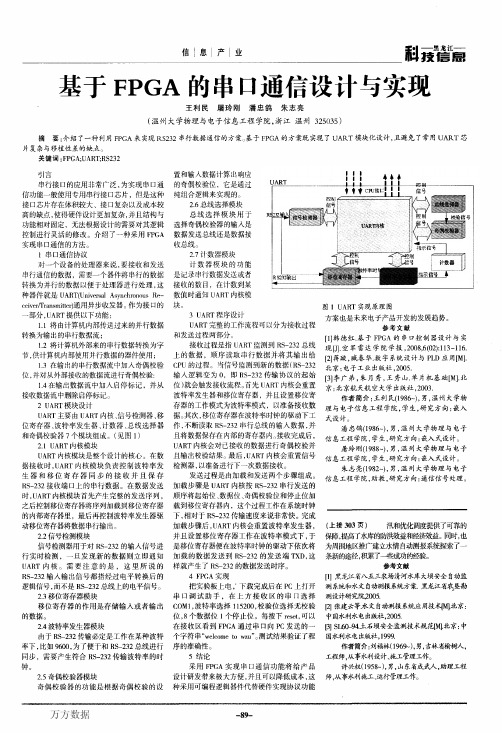

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

CPLD与FPGA学习总结资料

一.VHDL的设计单元Entity(实体)用来说明模型的外部输入输出特征Architecture(构造体)用来定义模型的内容和功能每一个构造体必须有一个实体与它相对应,所以两者一般成对出现端口模式:IN:数据只能从端口流入实体OUT:数据只能从端口流出实体INOUT:数据从端口流入或流出实体BUFFER:数据从端口流出实体,同时可被内部反馈数据类型:●BIT :位类型,其值只能为…0‟或'1…●BIT_VECTOR :位矢量类型,是基于BIT数据类型的数组。

使用位矢量必须注明宽度,即数组中的元素个数和排列。

●BOOLEAN:布尔类型,其值可为…TRUE‟或…FALSE‟●INTEGER:整型,范围为-214783647到214783647(232-1),综合时,要对范围加以限制。

常用于循环语句的循环次数、常量、数学函数或模式仿真●Natural:自然数类型,整型的子类型,含零和正整数●Positive:正整数类型,整型的子类型,含非零和非负整数●REAL:浮点类型,范围为:-1.0E38到1.0E38很多综合器不支持该类型,仅能在仿真器中使用。

●枚举类型:用户定义的数据类型例:TYPE traffic_light IS (red, yellow,green )TYPE int IS RANGE 0 TO 100signal a :traffic_light ;●数组类型:分一维数组和二维数组,限定性和非限定性数组例:TYPE Bit_Vector IS ARRAY (Natural RANGE<>) OF Bit;TYPE Word IS ARRARY (31 downto 0) OF Bit;●SUBTYPE:子类型,一般用来对其父类型加以限制例:SUBTYPE Std_Logic IS resolved Std_Ulogic●TIME:时间类型,范围和整型一样,表达时要包括数值和单位两部分。

逻辑设计中的FPGA与CPLD技术应用

逻辑设计中的FPGA与CPLD技术应用在现代电子行业中,逻辑设计是一个至关重要的环节。

FPGA (Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)技术作为两种主要的可编程设备,已经在逻辑设计中广泛应用。

它们具有灵活性、可编程性以及高度集成的特点,使得它们在各种应用领域中扮演着重要的角色。

一、FPGA技术应用FPGA是一种可编程逻辑器件,其内部可通过编程实现各种逻辑功能和数字电路设计。

FPGA通常由可编程逻辑单元(CLB)、输入输出引脚和输入输出模块等部分构成。

其设计过程包含RTL(Register-Transfer Level)描述、综合、布局布线以及配置等环节。

1. 通信与网络领域在通信领域,FPGA被广泛应用于协议转换、调制解调器设计以及网络加速器等方面。

由于FPGA的可编程性,可以根据需要灵活配置不同的协议,实现不同网络之间的无缝对接。

2. 数字信号处理(DSP)领域在数字信号处理领域,FPGA被广泛应用于图像处理、音频处理以及实时数据处理等方面。

由于FPGA具有并行处理的能力,能够同时处理多个数据流,因此在实时性要求较高的应用中表现出色。

3. 汽车电子领域在汽车电子领域,FPGA被广泛应用于汽车控制单元(ECU)和车载娱乐系统等方面。

由于汽车电子应用对可靠性和安全性要求较高,FPGA的可编程性以及自适应性能使其成为理想的选择。

二、CPLD技术应用CPLD是一种更小规模的可编程器件,与FPGA相比,CPLD通常更适用于复杂逻辑功能的实现。

CPLD通常由可编程逻辑阵列(PLA)、输入输出引脚以及输入输出缓冲区组成。

1. 控制系统领域在控制系统领域,CPLD被广泛应用于逻辑控制器的设计。

由于CPLD具有高速、低功耗以及可靠性强的特点,被广泛应用于各类自动化控制系统中。

2. 电源管理系统领域在电源管理系统领域,CPLD被广泛应用于电源管理单元(PMU)的设计。

FPGA与CPLD 总结

CPLD(complex programable logic device)复杂可编程逻辑器件FPGA(field programable gate array)现场可编程门阵列FPGA和CPLD的逻辑单元本身的结构与SPLD相似,即与阵列和可配置的输出宏单元组成。

FPGA逻辑单元是小单元,每个单元只有1-2个触发器,其输入变量通常只有几个因而采用查找表结构(PROM形式)这样的工艺结构占用的芯片面积小,速度高(通常只有1-2纳秒),每个芯片上能集成的单元数多,但逻辑单元功能弱。

如果想实现一个较复杂的功能,需要几个这样的单元组合才能完成(总延时是各个单元延时和互连延时的和),互连关系复杂。

CPLD中的逻辑单元是单元,通常其变量数约20-28个。

因为变量多,所以只能采用PAL结构。

由于这样的单元功能强大,一般的逻辑在单元内均可实现,因而其互连关系简单,一般通过集总总线既可实现。

电路的延时通常就是单元本身和集总总线的延时(通常在数纳秒至十几纳秒),但是同样集成规模的芯片中的触发器的数量少得多。

从上面分析可知道:小单元的FPGA较适合数据型系统,这种系统所需要的触发器数多,但是逻辑相对简单;大单元的CPLD较适合逻辑型系统,如控制器等,这种系统逻辑复杂,输入变量多,但触发器需求量相对较少。

反熔丝工艺只能一次性编程,EPROM EEPROM 和FLASH工艺可以反复的编程,但是他们一经编程片内逻辑就被固定。

他们都是只读型(ROM)编程,这类编程不仅可靠性较高还可以加密。

XILINX公司的FPGA芯片采用RAM型编程,相同集成规模的芯片中的触发器数目较多,功耗低,但是掉电后信息不能保存,必须与存储器联用。

每次上电时必须先对芯片配置,然后才能使用,这似乎是RAM型PLD的缺点,但是ROM型PLD中的编程信息在使用时是不能变化的,RAM型PLD却可以在工作时更换内容,实现不同的逻辑。

CPLD和FPGA的结构,性能对照:CPLD FPGA PROM集成规模:小(最大数万门)大(最高达百万门)单元粒度:大(PAL结构)小(PROM结构)互连方式:集总总线分段总线长线专用互连编程工艺:EPROM EEPROM FLASH SRAM编程类型:ROM RAM型须与存储器联用信息:固定可实时重构触发器数:少多单元功能:强弱速度:高低222222222222222222222222222222222222延迟:确定,可以预测不能确定不能预测功耗:高低加密性能:可加密不能加密适用场合:逻辑型系统数据型系统LCA(LOGIC CELL ARRAY)逻辑单元阵列CLB(CONFIGURABLE LOGIC BLOCK)可配置逻辑模块IOB(INPUT OUTOUT BLOCK)输入输出块Spartan-xl系列FPGA的主要特性SPARTAN-XL系列的FPGA具有低压,低功耗的特点。

FPGA的配置及其接口电路的设计

第21卷 第2期电子测量与仪器学报V ol 121 N o 12JOURNAL O F EL ECTRON I C 2007年4月M EASUR E M EN T AND I N STRUM EN T・109 ・本项目为福建省教育厅科技资助项目(编号:JA03005)和福建省自然科学基金计划资助项目(编号:Z0512003)。

本文于2005年12月收到。

王灵芝:硕士研究生;黄春晖:教授。

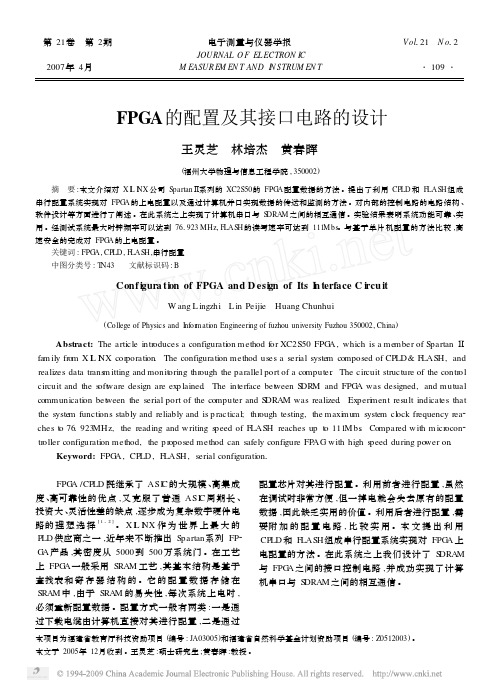

FPGA 的配置及其接口电路的设计王灵芝 林培杰 黄春晖(福州大学物理与信息工程学院,350002)摘 要:本文介绍对X I L I N X 公司Spartan Ⅱ系列的XC2S50的FPG A 配置数据的方法。

提出了利用CP LD 和F LASH 组成串行配置系统实现对FPG A 的上电配置以及通过计算机并口实现数据的传送和监测的方法。

对内部的控制电路的电路结构、软件设计等方面进行了阐述。

在此系统之上实现了计算机串口与S DRAM 之间的相互通信。

实验结果表明系统功能可靠、实用。

经测试系统最大时钟频率可以达到761923MHz,F LAS H 的读写速率可达到111Mbs 。

与基于单片机配置的方法比较,高速安全的完成对FPG A 的上电配置。

关键词:FPG A,CP LD,F LAS H,串行配置中图分类号:T N43 文献标识码:BConf i gura ti on of FPGA and D esi gn of Its I n terface C i rcu itW ang L ingzhi L in Peijie Huang Chunhui(College of Physics and I nfor mati on Engineering of fuzhou university Fuzhou 350002,China )Abstract:The article intr oduces a configurati on method f or XC2S50FPG A,which is a me mber of Spartan Ⅱfa m ily fr om X I L I N X cor porati on .The configurati on method uses a serial syste m composed of CP LD&F LASH,and realizes data trans m itting and monit oring thr ough the parallel port of a computer .The circuit structure of the contr ol circuit and the s oft w are design are ex p lained .The interface bet w een S DRM and FPG A was designed,and mutual communicati on bet w een the serial port of the computer and S DRAM was realized .Experi m ent result indicates that the syste m functi ons stably and reliably and is p ractical;thr ough testing,the maxi m um syste m cl ock frequency rea 2ches t o 76.923MHz,the reading and writing s peed of F LASH reaches up t o 111Mbs .Compared with m icr ocon 2tr oller configurati on method,the p r oposed method can safely configure FP AG with high s peed during power on .Keyword:FPG A,CP LD ,F LASH,serial configurati on 1 FPG A /CP LD 既继承了ASI C 的大规模、高集成度、高可靠性的优点,又克服了普通ASI C 周期长、投资大、灵活性差的缺点,逐步成为复杂数字硬件电路的理想选择[1-2]。

FPGA-CPLD-开发流程

FPGA(CPLD)开发流程欢迎选用开发板精品网的FPGA/CPLD 开发板。

其结构简洁,功能丰富,一定是你开发、设计中的好帮手!下面我们采用一个流水灯的范例,带领大家进入神奇的FPGA 世界。

在这里,我主要讲解方法;关于具体的VHDL 语法,请大家参考我们提供的一些相关书籍!首先,启动QuartusII5.1 ,选择File Æ New Project Wizard ,如图:在New Project Wizard :Introduction 中,选择Next >NIOS II ÿÿÿÿ.pdf在Directory,Name,Top-Level Entity 中,添入您所需的参数,比如下例中,目录选择: C:\altera\qdesigns51\LED;项目名字选择:LED; Top-Level design entity选择:LED .完成后,选择Next,进入下一步。

在Add Files中,选择光盘目录下的LED.VHD完成后,选择Next,进入下一步。

在Family & Device Settings中选择 Family:Cyclone ;Available Devices 中选择合适你的器件,比如EPM7032SLC-44-10或者EPM7128SLC-84-10或者EP1C3T144C8或者EP1C6T144C8,在该例中,选择EP1C3T144C8 。

完成后,选择Next,进入下一步。

在EDA Tool Seting中选择合适你的配置,完成后,选择Next,进入下一步。

最后,选择Finish,完成设置。

然后,将光盘目录下的Setup.tcl拷贝到你的project目录下。

该Setup.tcl主要是完成pin 脚的设置。

使用TCL脚本的目的,是为了一次性分配引脚,节约人力啦;希望大家多多使用脚本!如下是Setup.tcl的内容,非常容易理解:# Setup.tcl# Setup pin settingset_global_assignment -name RESERVE_ALL_UNUSED_PINS "AS INPUT TRI-STATED"#set_global_assignment -name ENABLE_INIT_DONE_OUTPUT ONset_global_assignment -name CYCLONE_CONFIGURATION_DEVICE EPCS1set_location_assignment PIN_16 -to CLKset_location_assignment PIN_85 -to LED\[0\]set_location_assignment PIN_91 -to LED\[1\]set_location_assignment PIN_94 -to LED\[2\]set_location_assignment PIN_96 -to LED\[3\]set_location_assignment PIN_97 -to LED\[4\]set_location_assignment PIN_98 -to LED\[5\]set_location_assignment PIN_99 -to LED\[6\]set_location_assignment PIN_100 -to LED\[7\]set_location_assignment PIN_10 -to KEY\[0\]set_location_assignment PIN_11 -to KEY\[1\]set_location_assignment PIN_27 -to KEY\[2\]set_location_assignment PIN_28 -to KEY\[3\]set_location_assignment PIN_72 -to SDRAM_CSnset_location_assignment PIN_71 -to SDRAM_RASnset_location_assignment PIN_69 -to SDRAM_CASnset_location_assignment PIN_68 -to SDRAM_WEnset_location_assignment PIN_55 -to SDRAM_CKEset_location_assignment PIN_26 -to SDRAM_CLKset_location_assignment PIN_73 -to SDRAM_BANK\[0\] set_location_assignment PIN_74 -to SDRAM_BANK\[1\]set_location_assignment PIN_76 -to SDRAM_A\[0\]set_location_assignment PIN_77 -to SDRAM_A\[1\]set_location_assignment PIN_78 -to SDRAM_A\[2\]set_location_assignment PIN_79 -to SDRAM_A\[3\]set_location_assignment PIN_67 -to SDRAM_A\[4\]set_location_assignment PIN_62 -to SDRAM_A\[5\]set_location_assignment PIN_61 -to SDRAM_A\[6\]set_location_assignment PIN_60 -to SDRAM_A\[7\]set_location_assignment PIN_59 -to SDRAM_A\[8\]set_location_assignment PIN_58 -to SDRAM_A\[9\]set_location_assignment PIN_75 -to SDRAM_A\[10\] set_location_assignment PIN_56 -to SDRAM_A\[11\]set_location_assignment PIN_35 -to SDRAM_D\[0\]set_location_assignment PIN_36 -to SDRAM_D\[1\]set_location_assignment PIN_37 -to SDRAM_D\[2\]set_location_assignment PIN_38 -to SDRAM_D\[3\]set_location_assignment PIN_39 -to SDRAM_D\[4\]set_location_assignment PIN_40 -to SDRAM_D\[5\]set_location_assignment PIN_41 -to SDRAM_D\[6\]set_location_assignment PIN_42 -to SDRAM_D\[7\]set_location_assignment PIN_54 -to SDRAM_D\[8\]set_location_assignment PIN_52 -to SDRAM_D\[10\] set_location_assignment PIN_51 -to SDRAM_D\[11\] set_location_assignment PIN_50 -to SDRAM_D\[12\] set_location_assignment PIN_49 -to SDRAM_D\[13\] set_location_assignment PIN_48 -to SDRAM_D\[14\] set_location_assignment PIN_47 -to SDRAM_D\[15\]set_location_assignment PIN_57 -to SDRAM_DQM\[0\] set_location_assignment PIN_70 -to SDRAM_DQM\[1\]set_location_assignment PIN_104 -to ROM_CSnset_location_assignment PIN_105 -to ROM_REnset_location_assignment PIN_140 -to ROM_WEnset_location_assignment PIN_125 -to ROM_A\[0\]set_location_assignment PIN_103 -to ROM_A\[1\]set_location_assignment PIN_1 -to ROM_A\[2\]set_location_assignment PIN_2 -to ROM_A\[3\]set_location_assignment PIN_3 -to ROM_A\[4\]set_location_assignment PIN_4 -to ROM_A\[5\]set_location_assignment PIN_5 -to ROM_A\[6\]set_location_assignment PIN_144 -to ROM_A\[7\]set_location_assignment PIN_143 -to ROM_A\[8\]set_location_assignment PIN_134 -to ROM_A\[9\]set_location_assignment PIN_133 -to ROM_A\[10\]set_location_assignment PIN_132 -to ROM_A\[11\]set_location_assignment PIN_131 -to ROM_A\[12\]set_location_assignment PIN_130 -to ROM_A\[13\]set_location_assignment PIN_129 -to ROM_A\[14\]set_location_assignment PIN_128 -to ROM_A\[15\]set_location_assignment PIN_127 -to ROM_A\[16\]set_location_assignment PIN_126 -to ROM_A\[17\]set_location_assignment PIN_142 -to ROM_A\[18\]set_location_assignment PIN_141 -to ROM_A\[19\]set_location_assignment PIN_139 -to ROM_A\[20\]set_location_assignment PIN_106 -to ROM_D\[0\]set_location_assignment PIN_108 -to ROM_D\[1\]set_location_assignment PIN_110 -to ROM_D\[2\]set_location_assignment PIN_112 -to ROM_D\[3\]set_location_assignment PIN_114 -to ROM_D\[4\]set_location_assignment PIN_122 -to ROM_D\[6\]set_location_assignment PIN_124 -to ROM_D\[7\]set_location_assignment PIN_34 -to RXDset_location_assignment PIN_33 -to TXDset_location_assignment PIN_6 -to SCLset_location_assignment PIN_7 -to SDA#set_location_assignment PIN_83 -to SPI_DO#set_location_assignment PIN_84 -to SPI_CLK#set_location_assignment PIN_82 -to SPI_DIset_location_assignment PIN_83 -to VGA_Rset_location_assignment PIN_84 -to VGA_Gset_location_assignment PIN_82 -to VGA_Bset_location_assignment PIN_31 -to VGA_HSset_location_assignment PIN_32 -to VGA_VS然后,选择Tools Æ Tcl Scripts这时,会弹出Tcl Scripts对话框。

基于CPLD实现FPGA的SPI Flash配置

基于CPLD实现FPGA的SPI Flash配置在FPGA设计中,通常需要将配置数据存储在外部闪存器中,以便FPGA在上电后可以正确配置。

常用的文化遗产具有以下几种:Parallel Flash:传统的存储器,通常包含16至32位数据总线,需要大量引脚。

但是,它们提供高性能,可以以快速的速度读写数据。

Serial Flash:通常采用SPI(串行外设接口)或QSPI(准同步串行通信接口)接口进行通信,可使用少量引脚,并且内部积累了大量闪存技术。

在此示例应用中,我们将使用CPLD实现FPGA的SPI Flash配置。

SPI Flash框图SPI Flash与FPGA之间的接口非常简单,只需要四个信号,分别是“Chip Select”(选通)、“Clock”(时钟)、“MOSI”(主机输出/从机输入)和“MISO”(从机输出/主机输入)。

FPGA需要传输的读写命令和地址,以及从Flash接收的数据。

因此,与Flash通信的协议非常重要。

常见的协议是“读”和“写”命令序列,以及擦除和编程命令。

操作步骤1. 将SPI Flash的“Chip Select”(CS)引脚连接到FPGA中的任意引脚。

2. 将SPI Flash的“Clock”(CLK)引脚连接到FPGA中的任意引脚。

3. 将SPI Flash的“MOSI”(主机输出/从机输入)引脚连接到FPGA中的任意引脚。

4. 将SPI Flash的“MISO”(从机输出/主机输入)引脚连接到FPGA中的任意引脚。

5. 在FPGA制作的SPI硬核中,设置针脚分配。

如果您使用芯片设计工具,可以使用默认分配。

6. 实现SPI驱动程序以处理读写和闪存操作。

7. 要将配置数据加载到闪存中,首先需要在计算机上生成.bin 文件。

可以使用Xilinx编译器进行编译。

8. 在闪存中使用适当的FLASH编程工具将.bin文件加载到闪存中。

9. FPGA在上电后会读取配置信息,完成初始化并开始操作。

CPLD-FPGA设计流程

设计输入

module paobiao( clk, reset, pause, ms_h, ms_l, s_h, s_l, m_h, m_l

); input output[3:0] clk,reset,pause; ms_h,ms_l,s_h,s_l,m_h,m_l;原理图来自入 Verilog/VHDL 输入

仿真波形

电路综合

Verilog/VHDL 原理图

门级网表 Synthesize

门级网表是利用厂商提 供的器件库生成的, 由与、或、非、寄 存器等基本逻辑单 元组成的连接关系

该网表可以用来进 行门级前仿真, 更重要的是还 可以用来后端 布局布线

综合之后的部分原理图

布局布线

• 布局:将综合输出的逻辑网表适配到 布局: 具体FPGA FPGA器件的物理单元上 具体FPGA器件的物理单元上 • 布线:实现FPGA器件元件之间的互连 布线:实现FPGA FPGA器件元件之间的互连

布局布线之后的电路图

CLB的结构

IOB的结构

Bit文件生成、加载、 Bit文件生成、加载、系统调试 文件生成

CPLD/FPGA设计流程 设计流程

温国忠

主要内容

• 以数字跑表为例介绍 以数字跑表为例介绍CPLD/FPGA设计 设计 的主要流程 • FPGA及其设计优点 及其设计优点

FPGA设计流程示意图

产品需求 FPGA规格 设计方案 设计输入 功能仿真 电路综合 门级前仿真 布局布线 bit文件生成及加载 FPGA系统测试 设计修改

设计方案

跑表模块

pause ms_h

百分秒 计数器

flag1 clk

ms_l

s_h

秒计数器

flag2 reset

基于FPGA实现的高速串口传输技术与实现

(5)将配置位流文件下载到FPGA芯片中,进行实际运行和测试。

4、结论

本次演示设计和实现了一种基于FPGA的以太网和串口数据传输系统,实现了 高速、高效的数据传输和共享。本系统的优点在于具有高度的灵活性和可扩展性, 可以方便地根据实际需要进行功能扩展和优化。由于采用了FPGA技术,本系统还 具有体积小、功耗低、可靠性高等优点,可以广泛应用于各种嵌入式系统和智能 设备中。

为了更好地实现基于FPGA的高速光纤通信数据传输技术,需要以下几个方面:

1.优化硬件设计:根据具体的应用场景和需求,选择合适的FPGA芯片和硬件 组件,并对其进行优化设计,以实现更高效的数据传输和处理。

2.完善软件算法:利用FPGA的并行处理能力和数字信号处理算法,进一步完 善软件算法,提高数据处理速度和可靠性。

最后,为了提高稳定性和可靠性,可以研究更为高效的错误检测和纠正算法, 以及研究如何提高数据传输的鲁棒性。

总结

本次演示介绍了基于FPGA实现的高速串口传输技术与实现。通过利用FPGA的 灵活性和高效性,我们成功地实现了高速串口传输技术,并在速度测试中验证了 其优势。然而,也需要注意到这种技术存在的不足和挑战。未来,高速串口传输 技术将会朝着更高速度、更低成本、更稳定可靠的方向发展。

参考内容

随着信息时代的到来,数据传输的速度和可靠性成为了关键的要素。光纤通 信作为一种现代化的数据传输方式,具有传输速度快、容量大、抗干扰能力强等 优点,被广泛应用于各个领域。为了进一步提升光纤通信的性能,基于FPGA(现 场可编程门阵列)的高速光纤通信数据传输技术得到了广泛的研究与实现。

FPGA是一种高度灵活的芯片,可以由用户进行编程配置,实现各种不同的逻 辑功能。在光纤通信领域,FPGA可以被用于实现数据编解码、信号调制解调、误 码纠正等功能,从而提升数据传输的速度和可靠性。

CPLD烧写方法 FPGA,CPLD,烧写,烧录,测试

CPLD烧写步骤

一、前期准备:

1、要烧写的CPLD程序

2、电脑以及相关软件以及下载器驱动(默认自动安装)。

3、下载工具以及连接线

二、连线方式:通过连接线连接下载器和J2接口,连接的时候注意1口对1口连接,连接错误将导致无法下载。

左图中三角号对应的是1脚,连接图示下载器1脚,另一端连接P3的1脚,下载器另一端连接到笔记本的usb接口上。

下载线以及下载器

接口示意图

下面是连接后的示意图

连接示意图

三、下载方法

连好线后,打开XILINX工具软件,默认在开始-所有程序菜单里,如下图

xilinx打开路径图

点击文件-新建工程

然后会弹出一个对话框,这时候点yes,然后点ok。

下面添加烧写的程序,在空白处右击,选择如图示

然后选择要烧写的jed程序

选择后,在添加的程序上右击,选择programmer进行烧写。

等待提示success。

如果failed请检查连线是否松动尝试重复烧写几次。

可编程逻辑器件CPLD和FPGA的特点和应用

可编程逻辑器件CPLD和FPGA的特点和应用作者:田生宏,田培成来源:《科技视界》 2015年第18期田生宏田培成(西安理工大学高等技术学院,陕西西安 710082)【摘要】在可编程逻辑器件的发展过程中,不同厂家对新型PLD器件的叫法不尽相同,对CPLD和FPGA的分类标准也有差异,这样给使用和选择带来了不便甚至困惑,本文按一般的分类方法,分别介绍这两种可编程逻辑器件各自的特点,以期给使用者以帮助。

【关键词】可编程器件;PLD;CPLD;FPGA;硬件描述语言VHDL目前,大量使用的可编程逻辑器件是CPLD和FPGA,产品种类很多,均可实现任何数字逻辑功能。

设计者可以利用CPLD和FPGA,通过原理图输入法或硬件描述语言设计一个数字系统,使之完成特定的功能,并且能运用软件仿真的方法来验证设计的正确性。

CPLD和FPGA用于开发数字逻辑电路,可以缩短设计时间,减少集成电路数目和降低成本,极大地提高系统的可靠性。

近年来,诞生了一些新型的CPLD和FPGA器件,集成度高,可以替代几十甚至几千块通用IC芯片,其单片逻辑门数已达到上百万门,可实现的逻辑功能也越来越强。

在可编程逻辑器件的发展过程中,不同厂家对新型PLD器件的叫法不尽相同,对CPLD和FPGA的分类标准也有差异,人们通常把基于乘积项技术和EEPROM工艺或Flash Memory工艺的器件称为CPLD,把基于查找表技术和SRAM工艺的器件称为FPGA(也有些资料将这两种器件都称为CPLD或都称为FPGA)。

这样给使用和选择带来了不便甚至困惑,本文按一般的分类方法,分别介绍这两种可编程逻辑器件各自的特点,以期给使用者以帮助。

1 复杂可编程逻辑器件CPLDCPLD是从SPLD发展而来的高密度PLD产品,目前CPLD的产品种类繁多,各具特色,但其构成基本相同。

如图1所示为CPLD的结构示意图,它由若干个逻辑阵列块(LAB)、可编程互连阵列(PIA)和可编程的输入/输出模块(IOB)组成。

在CPLD管理下实现高效多串口中断源

在CPLD管理下实现高效多串口中断源在CPLD管理下实现高效多串口中断源摘要:针对嵌入式系统的精简特性,提出一种通过1个中断源高效管理多个串行口的有效方法,不但节省系统资源,而且实现了多个串行口中断的无漏检测与服务。

关键词:嵌入式系统RS232多串口CPLD中断近几年来,随着后PC时代的来临,具有简洁、高效等特点的嵌入式系统得到了飞速的发展。

嵌入式技术发展到今天已将各种计算机技术多层次、多方面的交叉融合在了一起。

嵌入式系统加快了工业设计进程,降低了开发成本及其风险,使用简便,扩展灵活,高效精简,可方便地应用于各工业领域。

中断请求采用边沿触发来进行中断检测,通过将信号送到特定的引线来检测中断。

每条引线对应一个可能的硬件中断,因为系统不能辨认哪个设备使用中断线,所以当多个1个的设备被设置成使用同一个特定中断时就产生了混乱。

中断产生时,由专用的中断程序接管系统,首先把所有的CPU 寄存器内容保存到堆栈里,并引导系统指向中断向量表。

在中断程序执行后的一段时间中,中断控制软件把堆栈内容返回给寄存器,系统恢复中断发生之前的状态。

如此段时间中又有中断请求,将造成中断的设备判断混乱,从而会造成中断冲突、丢失,甚至使得设置无法正常工作。

因此,每个中断通常被分配给单一的设备,使中断无法共享。

传统方法中,扩展多个串行口是利用多个中断源;但在嵌入式系统中,花费大量的中断源来扩展串口无疑是大量的资源浪费。

针对这种情况,为了节省紧张的系统资源,本文提出一种实现高效多串口中断方案,可以利用单一的中断源来管理多个扩展串口,并保证多个串口中断的无漏检测与服务。

1总体设计方案基本原理结构如图1所示。

RS232串口通过驱动芯片MAX202转换成TTL电平,通过串口异步通信器件16C554输出中断请求,通过或门获得多个串口的中断请求INTREQ,再通过CPLD与中断控制器相连接。

中断线INTREQ通过CPLD主要是在CPLD中做了一个1位的控制寄存器INTEN,用作中断允许控制位,并且根据16C554的中断请求INTREQ和INTEN的状态来最终生成DLY_IRQ,向CPU发出请求。

2.5.125FPGA与CPLD的编程与配置

FPGA/CPLD的编程与配置

该模式可以实现对FPGA在线可编程,升级方便。

用单片机进行配置

谢谢观看

5

FPGA/CPLD的编程与配置

在系统编程技术

CPLD编程

FPGA配置

总结

在系统编程ISP:指电路板上的空白器件可以编程写入最终用户代码, 而不需要从电路板上取下器件,已经编程的器件也可以用ISP方式擦除或再编程。

FPGA/CPLD的编程与配置

一、在系统编程ISP(In-System Programming)

1、JTAG模式使用JTAG将SRAM配置文件(.sof)配置到FPGA芯片中。

FPGA/CPLD的编程与配置

JTAG在线配置FPGA原理图

常用有如下三种模式:JTAG模式。AS(active serial,主动串行)模式。PS(passive serial,被动串行)模式。

在FPGA芯片外部放置EPCS等配置芯片 ,存储设计好的电 路固件。每次上电 ,FPGA主动读取配置芯片中的固件,并配置到FPGA芯片的每一个 SRAM中去。

标准JTAG接口:TCK——时钟输入;TDI——数据输入;TDO——数据输出;TMS——测试模式选择。

可选引脚TRST——测试复位,输入引脚,低电平有效。JTAG内部有一个状态机,称为TAP控制器。

三、FPGA配置FPGA采用SRAM工艺,配置在掉电后丢失,因此,有多种配置模式。模式选择引脚:FPGA上的MSEL。

优点:使硬件随时能够改变组态。

编程(Program): CPLD的在系统下载。配置(Configure):FPGA的在系统下载。

FPGA/CPLD的编程与配置

FPGA与CPLD设计流程

FPGA与CPLD设计流程FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)是现代数字电路设计中常用的可编程逻辑器件。

它们具有配置灵活、可重构的特点,使得数字电路的设计和开发更加高效和便捷。

本文将介绍FPGA与CPLD的设计流程,并探讨在设计过程中需要注意的一些关键要点。

一、设计前准备在进行FPGA与CPLD设计之前,我们首先需要明确设计的目标和需求,包括功能需求、性能需求和接口需求等。

同时,根据设计的规模和复杂性,确定所需的FPGA或CPLD器件型号,以及需要采用的开发工具和设计语言。

二、设计框架搭建在设计框架搭建阶段,我们需要创建一个新的工程,并选择适当的开发平台和工具。

根据设计需求,将逻辑功能进行划分,确定模块间的接口和数据交互方式。

同时,选择合适的开发语言,如Verilog或VHDL,开始进行设计代码的编写。

三、模块设计与验证在模块设计与验证阶段,我们需要将整个设计划分为多个模块,并逐个进行设计和验证。

每个模块都应该具备独立的功能,并能够与其他模块进行正确的数据交互。

设计人员可以使用仿真工具对每个模块进行功能验证,并通过调试和测试来保证模块的正确性。

四、综合与优化在综合与优化阶段,我们需要使用合成工具将设计代码转换为逻辑网表。

综合工具会将设计代码翻译成与目标FPGA或CPLD器件兼容的逻辑门级表示,并进行优化以提高设计的性能和面积效率。

在这个阶段,设计人员还需根据目标平台的资源限制进行约束设置,以确保设计在合理的范围内。

五、布局布线与时序分析在布局布线与时序分析阶段,我们需要将逻辑网表映射到目标FPGA或CPLD器件的物理资源上,并进行物理布局和布线。

同时,进行时序分析来保证设计在时钟频率和时序要求下能够正常工作。

此外,设计人员还需要注意信号的噪声抑制和时钟域的管理,以确保设计的可靠性和稳定性。

用CPLD实现同步串口转异步串口

用CPLD实现同步串口转异步串口

王绍翾;赵焕军;张林;罗军辉

【期刊名称】《电子元器件应用》

【年(卷),期】2002(4)12

【摘要】针对同步设备与异步设备之间进行串行通信时经常存在的转换问题,提出一种采用复杂可编程逻辑器件(CPLD)实现的解决方法,并详细介绍了具体实现过程,通过实践证明,该方法灵活方便,可靠性高,可以满足一般工程应用的要求.

【总页数】2页(P13-14)

【作者】王绍翾;赵焕军;张林;罗军辉

【作者单位】北京大学电子学系,北京,100871;西安电子科技大学电子工程学院,陕西,西安,710071;西安电子科技大学电子工程学院,陕西,西安,710071;西安电子科技大学电子工程学院,陕西,西安,710071

【正文语种】中文

【中图分类】TN409

【相关文献】

1.用CPLD实现同步串口与异步串口的转换 [J], 简思平;周学才;张基宏

2.基于DSP同步串口的异步串行通信接口的设计与实现 [J], 杨剑;贾冲;杨吉斌

3.基于CPLD实现ISA总线异步串口扩展 [J], 刘思慧;陈华明;欧钢

4.基于CPLD的同步/异步串口转换的实现 [J], 商丹;高永清

5.用FPGA实现异步串口与同步串口的转换 [J], 李文亮;姚冬苹

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

if(!rst)

key_entry1<=0;

else begin

if(key_entry2)

key_entry1<=0;

else if(cnt_delay==20'd800000) begin

if(!key_input)

key_entry1<=1;

////////////////////////////////////////////////

parameter div_par=16'h145;//分频参数,其值由对应的波特率计算而得,按此参数分频的时钟频率是波倍特率的8

//倍,此处值对应9600的波特率,即分频出的时钟频率是9600*8 (CLK 50M)

reg trasstart;//开始接受标志

reg rxd_reg1;//接收寄存器1

reg rxd_reg2;//接收寄存器2,因为接收数据为异步信号,故用两级缓存

reg txd_reg;//发送寄存器

reg[7:0] rxd_buf;//接受数据缓存

reg[7:0] txd_buf;//发送数据缓存

cnt_delay<=0;

start_delaycnt<=0;

end

end

else begin

if(!key_input&&cnt_delay==0)

start_delaycnt<=1;

end

end

always@(posedge clk)

reg[2:0] send_state;//每次按键给PC发送"Welcome"字符串,这是发送状态寄存器

reg[19:0] cnt_delay;//延时去抖计数器

reg start_delaycnt;//开始延时计数标志

reg key_entry1,key_entry2;//确定有键按下标志

begin

if(!rst)

div8_rec_reg<=0;

else if(recstart)//接收开始标志

div8_rec_reg<=div8_rec_reg+1;//接收开始后,时隙数在8倍波特率的时钟下加1循环

end

always@(posedge clkbaud8x or negedge rst)

reg clkbaud_tras;//以波特率为频率的发送使能信号

reg clkbaud_rec;//以波特率为频率的接受使能信号

reg clkbaud8x;//以8倍波特率为频率的时钟,它的作用是将发送或接受一个bit的时钟周期分为8个时隙

reg recstart;//开始发送标志

reg recstart_tmp;

if(clkbaud_tras) begin

txd_reg<=0;

state_tras<=state_tras+1;

end

end

else begin

key_entry2<=0;

state_tras<=0;

end

end

4'b0010: begin //发送第2位

if(clkbaud_tras) begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

end

end

4'b1000: begin //发送第8位

if(clkbaud_tras) begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

clkbaud_rec=1;//在第7个时隙,接收使能信号有效,将数据打入

else

clkbaud_rec=0;

end

always@(div8_tras_reg)

begin

if(div8_tras_reg==7)

clkbaud_tras=1;//在第7个时隙,发送使能信号有效,将数据发出

cnt_delay<=0;

start_delaycnt<=0;

end

else if(start_delaycnt) begin

if(cnt_delay!=20'd800000) begin

cnt_delay<=cnt_delay+1;

end

else begin

else

clkbaud_tras=0;

end

always@(posedge clkbaud8x or negedge rst)

begin

if(!rst) begin

txd_reg<=1;

trasstart<=0;

txd_buf<=0;

state_tras<=0;

end

end

4'b1001: begin //发送停止位

if(clkbaud_tras) begin

txd_reg<=1;

txd_buf<=8'h55;

end

else begin

case(state_tras)

4'b0000: begin //发送起始位

if(!trasstart&&send_state<7)

trasstart<=1;

else if(send_state<7) begin

end

end

always@(posedge clk)//分频得到8倍波特率的时钟

begin

if(!rst)

clkbaud8x<=0;

else if(div_reg==div_8x;

end

always@(posedge clkbaud8x or negedge rst)

////////////////////////////////////////////////

assign txd=txd_reg;

assign lowbit=0;

assign en=0;//7段数码管使能信号赋值

always@(posedge clk )

begin

if(!rst) begin

*/

module chuankou(clk,rst,rxd,txd,en,seg_data,key_input,lowbit);

input clk,rst;

input rxd;//串行数据接收端

input key_input;//按键输入

output[7:0] en;

output[7:0] seg_data;

/*

本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在PC机上安装一个串口调试工具来验证程序的功能。

程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控制器,10个bit是1位起始位,8个数据位,1个结束位。

串口的波特律由程序中定义的div_par参数决定,更改该参数可以实现相应的波特率。程序当前设定的div_par 的值

end

end

4'b0110: begin //发送第6位

if(clkbaud_tras) begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

reg[7:0] seg_data;

output txd;//串行数据发送端

output lowbit;

////////////////////inner reg////////////////////

reg[15:0] div_reg;//分频计数器,分频值由波特率决定。分频后得到频率8倍波特率的时钟

begin

if(!rst)

div8_tras_reg<=0;

else if(trasstart)

div8_tras_reg<=div8_tras_reg+1;//发送开始后,时隙数在8倍波特率的时钟下加1循环

end

always@(div8_rec_reg)

begin

if(div8_rec_reg==7)

end

end

4'b0001: begin //发送第1位

if(clkbaud_tras) begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

end

end

4'b0011: begin //发送第3位

if(clkbaud_tras) begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

end

end

4'b0111: begin //发送第7位

if(clkbaud_tras) begin