cadence指导详细版_

cadence教程

cadence教程Cadence 是一款流行的电路设计和仿真工具。

它广泛应用于电子工程领域,可以帮助工程师进行电路设计、布局、仿真和验证。

以下是一个简单的 Cadence 教程,帮助你快速入门使用该软件。

第一步: 下载和安装 Cadence首先,你需要从 Cadence 官方网站下载适用于你操作系统的Cadence 软件安装包。

在下载完成后,双击安装包文件并按照安装向导的指示进行安装。

第二步: 创建新项目打开 Cadence 软件后,你将看到一个初始界面。

点击“File”菜单,然后选择“New”来创建一个新的项目。

第三步: 添加电路元件在新项目中,你可以开始添加电路元件。

点击菜单栏上的“Library”按钮,然后选择“Add Library”来添加一个元件库。

接下来,使用菜单栏上的“Place”按钮来添加所需的电路元件。

第四步: 连接电路元件一旦添加了电路元件,你需要使用连线工具来连接它们。

点击菜单栏上的“Place Wire”按钮,然后将鼠标指针移到一个元件的引脚上。

点击引脚,然后按照电路的设计布局开始连接其他元件。

第五步: 设置仿真参数在完成电路布局后,你需要设置仿真参数。

点击菜单栏上的“Simulate”按钮,然后选择“Configure”来设置仿真器类型、仿真时间等参数。

第六步: 运行仿真设置完成后,你可以点击菜单栏上的“Simulate”按钮,然后选择“Run”来运行仿真。

仿真过程会模拟电路的运行情况,并生成相应的结果。

总结通过这个简单的 Cadence 教程,你了解了如何下载安装Cadence 软件、创建新项目、添加电路元件、连接元件、设置仿真参数和运行仿真。

掌握了这些基本操作后,你可以进一步学习和探索 Cadence 的更多功能和高级技巧。

祝你在使用Cadence 中取得成功!。

CadenceAllegro16.5详细教程ppt课件

Load logic data

Manufacturin g outputs check plots aperture files Gerber data NC drill data silkscreens Assembly drawings fabrications drawings reports Autorename backannotatio n

4

主要产品介绍

为了适应不同用户的需要,Cadence软件包中提供了Allegro PCB

Designer、OrCAD PCB Designer Standard和OrCAD PCB Designer Professional 3种PCB设计软件版本。 (1)Allegro PCB Designer:是应用最广泛的一种版本。产品由Base模 块和Option附加模块组成,通过一个完全集成式的设计流程进行PCB Layout设计。 (2)OrCAD PCB Designer:分为Professional和Standard版本,与 Allegro PCB Designer相比,不具有电气约束驱动规则( Professional 版本只有差分约束规则)、DFX检查、不允许修改电气拓扑结构、没 有扩展的Option功能、自动布线器最多支持到6层。

2

Lesson1 Allegro 环境介绍

学习要点: PCB Layout流程介绍 PCB设计主要产品介绍 工作界面介绍 视窗缩放控制介绍 鼠标Stroke功能介绍 主要文件类型

3

PCB Layout流程

HDL/schemat ic design capture Define board mechanical stackup Set/check CBD rules and constraints

cadence指导详细版

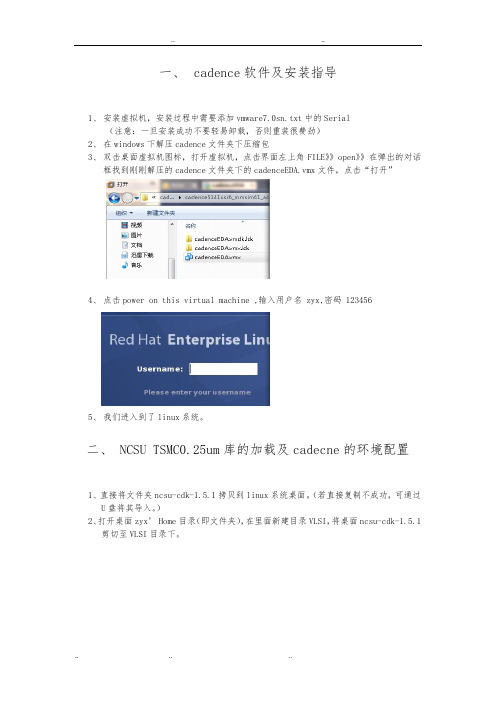

cadence指导详细版⼀、cadence软件及安装指导1、安装虚拟机,安装过程中需要添加中的Serial(注意:⼀旦安装成功不要轻易卸载,否则重装很费劲)2、在windows下解压cadence⽂件夹下压缩包3、双击桌⾯虚拟机图标,打开虚拟机,点击界⾯左上⾓FILE》》open》》在弹出的对话框内找到刚刚解压的cadence⽂件夹下的⽂件,点击“打开”4、点击power on this virtual machine ,输⼊⽤户名 zyx,密码 1234565、我们进⼊到了linux系统。

⼆、 NCSU 库的加载及cadecne的环境配置1、直接将⽂件夹ncsu-cdk-1.5.1拷贝到linux系统桌⾯。

(若直接复制不成功,可通过U盘将其导⼊。

)2、打开桌⾯zyx’Home⽬录(即⽂件夹),在⾥⾯新建⽬录VLSI,将桌⾯ncsu-cdk-1.5.1剪切⾄VLSI⽬录下。

3、在桌⾯空⽩处单击⿏标右键,点击open Teminal4、在终端内输⼊以下命令。

1、 su root -------进⼊到超级⽤户2、 sunface8211200 (不可见,直接输⼊即可)3、 chmod a+w ------修改权限后,可以对其进⾏编写4、 vi --------进⼊到vi 编辑器,单击键盘“ i ”进⼊到插⼊模式,在第⼀⾏我们添加⼀⾏语句。

INCLUDE /home/zyx/VLSI/ncsu-cdk-1.5.1/cdssetup/输⼊完之后,单击键盘“esc”键退出插⼊模式,再点击键盘“:wq ”退出vi编辑器5、cd VLSI/ncsu-cdk-1.5.1/cdssetup ---------进⼊到cdssetup⽬录6、 vi --------做如下图修改后,点击esc键并输⼊“:wq ”退出7、csh -------进⼊到c shell命令8、vi /home/zyx/.cshrc ------进⼊到⽤户⽬录下的 .cshrc的编写,并添加如下语句setenv CDK_DIR /home/zyx/VLSI/ncsu-cdk-1.5.1 ,添加后“:wq ”保存退出9、cp cdsinit /home/zyx/.cdsinit10、cp /home/zyx/11、⾄此,⼯艺库安装完毕,cadence环境配置也已经结束。

cadence教程

Cadence TutorialI. IntroductionThis tutorial provides an introduction to analog circuit design and simulation with Cadence, and covers the features that are relevant for the homework assignments. The tutorial is divided into the following topics:•Logging on and Starting Cadence•Creating a Designo Creating a new library and cellviewo Placing the Partso Editing the Symbol Propertieso Wiring the Schematico Modifying Wire Attributes•Analyzing the Design and Plotting Resultso Finding the DC Operating Point and performing a DC Sweepo Performing a Transient Analysiso Performing an AC Analysiso Performing a Parametric Sweepo A Note on Measuring Currentso A Note on Plotting•Invoking Cadence Helpo Getting Additional Help with CadenceThroughout the document, the followingII. Logging on and Starting CadenceIn order to use the ECE164-provided installation of Cadence, you either need to be sitting at one of the Linux workstations provided for use by ECE264 students (see the ECE264 website for the locations of these workstations), or you can login remotely to . In either case, you should login with your Open Computing Environment account obtained via Academic Computing Services (ACS).If you wish to login remotely, you will need SSH and X-server software on your local machine. The necessary software is available as part of the operating systems on Sun Workstations, PCs running Linux, and Macintosh computers running OS X. It can be obtained via third parties for computers running Windows. Students who wish to login remotely are responsible for obtaining (if running Windows), learning how to use, and maintaining their own SSH and X-server software.Once you have logged in, open a terminal window if one does not open automatically and type the following in the window:ee264acd ece-cadenceicfb &A window containing text should appear at the bottom of the screen, labeled “icfb - ...”. This is sometimes called the CIW (Command Interpreter Window). A window explaining new features should also come up; in this window, select “Edit > Off at Startup”, and then close it. The CIW window is the main Cadence window, and much useful information is displayed here. If Cadence isn’t doing what you expect, it is often helpful to look here to read the error messages. You may find it helpful to enlarge the window.You now need to bring up the library manager. To do this, select “Tools > Library Manager” in the CIW. A “Library Manager” window appears. Notice the library “ece264lib”.This library contains most if not all of the IC components (e.g., transistors, resistors, etc.) that will be used in this class.II.Creating a DesignThe creation of a simple transistor amplifier is described in this section. The following notational conventions are used in the description:•The text “[LIB]” should be replaced with “164” if you are taking ECE164 and by “264” if you are taking ECE264.•Bracketed letters such as “[a]” denote keyboard shortcuts (bindkeys) which can be used instead of the menus or buttons to accomplish the given task. To use them, place the pointer over the appropriate window and simply press the key. Please note that these bindkeys are case sensitive.For letters enclosed by square brackets such as “[a]”, the pointer must be in a schematic window.For letters enclosed by curly brackets such as “{a}”, the pointer must be in a waveform window. A summary of the most useful bindkeys is listed in Appendix A.Creating a new library and cellview1.Create a new library named “tutorial”:(a)In the CIW, select “File > New > Library”, and a “New Library” windowwill appear.(b)In the “Name” field, enter “tutorial”.(c)Verify that the path (near the bottom of the dialog box) points to your working directory(or wherever you’d like to place all your class libraries). This path will by default pointto the directory from which you invoked Cadence(d)Select the “Don't need a techfile” button, then click “OK”. In the LibraryManager, an entry “tutorial” should appear.2.Create a new schematic cellview in our new library.(a)In the CIW, select “File > New > Cellview...”, and a “Create New File”dialog box appears.(b)Ensure that the “tutorial” is selected for Library Name (by clicking on the squarebutton).Type “tutorial” in the “Cell Name” field as well.(c) Type “schematic” in the “View Name” field.(d)Select “Composer - Schematic” in the “Tool” field if it is not already selected,then click “OK”. An empty schematic window appears.(e)In the schematic window, select “Design > Save”. You have now successfullycreated a cellview.Placing the PartsYou will now place symbols on the Schematic Window as shown in Figure 1.Figure 1: Initial parts placement.1.Find and place the pMOST symbol as follows:(a)With the schematic window active, press “i” on the keyboard. An “Add Instance”dialog box will appear. The “i” key is a bindkey, or shortcut key, to this dialog box.You can also get the same dialog box by click on the “Instance” button on the lefthand side of the schematic window (it looks like a little DIP), or by going to “Add >Instance” in the menu bar (there is an “i” next to this menu selection, notice). Thereare many shortcuts like this throughout Cadence, and you can create more if you wish -see the online help. Note also that at the bottom of the schematic window and the CIW,the instructions “Point at location for the instance” appears, along withinformation about what the mouse buttons do: “mouse L: ...”. It’s often importantto look at these messages to figure out what is going to happen when you press theleft/middle/right mouse buttons. The mouse buttons are bound to Skill functions, but canbe reconfigured - see the online help for more details.(b)In the dialog box Library field, enter “ece[LIB]lib”. For Cell, enter “pmos4”. ForView, enter “symbol”. You can also use the Browse button to invoke the LibraryBrowser to find a part.(c)When you move the mouse over the schematic window, you will see the outline of a 4-terminal pMOST. Move the cursor to the desired location and press the left mousebutton. Repeat for the other pMOST transistor.(d)To stop placing pMOST symbols, press “ESC” on the keyboard (with the SchematicWindow active), or click the “Cancel” button in the Add Instance dialog box.2.Place an nMOST using a similar procedure. This time, try using the Library Browser to place the“nmos4” symbol. Position it relative to the pMOST symbols as shown in Figure 1, then press “ESC” to get rid of the Add Instance window.3.Next, place the DC Current Source symbol as follows:(a)Press “i” as before, then click “Browse” to bring up the Library Browser.(b)Select “ece[LIB]lib” in the Browser library list, then find the “idc” componentsymbol using the scroll bar. Highlight this component in the browser by left-clicking on“idc”. Sometimes you may need to specify that you want to place the “symbol”version of this part.(c)Move the mouse over the schematic window and place it in the desired location. Don’tpress “ESC” yet.4.Go back to the Library Browser and find the “vdc” part. Place it.5.Similarly, place the “vsin”, “res”, and five copies of “gnd”. Finally, press “ESC” (remember,the Schematic Window must be active) to stop placing parts.6.If you need to move any of the parts, use the following procedure:(a)Press “M” (stretch) or “m” (move). Note the message at the bottom of the SchematicWindow. At this point, there is no difference between these two commands. But whenwires are attached to the parts, “M” will move the wires as well, whereas “m” will justmove the part.(b)Click on the part you wish to move. Again, keep an eye on the bottom of the SchematicWindow. Follow the instructions there. Repeat as needed.(c)Note that you can also move items by moving the cursor over the item, pressing andholding the left mouse button, moving the mouse, and then releasing the mouse button.Editing the Symbol PropertiesOnce all the parts are placed on the schematic, you can set property values that are specific to the design on each symbol. Figure 2 shows many of the property values that you will add in this part of the tutorial. The “vsin” symbol has many properties: “acm” is “AC Magnitude”, the amplitude of the AC signal applied to the linearized circuit (small signal circuit) during an AC Analysis. The “acp” is the “AC Phase”, “vo” refers to “DC Offset”, and “vm” refers to “Amplitude”, the amplitude of the signal applied to the large-signal (non-linear) circuit during a Transient Analysis.Figure 2: Symbol property values.e the following procedure to change a symbol’s properties. Before you begin, make sure thatyou have pressed ESC to clear the last action performed (the bottom line of the Schematic Window should read “>”):(a) Move the cursor to a location where there are no parts. Then press “q”. An “EditObject Properties” dialog box will appear.(b)Click on the item whose properties you’d like to change. The dialog box will expand todisplay a list of properties that can be changed. If you can’t see any properties, makesure thatthe “CDF” box is checked near the top of the “Edit Object Properties”window.(c)In the list of properties, edit those that you would like to change or specify. DO NOTinclude units such as “Volts” or “Ohms” - you’ll notice that these are filled inautomatically after you move on to the next property. DO NOT press return after youenter a property - use the mouse or use the “TAB” key to proceed. DO specifyabbreviations for scientific notation such as “k” (kilo),”u” (micro), “m” (milli), “M”(mega), “p” (pico), “f” (femto).(d)Click on the next part to change its properties. Cadence will ask whether you want tosave the property changes from the old part - say yes.(e)When you’re done entering properties, click “Cancel” at the top of the “EditObject Properties” dialog box.2. Change the names of the transistors according to Figure 2 by changing the “Instancename” field. Note: The name must be unique. Also insert the values for the transistor widthsand lengths.3.Flip the display of transistor M0 by first pressing “m” and clicking on the transistor to move it.While you are “holding” it, press “R” on the keyboard. The symbol outline should flip. Place theflipped part as shown in Figure 2.4.Note that the ac magnitude and phase of the “vsin” part are not displayed by default. Edit theproperties of this part (with the “q” key, and then look at the “AC Magnitude” property. Clickon the button to the right of the property value, and a list of choices will appear. Select “Both”.This will cause this property to be displayed on the schematic.Wiring the SchematicAfter the symbols are placed and the properties are set, you can wire the parts together as shownin Figure 3 by doing the following:1.One way to create a wire between two ports is as follows:(a)Position the mouse cursor over the first port (for example, start with the top of theconstant voltage source).(b)Click and hold the left mouse button.(c)Position the mouse cursor over the second port (the Vdd symbol above the Vdc symbol).(d)Release the left mouse button.(e)Repeat steps a through d to connect each Ground and Vdd symbol to the associatedparts, as shown in Figure 3.2. To connect the Gate terminals of the pMOSTs to the Drain terminal of M1, do the following:(a)Press “w” on the keyboard. Note the instructions at the bottom of the SchematicWindow.(b)Click and hold the left mouse button.(c)Position the cursor over the mid-point of the wire between the Gate terminals of M1 andM2, and click the left mouse button.(d)Move the mouse cursor four grid-points down, and click the left mouse button.(e)Move the mouse cursor six grid-points to the left, and click the left mouse button. Thiscompletes the connection.plete the remaining wire connections as shown in Figure 3.Figure 3: Schematic Wire Connections.Modifying Wire AttributesIf you do not label wires, Cadence automatically provides names for each wire, such as “net30”. It can be helpful later on during design and analysis if you label the wires with meaningful designators that are easy to understand and refer to. To add the attribute “vout” to the wire shown in Figure 3, do the following:1. Press “l” (for label) on the keyboard. An “Add Wire Name” dialog box appears.2.Enter “vout vin” in the “Names” field and press “Return”3.Move the cursor until the dot is on top of the wire to be labeled “vout”. Left click once with themouse. The label will be attached to the wire, and the label you are moving with your cursor changes.4.Place the “vin” label in an appropriate spot. Make sure the dot is on top of the wire before youleft-click.Finally, add a single instance of “ece[LIB]lib title” underneath your schematic. Please make sure that this is always placed in all your schematics.At this point you have a completed design that is ready to be analyzed. In the next part of the tutorial, you will simulate the amplifier. First, save the design by clicking the checkmark icon (the Check and Save icon) on the left hand side of the Schematic Window (top). Check the CIW. There should be a message saying that “Schematic Check completed with no errors”. Whenever you make a change to your design, you’ll need to check and save before you simulate. Otherwise, you may get an error, which will show up in the CIW window. Again, the CIW is extremely important for finding errors. You should read any errors carefully, and sometimes warnings are important too.III. Analyzing the DesignBefore performing the circuit analysis, you need to start the analog environment by going to “Tools > Analog Environment” in the schematic window. A new window called the“Simulation Window” will appear.Next you need to tell Cadence where to find the model library. For this class, we have a single model library file, called “cmos018.scs”, which contains an nMOST model named “N”, and a pMOST model named “P”. The symbols we’re using by default have these names specified in their symbol properties (look at the properties for one of the transistors). If you ever decide to use a different symbol, you’ll need to make sure the “Model name” property is correctly filled in. To tell Cadence where to look for the model file, go to “Setup > Model Libraries” in the Simulation Window. In the “Model Library File” field, enter:/home/linux/ieng6/ee164f/your_login_name/ece-cadence/cmos018.scs(if you are taking EE164)or/home/linux/ieng6/ee264a/your_login_name/ece-cadence/cmos018.scs(if you are taking EE264a)where “your_login_name” should be replaced by the name of the account under which you logged into the system (e.g., bobama). Then click on “Add” (NOT “OK”). You’ll see the path placed in the list of Model Library Files. Now click on “OK”.Finding the DC Operating Point and Performing a DC SweepIn this section, you’ll find and annotate the DC operating point, and you’ll sweep the input voltage to find the correct bias voltage for the nMOST transistor.1.Now go to “Analyses > Choose...”. A new dialog box will appear. [a]2.In the new dialog box, select the “dc” button. Check the “Save DC Operating Point” box.This will allow us to annotate node voltages later. Finally click “OK”3.We’ll now perform our first simulation. Click on the “Netlist and Run” icon, which is thegreen traffic light on the right hand side of the Simulation Window. If this is your first time running Cadence, a “Welcome” menu appears – close it. A new window will appear, hopefully saying that the simulation was successful, and providing a brief summary of the simulation convergence. [s]4.If everything went well, go to the Simulation Window, and select “Results > Annotate >DC Node Voltages”[d]. Note that the voltages at each terminal of each device are now marked on the schematic. Now go to “Results > Annotate > DC Operating Point”[D]. Note that important voltages and currents are now marked on each device. You can quicklysee whether the devices are biased properly. You can remove this annotation by using “Results > Annotate >Design Defaults”[^d].5.You should see a problem with the node voltages. The node “vout” should be about 2.4V. Thismeans that the top pMOST is operating in triode, and this amplifier will not work properly. You’ll now fix this using a DC sweep to find the correct bias point.6.Go back to the Simulation Window, and select “Analyses > Choose...” [a]. Under “SweepVariable” on the DC Analysis Form, select “Component Parameter”. The form will become larger.7.On the expanded form, click the “Select Component” button. You will be prompted to selecta component on the schematic. Select the “vsin” symbol at the nMOST input. A new window willappear, and you should select “dc” as the parameter you wish you vary, then click “OK” in the new window.8.Fill in the rest of the form so that the voltage is swept from 0 to 2.5V. Set the sweep type to“Linear”, and set the number of points to be plotted to 500. When you’re done, click “OK” on the Choose Analyses window.9.Now you need to select an output to plot. To plot a voltage, use the following procedure:10.Go to “Outputs > To Be Saved > Select on Schematic” in the SimulationWindow. Left-click on the “vout” and “vin” nets in the schematic window, and then press “ESC”. This step is typically not done as you can simply click on the nodes you want to plot after the simulation is complete. However, go ahead and try it this time.11.Go to “Outputs > Setup...”. In the Setting Outputs window, click on the “vout” line onthe right hand side. Then select the “Plotted” button, and press “Apply”. Do the same for the “vin” line. Then click “OK” in the Setting Outputs window.12.Finally, we can perform the DC Sweep. Press the green traffic light. The Waveform Window withthe simulation results should appear.13.We need to find the input voltage which will place our output bias at roughly Vdd/2. Move yourcursor over the waveform plot of “vout”. You’ll see the x and y coordinates at the top of the window. Using this method, select the DC value of “vin” which will give an output of approximately 1.25V. You should get about 550mV. Update the “vsin” symbol with this new DC offset voltage.14.Repeat the DC simulation, and verify from the annotated voltages that your output is now roughlyat Vdd/2. If so, you’re ready to move on to the next simulation.15.But first, unless you like to repeat things, you should learn how to save the simulation state.Go to“Session > Save State...”, and you’ll be prompted to save your current state. Enter the name of a state of your choosing, or just stick with the default. This state can be reloaded later (using “Session > Load State...”, and you won’t have to enter all of the setup data again.Performing a Transient AnalysisIn this section, we’ll look at the amplifier’s large signal response to a sinusoidal input signal at 100kHz.1.First, turn off the DC Sweep analysis by bringing up the choose Analysis window and unselectingthe “Enabled” box at the bottom of the form.2.Select the “tran” button. Enter “100u” in the “Stop Time” field. If you want, you can alsoclick the “moderate” button, but this is not necessary. It is recommended by Cadence you never click the other two.3.Click the “Options” button. A new dialog box appears. In this Transient Options window,change the following attributes: “step” to 10n, “maxstep” to 10n, then press “OK”. These options make sure that enough points are taken during the transient analysis. They will be different for other simulations in this class, and you’ll need to experiment with them. Typically, you can leave this field blank and see how well the transient results look. If they seem “choppy,” go ahead and enter a number here. Refer to the Cadence documentation for more information on the other parameters on this form.4.You’re now ready to simulate, and you haven’t changed the schematic, so you can press the yellowtraffic light to simply run the simulation.5.After a few moments, the waveform window should appear with a nice sinusoid. You can removethe input sinusoid (we know it’s just a 2mV peak-to-peak wave) to get a better view of the output.Go to “Curves > Edit” in the Waveform Window, and turn off the “vin” waveform or click on the waveform and press “del”.6.To measure the peak-to-peak amplitude of the output, use the “Markers” {a},{b} menu to placemarkers A and B at the highest and lowest points of “vout”. From the display at the bottom of the window which will appear after you have done this, you should find the peak-to-peak amplitude to be about 63mV, meaning the circuit has a gain of about 30.Performing an AC AnalysisIn this section, we’ll look at the amplifier’s frequency response. Hopefully you’re becoming proficient with Cadence now, so not as much detail about the individual steps will be provided.1.Bring up the Choosing Analyses window, and disable the transient simulation, and the sweepportion of the DC simulation. Then click the “ac” button, and set up this simulation to sweep frequency from 100Hz to 1GHz, with 100 points per decade. You will need to change the sweep type to “logarithmic”.list and Run the simulation (or just run it, if your schematic is unchanged). [s]3.In the schematic window, we will now create a Bode plot. The easy way to do this is to go to“Axes” and change the scale of the y-axis to be logarithmic. We’ll use a different approach, usingthe Waveform Calculator, an important Cadence tool.(a)First, add a new subwindow to plot our new graph in. Do this by going to the “Window >Subwindows...” menu option, or by clicking on the subwindow icon on the left-handside of the Waveform Window{S}. Make sure that the new subwindow is active by left-clicking in its area. Now click on the calculator icon on the left side of the waveformwindow. The calculator will appear. By default, the calculator uses RPN (Reverse PolishNotation), but this can be changed in the “Options” menu item, if you’d like. For thefollowing, I assume you’re using RPN.(b)Click on the “wave” button in the calculator. You will be prompted to click on a wave -select the “vout” waveform. The expression for this wave will appear in the calculatorwindow.(c)You want to plot 20*log10(vout). To do this in RPN, now click on the “log10” button,then enter “20” on the keypad, then press the multiply button. You should see thecalculation take place in the calculator window. If you prefer, you can simply type “*20”at the end of the expression in the calculator window. – in other words, use it as a normalcalculator.(d)Now press the calculator “plot” button. The new wave will appear in the subwindow.4.You can also make measurements with the calculator. If you click and hold the “SpecialFunctions” button, you will see a list of functions. Select “bandwidth”. A form will come up, and you can click “OK”. Then press the “print” button on the calculator. This will bring up a window with the measured 3-db bandwidth of your circuit.5.You’re done with the AC Analysis now. We’ve only scratched the surface of what can be donewith the Waveform Calculator. Feel free to experiment more with it if you wish. Then go to the next section.Performing a Parametric SweepSometimes it’s important to perform sweeps of two variables simultaneously. This section shows you how to do this. We will sweep the nMOST bias voltage over a few values, and plot the frequency response of the amplifier for each value. This will demonstrate how drastically the bias point (which determines whether transistors are saturated) can affect circuit performance.1.For a parametric analysis, you must first define the variable to be parameterized (the one whichtakes on discrete values). In our case, this will be the offset voltage of the “vsin” symbol. Go to this symbol and edit its properties. In place of the number which you currently have entered in the “Offset voltage” field, enter “vgs”. Then click “OK”. Check and save.2.Go to the Simulator Window and select “Variables > Copy From Cellview”. You willnotice that “vgs” appears in the Design Variables subwindow.3.Go to “Variables > Edit...” (or use the shortcut) and set the value of “vgs to the bias voltage youfound during the DC Sweep portion of the tutorial.4.Next, you will need to re-enable the DC simulation. To do so, go back to the analysis chooser andselect the DC analysis button. Choose to enable this simulation; however, make sure you disable the “component parameter” sweep.5.Now netlist the schematic. (You can find the option to just netlist under “Simulation”, or youcan just netlist and run. It doesn’t make any difference. We just need to netlist somehow.) This is a critical step. If you forget to do this, the parametric analysis will seem to do nothing.6.In the Simulation Window, go to “Tools > Parametric Analysis...”. Set up the formso that “vgs” is swept from 0.4V to 0.8V in 9 total steps. In the same form, go to “Analysis > Start” to begin the analysis.7.When the Waveform window comes back, it should have multiple distinct curves, showing thefrequency response for each value of vgs. Notice how dramatically the gain drops off away from the correct bias point!A Note on Measuring CurrentsYou select a current to be plotted in much the same way as you select a voltage. When selecting outputs to be plotted (see the beginning of “Analyzing the Design”), click on the terminal of adevice rather than a wire. A circle should surround the terminal to show that the current flowing INTO this terminal will be plotted. A few caveats: first, sometimes it can be very difficult to select a node - you may have to click on the center of the symbol at which you want to measure current, which will select all nodes of that symbol, and then delete the currents you don’t want in the Simulation Window. Second, the transistor symbols used for the class don’t allow their currents to be plotted for some reason. Remember, you can always put in a zero-volt voltage source if you need some usable terminals for measuring current!A Note on Printing/PlottingSome information on customizing printing was given earlier in this tutorial. In order to actually bring up a plotting dialog box, you can go to “Design > Plot > Submit..” in the Schematic Window, or “Window > Hardcopy” in the Waveform Window. You’ll have to experiment with the forms to get what you want. The forms are quite versatile. Keep in mind you can print to a postscript file as well as directly to a printer.When printing, it is suggested that you do the following:(a)Unselect the [Plot with] “Header” button.(b)On the Plot options page:i.Unselect the “Mail Log to” button.ii.Select the “Center plot” button. [Not available when printing waveforms]iii. Select the “Fit to page” button. [Not available when printing waveforms]iv. Check that the correct printer is selected (or)v. If you want to print to a postscript file, select the “Send plot only tofile” button.If you decide to print to a file, the output will be a postscript file. This may be inconvenient for some students. If this is the case, you can run “ps2pdf <filename.ps>” to convert the postscript file to a PDF. This program, however, is not available in your path, by default. You will need to add it to your path before ps2pdf will work. To do so, at the UNIX command prompt (not the CIW!), type:set path = ( $path /software/common/ghostscript-8.0.0/bin )Note: Due to a “bug” in Cadence, waveforms are printed as they appear on the screen. In other words, if the waveform window is small, on the screen, the printout will be equally small. It is suggested that you make the waveform windows large to get the clearest printouts.。

cadence使用方法

cadence使用方法一焊盘制作1. smt焊盘1)所有程序→cadence SPB15.7→PCB edit utilities→Pad designer;2) parameter选项中: type选single ,internal layer 选option,Unit 选毫米或mi l;3)layer 选项中设置焊盘:选Begin layer→regular pad 设置焊盘形状和大小;thermal relief 和anti pad 选NULL;4)取名SAVE as存盘。

2.通孔焊盘1)所有程序→cadence SPB15.7→PCB edit utilities→Pad designer;2) parameter选项中: type选through,internal layer 选option,Unit 选毫米或mi l;设置焊盘钻孔大小,焊盘字符(可不设);3)layer 选项中设置焊盘:选Begin layer→regular pad 设置焊盘形状和大小;thermal relief 和anti pad 比焊盘大0.8或1mm,同样设置end layer(底层),soldermask_top、soldermask_bottom设置比焊盘大0.15mm,paste_top、paste_bottom设置成与焊盘一样大。

4)取名save as存盘。

二封装制作1.所有程序→cadence SPB15.7→pcb editor→Allegro PCB designe XL;2.File→new,弹出New Drawing对话框,输入文件名,在Drawing type中选Package symbol→OK;3.设置绘画尺寸:Setup→drawing size ,分别设置类型、单位、左下角座标、绘图区宽、高→OK;4. 设置栅格:setup grid,将所有层栅格设为0.0254或1mil→OK;5. Layout→pins ,Options中选connect,选定焊盘、设置重复放置形式;6. 重复放置所有焊盘;7.放置元件边界区,用于DRC检查(通常与元器件一样大,与其外形丝印一样大):Add→Rectange,右边Option中选Package geometry和place bound_top,绘制边界(此项可以不做);8.添加零件外框(集成电路再增加1脚标识):Add→line ,选package geometry和silkscreen_top选项,在line width文本框中输入线的粗度;同样方法在Assembly_top 层添加同样图形(可不用);9.增加Ref Des层零件标号:Layout→Labels→Refdes,打开Option选项,选择Silkscreen_Top,单击1脚附近,输入标号如U*,D*,R*之类,同样方法在Assembly_top层添加同样图形;10.取名save as存盘。

cadence入门指导

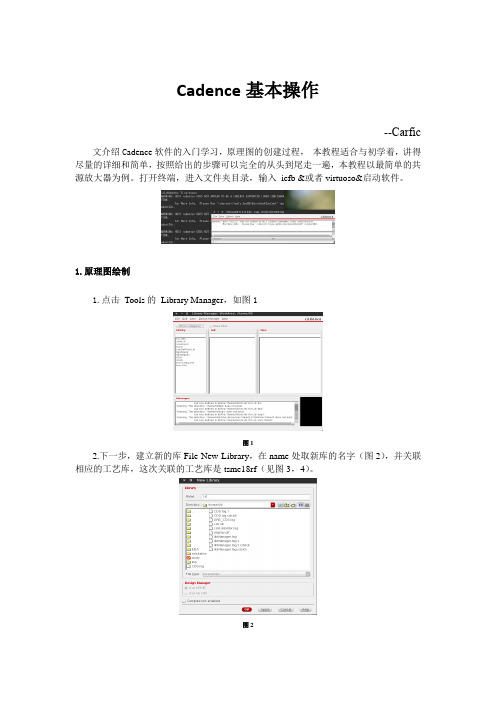

Cadence基本操作--Carfic文介绍C adence软件的入门学习,原理图的创建过程,本教程适合与初学着,讲得尽量的详细和简单,按照给出的步骤可以完全的从头到尾走一遍,本教程以最简单的共源放大器为例。

打开终端,进入文件夹目录,输入icfb &或者virtuoso&启动软件。

1.原理图绘制1.点击Tools的Library Manager,如图1图12.下一步,建立新的库File-New-Library,在name处取新库的名字(图2),并关联相应的工艺库,这次关联的工艺库是tsmc18rf(见图3,4)。

图2图3 图43.接下来在,新建库(CS)下面建立原理图,在manager中点击新建的库,再点击File-New-Cell View,并取名字,此处仍取名cs(图5)。

出现原理图(图6)图5 图6接下来可以进行原理图绘制,首先介绍几个快捷键:F:调节界面至最全最合适模式M:移动器件I:加入器件Q:调整器件参数W:连线C:复制器件R:旋转器件,在移动,复制和加器件的时候可以使用X:保存电路并且检查是否有error和warningL:给线标注名字,名字相同即相连,尽量不要取关键字的名字,如vdd!,gnd!等P:加pin脚,在做symbol的时候使用,pin的名字和线的名字一样的时候,默认相连接。

E:进入symbol下一层电路shift+M:移动器件不会影响线shift+W:粗线shift+R:镜像器件ctrl + E:返回上一层电路图4.第一步,先按I(图7),再选择tsmc18rf库,在cell找nmos2v(在此工艺下的器件名,有些工艺是nch),并在view选择symbol,即可添加(图8)。

图7图8同样,可以加入此工艺库下的pmos,电阻和电容等,在简单仿真的时候,除晶体管外的元件(电压源,电流源)可以使用虚拟模拟元件,都在在analogLib下面。

以添加DC电压源步骤为例,按I,再选择analogLib库,在cell中找到vdc,并在view选择symbol(图9)。

cadence使用教程

p+ implant

Thin oxide

contact

Metal1

n+ implant poly

PMOS layout view

n-well

p+ implant

n+ implant

12

Start schematic

一. 建立 Schematc view:跟建立 layout view 方法一樣(請參考 Start Cadence 的第 五大點的第二小點),先點選要 LM 視窗預定的 library,再點選 LM 視窗的 File→New→Cell view,按 OK 之後,即可建立 Schematic View

1.數字應該是 4.4.5 2.若不是 4.4.5,代表使用到舊版 的 cadence 了,請從第一點重新 開始

CIW(command Interpreter window)

三.點選在 CIW 視窗的上面工具列 Tools→Library Manager, 會出現 LM 視窗 LM(Library Manager)

1. 桌面改為 1024*768*256 色 2. 執行 xwin 程式 3. Netterm telnet 140.116.164.112~141 (CIC 電腦教室) 4. e2486***@eesol08:~> who

e2486*** pts/2 Dec 28 11:43 (.tw) 5. e2486***@eesol08:~> setenv DISPLAY .tw:0.0 6. 完成上述五個步驟後,Start Cadence 的方法,請參閱使用手冊第六頁。

10

四.當在畫的途中,可以使用 on-line drc(DIVA)來檢查是否違反 design rule 1. 點選 Layout 視窗上面的指令 Verify→DRC 2. 出現 DRC 視窗

Cadence 手册详细图解 英文版

Cadence IC Design ManualFor EE5518ZHENG Huan QunLin Long YangRevised onMay 2017Department of Electrical & Computer EngineeringNational University of SingaporeContents1 INTRODUCTION (4)1.1 Overview of Design Flow (4)1.2 Getting Started with Cadence (6)1.3 Using Online Help (8)1.4 Exit Cadence (8)2 SCHEMATIC ENTRY (9)2.1 Creating a New Design Library (9)2.2 Creating a Schematic Cellview (10)2.3 Adding Components to Schematic (11)2.4 Adding Pins to Schematic (12)2.5 Adding Wires to Schematic (13)2.6 Saving Your Design (14)3 SYMBOL AND TEST CIRCUIT CREATION (15)3.1 Creating Symbol (15)3.2 Editing Symbol (16)3.3 Building Test Bench (18)4 SIMULATING YOUR CIRCUIT (21)4.1 Start the Simulation Environment (21)4.2 Selecting Project Directory (21)4.3 Setup Model Library (22)4.4 Choosing the Desired Analysis (22)4.5 Setup Variables (23)4.6 Saving Simulation Data (24)4.7 Saving Output for Plotting (24)4.8 Viewing the Netlists (25)4.9 Running the Simulation (25)5 PHYSICAL LAYOUT (28)5.1 Layout vs Symbol of CMOS Devices (28)5.2 Starting Layout Editor (29)5.3 Vias (31)5.4 Changing the Grid (33)5.5 Inserting and Editing Instances (34)5.6 Drawing Shapes / Paths (35)5.7 Creating Pins (36)6 DESIGN VERIFICATION: DRC AND LVS (38)6.1 Performing DRC (38)6.2 Performing LVS (40)6.3 Performing PEX (41)7 POST‐LAYOUT SIMULATION (45)7.1 Simulation the Extracted Cell View (45)8 CONCLUSION (46)1INTRODUCTIONThis manual describes how to use Cadence IC design tools. It covers the whole design cycle, from the front-end to the back-end, i.e., from the pre-layout design to the post-layout design.The manual aims to provide a guide for fresh users. Following the manual, users can start doing analog IC design even though the users don’t have any knowledge of the tools.An inverter is used to illustrate the whole cycle of analog IC design, and Cadence Generic 45nm (cg45nm) kit is the technology library used for implementing the inverter. The method stated in the manual can be applied to other type of analog circuit design.1.1Overview of Design FlowFigure 1 shows a typical analog IC design flow.The design flow starts from schematic entry with the Cadence schematic capture tool –Schematic Editor. Devices or cells from the cg45nm or other libraries are used to build your circuit. Your design is hierarchical; therefore higher level schematics also incorporate cells which you have already developed. The schematics which you enter at this stage therefore typically consist of a number of base library cells and also lower level cells designed yourself.These are described in Sections 2 and 3 of the manual.When you have finished designing a particular circuit, you need to simulate it to ensure that it works as expected. It would be unlikely that your circuit works as expected at the first time so you have to repeat the cycle to improve the circuit, as shown in Figure 1, until the circuit works satisfactorily. This must be done for each sub-circuit of your design and then for the top level design. How to simulate and view the performance of simulation results are presented in Sections 4 of the manual.When the performance of the circuit is satisfactory, it is ready to start the physical design or layout of the circuit. The layout starts with the cell or device placement. Once the cells have been placed, routing can be carried out. Routing connects the cells/device of the design.After finishing placement and routing, the layout has to go through the Design Rule Check (DRC) with rule decks provided by PDK provider, to ensure that there is no design rule violation in the layout. The layout has to be rectified accordingly to the rules’ requirement till it passes DRC.Upon a successful DRC, it is Layout-versus-Schematic (LVS) check, to assure that all connections in the layout are correct. The layout has to be amended accordingly to the schematic If LVS doesn’t pass. DRC has to be done whenever layout is changed. The process is repeated until the LVS passes.Figure 1. Analog IC Design FlowThe next step is parasitic extraction (PEX) to get the extracted view of the circuit, which is used for post–layout simulation. The extracted view includes the parasitic effects in both the instances/devices and the required wiring interconnects of the circuit.Following DRC, LVS and PEX, it is post-layout simulation. The post-layout simulation is essential to make sure that the circuit with the extra parasitic parameters functions well and still meet the design specifications. If the performance of the post-layout simulation is not acceptable, back to the stage of schematic entry to check the circuit. Basically, re-design the circuit is necessary. Repeat the whole flow until the results of the post-layout simulation meet the design specifications.If everything is satisfactory, the next stage is GDSII Generation. It generates a file which depicts the low level geometry of layout. GDSII format is industry standard format suitable fora semiconductor company to fabricate and manufacture the chip of layout. This is briefed inthe last section of the manual.1.2Getting Started with CadenceUpon logging into your account, you will be brought to the Linux Desktop Environment.Right click on the desktop and click Open Terminal to open a “window” on the desktop. This window is the Linux command line prompt at which you can run Linux commands. After running a Linux command, this window also shows the output of the command.The following steps show how to start Cadence with cg45nm kit.A.Create a working directory - project (it can be any name as you like) with thecommand:mkdir projectwhere mkdir is Linux command and the project is the directory name;B.Enter the working directory with the command:cd projectwhere the cd is the Linux command;C.Type the followings commands to do the environment setup for using Cadence Generic45nm PDK.cp /app11/cg45nm/USERS/cds.lib .cp /app11/cg45nm/USERS/assura_tech.lib .cp /app11/cg45nm/USERS/pvtech.lib .D.Start cadence in the working directory – project with the following command:virtuoso &where virtuoso is the command to start Cadence IC design tool.Now, Cadence tools are successfully started. Keeps only the Command Input Window (CIW) which is shown in Figure 2.Figure 2. CIW WindowDo not close this CIW and try to keep it in view whenever you are using Cadence. Error messages and output from some of the tools are always sent to the CIW. If something doesn't appear to be working, always check the CIW for error messages. In addition, the CIW allows the user great control over Cadence by interpreting skill commands which are typed into it.E.In the CIW, select Tools Library Manager. The Library Manager pop up as inFigure 3. The Library Manager is where you create, add, copy, delete and organizeyour libraries and cell views.Figure 3. Library Manager WindowYou can see that the library gpdk045 appears in the Library column of the librarymanager.Now, you have started Cadence tool and loaded the cg45nm kit successfully. There are some documents in /app11/cg45nm/ gpdk045_v4_0/docs, and you can always refer to these documents for the information such as devices, device models, DRC rules and others related to cg45nm kit.Next time, you need only to repeat the steps B and D, for launching Cadence virtuoso and doing your project.1.3Using Online HelpCadence provides a comprehensive online manuals for all Cadence tools. You can launch the online help by typing the following command at the Linux prompt.cdnshelpThis invokes the online software manuals. Alternately, there is a help menu on each Cadence window. Manual which is related to that window related will pop-up once clicking on the help button.1.4Exit CadenceTo exit Cadence, just click on the cross sign X or File Exit in CIW. It is necessary to exit Cadence when it is not in use. Your library file would be locked or cannot edited next time if Cadence was not exited properly.2SCHEMATIC ENTRYNow that Cadence is running, you are almost ready to start entering schematics. However, you must first create a library which will be used to store all the parts of your design. Then, schematic can be created in the library.2.1Creating a New Design LibraryA.In the Library Manager window, select File→New→Library. New Library formpops up as shown in Figure 4.B.In the New Library form referring to Figure 4, key in your design library name(example: test) in the field of Name, and then click Ok.C.Click Ok in the pop-up window - the Technology File for New Library, referring toFigure 5.D.Choose gpdk045 in the Attach Library to Technology Library form, referring toFigure 6, and then click Ok.Figure 4. New Library FormFigure 5. Technology File for New Library FormFigure 6. Attach Library to Technology File FormA new library, named test, should appear in your Library Manager window.2.2 Creating a Schematic CellviewA.In Library Manager, select the Library where you would like to create a schematic. Then,select File→New→Cell View.B.Set up the New File form as Figure 7Figure 7. Create CellViewC.Click OK when done. A blank schematic window for the "inv" (your cell name)schematic appears.Explore the functions available by putting your mouse over the toolbar and fixed menu icons.In addition, note that some of the menu selections have alphabets listed to the right of them. These are bind-key or shortcut-key definitions which are very useful in the long run.Test them out during the schematic drawing in subsequent steps.2.3Adding Components to SchematicFigure 8 shows the schematic which you are going to patch, and the property of each component is listed in Table 1.Figure 8. Inverter CircuitTabel 1. Component Properties of Figure 8: Inverter CircuitComponents Library Name Cell Name PropertiesPMOS gpdk045 pmos1v l:45nm w:120nm (default size)NMOS gpdk045 nmos1v l:45nm w:120nm (default size)Here is the example on how to add component instances by placing cell views from libraries. Type “i” bind-key or select Create Instance in the schematic window or click on the menu bar to display Add Instance form. Then in the Add Instance window, select gpdk045as Library, choose the NMOS transistor by selecting nmos1v in Cell and also choose symbol as View, as shown in Figure 9.Figure 9. Add Instance FormSimilarly, add the pmos1v into the schematic. As an example, here we just keep all theparameters as default.If you place a component with the wrong parameter values, select the component and type “q” bindkey or use the Edit→Properties→Objects command to change the parameters. Use the Edit→Move command or type “m” if you place components in the wrong location.2.4Adding Pins to SchematicYou must place I/O pins in your schematic to identify the inputs and the outputs. A pin can be an input, output or an input-output (bi-directional) pin.Type “p” or select Add →Pin from inv Schematic Window or click the Pin fixed menuicon in the schematic window. The Add Pin form appears as Figure 10.Figure 10. Add Pin FormClick Hide and move you cursor to the Schematic Window. Place pins at the correct places and click right mouse key to rotate the pin if necessary.Add pins according to Table 2, paying attention to the direction.Table 2. Pin Names and Direction of invPin Names DirectionVin InputVout OutputVDD, GND Input-OutputCaution: Do not use the add component form to place schematic pins.2.5 Adding Wires to SchematicAdd wires to connect the components and pins in the design.A.Type “w” or select Add →Wire (narrow) in Schematic Window or click (narrow)fixed menu icon.B.In the schematic window, click on a pin of one of your components as the first pointfor your wiring. A diamond shape appears over the starting point of this wire.C.Follow the prompts at the bottom of the design window and click left mouse key onthe destination point for your wire.D.Continue wiring the schematic. When done wiring, press Esc with your cursor in theschematic window to cancel wiring.2.6Saving Your DesignCheck the design to ensure that it is correct and save the design.A.Click the Check and Save icon in the schematic window.B.Observe the CIW output area, for the information of the check and save action.3SYMBOL AND TEST CIRCUIT CREATIONSymbols are useful when creating designs as it is impractical to show every transistor on the top level schematic. Instead, the symbols of cells are created in order to instantiate them in the higher level schematics and make them more readable (i.e. hierarchical designs). Create a symbol for your design so you can place it in a test circuit for simulation.3.1Creating SymbolA.In the inv schematic window, select Create → Cellview → From Cellview. CellviewFrom Cellview pops up as shown in Figure 11.Figure 11. Cellview From Cellview FormB.Click OK in the Cellview From Cellview form. The Symbol Generation Options formappears as Figure 12. Enter the information listed in Table 3 for the symbol.Table 3: Pin SpectificationsLeft Pins : VinRight Pins : VoutTop Pins: VDDBottom Pins: GNDFigure 12. Symbol Generation Options FormC.Click OK in the Symbol Generation Options form. A window with a symbol createdautomatically by the tools pops up, referring to Figure 13.Figure 13. Symbol Generated AutomaticallyD.Observe the CIW output pane and note the messages stating Adding ‘CDFinformation ...’.3.2Editing SymbolYou can modify the symbol to have a more meaningful shape for easy recognition.A.Move your cursor over the symbol, until the entire green rectangle is highlighted. Clickleft to select it.B.Click Delete icon in the symbol window to delete the green rectangle.C.Select Create→Shape→Polygon. Follow the prompts at the bottom of the symbol, anddraw the triangle shown in Figure 14.D.Type “m” or click Move icon in the symbol window, move the pins to the finaldestination.E.Select [@partName], and use Edit→Properties→Object to change it to inverter asshown in Figure 14.Figure 14. Edit Object Properties FormF.Save your edited symbol view. The final symbol is shown in Figure 15.Figure 15. Symbol of inv3.3Building Test BenchTo test the inverter that you have just built, you need to create a test bench. This test bench will also be used during the post-layout simulation.Creating an inv_test schematic cellview with the below information, following the steps listed in Section 2 – SCHEMATIC ENTRY. The test bench is as shown in Figure 17.Library Name : testCell Name : inv_testView Name : schematicLibrary Name Cell Name Propertiestest inv_testanalogLib Vdc VDDanalogLib vpulse Referring to Figure 16analogLib gnd GNDanalogLib cap 1f FFigure 16. Vpulse FormFigure 17. Test Bench – inv_test for inv CircuitNote:There are wire names Vin and Vout in Figure 17. These can be created by clicking on Create Wire Name on the inv_test schematic window. Key in Vin Vout in the Names field of the Add Wire Name form, and then click Hide. Moving your mouse to the schematic window, click the wire where you want it to be named in the same sequence as typing the names in the Names field.4SIMULATING YOUR CIRCUITBefore starting the simulation, make sure that the schematic (inv_test) is open, then perform the following steps.4.1Start the Simulation EnvironmentIn your schematic window, select Launch →ADE L. The Analog Design Environment (ADE) window appears as shown in Figure 18.Figure 18. ADE Window4.2Selecting Project DirectoryIn the ADE window, select Setup→Simulator/ Directory/ Host. A Choosing Simulator form appears as Figure 19. In the Project Directory blank, type in /var/tmp/(desired folder name) to save your simulation files in the /var/tmp directory on the local server. Click OK to confirm.Figure 19. Choosing Simulator/Directory/Host FormAs each user account has a limited quota, this helps to conserve memory space in your account and prevents you from exceeding your account quota. However, note that contents in this folder is deleted periodically every 30 days automatically.4.3Setup Model LibraryIn the ADE window, select Setup Model Libraries. The Model Library setup form appears. Double click the column of section, and then click the down arrow to choose tt which is typical N and P model parameters. The model library setup for the inv_test circuit is shown in Figure 20. Click ok on the setup form to finish the settings.The information of models can be found in/app11/cg45nm/gpdk045_v4_0/docs/gpdk045_pdk_referenceManual.pdf.Figure 20. Model Library Setup for inv_test4.4Choosing the Desired AnalysisIn the ADE window, click the Choose Analyses icon . The Choosing Analyses form appears. Cadence ADE is able to run several types of simulations consecutively. You are then able to view the signals from different simulations at the same time. In this example, we will do transient analysis, so we shall setup transient analyses through the ADE as Figure 21.Figure 21. Setup for Transient Analyses4.5Setup VariablesThere is a variable, VDD, in the inv_test circuit. We need to set a value to it before starting simulation.In the ADE window, click Variables. Enter the name as the variable name VDD, then set the valueas 1.1, and finally click Ok. Please take note that 1.1v is the nominal voltage for this technology.Figure 22. Editing Design Variables4.6Saving Simulation DataThe simulation environment is configured to save all node voltages in the design by default. In larger designs, where saving all of the data requires too much disk space, you can select a specific set of node to save. Following steps show you how to select terminals to save.A.In the ADE window, select Outputs→Save All.B.The Keep Options form appears. Do not modify the form at this time. However, if youneed to save less data, under the first option “Select signals to output”, Click “selected”.4.7Saving Output for PlottingSelect the signals that you would like to observe.A.Select Outputs→To Be Plotted→Select On Design.B.Note that if you click on wires / nets, voltage signals are selected. If you click onconnection nodes, currents flowing through that note and into the component are saved.C.Follow the prompts at the bottom of the schematic window. Click on the output wireslabeled with Vout and Vin (select the wire that you want to monitor).D.Press Esc with your cursor in the schematic window when finished.Now you have set up the simulation environment which as shown in Figure 23. You can save the simulation state. This saves all the information such as the Model Path, outputs, analyses, environment options, and variables so that you do not need to set these parameters the next time again.Figure 23. ADE window with completed settingsIn the ADE window, select Session→Save State. Tick Cellview and then click OK. You can recall your settings by selecting Session→Load State.4.8Viewing the NetlistsSometimes, you need to view the netlist of your circuit or design. You can do so through the ADE, select Simulation→Netlist→Create / Display / Recreate.If there are any errors encountered during this step, check the messages in the CIW and retrace your steps to see that all data was entered properly.4.9Running the SimulationSelect Simulation→Netlist and Run to start the simulation or click on the Run Simulation icon in the Simulation Window. After the simulation is done, a waveform window will pop up showing the simulation results as Figure 24.Click on the waveform window to separate Vin and Vout.You can create a horizontal or vertical marker by clicking Marker on the waveform window. For example, creating a horizontal marker on Figure 24 with put Y Postion at 0.5*VDD=550mV, and then zoom in. The waveform window will look like Figure 25. Delays of the inverter could be found from the reading on the marker.Figure 24. Output of SimulationFigure 25. Waveform with Marker.Explore the icons on the toolbar as well as the various items on the menu. Try to add markers as that is something that will be used often during your simulations. You can also update the titles and labels on your plot to make them easy to read or more meaningful, if necessary.*Quick Tip : Shortcuts “a” and “b” to place a delta marker where you observe the difference between two points. What does shortcuts “v” and “h” do?There are many other functions available in the calculator tool, explore and play around with them.By now, you have finished pre-layout simulation (schematic level simulation). Next, you need to draw the layout of the inverter circuit and then do post-layout simulation to check your circuitperformance.5 PHYSICAL LAYOUTBy now, you should know how to create and simulate your circuit. Once the performance of your design is satisfactory, the next step in the process of making an integrated circuit chip is to create a layout. What is a layout? A layout is basically a drawing of the masks from which your design will be fabricated. Therefore, layout is just as critical as specifying the parameters of your devices.Before we get into the layout, first you need to understand the design rules for layout. Design rules give guidelines for generating layouts. They dictate spaces between wells, sizes of contacts, minimum spacing between a poly and a metal, and many other similar rules.Design rules are essential to any successful layout design, since they account for the various allowances that need to be given during actual fabrication and to account for the sizes and the steps involved in generating masks for the final layout. Note that the layout is very much process dependent, since every process has a certain fixed number of available masks for layout and fabrication.You may find more details on the Design Rules Manual (DRM):/app11/cg45nm/gpdk045_v_4_0/docs/gpdk045_drc.pdf5.1 Layout vs Symbol of CMOS DevicesIn this section, we look at only three devices: nmos1v and pmos1v. Check the process document, you can find the information for other devices.Figure 26 shows the nmos1v device. From layout view, you can see that the terminal B is the black background of the layout window.Figure 26. Layout vs Symbol of NMOSFigure 27 shows the pmos1v device, which looks similar to NMOS device but with P type implant (orange-stripe layer) and N-well (purple surrounding layer). G D SBFigure 27. Layout vs Symbol of PMOS5.2Starting Layout EditorNow we are going to create a new layout in the cell “inv” in “test” library.A.In Library Manager, select File→New→Cellview ... A Create New File form pops up.B.Select "test" as Library Name; enter "inv" as Cell Name, "layout" as View Name.C.Choose Open with Layout XL, and then click OK.Figure 28. Create Cellview – LayoutUseful layerselectionfeatureFigure 29. Layout WindowCell "inv" with "layout" view in library "test" will be created. It is opened up automatically, followed by inv schematic window, as shown in Figure 29. The layout editor contains two main sub-windows, namely the Layers sub-window on the left and Layout Editing window on the right. Notice the Layers sub-window on the left side of the layout view. This sub-window displays the fabrication layers defined in the technology. You can find the cross sectional profile in the process documents.Each layer is represented by a different color and pattern for easier differentiation. The black background on the right can be interpreted as the p-substrate of the wafer.To hide a layer, use the middle scroll button to click on a layer. To disable a layer from use, use the right mouse button.You might notice that some layer names appear more than once in the Layers sub-window. For example, Metal1 appears two times: one as Metal1 drawing, the other as Metal1 pin. Metal1 drawing is a layer with drawing purpose, and such layers with drawing purposes will be fabricated in the mask. The pin layers are symbolic layers and serve to indicate position of I/O pins and define net names. Such layers are not part of the mask layout and will not be fabricated.5.3ViasVias are used to connect between layers, much like those used in PCB design.There are different types of vias for different layer pairs. Normally a via is only for connecting two successive layers, e.g., Metal 1 and Metal 2. In case there is a metal jump between more than two layers, via stacking is required.In the layout window, click Create→Via or type “o” to bring up the via menu. Place the vias on the layout editing window, you can observe the layers that are involved in each type of via. Experiment with the different modes and configurations in the via menu to create arrays and stacks of vias as well. For example,A.Click on Create→Via, the Create Via window pops up as figure 30 shows.B.Choose M1_PO under Via Definition, and click on the layout window to place it andthen press Esc button to stop the placing. You can change the number of Rows and Columns on the Create Via form.C.To view the layers of M1_PO, click to select it first and then press Shift + f key. Observethe via appears different.D.To check the layers used in via M1_PO, select it and then click Edit→Hierarchy→Flatten as shown in figure 31. Click OK on the pop-up form shown in Figure 32.E.Now, you can separate the layers and check layers’ property to find out the layers’ name.Via M1_PO connects layers Metal 1 and Poly as shown in Figure 33.Try to explore different options (Rows, Columns, Stack, etc.) under via menu by yourself, this will be very helpful for layout drawing.Figure 30. Create Via windowsFigure 31. Edit ViaFigure 32. Flatten FormFigure 33. Via M1_POThe M1_PSUB and M1_NWELL contacts are substrate and n-well contacts that are used to connect the bulks of the NMOS and PMOS respectively. For the inverter circuit used in this manual, the bulks of the NMOS and PMOS need to be connected to ground (GND) and VDD respectively.5.4Changing the GridIn Figure 29, the black window on the right is the layout editing window. The position of the cursor in layout editing window is indicated by the coordinate showed on the top right corner of the window after X: and Y:. The unit here is "µm". Move your cursor around the editing window and see the X: Y: values change with step size 0.1. Change the step size to 0.005 as that is the minimum step size for this technology.From Layout Editing window pull down menu, select Options →Display... change "X Snap Spacing" and "Y Snap Spacing" to 0.005 then click on "OK". Now move the cursor around the editing window again, you will see the X: Y: values change with step size 0.005.There are raw grid and fine grid (as small dots) on the window background. If you cannot clearly see the raw grids, from pull down menu select Window →Zoom out by 2In addition to pull down menu and bind key "z", "Zoom Out" is also listed in the picture tool bar to the left of the window. Find it and try it out.Also you may use up, down, left, and right arrows to move around the design window. You will need to use "Zoom in" and "Zoom out" and those arrows many times throughout your design process. So it's not a bad idea to practice them a little bit now.To save and close the cell view, from Virtuoso Editing window, Select Design →Save.。

Cadence入门使用说明

• 1.确认服务器打开,将IP地址更改为 192.123.123.150,进入Xbrowser浏览器 • 2.单击CAD1500,输入用户名和密码,进入 Solaris系统

• 3打开终端,进入文件夹目录,输入icfb&启 动软件,主要中间有个空格。

启动后出现如下界面

· 4点击Tools-Library Manager进入Library Manager界面

上面显示的是文件管理窗口,可以看到文件存放的结构,其中Library就是文 件夹,Cell就是一个单元,View就是Cell的不同表现形式,比如一个mos管 是一个Cell,但是mos管有原理图模型,有版图模型,有hspice参数模型, 有spectre参数模型等,这就列举了Cell的4个View。他们之间是树状的关系, 即,Library里面有多个Cell,一个Cell里面有多个View。

• 5建立新的Library

• 6文件夹建好了后,我们要建立原理图

注意ViewName是填的schematic,Tool用的是这个。点 击OK之后发现Library Manager里面有如下变化:

• 7双击View中的schematic打开schematic editing窗口进行版图绘制

• Cadence绘制版图常用的快捷键 R 矩形 C 复制 Q 显示属性 DEL 删除 shift+O 旋转 shift+M 粘合 C+F3 镜像

cadence指导详细版_3

一、cadence软件及安装指导1、安装虚拟机,安装过程中需要添加vmware7.0sn.txt中的Serial(注意:一旦安装成功不要轻易卸载,否则重装很费劲)2、在windows下解压cadence文件夹下压缩包3、双击桌面虚拟机图标,打开虚拟机,点击界面左上角FILE》》open》》在弹出的对话框找到刚刚解压的cadence文件夹下的cadenceEDA.vmx文件,点击“打开”4、点击power on this virtual machine ,输入用户名 zyx,密码 1234565、我们进入到了linux系统。

二、 NCSU TSMC0.25um库的加载及cadecne的环境配置1、直接将文件夹ncsu-cdk-1.5.1拷贝到linux系统桌面。

(若直接复制不成功,可通过U盘将其导入。

)2、打开桌面zyx’Home目录(即文件夹),在里面新建目录VLSI,将桌面ncsu-cdk-1.5.1剪切至VLSI目录下。

3、在桌面空白处单击鼠标右键,点击open Teminal4、在终端输入以下命令。

1、 su root -------进入到超级用户2、 sunface8211200 (不可见,直接输入即可)3、 chmod a+w cds.lib ------修改cds.lib权限后,可以对其进行编写4、 vi cds.lib --------进入到vi 编辑器,单击键盘“ i ”进入到插入模式,在第一行我们添加一行语句。

INCLUDE/home/zyx/VLSI/ncsu-cdk-1.5.1/cdssetup/cds.lib输入完之后,单击键盘“esc”键退出插入模式,再点击键盘“:wq ”退出vi编辑器5、cd VLSI/ncsu-cdk-1.5.1/cdssetup ---------进入到cdssetup目录6、 vi cds.lib --------做如下图修改后,点击esc键并输入“:wq ”退出7、csh -------进入到c shell命令8、vi /home/zyx/.cshrc ------进入到用户目录下的 .cshrc的编写,并添加如下语句setenv CDK_DIR /home/zyx/VLSI/ncsu-cdk-1.5.1 ,添加后“:wq ”保存退出9、cp cdsinit /home/zyx/.cdsinit10、cp display.drf /home/zyx/display.drf11、至此,ncsu-tsmc0.25um工艺库安装完毕,cadence环境配置也已经结束。

cadence入门指导

Cadence基本操作--Carfic文介绍C adence软件的入门学习,原理图的创建过程,本教程适合与初学着,讲得尽量的详细和简单,按照给出的步骤可以完全的从头到尾走一遍,本教程以最简单的共源放大器为例。

打开终端,进入文件夹目录,输入icfb &或者virtuoso&启动软件。

1.原理图绘制1.点击Tools的Library Manager,如图1图12.下一步,建立新的库File-New-Library,在name处取新库的名字(图2),并关联相应的工艺库,这次关联的工艺库是tsmc18rf(见图3,4)。

图2图3 图43.接下来在,新建库(CS)下面建立原理图,在manager中点击新建的库,再点击File-New-Cell View,并取名字,此处仍取名cs(图5)。

出现原理图(图6)图5 图6接下来可以进行原理图绘制,首先介绍几个快捷键:F:调节界面至最全最合适模式M:移动器件I:加入器件Q:调整器件参数W:连线C:复制器件R:旋转器件,在移动,复制和加器件的时候可以使用X:保存电路并且检查是否有error和warningL:给线标注名字,名字相同即相连,尽量不要取关键字的名字,如vdd!,gnd!等P:加pin脚,在做symbol的时候使用,pin的名字和线的名字一样的时候,默认相连接。

E:进入symbol下一层电路shift+M:移动器件不会影响线shift+W:粗线shift+R:镜像器件ctrl + E:返回上一层电路图4.第一步,先按I(图7),再选择tsmc18rf库,在cell找nmos2v(在此工艺下的器件名,有些工艺是nch),并在view选择symbol,即可添加(图8)。

图7图8同样,可以加入此工艺库下的pmos,电阻和电容等,在简单仿真的时候,除晶体管外的元件(电压源,电流源)可以使用虚拟模拟元件,都在在analogLib下面。

以添加DC电压源步骤为例,按I,再选择analogLib库,在cell中找到vdc,并在view选择symbol(图9)。

Cadence软件使用教程 ppt课件

Allegro PCB Router 自动布线工具,对于有复杂设计规则的高密度电路板处理能力很强, 可以在Allegro PCB Editor中用自动布线命令调出来。这个布线工 具名气很大,对于简单的电路板,布线很美观,布通率很高。

Cadence软件使用教程

Cadence软件使用教程

1、利用OrCAD Capture CIS进行原理图设计 2、利用Cadence PCB Editor进行PCB布局布线 3、光绘文件(Artwork)制作,如何生成Gerber文件

Cadence软件使用教程

Cadence软件使用教程

1、系统的原理图工程文件 2、系统的PCB图工程文件 3、原件库、封装库文件 4、板上芯片的datasheet 5、给PCB厂商的Gerber文件(Artwork) 6、DSP6713程序的C语言源代码

Padstack Designer 创建及修改焊盘padstacks Allegro在创建零件封装时,焊盘需要单独设计,必须使用这个工具先创建焊盘。 DB Doctor 用于检查设计数据中的错误,在设计的每一个阶段执行,可以部分修复数据错误。 在生成光绘文件前必须进行DBDoctor检查。

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Candence指导

Linux系统用户是:nwpu密码是:eeCadence启动命令:第一步:键入“lmli”命令。

第二步:键入“icfb&”命令即可。

进入库管理界面:Tools -> Library Manager新建库:File -> New -> Library在弹出的界面中输入库名及路径,“OK”。

之后弹出“technology file for new library”对话框,选择最后一项“do not need process information”, “OK”即可。

新建Cell:File -> New ->Cell ViewCell:输入Cell名字Type:schematic其他默认“OK”即可。

Candence下画电路图的基本快捷键:加入实例化:I给线加名字:L被选对象旋转:R被选对象水平/上下翻转:M –〉F3 出现对话框进入下一层:E返回上一层:Ctrl+E加Pin:P 出现对话框缩小:[放大:]画单根总线:W画多根总线:Shift+W看对象属性:Q 也可以在属性对话框中修改对象产生Symbol:Create –〉Cellview –〉From Cellview、产生网表:Launch –〉ADE L 出现“analog design environment”对话框;Setup –〉Simulator 在出现的对话框中Simulator选择:hspiceD, “OK ”;Simulation –〉Netlist –〉Create 产生网表。

保存时,存储到Windows系统可见的文件夹下,以便在Windows下仿真。

Cadence入门教程

Cadence使用初步简介在早期的ASIC 设计中电路图起着更为重要的作用作为流行的CAD软件Cadence 提供了一个优秀的电路图编辑工具Composer。

Composer不但界面友好操作方便而且功能非常强大电路图设计好后其功能是否正确性能是否优越必须通过电路模拟才能进行验证Cadence 同样提供了一个优秀的电路模拟软件Analog Artist由于Analog Artist 通过Cadence 与Hspice 的接口调用Hspice 对电路进行模拟。

但是我们的虚拟机中并没有安装Hspice软件,所以我们使用Cadence自带的仿真软件进行仿真。

本章将介绍电路图设计工具Composer 和电路模拟软件Analog Artist 的设置启动界面及使用方法简单的示例以及相关的辅助文件以便大家能对这两种工具有一个初步的理解。

一、Cadence平台的启动:①右击桌面,在弹出菜单中单击open Terminal②在弹出的终端中输入icfb&然后按回车启动Cadence③Cadence启动过程④Cadence启动完成后,关闭提示信息①点击Tools—Library Manager…启动设计库管理软件②启动设计库管理软件③点击File—New--Library新建设计库文件④在弹出的菜单项中输入你的设计的库的名称,比如MyDesign,点击OK⑤选择关联的工艺库文件,我们选择关联已有的工艺库文件,点击OK⑥在弹出菜单中的Technology Library下拉菜单中选择我们需要的TSMC35mm 工艺库,然后点击OK。

⑦设计的项目库文件建立完成,然后我们在这个项目库的基础上建立其子项目。

点击选择mydesign,然后点击File-New-Cell View…⑧输入子项目的名称及子项目的类型,多种类型,目前课程设计中用到的主要是电路图编辑和版图编辑。

在设计版图之前我们假定先设计原理图:所以我们选择,然后点击OK。

Cadence技巧精品文档13页

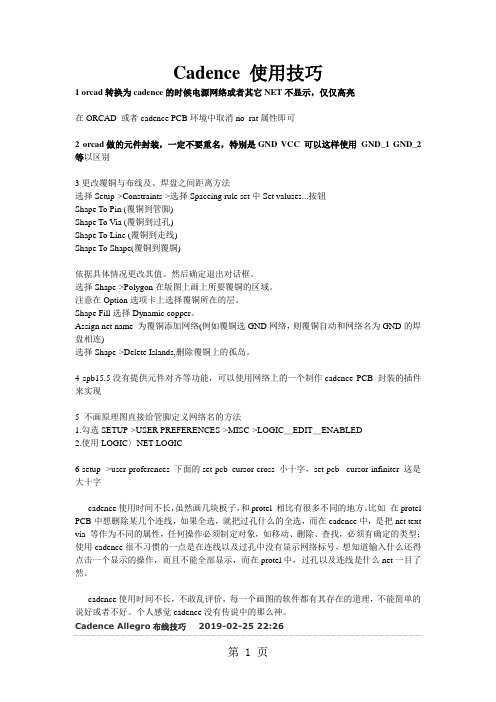

Cadence 使用技巧1 orcad转换为cadence的时候电源网络或者其它NET不显示,仅仅高亮在ORCAD 或者cadence PCB环境中取消no_rat属性即可2 orcad做的元件封装,一定不要重名,特别是GND VCC 可以这样使用GND_1 GND_2等以区别3更改覆铜与布线及、焊盘之间距离方法选择Setup->Constraints->选择Spaceing rule set中Set valuses...按钮Shape To Pin (覆铜到管脚)Shape To Via (覆铜到过孔)Shape To Line (覆铜到走线)Shape To Shape(覆铜到覆铜)依据具体情况更改其值。

然后确定退出对话框。

选择Shape->Polygon在版图上画上所要覆铜的区域。

注意在Option选项卡上选择覆铜所在的层。

Shape Fill选择Dynamic copper。

Assign net name 为覆铜添加网络(例如覆铜选GND网络,则覆铜自动和网络名为GND的焊盘相连)选择Shape->Delete Islands,删除覆铜上的孤岛。

4 spb15.5没有提供元件对齐等功能,可以使用网络上的一个制作cadence PCB 封装的插件来实现5 不画原理图直接给管脚定义网络名的方法1.勾选SETUP->USER PREFERENCES->MISC->LOGIC_EDIT_ENABLED2.使用LOGIC〉NET LOGIC6 setup-->user proferences 下面的set pcb_cursor cross 小十字,set pcb _cursor infiniter 这是大十字cadence使用时间不长,虽然画几块板子,和protel 相比有很多不同的地方。

比如在protel PCB中想删除某几个连线,如果全选,就把过孔什么的全选,而在cadence中,是把net text via 等作为不同的属性,任何操作必须制定对象,如移动、删除、查找,必须有确定的类型;使用cadence很不习惯的一点是在连线以及过孔中没有显示网络标号,想知道输入什么还得点击一个显示的操作,而且不能全部显示,而在protel中,过孔以及连线是什么net一目了然。

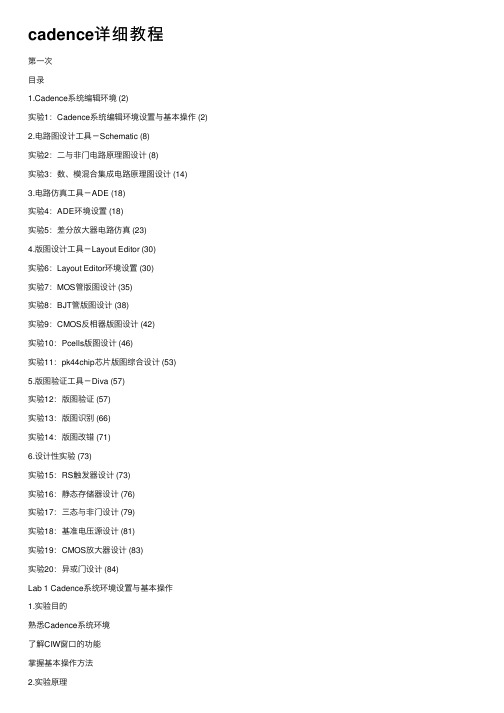

cadence详细教程

cadence详细教程第⼀次⽬录1.Cadence系统编辑环境 (2)实验1:Cadence系统编辑环境设置与基本操作 (2) 2.电路图设计⼯具-Schematic (8)实验2:⼆与⾮门电路原理图设计 (8)实验3:数、模混合集成电路原理图设计 (14)3.电路仿真⼯具-ADE (18)实验4:ADE环境设置 (18)实验5:差分放⼤器电路仿真 (23)4.版图设计⼯具-Layout Editor (30)实验6:Layout Editor环境设置 (30)实验7:MOS管版图设计 (35)实验8:BJT管版图设计 (38)实验9:CMOS反相器版图设计 (42)实验10:Pcells版图设计 (46)实验11:pk44chip芯⽚版图综合设计 (53)5.版图验证⼯具-Diva (57)实验12:版图验证 (57)实验13:版图识别 (66)实验14:版图改错 (71)6.设计性实验 (73)实验15:RS触发器设计 (73)实验16:静态存储器设计 (76)实验17:三态与⾮门设计 (79)实验18:基准电压源设计 (81)实验19:CMOS放⼤器设计 (83)实验20:异或门设计 (84)Lab 1 Cadence系统环境设置与基本操作1.实验⽬的熟悉Cadence系统环境了解CIW窗⼝的功能掌握基本操作⽅法2.实验原理系统启动Cadence系统包含有许多⼯具(或模块),不同⼯具在启动时所需的License 不同,故⽽启动⽅法各异。

⼀般情况下涉及到的启动⽅式主要有以下⼏种,本实验系统所⽤到的有icms、icfb、layoutPlus等。

①前端启动命令:表1.1 前端启动命令命令规模功能icde s 基本数字模拟设计输⼊icds s icde以及数字设计环境icms s 前端模拟、混合、微波设计icca xl 前端设计加布局规划②版图⼯具启动命令表1.2 版图⼯具启动命令命令规模功能Layout s 基本版图设计(具有交互DRC功能)layoutPlus m 版图设计(具有⾃动化设计⼯具和交互验证功能)③系统级启动命令表1.3 系统级启动命令命令规模功能swb s PCB设计msfb l 混合型号IC设计icfb xl 前端到后端⼤多数⼯具CIW窗⼝Cadence系统启动后,⾃动弹出“what’s New…”窗⼝和命令解释窗⼝CIW (Command Interpreter Window)。

cadence中文详细教程

第一章. Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 1-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图1-1-1所示:图 1-1-1Candence 主窗口 二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

并点击后面的按钮,在弹出菜单中选择command tool 。

确认选择完毕后,点击run !3)在提示符ZDASIC22> 下键入:setenv DISPLAY 本机ip:0.0(回车)4)在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键)即进入cadence 中。

出现的主窗口如图1-1-1所示。

以上是使用xstart 登陆cadance 的方法。

在使用其他软件登陆cadance 时,可能在登录前要修改文件.cshrc ,方法如下:在提示符下输入如下命令:vi .cshrc ↙ (进入全屏幕编辑程序vi )将光标移至setevn DISPLAY ZDASIC22:0.0 处,将“ZDASIC22”改为PC 机的IP ,其它不变(重新回到服务器上运行时,还需按原样改回)。

改完后存盘退出。

然后输入如下命令: source .cshrc ↙ (重新载入该文件)以下介绍一下全屏幕编辑程序vi 的一些使用方法:vi 使用了两种状态,一是指令态(Command Mode ),另一是插入态(Insert Mode )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、cadence软件及安装指导1、安装虚拟机,安装过程中需要添加vmware7.0sn.txt中的Serial(注意:一旦安装成功不要轻易卸载,否则重装很费劲)2、在windows下解压cadence文件夹下压缩包3、双击桌面虚拟机图标,打开虚拟机,点击界面左上角FILE》》open》》在弹出的对话框内找到刚刚解压的cadence文件夹下的cadenceEDA.vmx文件,点击“打开”4、点击power on this virtual machine ,输入用户名zyx,密码1234565、我们进入到了linux系统。

二、NCSU TSMC0.25um库的加载及cadecne的环境配置1、直接将文件夹ncsu-cdk-1.5.1拷贝到linux系统桌面。

(若直接复制不成功,可通过U盘将其导入。

)2、打开桌面zyx’ Home目录(即文件夹),在里面新建目录VLSI,将桌面ncsu-cdk-1.5.1剪切至VLSI目录下。

3、在桌面空白处单击鼠标右键,点击open Teminal4、在终端内输入以下命令。

1、su root -------进入到超级用户2、sunface8211200 (不可见,直接输入即可)3、chmod a+w cds.lib ------修改cds.lib权限后,可以对其进行编写4、vi cds.lib --------进入到vi 编辑器,单击键盘“i ”进入到插入模式,在第一行我们添加一行语句。

INCLUDE/home/zyx/VLSI/ncsu-cdk-1.5.1/cdssetup/cds.lib输入完之后,单击键盘“esc”键退出插入模式,再点击键盘“:wq ”退出vi编辑器5、cd VLSI/ncsu-cdk-1.5.1/cdssetup ---------进入到cdssetup目录6、vi cds.lib --------做如下图修改后,点击esc键并输入“:wq ”退出7、csh -------进入到c shell命令8、vi /home/zyx/.cshrc ------进入到用户目录下的 .cshrc的编写,并添加如下语句setenv CDK_DIR /home/zyx/VLSI/ncsu-cdk-1.5.1 ,添加后“:wq ”保存退出9、cp cdsinit /home/zyx/.cdsinit10、cp display.drf /home/zyx/display.drf11、至此,ncsu-tsmc0.25um工艺库安装完毕,cadence环境配置也已经结束。

大家可以关掉终端即可。

三、反相器电路图的搭建及仿真1、打开cadence软件。

单击鼠标右键,打开open terminal输入以下命令csh --------进入C shell (注意:大家要在用户目录/home/zyx下启动cadence)icfb & --------启动cadence软件2、建新库,在库里面我们将画出反相器电路图和版图两个cell。

①在CIW(command interpreter window,即命令解释窗)中,点击File→New→Library...;②在New Library对话框内输入库名,例如cell_lib_tsmc03;并在Technology File 中选择第二项,Attach to an exiting techfile,然后点击Technology Library中NCSU_TechLib_tsmc03,点击OK,最终将在CIW中提示成功。

3、建立新文件,先画反相器电路图①在CIW中,选File→New→Cell view...,=>“Create New File”对话框。

②在Library Name,选刚建的库cell_lib_tsmc03, ③在Cell Name中输入单元名INV,④点击Tool文本区右端的按钮,出现下拉菜单。

选择Composer-Schematic,在View Name内自动生成Schematic。

⑤按OK键=>“Virtuoso Schematic Editing”(电路图编辑窗)。

4、加器件①选命令Add→Instance...<i>,出现“Add Instance”对话框。

②点击Browse按钮,出现Library Browser ,在library一栏中选择NCSU_Analog_Parts,库中包含花振荡器的所有cell,如pmos4,nmos4,vdd,gnd,如图选择nmos4,再点击HIDE,将器件添加即可。

③修改器件尺寸,选中器件,即将鼠标单击器件,若器件被白色方框包围,则代表选中。

按字母q,进行修改,如图,我们修改pmos4,设置l=300n,w=4500n,类似我们修改nmos4,设置l=300n,w=2700n5、连线。

点击图标,或直接点击字母w。

6、添加反相器输入、输出引脚①点击屏幕左下方按钮,如图添加输入引脚in,同理,添加输出引脚output,需要注意的是在Direction处选择output,我们可以命名为out。

②结果如下图7、检查并存盘。

即点击图标。

观察CIW中是否出现error。

8、建立symbol,目的是以后用到反相器可以直接调用。

大家也可以选择Add→Shape,在里面选择所需的图形进行手工绘画。

想要修改图形格点间距选择Options,在里面进行修改。

9、进行INV的电压传输特性曲线的仿真A 创建新的library,命名为testbench_tsmc03,在Technology File处选择Don’t need a techfile 。

B 在新建的testbench_tsmc03库下建立新的文件INV_test。

C 在INV_test里面添加我们刚刚创建的INV,方法如下D 我们再按照以上的方法依次添加NCSU_Analog_Parts里面的vdc、vdd、vpulse、cap和gnd,并点击字母w进行连线。

E 修改器件的参数。

例选中vpulse,点击字母“q”,按照下图进行修改,注意的是最后DC voltage设置为变量vin V,是为了方便接下来的要进行的DC直流分析。

同理我们修改vdc直流电压为2.5V。

cap 电容值修改为50f F.F 加标记。

点击字母“L”,我们给电路图中的连接输入输出的导线加上标记in和out,添加方法是将in或out下方的小方框置于输入和输出的导线上再单击鼠标左键。

G check and save,若有错误可以在CIW中查看并回到电路图中修改;在没有错误和警告下,点击左上角Tools→Analog environment,我们进入仿真环境ADE。

H 点击ADE中标题栏Setup→Simulator/Directory/Host…,在弹出的对话框中,我们在Simulator处选择spectre 作为仿真工具I 设置仿真库,如图点击setup,菜单下选择model libraries,在出现的对话框内直接输入/home/zyx/VLSI/ncsu-cdk-1.5.1/models/spectre/standalone/tsmc25N.m,点击Add,再次输入/home/zyx/VLSI/ncsu-cdk-1.5.1/models/spectre/standalone/tsmc25P.m,点击Add,最后点击ok 。

注意:也可以点击Browse直接找。

J 设置vpulse直流电压vin,如图,将其设置为2.5K 设置仿真类型。

点击ADE中标题栏Analyses→Choose。

在弹出的对话框中,选择Analysis 为tran,在Stop Time 处设置为20n。

在单击Analysis处dc,在弹出的对话框中做如下修改。

L 在图中选择要仿真的连接反相器输入和输出的导线。

点击ADE菜单栏中Outputs→To Be Plotted→Select On SchematicM 点击ADE中输出仿真结果。

N 查看输出波形。

四、反相器版图绘制及验证1、在cell_lib_tsmc03库下建立新文件。

此时在Tool处选择Virtuoso。

2、如图,会出现LSW和Layout Editing,在LSW中将所有的层选中。

3. 使用Option菜单进行版图编辑窗设置。

选命令Option→Display…<e>,出现“Display Options”对话框。

在Grid Controls处,4个参数的缺省设置为1、5、0.075和0.075。

我们可设置为0.075 、0.15 、0.075 、0.075。

(最小设计尺寸λ=0.15)4、画反相器版图。

画版图时要严格遵循设计规则(tsmc0.25rule.pdf),即满足最小间距,最小包围、最小延伸、最小宽度等。

下图为反相器版图的最终图形。

A. 画pmos管。

先放大layout editing桌面,即一直按着鼠标右键在桌面出画矩形;若放大桌面过大,可按着shift,并一直按着鼠标右键在桌面出画矩形,实现缩小,或点击字母“f ”适中。

在lsw中选择pactive (选择后缀为drw,即drawing绘图,其它层类似,选drw)作为输入层,再选画矩形的命令(按字母r ),在屏幕中央画有源区矩形。

竖直距离(W)设置为4.5um,可用直尺命令(左下角Ruler,或字母k,去除直尺可用“shift+k”)进行测量,水平距离(L)设置1.8um。

若不小心画多了,可按字母s ,进行修剪。

(这里w设置为4.5um 为先前设计反相器电路图中pmos的尺寸,大家可以根据自己的实际情况画图)B. 画多晶硅栅极。

多晶硅位于有源区中部,即离有源区左边0.75um,也为矩形。

栅长为0.3 um.可用直尺命令(左下角Ruler)进行测量。

多晶伸出有源区不小于0.3 um.如下图。

注意,要严格按照设计规则来画,不然DRC时会报错。

C. 画源区和漏区接触孔。

输入层在LSW 中选择ca ,后缀drw ,也为矩形,大小为0.3um ×0.3um 。

画完一个接触孔,其它的用复制(点击键盘字母 C ,再选中器件)即可,每个接触孔间距设置为不小于0.45um 。

若不满足可将其移动 (点击键盘字母 M )。

D. 在有源区外画P+注入的矩形。

即选择pselect层,满足最小包围,并且它离gate栅极要至少0.3um。

E.在P+注入区外再画nwell的矩形,为满足最小包围,nwell要离contact 0.9um。

如图。

到此为止,除了金属连线,pmos基本完成。

F . 画nmos 管。

因为nmos 和pmos 差不多,可将pmos 管包括pselect 以内的层复制过去,并加以修改即可。

1.修改有缘区W 为2.7um 。