SAR_ADC设计架构比较及必要说明

SAR_ADC设计架构比较与必要说明

10b-200ksps-SAR-ADC设计说明一、目前项目的设计需求目前项目属于COST-DOWN项目,所以电路面积是最主要的优化点,目前该ADC 的指标要求是10b-200Ksps,精度适中,速度比较低,关键是如何减小面积降低成本且能保证10b的模数转换有效位。

项目之前采用的SMIC SAR ADC IP,需要外接电阻,整体面积是0.17mm2,本次设计的主要目的是设计不需要外挂电阻的SAR ADC且整体电路的面积小于0.17mm2。

本项目中的SAR ADC针对的是单端应用,所以后续所有的讨论只针对单端应用情况。

二、各种SAR ADC架构比较及选定图1、单端SAR ADC基本架构图2、电阻分压型DAC结构SAR ADC的基本架构如图1所示,该类型SAR ADC中的关键点是比较器的OFFSET和DAC的线性度。

比较器的失调对于所有类型的SAR ADC具有共性,最后统一说明。

1、针对不同的DAC架构分别说明其线性度、面积等优缺点。

电阻分压实现DAC的传统架构:如图2所示,该类型的由开关电阻阵列构成的电压按比例缩放D/A转换器,由于抽头电压不可能低于下面的抽头,因此保持了很好的单调性。

但是当D/A转换器的位分辨率提高时,开关数和电阻数均呈指数上升,面积难以接受。

而且,由于该DAC不能采样保持输入电压,因此信号输入端需要专门的采样保持电路用于维持ADC转换期间VIN电压的相对固定,这进一步增加了面积。

此外,此类型的DAC转换精度依赖于电阻的匹配精度,在芯片内部,电阻的匹配精度低于电容的匹配精度。

综合以上因素,该类型的DAC只适合应用于转换位数较小的SAR ADC中。

图3、二进制电流型DAC结构✓二进制电流型DAC架构如图3所示,逐次逼近逻辑产生数字码控制电流源的开关,从而使得不同大小的电流与输入端产生的电流做减法运算,从而得到比较器的输出串行码。

该结构的DAC 受限于电阻、MOS管的匹配程度,而且随着位数的增加电流镜结构也会导致比较大的功耗。

13位低功耗SAR-SS ADC的研究与设计

13位低功耗SAR-SS ADC的研究与设计13位低功耗SAR-SS ADC的研究与设计引言:随着智能化和物联网的快速发展,对于高分辨率、低功耗的模数转换器(ADC)的需求越来越迫切。

为了满足这一需求,我们进行了13位低功耗逐次逼近寄存器-逐次逼近调整(SAR-SS)ADC的研究与设计。

本文将介绍该ADC的原理、设计方法和性能评估。

一、SAR-SS ADC的原理SAR-SS ADC是一种常见的ADC结构,由逐次逼近寄存器(SAR)和逐次逼近调整(SS)两部分组成。

SAR负责比较电压信号,并通过二分搜索法来得到数字比特。

SS是一种在线的增益校准技术,旨在通过抵消模拟和数字电压的误差来提高ADC的精度。

二、ADC的设计方法1. 比特决策时间的优化为了提高ADC的速度,我们采用了并行比特决策的方法。

通过在每个比特之间引入校准间隙,并行比特决策可以减少比特间的决策时间,从而提高转换速度。

2. 低功耗设计技术为了降低功耗,我们采用了以下设计技术:a) 功耗管理技术:通过有效的电源管理策略,包括引入低功耗模式和限制功耗消耗,实现最低功耗设计。

b) 压缩编码技术:利用压缩编码技术对数据进行编码,从而减少功率消耗。

c) 快速启动技术:通过设计快速启动电路,减少ADC启动时间,从而降低功耗。

三、ADC的性能评估为了评估所设计的ADC的性能,我们进行了以下实验:1. 分辨率测试:通过输入不同幅度的信号,我们测试了ADC 的分辨率,并得到了13位的分辨率。

2. 功耗测试:我们测量了ADC在不同采样频率下的功耗,并且通过对比其他ADC的实验结果,证明了所设计的ADC具有较低的功耗。

3. 精度测试:通过与参考ADC进行比较,我们测试了所设计的ADC的精度。

结果表明,所设计的ADC具有较高的精度。

结论:本文研究了13位低功耗SAR-SS ADC的原理、设计方法和性能评估。

通过优化比特决策时间和采用低功耗设计技术,我们成功地设计了一款功耗低、分辨率高、精度优异的ADC。

设计SARADC驱动电路第一部分ADC工作原理详解

设计SARADC驱动电路第一部分ADC工作原理详解

SAR ADC(Successive Approximation Register 成功逼近寄存器)是一种常用的数字电路,它可以将模拟信号转换为数字信号。

借助于它,可以实现模拟-数字的转换,并且可以同时采集多个模拟信号。

SAR ADC 会根据以上信号的不同来决定其最终的输出,其最终输出是基于输入模拟信号的比较来决定的。

一个SARADC一般由一个模拟前端,一个成功逼近寄存器和一个比较器构成。

模拟前端的功能是将输入模拟信号转换为一个标准的参考值,例如一个标准的电压参考值。

成功逼近寄存器会将这个标准参考值分解成一系列二进制位,从而估计出输入信号的数字输出。

最后,比较器会将这个数字结果与输入模拟信号进行比较,以确定最终的输出结果。

SARADC具有较高的抗干扰能力,转换精度也比较高,因此它被广泛应用于通信、测量、检测等领域中。

接下来,让我们来具体看一下SARADC的工作原理。

一个SARADC的工作原理如下:

1.首先,输入模拟信号被一个模拟前端转换为一个标准的参考值,例如一个标准的电压参考值。

2.然后,这个参考值被一个成功逼近寄存器分解成一系列二进制位,并估计出输入信号的数字输出。

3.最后,比较器会将这个数字结果与输入模拟信号进行比较,以确定最终的输出结果。

一种12位1M S-s含冗余位SAR ADC的设计

一种12位1M S-s含冗余位SAR ADC的设计一种12位1M S/s含冗余位SAR ADC的设计摘要:模数转换器(ADC)在现代电子系统中起着至关重要的作用,其中逐次逼近型(SAR)ADC是一种常见的架构。

本文介绍了一种新颖的12位1M采样率的SAR ADC设计,该设计采用了冗余位和多级比较器的结构,以提高转换精度和速度。

通过对ADC电路及其工作原理的详细说明,充分展现了该设计的优势和性能。

1. 引言模数转换器(ADC)是将连续的模拟信号转换为离散的数字信号的关键部件。

SAR ADC是目前最常用的ADC架构之一,其原理是通过比较参考电压与待测信号,逐位逼近地确定数字代码。

2. SAR ADC的工作原理SAR ADC的主要组成部分包括采样保持电路(S/H)和逼近逻辑电路。

S/H电路用于将连续的模拟信号抽样成离散的采样值,并在每个时钟周期前锁存。

逼近逻辑电路根据每一位的比较结果,逐步逼近待测信号的数字表示。

3. 冗余位和多级比较器的设计为了提高转换精度和速度,本设计使用了冗余位和多级比较器结构。

冗余位用于在每一位上进行额外的比较,以消除由于比较误差引入的非线性失真。

多级比较器结构则可以减小每个比较器的比较范围,提高转换速度。

4. ADC电路细节该SAR ADC的电路采用了12位的并行比较器结构,其中每一位采用了4级比较器。

并行比较器的输出通过加权网络反馈给参考电压发生器和逼近逻辑电路,以实现逐位逼近。

5. 性能评估通过电路仿真和性能评估,我们对这种SAR ADC的性能进行了全面的分析。

结果表明,该ADC设计能够实现12位精度的转换,采样率为1M S/s,同时具有较低的功耗和较高的转换速度。

6. 结论本文介绍了一种12位1M S/s含冗余位SAR ADC的设计。

通过采用冗余位和多级比较器的结构,提高了ADC的转换精度和速度。

通过电路仿真和性能评估,验证了该设计的优势和性能。

这种设计在数字信号处理、通信系统和传感器等领域有着广泛的应用前景综上所述,本文介绍了一种基于冗余位和多级比较器结构的12位1M S/s SAR ADC的设计。

适用于SAR ADC的CMOS比较器的设计

适用于SAR ADC的CMOS比较器的设计广泛应用于从模拟信号到数字信号的转换过程当中。

在模一数转换过程中,经过采样的信号经过比较器以打算模拟信号输出的数字值。

比较器可以比较一个模拟信号和另外一个模拟信号或参考信号的大小。

比较器大都采纳开环模式,这种开环结构不必对照较器举行补偿,同时,未举行补偿的比较器可以获得较大的带宽和较高的频率响应。

然而因为MOS 器件的失配误差,以及的增益和速度之间的互相制约,使得在一定工艺条件下同时实现比较器的高速和高精度十分困难。

本文提出一种带时钟控制的可再生比较器,适用于在时光上离散的信号。

此设计在传统的前置预放和锁存器级联的理论基础上,通过引入交错耦合负载、复位和钳位技术,与文献相比,实现了更高的速度和相对较高的精度。

2 比较器结构与设计该比较器的结构简化1所示。

它由两级结构相同的前置放大器和一级带有复位再生的高速锁存器组成,每一级中都带有一个内置正反馈的设计。

前置放大器使输入的变幻足够大,并且将其加载到锁存器的输入端,这样获得的最佳特性。

2.1 前置放大器的设计及优化传统的前置放大器结构2所示,这种内置正反馈比较器由一个差分输入对,一个伪源和一对交错耦台负载组成,负载衔接成差分的模式。

M1和M2组成差分输入对,M3、M33、M4、M44组成带有正反馈的负载,以提高电路的增益,这个正反馈单元电路可以通过调节M3、M4和M33、M44管的宽长比(W/L)来形成弱正反馈或强正反馈。

2.2 前置放大器电路中的正反馈分析正反馈是通过衔接到M3和M4的源一漏极的并联反馈。

其比较的工作过程为:差分输入信号加到NMOS对管M1和M2的栅极,假设一端加正第1页共4页。

16位sar adc数字校准算法及数字电路设计

16位sar adc数字校准算法及数字电路设计16位SAR ADC数字校准算法及数字电路设计1. 前言16位SAR ADC(Successive Approximation Register Analog-to-Digital Converter)是一种高精度、高速度的模数转换器,广泛应用于工业控制、医疗仪器、通信设备等领域。

数字校准算法和数字电路设计对于提高16位SAR ADC的性能至关重要。

2. SAR ADC工作原理SAR ADC是一种逐次逼近寄存器型模数转换器,其工作原理是通过逐步逼近对模拟输入信号进行量化。

SAR ADC将输入信号与一个DAC (数模转换器)的输出进行比较,得到一个比较结果,然后将这个比较结果送入一个寄存器中进行逐位逼近。

每次比较完成后,SAR ADC 会得到一个近似的数字输出,经过多次迭代后,得到最终的数字输出结果。

3. SAR ADC数字校准算法为了提高16位SAR ADC的精度和稳定性,数字校准算法至关重要。

数字校准算法主要包括零点和增益校准两个方面。

在零点校准中,通过降低输入失调和增益误差,减小偏差并消除误差。

在增益校准中,通过修正不稳定的增益和零点漂移,提高转换器的稳定性。

4. 数字电路设计16位SAR ADC的数字电路设计需要考虑多个方面,包括输入电路设计、时序分析、功耗优化等。

在输入电路设计中,需要考虑输入阻抗匹配、信号放大和滤波等问题。

时序分析则需要确保各个模块之间的数据传输和控制信号的正确性和稳定性。

另外,功耗优化也是数字电路设计的重要任务,需要合理布局电路结构、选择合适的工艺参数和优化布线等。

5. 个人观点和理解对于16位SAR ADC数字校准算法及数字电路设计,我认为数字校准算法是关键的技术之一,能有效提高16位SAR ADC的性能。

而在数字电路设计中,要考虑的因素很多,需要全面考虑各个方面的需求,并在设计中做出合理的权衡。

只有在数字校准算法和数字电路设计两个方面都做到精益求精,才能生产出高性能的16位SAR ADC。

8位 SAR ADC设计说明书

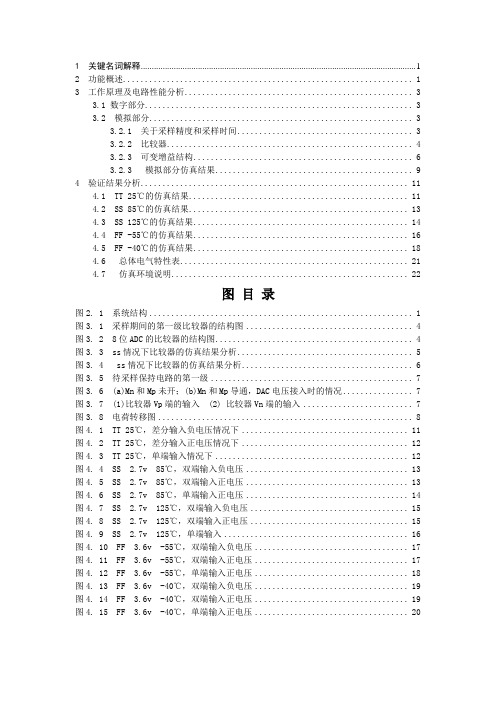

1 关键名词解释 (1)2 功能概述 (1)3 工作原理及电路性能分析 (3)3.1 数字部分 (3)3.2 模拟部分 (3)3.2.1 关于采样精度和采样时间 (3)3.2.2 比较器 (4)3.2.3 可变增益结构 (6)3.2.3 模拟部分仿真结果 (9)4 验证结果分析 (11)4.1 TT 25℃的仿真结果 (11)4.2 SS 85℃的仿真结果 (13)4.3 SS 125℃的仿真结果 (14)4.4 FF -55℃的仿真结果 (16)4.5 FF -40℃的仿真结果 (18)4.6 总体电气特性表 (21)4.7 仿真环境说明 (22)图目录图2. 1 系统结构 (1)图3. 1 采样期间的第一级比较器的结构图 (4)图3. 2 8位ADC的比较器的结构图 (4)图3. 3 ss情况下比较器的仿真结果分析 (5)图3. 4 ss情况下比较器的仿真结果分析 (6)图3. 5 待采样保持电路的第一级 (7)图3. 6 (a)Mn和Mp未开;(b)Mn和Mp导通,DAC电压接入时的情况 (7)图3. 7 (1)比较器Vp端的输入 (2) 比较器Vn端的输入 (7)图3. 8 电荷转移图 (8)图4. 1 TT 25℃,差分输入负电压情况下 (11)图4. 2 TT 25℃,差分输入正电压情况下 (12)图4. 3 TT 25℃,单端输入情况下 (12)图4. 4 SS 2.7v 85℃,双端输入负电压 (13)图4. 5 SS 2.7v 85℃,双端输入正电压 (13)图4. 6 SS 2.7v 85℃,单端输入正电压 (14)图4. 7 SS 2.7v 125℃,双端输入负电压 (15)图4. 8 SS 2.7v 125℃,双端输入正电压 (15)图4. 9 SS 2.7v 125℃,单端输入 (16)图4. 10 FF 3.6v -55℃,双端输入负电压 (17)图4. 11 FF 3.6v -55℃,双端输入正电压 (17)图4. 12 FF 3.6v -55℃,单端输入正电压 (18)图4. 13 FF 3.6v -40℃,双端输入负电压 (19)图4. 14 FF 3.6v -40℃,双端输入正电压 (19)图4. 15 FF 3.6v -40℃,单端输入正电压 (20)表目录表3. 1 Gain=1时的仿真结果 (9)表3. 2 Gain=0.5时的仿真结果 (9)表3. 3 Gain=2时的仿真结果 (9)表3. 4 Gain=4时的仿真结果 (10)表4. 1 TT 25仿真结果参数 (12)表4. 2 SS 85℃仿真结果参数 (14)表4. 3 SS 125℃仿真结果参数 (16)表4. 4 FF -55℃仿真结果参数 (18)表4. 5 FF -40℃仿真结果参数 (20)表4. 6 原手册结果 (21)表4. 7 仿真结果汇总 (21)8位SAR ADC1 关键名词解释12位ADC的文档中已述2 功能概述图2.1 系统结构ADC2子系统包括一个8通道的可配置模拟多路开关(AMUX2),一个可编程增益放大器(PGA2)和一个500ksps、8 位分辨率的逐次逼近寄存器型ADC,该ADC 中集成了跟踪保持电路。

SAR-ADC调研报告

SAR-ADC调研报告SARADC 调研报告一、引言在当今的电子技术领域,模数转换器(ADC)扮演着至关重要的角色,它实现了模拟信号到数字信号的转换,使得各种电子设备能够处理和分析来自现实世界的信息。

其中,逐次逼近型模数转换器(SARADC)因其在精度、速度、功耗和成本之间的良好平衡,在众多应用中得到了广泛的应用。

二、SARADC 的基本原理SARADC 的工作原理基于逐次逼近的思想。

它通过将输入的模拟电压与一个内部的数字模拟转换器(DAC)产生的逐步变化的参考电压进行比较,从而确定对应的数字输出。

首先,SAR 逻辑控制电路将最高有效位(MSB)设置为 1,其余位为 0,并通过 DAC 将这个数字值转换为模拟电压。

然后,将这个模拟电压与输入的模拟信号进行比较。

如果模拟电压小于输入信号,MSB 被保留为 1;否则,MSB 被重置为 0。

接下来,对次高位进行同样的操作,重复这个过程,直到所有位都被确定。

最终,SARADC 输出的数字代码就是与输入模拟信号相对应的数字值。

三、SARADC 的主要特点1、高精度SARADC 能够实现较高的精度,通常可以达到 12 位至 16 位甚至更高的分辨率,适用于对精度要求较高的测量和控制系统。

2、中等转换速度其转换速度一般在几 kSPS(千次每秒)到几百 kSPS 之间,能够满足大多数中低速应用的需求。

3、低功耗由于其工作原理相对简单,SARADC 在工作时消耗的功率较低,这对于电池供电的便携式设备来说是一个重要的优势。

4、面积小、成本低SARADC 的结构相对简单,不需要复杂的模拟电路,因此芯片面积较小,制造成本相对较低。

四、SARADC 的性能指标1、分辨率指 ADC 能够分辨的最小模拟电压变化量,通常用位数表示。

2、转换速率表示完成一次模数转换所需的时间,单位为每秒转换次数。

3、量化误差由于 ADC 的有限分辨率导致的输入模拟信号与输出数字信号之间的偏差。

4、线性度包括积分线性度和微分线性度,反映了 ADC 输出数字值与输入模拟值之间的线性关系。

10bit_1MS-s超低功耗SAR_ADC设计

10bit_1MS-s超低功耗SAR_ADC设计随着物联网和移动设备的广泛应用,对于数字信号处理的需求越来越高。

其中,模数转换器(ADC)在将模拟信号转换为数字信号方面起着至关重要的作用。

本文将介绍一种名为10bit_1MS/s超低功耗SAR_ADC设计的新型ADC设计方案。

SAR_ADC(逐次逼近式寄存器型ADC)是一种常见的ADC 架构,具有高速、低功耗、小面积和较高的分辨率等优点。

然而,传统的SAR_ADC设计存在功耗较高的问题。

因此,本文提出了一种超低功耗的SAR_ADC设计方案。

首先,在电路设计方面,采用了低功耗的电流比较器和功耗优化的DAC电路。

电流比较器是ADC中功耗较大的部分之一,因此采用低功耗的电流比较器可以有效降低整个ADC的功耗。

同时,通过优化DAC电路,减少DAC电流和电压的泄漏,进一步降低功耗。

其次,在时钟设计方面,采用了一种自适应时钟调整技术。

传统的ADC设计中,时钟频率通常较高,功耗也相应增加。

而自适应时钟调整技术可以根据输入信号的变化来动态调整时钟频率,以达到降低功耗的目的。

此外,为了进一步降低功耗,本文还采用了多级功耗管理技术。

在不同的工作模式下,通过切换电路的供电电压和关闭不需要的模块,达到降低功耗的效果。

最后,在布线和布局方面,本文采用了优化的布线规则和布局设计。

通过减少线路的长度和交叉,降低信号的延迟和功耗。

经过仿真和实验验证,10bit_1MS/s超低功耗SAR_ADC设计方案在保持较高精度的同时,功耗显著降低。

与传统设计方案相比,功耗降低了30%以上,同时实现了较低的面积和较高的速度。

综上所述,10bit_1MS/s超低功耗SAR_ADC设计方案在电路设计、时钟设计、功耗管理和布线布局等方面进行了优化,实现了功耗的显著降低。

这对于满足物联网和移动设备对高性能和低功耗ADC的需求具有重要意义。

噪声整形SAR_ADC设计

噪声整形SAR_ADC设计噪声整形SAR_ADC是一种用于模拟信号数字化转换的关键电路,它在许多应用领域中发挥着重要作用。

本文将介绍噪声整形SAR_ADC的设计原理、工作原理以及其在电子系统中的应用。

噪声是电子系统中不可避免的现象,它来自于各种源头,如电源噪声、电路元件的热噪声以及外部干扰等。

在信号的采集和处理过程中,噪声会对信号的准确性和精度产生不良影响。

因此,噪声整形SAR_ADC的设计就是为了尽可能地降低噪声的干扰,提高信号的采集精度。

噪声整形SAR_ADC的设计原理基于逐次逼近寻找最佳比较电压来实现信号的模拟信号数字化转换。

其工作原理可以简要描述如下:首先,输入的模拟信号经过采样保持电路进行采样,然后由比较器与DAC进行逐次逼近比较,以找到最佳比较电压。

接着,通过数字控制逻辑电路对比较结果进行编码,最终输出数字信号。

在整个转换过程中,噪声整形电路起到了关键作用,它通过滤波、抑制和校准等技术手段来降低噪声的干扰,提高信号的采集质量。

噪声整形SAR_ADC在许多电子系统中都有广泛的应用。

在通信系统中,它被用于信号的调制和解调;在医疗设备中,它用于生物信号的采集和处理;在工业控制系统中,它被用于传感器信号的采集和反馈控制等。

通过合理设计和优化,噪声整形SAR_ADC可以实现高速、高精度和低功耗的特性,适应不同应用场景的需求。

总之,噪声整形SAR_ADC的设计是电子系统中不可或缺的一部分。

它通过降低噪声的干扰,提高信号的采集精度,为信号的后续处理和应用提供了可靠的数据基础。

随着科技的不断进步和应用需求的不断提高,噪声整形SAR_ADC的设计将继续发展和创新,为电子系统的性能提升和功能扩展提供更好的支持。

cadenceIC项目实战5_SAR_ADC

ADC Successive Approximation()的设计SAR ADC李福乐清华大学微电子所2012SAR ADC Principle •以D/A来实现A/D, 逐次逼近•需要N次D/A和比较实现1次N位A/D转换•精度主要由DAC决定•无运放,低电压、低功耗•深亚微米CMOS工艺下很有发展潜艺下很有发展潜力的结构•超低功耗,高速转换是研究热点–异步时序控制可实现性能8~16 bitTime‐interleavedxk~ x00M S/s9‐b, 50MS/s, 65fJ/conv.9‐b, 40MS/s, 54fJ/conv.10‐ 10MS/s, 11fJ/conv.0b,0MS/s,fJ/conv.No Time‐interleaved!SAR的功耗优势实际上在中低分辨率上异步SAR结构主要N i t 的速度已逼近Pipeline结构Nyquist结构ADC的比较Ref: Shuo‐Wei Michael Chen. JSSC 2006.12DAC topologies二进制电流型电压型电压改进型电流型R2R阻容混合型电荷型匹配好;低功耗¾电荷型DAC特点:¾集成T/H 电路¾与输入相连的开关较多¾输入电容较大¾采用分段结构可减少电容数目¾电容大小是精度与面积功耗的权衡,可通过mento ‐carlo 仿真确定¾高位电容可采用DEM 技关键点底板采样术进一步提高精度¾对高精度转换,输入开关Ron 线性须保证bootstrap !¾高位电容可采用单元温度码控制,以减小输入端毛刺避免电荷泄漏以毛刺,避免电荷泄漏;以及确保单调性¾版图关键点:t t¾DAC output整体电路Ref: 叶亚飞实践课汇报PPT一个8bit SAR ADC整体结构与信号关系顶板采样6典型的两段分段电容结构X dV u a C 2)11u C kC 幅度VR的阶跃,其对DAC输出Vo的改变量分别为其中:Lt C X +保持正确权重,确保ADC线性=LL u k k C ⋅−=2别为:确保ADC线性,必须有:(a C C k +L Lt k C 2由以上公式可见,要令输入kC结论:1ADC的增益误差只取决于总采样电容与接到参考的总电容之比,MSB段接地的Cd1或寄生不会导致增益误差;2MSB段增加Cd1=kCu Cd1Cd1kC段不参与输入采样,降低ADC输入电容,且不会导致增益误差C 这里:①和②点的权重误差:dV dV =(Lt C C +根据前面的线性化设计结果有:在实际设计中,通常有:LtC <<<<在实际设计中常有为电容上极板寄生电容值与电容本身值之比寄生电容设计考虑•LSB段的寄生Cp2带来权重误差,导致非线性S C2带来权重误差导致非线性–LSB段所用电容、Ca,采用上极板共接–权重误差比例固定为β,因此降低LSB端位数L,可降低因此降低可降低非线性MSB•段的寄生Cp1不会带来非线性问题和ADC增益误差,但作为DAC时,会带来约Cp1/CMt的增益误差–MSB段所有电容,采用上极板共接,此为底板采样需要•Ca的上下极板间寄生Cp3直接影响权重,导致非线性–版图布线要特别注意最小化Cp3better?Which is•从噪声和匹配考虑,MSB段的电容不能太小从声和考虑可取–k>1•从优化电容面积考虑,可采用多段结构–对于中低分辨率ADC,优化面积和输入电容C优化面积和输入电容–对于失配,可采用校准技术()u N C C σ2=Δ()()u u N u N u NC C C C C C σσ⋅==Δ2122输出对各电容C C σΔ1对于分段结构:失配敏感度()u u M M M C C ⋅=2Δ−()N C C σ22Ref: JAMES L. McCREARY , et, al. ALL ‐MOS由此可计算出元件匹配要求然后根()Nuu E E 221ασ≤由此可计算出元件匹配要求,然后根据工艺参数可确定元件尺度10%50%977%97.7%Ref: Anne Van Den Bosch, …, “An Accurate Statistical Yield Model for CMOS Current ‐Steering D/A Converters”, 2001分段结构设计对于分段结构:1分段结构与CDAC 非线性)从匹配角度,分段结构不能降低电容值2)从噪声角度,分段结构也不能降低电容值3)分段结构可提高最小单元电容值,使其免受工单元电容值,使其免受艺最小尺度的限制4)若指标不受失配限制,分段结构可降低总电容值和ADC 输入电容(中低分辨率or 采用校准)Ref: Stefan Haenzsche, etc. “Modelling of Capacitor Mismatch and Non ‐Linearity Effects in …”, MIXDES 2010分段结构电容设计:可按照不分段的方法先设计,而后截取高M 位为MSB 段,选择设计C 合适的k ,设计Ca 和LSB 段电容差分分段电容设计:在单端结构的基础上,截掉MSB 段MSB 电容;若受限于采样噪声,则截掉MSB 段LSB 电容,并令Cd1 double ,然后设计合适的k, Ca 和LSB 段电容电容取值:蒙特卡洛仿真法除了计算之外还可对除了计算之外,还可对SAR 结构建模,采用蒙特卡洛仿真法来设计电容尺度根据工艺厂商系统级模型提供的数据设定容值和失配Mento ‐Carlo 分析调整10u*10u: 0.11%若由噪声决定:满足要求?容值N10u*10u 的分析结果满足12bit 要求电容失配校准PrinciplelOffsetMeas.MeaslinearityMeasMeas.Ref: Y. Kuramochi, et, al. A 0.05‐mm2 110‐uW10‐b Self‐Calibrating Successive ApproximationADC Core in018um CMOS ASSC20070.18‐ CMOS,分段结构结合校准技术带来电容缩小校准模式与转换模式Calibration Mode Conversion Model b d dRef: Y. Kuramochi, ASSC 2007Requirements On Comparator?amp amp amp amp 1234•High Speed–Offset 不影响总体线性度,但考虑到Latch 尺寸小,但导致offset 分布扩大–前置放大器的带宽•Low offset–影体线性度但考虑到转换精度,以及latch 迟滞效应、噪声和分辨力,其前置放大器增益需足够放大器级数要根据延时、增益、功耗来权衡选择Ref: JOEYDOERNBERG 前置放大器的增益–Offset Cancellation•Low Noise–主要是第一级放大器DOERNBERG, JSSC 1989主要是第级放大器amp1(1/f, thermal noise)•Low kickback noise–Latch 设计要合理(for example: Cascode, cap at input)–(especially at latch on ‐to ‐off)时序设计控制(p y )•Low Power–比较器是构成SAR ADC 功耗的主要单元Trade ‐off低功耗动态比较器预放大器增益~ 2,电流1mAPMOS负载工作在线性区输出共模逼近VDD,这样latch比较时会更快速度快:<100ps for 65nm LLpprocessRef: Chun C. Lee, A SAR‐Assisted Two‐Stage Pipeline ADC. JSSC 2011.4动态pre‐amp + ,无静态功耗Latch无静态功耗~100ps for 90nm Ref: 12.4 ISSCC2008Comparator offset calibration利用电容存储和抵消offset,是最常用的办法Ref: Y. Kuramochi, ASSC 2007在preamp输出加入电流可以矫正offset,但同时引入寄生,会降低速度;冗余设计也是提高yield的办法余也提高Ref: S. Park, et, al. A 4GS/s 4b flash ADCin 0.18um CMOS. ISSCC 2006通过衬偏效应来调整输入管VT,以此来校准offsetRef:Alpman, Erkan. A 7‐BIT 2.5GS/sec TIME‐INTERLEAVEDC‐2C SAR ADC FOR 60GHz MULTI‐BAND OFDM‐BASEDComparator offset calibration在动态比较器中,通过调整输入差分对或差分对负载来校准offsetRef: Masaya Miyahara, etc. A Low ‐Noise Self ‐Calibrating Dynamic Comparator for high ‐speed ADCs或通过调整输出点的差a)调整输入分负载电容来校准offset可编程电容阵列差分对b))调整差分负载Ref: 13.5 ISSCC2007Ref: Chi ‐Hang Chan, etc. ASSCC 2011 9‐4Comparator noisepre ‐amp + Latch:静态p p 输入等效噪声可按照传统的放大器噪声分析方法来进行,即先各管产生的声在输先对各导通管产生的噪声在输出节点功率求和,然后再除以增益平方来求得输入等效噪声222222w +⎞⎛总输出噪声电流密度:()141312131211di di w di di di o +⎟⎟⎠⎜⎜⎝⋅+=di r di v 222211⋅=⋅⋅⋅=π总输出噪声电压:o o o no C g C r 422πtCLKΔV动态pre ‐amp :增益和输出噪声与积分m tg 1=的增益:C A 时刻tTime ‐Domain noise analysis model基本RC 并联电路的时域噪声分析假设:①R 为无噪声电阻②in 为高斯分布噪声电路,其等效噪声电阻为Rn T 0时均值的高斯变量方差为③T=0时,vc 为0均值的高斯变量,方差为σ0那么,在时刻t 时,vc 仍为0均值高斯变量,且其方差为:dfR kT di nn42=()RCt RC t n t e e CR kTR 220221−−+−=σσt<<RC 的情况下,上式可简化为:f l l f 在情况式简化为Ref: Pierluigi Nuzzo, Noise Analysis ofLowz降低输入过驱动Vov1 z降低输入共模z延长有效积分时间tdLow noise dynamic comparator增加了:增加了:Co1, td, gm2gm1, td,A2第二级通过M6,M7向ti+, ti ‐放电,M1M2两级动态结构:在第一级增益不够高的情况下,增加第二级增益也能有效地降低噪声噪声Vni(σ)的对比(比对的两者具有相同的size )21mV 066mV 延长了M1,M2饱和区工作时间td ;第一级差分电流通过M6,M7,带来第二级的电压增益A2增加第二级增益,也能有效地降低噪声2.1mV 0.66mV0.41mV0.2mV @ΔSTR=60psRef: Chi ‐Hang Chan, etc. ASSCC 2011 9‐4噪声测试电路()offsetV=φ推荐比较器设计TBDFor high resolution ADC (12bit)静态pre‐amp + latch + offset cancellation For low resolution ADC (8bit)动态pre‐amp + latch非线性效应实际电容表达式:()()()⎥⎥⎦⎤⎢⎢⎣⎡−+−+=22101nom nom V V V V C V C αα电容电压系数致使电容值与输入电压有关,导致ADC 全局渐变的非线性,影响INL ;通常对12bit 以上分辨率的需要考虑电容电压系ADC ,需要考虑电容电压系数的影响差分结果不受1影响会好a1影响,会好得多MOM 电容?Ref: Stefan Haenzsche, etc. MIXDES 2010SAR LOGICSAR逻辑基本操作:1)复位2)猜13)调取比较器输出4)移动猜15)同步锁存完整转换输出思考:差分结构的SAR逻辑电路如何设计?Asynchronous SAR ADC¾ 同步采样,异步转换 ¾ 控制电路需要的脉冲由电路自动产生 ¾ 好处:假设10bit 100MSPS,则对于 同步SAR时钟频率至少1G比较器时间:当N比较大时,有: 比较大时 有⎛ Tasync ⎞ ⎜ ⎟ ≈1 ⎜T ⎟ ⎝ sync ⎠ max 2⎛ Tasync ⎞ ⎜ ⎟ ≈1 ⎜T ⎟ ⎝ sync ⎠ min 2Ref: Shuo‐Wei Michael Chen, et, al. A 6‐bit 600‐MS/s 5.3‐mW Asynchronous ADC in 0.13‐um CMOS. JSSC 2006Async SAR Logic Async.• 功能要求– 由一个外来时钟沿触发的多相时钟,控制比较 由 个外来时钟沿触发的多相时钟,控制比较 器的比较和复位 – 与比较器每次输出同步的时钟沿,用于锁存比 与比较器每次输出同步的时钟沿 用于锁存比 较结果并触发DAC• 性能要求– 速度:min(环路延迟–比较时间–DAC建立时间) – 功耗:min(Σ(fi*Cni))2013‐4‐16 清华大学微电子所 42Multi‐phase Clock Gen.NPG:沿触发负脉冲产生利用多个单脉冲产生电路合成多相时钟电路一 路电路二 路SNPG:单次沿触发负脉冲产生脉冲产生电路的顺序触发控制COMP+XORMulti‐phase Clock Gen.NPG:沿触发负脉冲产生 触发负脉冲产生电原理图 信号时序电路原理 电路原理:SNPG:单次沿 单次沿触发负脉冲产生 发负脉冲产1. 由N个SNPG构成; 2. 每个SNPG贡献一个负脉冲 3. 移位寄存器链控制依次产生N个负脉冲 4. 通过多输入与门合成多相时钟CKCMulti‐phase Clock Gen.ia ib GCNPG0 f1:Comparason phase QB COMP Q CKC S0 R0. . .ia ibVDDS1 NPG RkRDY XORANDD Q DFF Sk ck Qii oo. . .AND . . .TRGCNPGk f1 Sk+1 f1 Rk+1NPG: 上升沿触发负脉冲 产生器 GCNPG: 门控单次上升沿触 发负脉冲ia ib GCNPGk+1. . .=VDDSk SN-1 RN-1SNia ib GCNPGN-1电原理图电路原理、信号时序与上一页胶片中的电路类似,区别在于移位控制电路 的实现方式 优点:参与高频翻转的电路节点少,功耗低 缺点:单bit转换周期多一个AND门的门延迟Single step conversion loopSk的沿恰好在输出Q有效窗口内, 可用于触发锁存与D/A转换 CKC上升沿走 一圈的时间:tloop = tcomp + t xor + t and 2 + t dff + t npg + t andn = t npg + t andn − t dff − tor = TR + t andn − t dff tloop − t dac = tcomp + t xor + t and 2 + 2t dff + torDAC的建立时间: t dac 需优化的时间:4‐bit设计例子• SAR结构– 电荷重分布 型DACAN ND¾异步逻辑由 异步逻辑由一个时钟沿触发 个时钟沿触发 ¾异步控制逻辑自动产生后续的所有脉冲2013‐4‐16 清华大学微电子所 47ANDANDAN ND• 1个动态比 较器 • 异步控制逻 辑NPMulti‐phase Clock Gen.什么电路可以无需外部时 钟,自主产生多相时钟?振荡器!实际电路 思路: 1. 用环振自主产生时钟; 2. 用门控信号控制时钟的 周期数; 电路特点: 1. 单bit转换环路最简洁,无DFF 延迟,可以实现最高速度 2. 需要增加类似于移位寄存器这 样的电路来产生数据锁存时钟门控环振模型时序控制 路 时序控制电路顺序控制电路 1. 利用与非门与触发 器配合产生顺序翻 转的状态信号S1, S2, … 2 利用f1, 2. f1 S1, S1 S2, S2 …合 成顺序选通信号 SC1, SC2, … 3 利用顺序选通信号, 3. 利用顺序选通信号 将每步比较结果分 别锁存,用于产生 DAC开关控制信号 信号时序图比较器输出的锁存Low power designDFF接收全部时钟脉冲DFF接收一半时钟脉冲DFF接收一个时钟脉冲低功耗逻辑设计: 1. 尽量减少高频翻转的节点 2. 采用动态逻辑顺序控制电路一个单元电 路的动态逻辑实现注:延迟反相电路,可由奇数个反相器串联而成。

10bit500MS_sPipeline-SARADC的设计

摘要模数转换器(ADC)作为现代通信系统中的关键电路,其性能直接决定了通信系统的整体性能。

在需要中等精度高速ADC的应用场合,如无线网802.11ac通信协议等,流水线逐次逼近型模数转换器(Pipeline-SAR ADC)以其兼顾高速和低功耗的结构特点、对先进工艺兼容良好等优良特性被广泛使用。

针对现代高速通信系统的应用场合,论文设计了一款10bit 500MS/s的Pipeline-SAR ADC,其系统架构为两级结构,两级SAR ADC都实现6bit的数据量化,级间放大器提供4倍增益,设置2bit 级间冗余。

在第一级SAR ADC中,提出了一种基于自关断比较器的非环路(Loop-unrolled)结构,在每位比较完成后,通过自关断信号将当前位比较器关断,在不影响比较器锁存级保持数据的前提下,极大减小了Loop-unrolled结构的功耗;同时,针对Loop-unrolled结构多个比较器之间的失调失配,采用了一种基于参考比较器的后台失调校准方法,参考比较器的引入使得该校准方法可以在不增加额外校准时间的前提下完成后台校准,保证了系统的高速特性。

级间放大器采用了一种增益稳定的动态放大器,通过将动态放大器的增益构造为同种参数比例乘积的形式,实现增益稳定,并对其工作时序进行了优化,避免了额外时钟相的引入。

第二级SAR ADC采用了两路交替比较器结构,同时对两个比较器采用了前台失调校准,以避免引入额外的校准时间。

由于级间放大器仅提供4倍增益,第二级的量化范围较小,本文在第二级电容阵列的设计上使用了非二进制冗余,以减小DAC建立误差造成的影响。

本文还设计了数字码整合电路、全局时钟产生电路,以保证整个Pipeline-SAR ADC设计的完整性。

本文基于TSMC 40nm CMOS工艺设计了具体的电路与版图。

后仿真结果表明,在1.1V电源电压下,采样率为500MS/s时,输入近奈奎斯特频率的信号,在tt工艺角下,有效位数(ENOB)达到9.2位,无杂散动态范围(SFDR)达到64.5dB,功耗为7.52mW,FoM值为25.76fJ/conv.step,达到设计指标要求。

基于40_nm_CMOS工艺的高速SAR_ADC的设计_

图1 SAR ADC的基本架构最后当每一位都比较完成后,DAC的输出电压将收敛到与输入信号相差不超过1/2 LSB(1LSB=V FS/2N)的范围,比较器的每一位输出码组成最终的N位输出码。

本设计采用了非2进制冗余DAC技术、静态锁存比较器、基于锁存器的SAR逻辑控制电路,在CMOS工艺下实现了12 bit的高速SAR ADC的设计。

1 DAC的设计DAC为非二进制传统电容阵列,阵列基底小于2。

根据式(1),如果利用位电容来实现12位ADC,则基底至少为1.8772发生在量化编码为0111输入信号在此冗余范围终都能被准确地表示,应的冗余范围内,最终就能正确完成量化2 SRA ADC的工作原理在采样阶段,采用下极板采样的方式出端接共模电压V_CM图2 本设计的SAR ADC结构图图3 本设计中用到的静态锁存比较器图4 SAR逻辑结构图号V ip和V in,此时差分DAC输出端的电荷:(2)(3)为了减小采样开关的非理想效应,先将V CM开关断开,再将自举采样开关断开,完成对输入信号的采样。

采样完成后即进行第一次量化。

以差分DAC的P端为例,首先将上极板从共模电平V CM断开,然后将除MSB 电容外所有电容的下极板切换到V refb,MSB电容下极板切换到V refb,DAC建立完成即进行第一次比较,此时,上极板电荷:(4)互补DAC的N端的切换方式和P端相反,其切换后(5)可得第一次比较时(7)(8)其中定义模拟权重:假设第一次比较结果D12=1,即V X P<V X N,则P端D A C的M S B电容下极板接V r e f保持不变,将MSB-1电容从V refb切换到V refb,V XP=V CM-V ip+V reft · (ω12,p,a+ω11,p,a)+V refb · (1-ω12,p,a-ω11,p,a )。

互补DAC端MSB电容下极板接V reft保持不变,并将MSB-1电容下极板从V refb切换到V reft,V XN=V CM-V in+V refb ·(1-ω12,n,a-ω11,n,a )+V refb · (ω12,n,a+ω11,n,a)。

SARADC设计和进展

比较器结构示意图

结构模块-digital模块

包括控制逻辑,移位寄存 器, SAR逐次逼近寄存器 实现对S/H模块,DAC 模块,comparator模块的 时序控制 数字部分时序示意图

工作时序

采样时钟320ns,系 统时钟20ns,一个采 样周期包含16个clk时 钟周期 5个clk时钟采样时间, 输入信号采样到电容 阵列 11个clk的转换时间, DAC模块在数字部分 控制下将输出送到比 较器进行逐次比较

结构模块-comparator模块

包括预放大级和快速锁 存比较器两级 预放大器: 放大输入信号, 提高比较器精度, 隔离锁 存比较器feed-back noise 对DAC部分开关电容阵列 的影响 锁存比较器: 包括跟踪和 锁存阶段,把预放输出快速 锁存到逻辑电平 开关电容结构: 输出失调 电压存储技术, 将预放输 出失调电压存储到存储电 容上

失调消除控制信号swg<1:0>,比较器输入 op_n, op_p,系统时钟clk对比图

工作时序-比较周期

比较周期由四部 分组成: 逻辑延迟 跟踪阶段信号 建立时间 锁存时间 比较器输出到 数字模块延迟

比较周期仿真图

设计难点-S/H模块

• HOLD阶段需要在要求时间内达到10bit精度 要求 • 运放的增益需要增益误差小于0.5LSB的需 要 • 运放带宽需要满足建立时间的要求 • 运放噪声要降到不至于影响精度的水平 • 开关尺寸的确定 • 电容大小的确定

0比较器输入比较器输入opnoppopnopp系统时钟系统时钟clkclk对比图对比图3clk3clk周期的时间周期的时间60ns60nsswg1swg1和和swg0swg0为高比较器将比较器将opampopamp级的失调级的失调储存到失调消除电容储存到失调消除电容c0c1c0c1上上这段时间里这段时间里opampopamp的性能应保证失调的性能应保证失调能完全储存到电容上能完全储存到电容上2clk2clk周期的时间周期的时间40ns40nsswg1swg1和和swg0swg0为低比较器等待比较器等待caparycapary模块的模块的输入到来输入到来接下来的接下来的11clk11clk周期用来周期用来比较比较每个比较周期包括每个比较周期包括四部分四部分工作时序比较周期比较周期由四部比较周期由四部分组成

SAR型ADC原理简析

SAR 型ADC 原理简析

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低

于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。

SAR ADC 的分辨率一般为8 位至16 位,具有低功耗、小尺寸等特点。

这些特点使该类型ADC 具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC 实质上是实现一种二进制搜索算法。

所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC 采样速率仅是该数值的几分之一。

SAR ADC 的架构

尽管实现SAR ADC 的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N 位寄存器首先设置在中间刻度(即:100.。

.00,MSB 设置为1)。

这样,DAC 输出(VDAC)被设为VREF/2,VREF 是提供给ADC 的基准电压。

然

后,比较判断VIN 是小于还是大于VDAC。

如果VIN 大于VDAC,则比较

器输出逻辑高电平或1,N 位寄存器的MSB 保持为1。

相反,如果VIN 小于VDAC,则比较器输出逻辑低电平,N 位寄存器的MSB 清0。

随后,SAR 控。

分段电容sar adc原理

分段电容sar adc原理分段电容SAR ADC原理一、引言分段电容逐次逼近型(Successive Approximation Register, 简称SAR)模数转换器(ADC)是一种常用的高精度ADC转换器。

它通过逐次逼近的方式,将模拟信号转换为数字信号。

本文将详细介绍分段电容SAR ADC的原理和工作流程。

二、分段电容SAR ADC的原理分段电容SAR ADC主要由以下几个部分组成:数字控制逻辑、比较器、DAC(数字模拟转换器)、分段电容阵列和采样保持电路。

1. 数字控制逻辑:数字控制逻辑负责控制ADC的工作流程。

它通过逐次逼近的方式,逐位地对模拟输入信号进行逼近,最终得到数字输出。

2. 比较器:比较器的作用是将DAC输出的模拟电压与输入信号进行比较,输出比较结果。

比较器通常采用高速运算放大器来实现。

3. DAC:DAC将数字控制逻辑输出的二进制码转换为相应的模拟电压输出,用于与输入信号进行比较。

4. 分段电容阵列:分段电容阵列是分段电容SAR ADC的核心组成部分。

它通过将总电容分为多个小电容单元,并通过开关控制,实现对电容的分段调节。

分段电容阵列的每个小电容单元与DAC的输出端相连,通过调节每个小电容单元的电容值,可以得到不同电压的输出。

5. 采样保持电路:采样保持电路用于将输入信号进行采样,并在转换过程中保持其稳定。

采样保持电路通常由开关和电容组成,通过控制开关的状态,将输入信号进行采样并保持在电容上。

三、分段电容SAR ADC的工作流程分段电容SAR ADC的工作流程可以分为以下几个步骤:1. 初始化:首先,数字控制逻辑将比特位数设定为要转换的目标精度,并将比特位数设置为最高有效位(Highest Significant Bit, 简称HSB)。

2. 比较:数字控制逻辑将DAC输出的电压与输入信号进行比较。

如果DAC输出的电压大于输入信号,则将当前比特位设为1,否则设为0。

3. 逼近:根据当前比特位的值,数字控制逻辑调整分段电容阵列的电容值,使得DAC输出的电压逼近输入信号的电压。

sar adc典型电路结构

sar adc典型电路结构SAR ADC(逐次逼近型模数转换器)是一种常用的模数转换器电路,具有高精度和低功耗的特点。

它通过逐次逼近的方式,将模拟信号转换为数字信号。

SAR ADC的典型电路结构如下:1. 采样保持电路(Sample and Hold Circuit):用于将输入的模拟信号进行采样并保持,在转换过程中保持信号的稳定性。

采样过程发生在采样脉冲的上升沿,保持脉冲的高电平期间,采样保持电路将输入信号模拟值保持不变。

2. 比较器(Comparator):将采样保持电路输出的模拟信号与DAC(数字模拟转换器)输出的数字信号进行比较。

比较器的输出为高电平或低电平,表示采样信号与参考信号的大小关系。

3. 逐次逼近寄存器(Successive Approximation Register):用于存储和逐位逼近计算最佳数字输出。

它通过串行输出控制信号,逐步逼近模拟信号的数字表示,以最终获得转换结果。

4. DAC(数字模拟转换器):将逐次逼近寄存器的输出数字信号转换为模拟信号,用于与输入的模拟信号进行比较。

5. 控制逻辑电路(Control Logic):用于控制ADC电路的整个工作过程。

它根据比较器的输出信号,调整逐次逼近寄存器的状态,并控制采样保持电路和DAC的工作时序。

以上是SAR ADC的典型电路结构。

在转换过程中,采样保持电路获取输入的模拟信号,比较器和DAC进行模拟信号与数字信号的比较和转换,逐次逼近寄存器完成数字信号的逐位逼近,最终得到模拟信号的数字表示。

SAR ADC的优点是功耗低、转换速度快、精度高,适用于对功耗和转换速度有严格要求的场景。

然而,它的缺点是整体电路较为复杂,需要较大的面积和更多的控制逻辑电路,因此在一些应用中可能不适用。

SARADC的设计_90510878

SAR ADC的设计李福乐清华大学微电子所2012SAR ADC Principle •以D/A来实现A/D, 逐次逼近•需要N次D/A和比较实现1次N位A/D转换•精度主要由DAC决定•无运放,低电压、低功耗•深亚微米CMOS工艺下很有发展潜艺下很有发展潜力的结构•超低功耗,高速转换是研究热点–异步时序控制可实现性能8~16 bitTime‐interleavedxk~ x00M S/s9‐b, 50MS/s, 65fJ/conv.9‐b, 40MS/s, 54fJ/conv.10‐ 10MS/s, 11fJ/conv.0b,0MS/s,fJ/conv.No Time‐interleaved!SAR的功耗优势实际上在中低分辨率上异步SAR结构主要N i t 的速度已逼近Pipeline结构Nyquist结构ADC的比较Ref: Shuo‐Wei Michael Chen. JSSC 2006.12DAC topologies二进制电流型电压型电压改进型电流型R2R阻容混合型电荷型匹配好;低功耗¾电荷型DAC特点:¾集成T/H 电路¾与输入相连的开关较多¾输入电容较大¾采用分段结构可减少电容数目¾电容大小是精度与面积功耗的权衡,可通过mento ‐carlo 仿真确定¾高位电容可采用DEM 技关键点底板采样术进一步提高精度¾对高精度转换,输入开关Ron 线性须保证bootstrap !¾高位电容可采用单元温度码控制,以减小输入端毛刺避免电荷泄漏以毛刺,避免电荷泄漏;以及确保单调性¾版图关键点:t t¾DAC output整体电路Ref: 叶亚飞实践课汇报PPT一个8bit SAR ADC整体结构与信号关系顶板采样6典型的两段分段电容结构X dV u a C 2)1(1u C kC 幅度VR的阶跃,其对DAC输出Vo的改变量分别为其中:Lt C X +保持正确权重,确保ADC线性=LL u k k C ⋅−=2别为:确保ADC线性,必须有:(a C C k +L Lt k C 2由以上公式可见,要令输入kC结论:1ADC的增益误差只取决于总采样电容与接到参考的总电容之比,MSB段接地的Cd1或寄生不会导致增益误差;2MSB段增加Cd1=kCu Cd1Cd1kC段不参与输入采样,降低ADC输入电容,且不会导致增益误差C 这里:①和②点的权重误差:dV dV =(Lt C C +根据前面的线性化设计结果有:在实际设计中,通常有:LtC <<<<在实际设计中常有为电容上极板寄生电容值与电容本身值之比寄生电容设计考虑•LSB段的寄生Cp2带来权重误差,导致非线性S C2带来权重误差导致非线性–LSB段所用电容、Ca,采用上极板共接–权重误差比例固定为β,因此降低LSB端位数L,可降低因此降低可降低非线性MSB•段的寄生Cp1不会带来非线性问题和ADC增益误差,但作为DAC时,会带来约Cp1/CMt的增益误差–MSB段所有电容,采用上极板共接,此为底板采样需要•Ca的上下极板间寄生Cp3直接影响权重,导致非线性–版图布线要特别注意最小化Cp3better?Which is•从噪声和匹配考虑,MSB段的电容不能太小从声和考虑可取–k>1•从优化电容面积考虑,可采用多段结构–对于中低分辨率ADC,优化面积和输入电容C优化面积和输入电容–对于失配,可采用校准技术COMP +MSB-1D i i-VcmMSB-1DecisionCOMP +-Decision COMP +COMP LSB Decision211-LSB Decision+COMP 211Vcm()u N C C σ2=Δ()()u u N u N u NC C C C C C σσ⋅==Δ2122输出对各电容C C σΔ1对于分段结构:失配敏感度()u u M M M C C ⋅=2Δ−()N C C σ22Ref: JAMES L. McCREARY , et, al. ALL ‐MOS由此可计算出元件匹配要求然后根()Nuu E E 221ασ≤由此可计算出元件匹配要求,然后根据工艺参数可确定元件尺度10%50%977%97.7%Ref: Anne Van Den Bosch, …, “An Accurate Statistical Yield Model for CMOS Current ‐Steering D/A Converters”, 2001分段结构设计对于分段结构:1分段结构与CDAC 非线性)从匹配角度,分段结构不能降低电容值2)从噪声角度,分段结构也不能降低电容值3)分段结构可提高最小单元电容值,使其免受工单元电容值,使其免受艺最小尺度的限制4)若指标不受失配限制,分段结构可降低总电容值和ADC 输入电容(中低分辨率or 采用校准)Ref: Stefan Haenzsche, etc. “Modelling of Capacitor Mismatch and Non ‐Linearity Effects in …”, MIXDES 2010分段结构电容设计:可按照不分段的方法先设计,而后截取高M 位为MSB 段,选择设计C 合适的k ,设计Ca 和LSB 段电容差分分段电容设计:在单端结构的基础上,截掉MSB 段MSB 电容;若受限于采样噪声,则截掉MSB 段LSB 电容,并令Cd1 double ,然后设计合适的k, Ca 和LSB 段电容电容取值:蒙特卡洛仿真法除了计算之外还可对除了计算之外,还可对SAR 结构建模,采用蒙特卡洛仿真法来设计电容尺度根据工艺厂商系统级模型提供的数据设定容值和失配Mento ‐Carlo 分析调整10u*10u: 0.11%若由噪声决定:满足要求?容值N10u*10u 的分析结果满足12bit 要求电容失配校准PrinciplelOffsetMeas.MeaslinearityMeasMeas.Ref: Y. Kuramochi, et, al. A 0.05‐mm2 110‐uW10‐b Self‐Calibrating Successive ApproximationADC Core in018um CMOS ASSC20070.18‐ CMOS,分段结构结合校准技术带来电容缩小校准模式与转换模式Calibration Mode Conversion Model b d dRef: Y. Kuramochi, ASSC 2007Requirements On Comparator?amp amp amp amp 1234•High Speed–Offset 不影响总体线性度,但考虑到Latch 尺寸小,但导致offset 分布扩大–前置放大器的带宽•Low offset–影体线性度但考虑到转换精度,以及latch 迟滞效应、噪声和分辨力,其前置放大器增益需足够放大器级数要根据延时、增益、功耗来权衡选择Ref: JOEYDOERNBERG 前置放大器的增益–Offset Cancellation•Low Noise–主要是第一级放大器DOERNBERG, JSSC 1989主要是第级放大器amp1(1/f, thermal noise)•Low kickback noise–Latch 设计要合理(for example: Cascode, cap at input)–(especially at latch on ‐to ‐off)时序设计控制(p y )•Low Power–比较器是构成SAR ADC 功耗的主要单元Trade ‐off低功耗动态比较器预放大器增益~ 2,电流1mAPMOS负载工作在线性区输出共模逼近VDD,这样latch比较时会更快速度快:<100ps for 65nm LLpprocessRef: Chun C. Lee, A SAR‐Assisted Two‐Stage Pipeline ADC. JSSC 2011.4动态pre‐amp + ,无静态功耗Latch无静态功耗~100ps for 90nm Ref: 12.4 ISSCC2008Comparator offset calibration利用电容存储和抵消offset,是最常用的办法Ref: Y. Kuramochi, ASSC 2007在preamp输出加入电流可以矫正offset,但同时引入寄生,会降低速度;冗余设计也是提高yield的办法余也提高Ref: S. Park, et, al. A 4GS/s 4b flash ADCin 0.18um CMOS. ISSCC 2006通过衬偏效应来调整输入管VT,以此来校准offsetRef:Alpman, Erkan. A 7‐BIT 2.5GS/sec TIME‐INTERLEAVEDC‐2C SAR ADC FOR 60GHz MULTI‐BAND OFDM‐BASEDComparator offset calibration在动态比较器中,通过调整输入差分对或差分对负载来校准offsetRef: Masaya Miyahara, etc. A Low ‐Noise Self ‐Calibrating Dynamic Comparator for high ‐speed ADCs或通过调整输出点的差a)调整输入分负载电容来校准offset可编程电容阵列差分对b))调整差分负载Ref: 13.5 ISSCC2007Ref: Chi ‐Hang Chan, etc. ASSCC 2011 9‐4Comparator noisepre ‐amp + Latch:静态p p 输入等效噪声可按照传统的放大器噪声分析方法来进行,即先各管产生的声在输先对各导通管产生的噪声在输出节点功率求和,然后再除以增益平方来求得输入等效噪声222222w +⎞⎛总输出噪声电流密度:()141312131211di di w di di di o +⎟⎟⎠⎜⎜⎝⋅+=di r di v 222211⋅=⋅⋅⋅=π总输出噪声电压:o o o no C g C r 422πtCLKΔV动态pre ‐amp :增益和输出噪声与积分m tg 1=的增益:C A 时刻tTime ‐Domain noise analysis model基本RC 并联电路的时域噪声分析假设:①R 为无噪声电阻②in 为高斯分布噪声电路,其等效噪声电阻为Rn T 0时均值的高斯变量方差为③T=0时,vc 为0均值的高斯变量,方差为σ0那么,在时刻t 时,vc 仍为0均值高斯变量,且其方差为:dfR kT di nn42=()RCt RC t n t e e CR kTR 220221−−+−=σσt<<RC 的情况下,上式可简化为:f l l f 在情况式简化为Ref: Pierluigi Nuzzo, Noise Analysis ofLowz降低输入过驱动Vov1 z降低输入共模z延长有效积分时间tdLow noise dynamic comparator增加了:增加了:Co1, td, gm2gm1, td,A2第二级通过M6,M7向ti+, ti ‐放电,M1M2两级动态结构:在第一级增益不够高的情况下,增加第二级增益也能有效地降低噪声噪声Vni(σ)的对比(比对的两者具有相同的size )21mV 066mV 延长了M1,M2饱和区工作时间td ;第一级差分电流通过M6,M7,带来第二级的电压增益A2增加第二级增益,也能有效地降低噪声2.1mV 0.66mV0.41mV0.2mV @ΔSTR=60psRef: Chi ‐Hang Chan, etc. ASSCC 2011 9‐4噪声测试电路()offsetV=φ推荐比较器设计TBDFor high resolution ADC (12bit)静态pre‐amp + latch + offset cancellation For low resolution ADC (8bit)动态pre‐amp + latch非线性效应实际电容表达式:()()()⎥⎥⎦⎤⎢⎢⎣⎡−+−+=22101nom nom V V V V C V C αα电容电压系数致使电容值与输入电压有关导致输入电压有关,导致ADC 全局渐变的非线性,影响INL ;通常对12bit 以上分辨率的ADC ,需要考虑电容电压系数的影响MOM 电容?Ref: Stefan Haenzsche, etc. MIXDES 2010SAR LOGICSAR逻辑基本操作:1)复位2)猜13)调取比较器输出4)移动猜15)同步锁存完整转换输出Asynchronous SAR ADC¾同步采样,异步转换¾控制电路需要的脉冲由电路自动产生¾好处:假设10bit 100MSPS ,则对于同步SAR 时钟频率至少1G比较器时间:比较大时有当N 比较大时,有:21≈⎟⎞⎜⎛async T max ⎟⎠⎜⎝sync T 1≈⎟⎞⎜⎛async T 2min ⎟⎠⎜⎝sync T Ref: Shuo ‐Wei Michael Chen, et, al. A 6‐bit 600‐MS/s 5.3‐mWAsynchronous ADC in 0.13‐um CMOS. JSSC 2006异步SAR•异步时序–比较器比较结束后能自动触发电荷重分配–电荷重分配结束后自动触发下一次比较下面给出个•下面给出一个4bit的设计例子–异步逻辑由一个时钟沿触发–异步控制逻辑自动产生后续的所有脉冲N PDD N N A A N D 异步逻辑由一个时钟沿触发个时钟沿触发异步控制逻辑自动产生后续的所有脉冲实验4SAR ADC•阅读SAR_ADC_8B_TB schematic,分析电路中各模块的功能•对电路进行瞬态仿真–CDAC输出VO,SAR Logic输入输出的波形查看输输出的波–查看双相不交叠时钟模块输入输出的波形,分析它们的timing关系–对理想8bit DAC的输出VTST进行采样并存储成文本文件,并用MATLAB导入并做谱分析,求出SNDR, HD2, HD3, SFDR等指标–对MSB电容加入2% mismatch,通过上一步方法仿真SNDR等指标–对MSB‐1电容加入2% mismatch,仿真SNDR等指标并对比•将电路修改为4‐4分段电容结构k=1, k=2, 并要求Ca为整数倍Cu,分别设计44CDAC;–令k=1k=2‐–令输入为覆盖整个量程的ramp信号,信号的上升速率足够慢,使得每个台阶都能出现在VTST中–进行瞬态仿真,通过VTST的波形来判断DNL–修改Cd1的值,仿真VTST的波形并观察其变化并分析的值仿真–修改Cd2的值,仿真VTST的波形并观察其变化并分析–修改Ca的值,仿真VTST的波形并观察其变化并分析–令输入为正弦信号瞬态分析对进行采样并存储成文本文件并用导入并做谱分析求出–瞬态分析,对VTST进行采样并存储成文本文件,并用MATLAB导入并做谱分析,求出SNDR, HD2, HD3, SFDR等指标–对MSB电容加入2% mismatch,通过上一步方法仿真SNDR等指标–对Ca电容加入2% mismatch,通过上一步方法仿真SNDR等指标–。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

10b-200ksps-SAR-ADC设计说明

一、目前项目的设计需求

目前项目属于COST-DOWN项目,所以电路面积是最主要的优化点,目前该ADC 的指标要求是10b-200Ksps,精度适中,速度比较低,关键是如何减小面积降低成本且能保证10b的模数转换有效位。

项目之前采用的SMIC SAR ADC IP,需要外接电阻,整体面积是0.17mm2,本次设计的主要目的是设计不需要外挂电阻的SAR ADC且整体电路的面积小于0.17mm2。

本项目中的SAR ADC针对的是单端应用,所以后续所有的讨论只针对单端应用情况。

二、各种SAR ADC架构比较及选定

图1、单端SAR ADC基本架构

图2、电阻分压型DAC结构

SAR ADC的基本架构如图1所示,该类型SAR ADC中的关键点是比较器的OFFSET

和DAC的线性度。

比较器的失调对于所有类型的SAR ADC具有共性,最后统一说明。

1、针对不同的DAC架构分别说明其线性度、面积等优缺点。

✓电阻分压实现DAC的传统架构:

如图2所示,该类型的由开关电阻阵列构成的电压按比例缩放D/A转换器,由于抽头电压不可能低于下面的抽头,因此保持了很好的单调性。

但是当D/A转换器的位分辨率提高时,开关数和电阻数均呈指数上升,面积难以接受。

而且,由于该DAC不能采样保持输入电压,因此信号输入端需要专门的采样保持电路用于维持ADC转换期间VIN 电压的相对固定,这进一步增加了面积。

此外,此类型的DAC转换精度依赖于电阻的匹配精度,在芯片内部,电阻的匹配精度低于电容的匹配精度。

综合以上因素,该类型的DAC只适合应用于转换位数较小的SAR ADC中。

图3、二进制电流型DAC结构

✓二进制电流型DAC架构

如图3所示,逐次逼近逻辑产生数字码控制电流源的开关,从而使得不同大小的电流与输入端产生的电流做减法运算,从而得到比较器的输出串行码。

该结构的DAC受限于电阻、MOS管的匹配程度,而且随着位数的增加电流镜结构也会导致比较大的功耗。

在高精度的SAR ADC架构中不宜采用此类DAC。

图4、R-2R结构的电流型DAC结构

✓R-2R电流型DAC架构

如图4所示,最低位2R/2R并联后的到R,R+R与2R并联后又得到R,依次类推,当所有的电阻均接地时,Vref端看到的输入阻抗为R。

开关S0~Sn-1控制接入比较器的电流大小,该结构解决了电阻随位数呈指数增加的问题,但是电路中的开关会导致电阻的匹配难度加大,此外,电流型运算放大器增加了该结构的设计难度,该结构同样需要额外的采样保持电路。

图5、电荷型DAC结构

✓电荷型DAC架构

如图5所示,电荷型也叫电容型DAC,该结构基于开关电容阵列,配合时序设计,运用电荷守恒的原理,实现电荷再分配而得到一个模拟电平。

在SAR ADC具体实现的时候,往往把信号采样和电容DAC放在一起设计,这样既实现了采样又实现了DAC,即在同一个电容阵列上面完成采样和DAC输出的数学运算。

该结构采用全电容设计,在片上容易得到更高精度的匹配。

不足之处在于,随着位数的增加,电容呈指数增加,从而使得电容占据了该ADC绝大部分的面积,增加了成本。

在8位及以下的SAR ADC架构中可以采用此类型的DAC,大大简化了设计难度。

图6、典型的二段分段电容结构

✓分段电容型DAC架构

如图6所示,为了解决典型电容型DAC的电容过大问题,通常采用分段电容结构实现高精度DAC的设计。

该结构解决了电容面积随位数指数增加的问题,由于电容的减小,该结构的转换速度会明显提高。

不足之处在于引入了Ca电容,该电容的寄生参数比较大,增加了匹配难度。

在12位左右或者以上的SAR ADC中采用此结构的电路必须对Ca及高位电容做失配校准,这会增加相应的时序和硬件电路,增加了设计和应用复杂度。

图7、阻容混合型DAC结构

阻容混合型DAC架构

如图7所示,阻容混合型的高位采用电容结构DAC,低位采用电阻结构DAC,以目前的10bit SAR ADC设计为例,高6位采用电容实现,低四位采用电阻实现。

由于C0和C1~C5所接的电压都是Vref,所以低位电阻型DAC不会超额,也就是说该类型的DAC 结构具有出色的单调性,这提高了ADC的ENOB。

片上4位16档电阻型DAC的步进为187mv(设定VREF=3V),这极大地降低了低位RES-DAC的设计难度。

该结构的缺点是,电阻性DAC的电阻不能取值过小,否则电流会增加,不利于低功耗设计。

相反,增加电阻降低功耗会导致该RES-DAC的响应速度降低,降低了该类型SAR ADC的转换速度。

以上几点决定了该类型的SAR ADC不利于目前主流的高速、低功耗应用场合。

但是目前我们的COST-DOWN方案的速度要求是200Ksps,因此该结构可以满足小面积,中等精度的应用要求。

由于该结构的线性度比较好,因此不需要针对电容或者电阻阵列做进一步的失配校准,减小了设计和应用难度。

综合以上情况,自主设计该SAR ADC电路时宜采用该阻容混合架构,其中,单位电容为5um×5um,总电容数为64*5um×5um,16个中等阻值的电阻及相应的开关用于设计RES-DAC,这极大的减小了整个SAR ADC的面积。

2、SAR ADC中比较器的精度对整体性能的影响

假设SAR ADC的比较器由于阈值电压、尺寸及电流镜的失配等导致输入OFFSET电压为20mv,则当比较器的输入电压差值接近该范围时,会导致其输出错误的电平。

该错误电平会导致转换后得到ADC码整体偏移一个档位。

由于阈值电压及尺寸、电流镜的失配属于静态OFFSET,不随PVT做动态变化,因此该参数并不影响ADC的线性度,

只是会导致输入输出之间存在一个固定的偏移。

对于检测相对变化的应用场合来说,比较器的OFFSET不需要做校准。

该问题详见图8

图8、OFFSET导致输入输出转换曲线的变化示意图

三、设计难点及解决方案

如果该应用关心模数转换的绝对精度,则必须校准比较器的OFFSET电压,如果只关心相对变化,则可以省去比较器的OFFSET校准,则该结构的SAR ADC设计难度会大大降低,也会相应减小面积和设计周期,从而降低投片风险

比较器的OFFSET电压<30mV,所以除非应用于高精度测量,一般情况输入输出曲线的小量偏移并不会影响使用,因此ADC更关心的是ENOB即线性度,所以建议自主设计该SAR ADC电路时对比较器OFFSET不做校准,这样会大大提高设计把握度。

最终可采用方案:阻容混合DAC架构,高6位采用电容架构DAC,低4位采用电阻架构DAC,不做比较器的OFFSET校准。

RES-DAC对VREF的要求不高,高6位C-DAC 要求其电容上的VREF抖动尽量小以提高转换精度,因此可以将该ADC的VREF接VCC(3.3VLDO的输出电压),另外适当增加退耦电容以尽量减小电容上的VREF波动。

高六位CDAC也可以分成两部分,其中的低两位采用二进制码控制,高四位可以采用温度计码控制,这样可以最大限度地保证DAC转换的线性度。

总之,通过以上调整,整体架构得到了简化,比较容易满足10Bit-200Ksps、减小面积的指标要求并且降低了设计难度。