第3章-指令级并行及其动态开发

《计算机组成原理》唐朔飞第二版_笔记

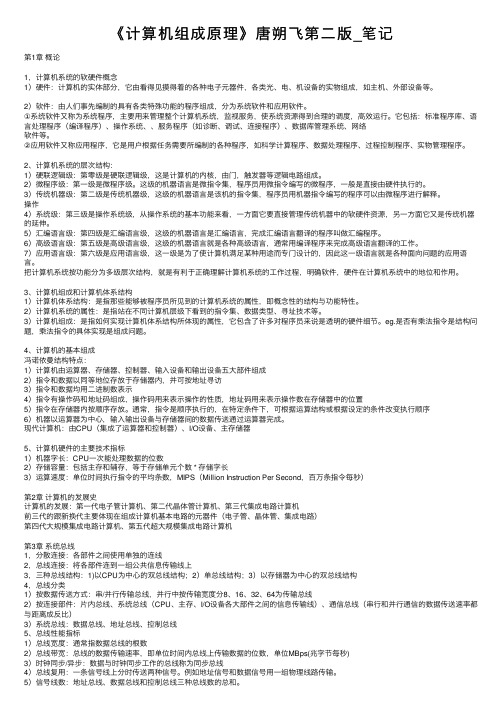

《计算机组成原理》唐朔飞第⼆版_笔记第1章概论1,计算机系统的软硬件概念1)硬件:计算机的实体部分,它由看得见摸得着的各种电⼦元器件,各类光、电、机设备的实物组成,如主机、外部设备等。

2)软件:由⼈们事先编制的具有各类特殊功能的程序组成,分为系统软件和应⽤软件。

①系统软件⼜称为系统程序,主要⽤来管理整个计算机系统,监视服务,使系统资源得到合理的调度,⾼效运⾏。

它包括:标准程序库、语⾔处理程序(编译程序)、操作系统、、服务程序(如诊断、调试、连接程序)、数据库管理系统、⽹络软件等。

②应⽤软件⼜称应⽤程序,它是⽤户根据任务需要所编制的各种程序,如科学计算程序、数据处理程序、过程控制程序、实物管理程序。

2、计算机系统的层次结构:1)硬联逻辑级:第零级是硬联逻辑级,这是计算机的内核,由门,触发器等逻辑电路组成。

2)微程序级:第⼀级是微程序级。

这级的机器语⾔是微指令集,程序员⽤微指令编写的微程序,⼀般是直接由硬件执⾏的。

3)传统机器级:第⼆级是传统机器级,这级的机器语⾔是该机的指令集,程序员⽤机器指令编写的程序可以由微程序进⾏解释。

操作4)系统级:第三级是操作系统级,从操作系统的基本功能来看,⼀⽅⾯它要直接管理传统机器中的软硬件资源,另⼀⽅⾯它⼜是传统机器的延伸。

5)汇编语⾔级:第四级是汇编语⾔级,这级的机器语⾔是汇编语⾔,完成汇编语⾔翻译的程序叫做汇编程序。

6)⾼级语⾔级:第五级是⾼级语⾔级,这级的机器语⾔就是各种⾼级语⾔,通常⽤编译程序来完成⾼级语⾔翻译的⼯作。

7)应⽤语⾔级:第六级是应⽤语⾔级,这⼀级是为了使计算机满⾜某种⽤途⽽专门设计的,因此这⼀级语⾔就是各种⾯向问题的应⽤语⾔。

把计算机系统按功能分为多级层次结构,就是有利于正确理解计算机系统的⼯作过程,明确软件,硬件在计算机系统中的地位和作⽤。

3、计算机组成和计算机体系结构1)计算机体系结构:是指那些能够被程序员所见到的计算机系统的属性,即概念性的结构与功能特性。

U035计算机操作系统教程_第四版_(张尧学著)_清华大学出版社_第3章

3.1.2 进程的定义 进程的概念是60年代初期,首先在MIT 的 Multics系 统和IBM 的 TSS/360系统中引用的。从那以来,人 们对进程下过许多各式各样的定义。 (1) 进程是可以并行执行的计算部分(S.E.Madnick, J.T.Donovan); (2) 进程是一个独立的可以调度的活动(E.Cohen, D.Jofferson); (3) 进程是一抽象实体,当它执行某个任务时,将要 分配和释放各种资源(P.Denning); (4) 行为的规则叫程序,程序在处理机上执行时的活 动称为进程(E.W.Dijkstra);

W(Si)={b1 b2 … bn},bj(j=1,…,n) 是语句Si在执行期间必须对其进行修改、访问的变量; 如果对于语句S1和S2,有 ① R(S1)∩ W(S2)={∮}, ② W(S1)∩ R(S2)={∮}, ③ W(S1)∩ W(S2)={∮} 同时成立,则语句S1和S2是 可以并发执行的。

(1) 进程是一个动态概念,而程序则是一个静态概念。程序是 指令的有序集合,没有任何执行的含义。而进程则强调执 行过程,它动态地被创建,并被调度执行后消亡。 (2) 进程具有并行特征,而程序没有。由进程的定义可知,进 程具有并行特征的两个方面,即独立性和异步性。也就是 说,在不考虑资源共享的情况下,各进程的执行是独立的, 执行速度是异步的。显然,由于程序不反映执行过程,所 以不具有并行特征。 (3) 进程是竞争计算机系统资源的基本单位,从而其并行性受 到系统自己的制约。这里,制约就是对进程独立性和异步 性的限制。 (4) 不同的进程可以包含同一程序,只要该程序所对应的数据 集不同。

第3章 进程管理

3.1 进程的概念 3.2 进程的描述 3.3 进程状态及其转换 3.4 进程控制 3.5 进程互斥 3.6 进程同步 3.7 进程通信 3.8 死锁问题 3.9 线程 本章小结 习题

西安交大-计算机系统结构复习提纲(可打印)

1. 开发 ILP 的两种方法 硬件动态,软件静态

2. 流水线中的调度策略 集中式调度、分布式调度 动态调度——乱序 Tomasulo 算法 分布式检测:重命名(换名)

3. 动态分支预测 针对控制相关,由硬件处理, 分支历史表 BHT——历史状态, 分支目标缓冲器 BTB——历史目标地址

5. 指令结构功能设计 CISC 机:三个目标优化 (也反映了编译,操作系统和系统结构的关系) 面向目标程序、面向高级语言、面向操作系统

RISC 机: 导致 RISC 机产生的缘由; (2-8 定理;控制器负责;不易纠错修改) 设计 RISC 机遵循的基本原则;

三、计算与设计

1. 指令格式设计 2. 指令格式的优化

延迟转移技术(延迟槽) 9. 流水线中的中断处理

不精确断点、精确断点 10. 向量处理机

向量数据表示,向量指令 向量处理方式

三、计算与设计

1. 时空图 2. 性能分析 3. 非线性流水线最小平均启动时间

第四章:指令级并行

一、基本概念——名词

超标量,超流水,动态调度,静态调度,超长指令字,保留站,Tomasulo 算法,ILP,BHT, BTB,ROB,前瞻执行(先执行再确认)

计算机系统结构是机器语言程序员或编译程序编写者所看到的外特性。所谓外特性,就 是计算机的概念性结构和功能特性。

(还有一个系统结构定义,这是由于存在计算机系统层次结构,不同的人看到不同的计 算机结构) 2. 计算机系统结构、组成与实现的三者关系:

系统结构——存在某个部件 计算机组成——罗技实现,门一级实现 计算机实现——物理实现,器件一级实现

第三章:流水线技术

一、基本概念——名词

先行控制,流水线,单功能流水线,标量流水线,重定向,分支预取,专用通道,无冲突调 度方法,冲突向量,启动距离,性能分析,时空图,缓冲技术,预处理等

archit44

4.3 动态分支预测技术

指令并行

处理器可达到的指令级并行度越高,控制相关 的影响越大 动态解决技术利用硬件对程序运行时分支的行 为进行预测,提前对分支操作做出反应,加快 分支处理的速度。分支预测的效果不仅取决于 其准确性,而且与分支预测时的开销密切相关。 分支转移的最终延迟取决于流水线的结构、预 测的方法和预测错误后恢复所采取的策略 动态分支预测技术要记录分支指令的历史、并 据此决定预测的分支,还要尽快找到分支目标 地址,从而避免控制相关造成流水线停顿

4.4 多指令流出技术

指令并行

将等于1的理想CPI减小,必须实现一个时钟周 期流出(发射issue)多条指令

超标量(Superscalar)处理器:每个时钟周期流出多条 指令(1~8),可以采用编译器进行静态调度顺序执行, 也可以采用硬件动态调度乱序执行 超长指令字(VLIW: Very Long Instruction Word):通 过编译器调度无关的多条指令(4~16)形成一条长指 令,每个时钟周期流出一条长指令 超级流水线(Super pipelining):将每个功能部件进一 步流水化,使得一个功能部件在一个时钟周期中可以处 理多条指令(可以简单地理解为很长的流水线)

WAW 冲突 (输出相关引起) 如果在SUB.D写入F10 之 前 ADD.D 执 行 结 束 , 会出现问题

寄存器换名可以消除WAR和WAW冲突

指令并行

DIV.D F4,F0,F2 SUB.D F10,F4,F6 ADD.D F8,F12,F14

DIV.D F4,F0,F2 SUB.D F10,F4,F6 ADD.D F8,F6,F14

① 根据历史记录(预测位状态)进行分支预测 ② 根据实际分支情况修改预测位

单片机指令的并行执行技术

单片机指令的并行执行技术单片机指令的并行执行技术是一种提高单片机性能和效率的重要方法。

通过同时执行多个指令,可以大大加快程序运行速度,提高系统的响应能力。

本文将介绍单片机指令的并行执行技术以及其应用。

一、指令的并行执行原理指令的并行执行是指在一个时钟周期内同时执行多个指令。

实现指令的并行执行需要满足以下几个条件:1. 数据无相关性:同时执行的指令之间不能有数据相关性,即后续指令不依赖于前面指令的结果。

否则会导致数据错误。

2. 硬件支持:需要具备支持并行执行的硬件结构,包括有多个执行单元和数据通路。

基于以上原理,下面将介绍几种常见的单片机指令并行执行技术。

二、指令级并行执行技术指令级并行执行技术是指在一个时钟周期内同时执行多条指令的技术。

常见的指令级并行执行技术包括:1. 流水线技术:将指令执行过程分为多个阶段,每个阶段由不同的硬件执行,实现多个指令的同时执行。

比如Fetch(取指令)、Decode (解码)、Execute(执行)和Write Back(写回)等阶段。

2. 超标量技术:通过增加硬件资源,同时从指令存储器中提取多条指令并行执行。

不同于流水线技术,超标量技术可以并行执行多个指令的某个或全部阶段。

三、循环级并行执行技术循环级并行执行技术是指在一个循环中同时执行多条指令的技术。

常见的循环级并行执行技术包括:1. 向量处理器:通过并行处理多个数据元素来加速程序运行速度。

向量处理器可以一次性处理多个相同类型的指令,提高程序的执行效率。

2. SIMT技术:Single Instruction Multiple Thread,即单指令多线程技术。

通过将多个线程分配给不同的处理单元,实现多个线程的同时执行。

这种技术广泛应用于图形处理器(GPU)等领域。

四、应用领域指令的并行执行技术在多个领域都有广泛应用,特别是对于对计算能力要求较高的应用场景。

下面列举几个典型的应用领域:1. 数字信号处理(DSP):在音频和视频处理等领域,需要高效处理大量数据,指令的并行执行技术可以提高处理速度和实时性。

2019年计算机系统结构第4章指令级并行及限制.ppt

Loop:

流出时钟

LD

F0,0(R1) 1

(空转)

2

ADDD F4,F0,F2 3

(空转)

4

(空转)

5

SD

0(R1),F4 6

LD

F6,-8(R1) 7

(空转)

8

ADDD F8,F6,F2 9

(空转)

10

(空转)

11

SD

-8(R1),F8 12

LD

F10,-16(R1) 13

(空转)

14

流出时钟

ADDD F12,F10,F2

2相关性对指令级并行的影响本章使用的浮点流水线的延迟产生结果指令使用结果指令延迟时钟周期数浮点计算另外的浮点计算3浮点计算浮点数据存操作sd2浮点数据取操作ld浮点计算1浮点数据取操作ld浮点数据存操作sd07例41对于下面的源代码fori1

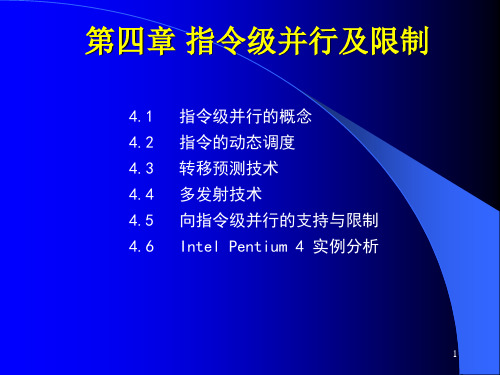

第四章 指令级并行及限制

4.1 指令级并行的概念 4.2 指令的动态调度 4.3 转移预测技术 4.4 多发射技术 4.5 向指令级并行的支持与限制 4.6 Intel Pentium 4 实例分析

15

(空转)

16

(空转)

17

SD

-16(R1),F12

18

LD

F14,-24(R1) 19

(空转)

20

ADDD F16,F14,F2

21

(空转)

22

(空转)

23

SD

-24(R1),F16 24

SUBI R1,R1,#32 25

(空转)

26

BNEZ R1,Loop 27

(空转)

28

25

结果分析: 这个循环每遍共使用了28个时钟周期 有4个循环体,完成4个元素的操作 平均每个元素使用28/4=7个时钟周期 原始循环的每个元素需要10个时钟周期 节省的时间:从减少循环控制的开销中获得的 在整个展开后的循环中,实际指令只有14条, 其它13个周期都是空转。 效率并不高

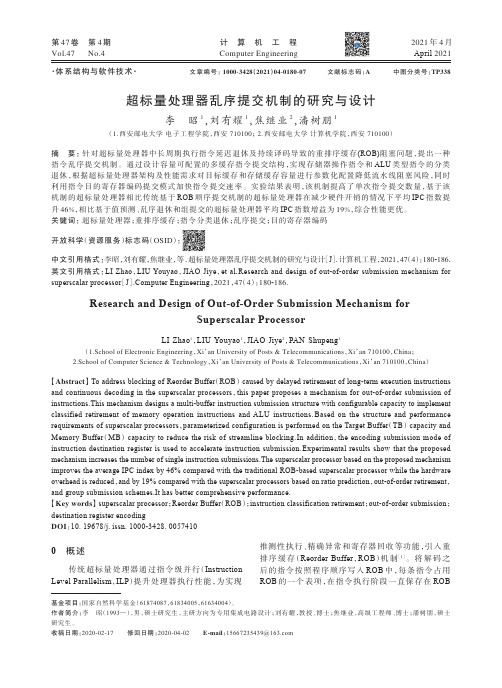

超标量处理器乱序提交机制的研究与设计

第47卷第4期Vol.47No.4计算机工程Computer Engineering2021年4月April2021超标量处理器乱序提交机制的研究与设计李昭1,刘有耀1,焦继业2,潘树朋1(1.西安邮电大学电子工程学院,西安710100;2.西安邮电大学计算机学院,西安710100)摘要:针对超标量处理器中长周期执行指令延迟退休及持续译码导致的重排序缓存(ROB)阻塞问题,提出一种指令乱序提交机制。

通过设计容量可配置的多缓存指令提交结构,实现存储器操作指令和ALU类型指令的分类退休,根据超标量处理器架构及性能需求对目标缓存和存储缓存容量进行参数化配置降低流水线阻塞风险,同时利用指令目的寄存器编码提交模式加快指令提交速率。

实验结果表明,该机制提高了单次指令提交数量,基于该机制的超标量处理器相比传统基于ROB顺序提交机制的超标量处理器在减少硬件开销的情况下平均IPC指数提升46%,相比基于值预测、乱序退休和组提交的超标量处理器平均IPC指数增益为19%,综合性能更优。

关键词:超标量处理器;重排序缓存;指令分类退休;乱序提交;目的寄存器编码开放科学(资源服务)标志码(OSID):中文引用格式:李昭,刘有耀,焦继业,等.超标量处理器乱序提交机制的研究与设计[J].计算机工程,2021,47(4):180-186.英文引用格式:LI Zhao,LIU Youyao,JIAO Jiye,et al.Research and design of out-of-order submission mechanism for superscalar processor[J].Computer Engineering,2021,47(4):180-186.Research and Design of Out-of-Order Submission Mechanism forSuperscalar ProcessorLI Zhao1,LIU Youyao1,JIAO Jiye2,PAN Shupeng1(1.School of Electronic Engineering,Xi’an University of Posts&Telecommunications,Xi’an710100,China;2.School of Computer Science&Technology,Xi’an University of Posts&Telecommunications,Xi’an710100,China)【Abstract】To address blocking of Reorder Buffer(ROB)caused by delayed retirement of long-term execution instructions and continuous decoding in the superscalar processors,this paper proposes a mechanism for out-of-order submission of instructions.This mechanism designs a multi-buffer instruction submission structure with configurable capacity to implement classified retirement of memory operation instructions and ALU instructions.Based on the structure and performance requirements of superscalar processors,parameterized configuration is performed on the Target Buffer(TB)capacity and Memory Buffer(MB)capacity to reduce the risk of streamline blocking.In addition,the encoding submission mode of instruction destination register is used to accelerate instruction submission.Experimental results show that the proposed mechanism increases the number of single instruction submissions.The superscalar processor based on the proposed mechanism improves the average IPC index by46%compared with the traditional ROB-based superscalar processor while the hardware overhead is reduced,and by19%compared with the superscalar processors based on ratio prediction,out-of-order retirement,and group submission schemes.It has better comprehensive performance.【Key words】superscalar processor;Reorder Buffer(ROB);instruction classification retirement;out-of-order submission;destination register encodingDOI:10.19678/j.issn.1000-3428.00574100概述传统超标量处理器通过指令级并行(Instruction Level Parallelism,ILP)提升处理器执行性能,为实现推测性执行、精确异常和寄存器回收等功能,引入重排序缓存(Reorder Buffer,ROB)机制[1]。

高级计算机系统结构部分知识点整理

1.高级计算机系统结构:Advanced Computer Architecture(Parallel Computer):The computer system constituted by many process units of mutual communication for solving some large-scale applications。

翻译:由多个处理单元组成的计算机系统,相互通信和协作,能快速求解大型复杂问题2. 课程教学内容第一章绪论3.MIPS处理机的运算速度MIPS=Fz*IPC Fz处理机的主频;IPC每个时钟周期平均执行指令数4.计算机技术快速进步的原因:计算机生产技术的发展—集成电路技术IC);计算机设计的创新—计算机系统结构。

5.2004年,Intel取消了高性能单核处理器项目,和其他公司一起宣布:为了获得更高性能的处理器,应当提高一个芯片上集成的核心数目,而不是加快单核处理器的速度。

历史性转折的里程碑信号处理器性能的提高从单纯依赖指令级并行(ILP)转向数据级并行(DLP)和线程级并行(TLP)6.体系结构研究的内容:--进一步提高单个微处理器的性能(光速极限问题)--基于微处理器的多处理器体系结构--全面提高计算机系统性能:可用性、可维护性、可缩放性--新型器件的处理器:如光计算机;新原理的计算机(生物、分子、量子、DNA计算机)7.应用程序中主要有以下两种并行:数据级并行(DLP):其出现是因为可以同时操作许多数据项任务级并行(TLP):其出现是因为创建了一些能够单独处理但大量采用并行方式执行的工作任务.8. 计算机硬件以如下四种主要方式来开发这两种类型的并行性:[1]指令级并行:在编译器的帮助下,利用流水线等思想适度开发数据级并行,利用推理执行等思想以中等水平开发数据级并行;[2]向量体系结构和图形处理器(GPU):将单条指令并行应用于一个数据集,以开发数据级并行[3]线程级并行:在紧耦合硬件模型中开发数据级并行或任务级并行,允许在并行线程之间进行交互;[4]请求级并行:在程序员或操作系统指定的大量去耦合任务之间开发并行性。

多发射指令的算法细节讲解

循环展开4次(straightforward way)

1 Loop: LD

2

ADDD

3

SD

4

LD

5

ADDD

6

SD

7

LD

8

ADDD

9

SD

10

LD

11

ADDD

12

SD

13

SUBI

14

BNEZ

15

NOP

F0,0(R1) stall

F4,F0,F2 stall stall

0(R1),F4

;drop SUBI & BNEZ

Ch 4 指令级并行

Embedded System Lab Fall 2012

4.1 指令级并行 (Instruction Level Parallelism)

• 相关是程序运行的本质特征

• 相关带来数据冒险

Loop: LD F0,0(R1) SUBI R2,R2,8

• 冒险导致CPU停顿 Stall

产生结果的指令 FP ALU op FP ALU op Load double Load double Integer op

使用结果的指令 Another FP ALU op Store double FP ALU op Store double Integer op

所需的延时 3 2 1 0 0

• 需要在哪里加stalls?(假设分支在ID段得到地址和条件)

A[1] = A[1] + B[1];

for (i=1; i<=99; i=i+1) {

NEW:

B[i+1] = C[i] + D[i];

A[i+1] = A[i+1] + B[i+1];

计算机体系结构优化基础知识

计算机体系结构优化基础知识计算机体系结构是指计算机硬件与软件共同组成的系统结构,涉及到计算机的组成部分、数据流动及处理方式等方面。

优化计算机体系结构可以提升计算机的性能、降低能耗并提高系统的可靠性。

本文将介绍计算机体系结构优化的基础知识,包括指令级并行、数据级并行、内存层次结构和硬件加速等方面。

一、指令级并行指令级并行是通过并发处理多条指令来提高系统性能。

它主要有以下几种形式:1. 流水线技术:流水线将一条指令的执行过程分解成多个步骤,并同时执行多条指令的不同阶段。

这样可以提高指令的执行速度。

典型的流水线包括取指、译码、执行、访存和写回等阶段。

2. 超标量技术:超标量技术允许同时发射多个指令,通过乱序执行和重排序来提高指令级并行性。

它可以同时执行多条在数据相关上无冲突的指令,从而提高系统的吞吐量。

3. 动态调度技术:动态调度技术可以根据指令之间的数据依赖关系,动态地调整指令的执行顺序,以最大程度地利用系统资源。

这样可以提高指令级并行性和执行效率。

二、数据级并行数据级并行是通过同时处理多个数据元素来提高系统性能。

它主要有以下几种形式:1. 向量处理器:向量处理器可以同时对一个向量中的多个元素进行计算,从而提高计算性能。

它适用于科学计算和图形处理等需要大量并行计算的应用场景。

2. 并行计算:并行计算将一个大问题拆分成多个子任务,并通过分布式计算来同时解决这些子任务。

这样可以充分利用多核处理器或集群系统的计算能力。

3. SIMD指令集:SIMD指令集允许一条指令同时对多个数据元素进行操作。

这样可以提高数据级并行性,加速图像处理和多媒体应用等。

三、内存层次结构内存层次结构是计算机存储器层次之间的组织方式。

通过合理的内存层次结构可以提高数据访问效率,减少内存访问延迟。

常见的内存层次结构包括:1. 高速缓存(Cache):高速缓存是位于处理器和主存之间的一层快速存储器。

它通过保存最近访问的数据和指令,减少了对主存的访问次数,提高了系统的运行速度。

指令级并行的概念

○ 是指令级并行研究 的重点之一。

指令级并行的概念

4.1 指令级并行的概念

最基本的开发循环级并行的技术

指令调度(scheduling)

A

技术 换名(renaming)技术 C

循环展开(loop

B

unrolling)技术

指令级并行 的概念

通过改变指令在程序中的位置,将相关指 ○ 令之间的距离加大到不小于指令执行延迟,将 ● 相关指令转化为无关指令。 ● 指令调度是循环展开的技术基础。

结构有关。 程序中的相关主要有以下三种

• 数据相关 • 名相关 • 控制相关

1.数据相关 (data

dependence)

指令级并行的概 念

0

对于指令i和指令j,如果

1

一.

指令j使用指令i产生的结果,或者

二.

指令j与指令k数据相关,指令k与指令i数据相

○

关,则指令j与指令i数据相关。

○

数据相关具有传递性。

ADDD F16,F14,F2

8

SD 0(R1),F4

SD -8(R1),F8

SUBI R1,R1,#32

12

SD 16(R1),F12

11

BNEZ R1,Loop

SD 8(R1),F16

14

指令 1 2

5 6

9 10

13

4.1 指令级并行的概念

结果分析:

没有数据相关引起的空转等待 整个循环仅仅使用了14个时钟周期

-8(R1),F8 F10,-16(R1) 13

流出时钟

ADDD 15

(空转) 16

(空转) 17

《指令动态调度》课件

IA-64架构的指令动态调度实现

1 IA-64架构

2 指令动态调度

由In te l和HP合作开发的处理器架构,广泛 应用于服务器和高性能计算领域。

IA-64架构提供了丰富的指令集和硬件支持, 实现了高效的指令动态调度。

根据指令之间的相关性和依 赖关系,灵活地调整指令的 执行顺序。

超标量执行

同时执行多条指令,充分利 用处理器的多个功能单元。

指令调度的优化技术

1 重排指令

通过调整指令的执行顺序,减少数据相关性和控制相关性,提高指令级并行度。

2 动态调度

根据当前的系统状态和资源利用情况,动态地调整指令的执行顺序,提高程序执行效率。

优点

简单、可控、资源消耗较少,适用于大部分处理器和指令集架构。

缺点

对分支指令和数据相关性处理不够灵活,可能会导致性能下降。

VLIW处理器的介绍

1 概念

Very Lo ng Instructio n W o rd (超长指 令字)处理器,一条指令包含多个操作 。

2 特点

通过静态调度和指令级并行,同时执行多 条操作,提高处理器性能。

Tomasulo算法的介绍

原理

通过将指令的执行和操作数的准备解耦,实现指令级并行执行。

优点

有效利用处理器资源,提高并行度和程序执行效率。

缺点

实现复杂,对硬件要求较高,需要较多的硬件资源。

Scoreboarding算法的介绍

原理

通过建立和管理保留站,并进行指令发射、执行和完成的控制,实现动态调度和执行。

动态调度和静态调度的区别

1 动态调度

实时地对指令进行调度和重排序,根据当前的系统状态进行优化,灵活适应不同的程序 和环境。

计算机系统结构考试重点

冯诺依曼的5个架构:控制器、运算器、存储器、输入设备、输出设备。

Cpu的发展趋势:1、多核技术出现的原因因为:“处理器功耗正比于电流x 电压 x 电压 x 主频”,“IPC 正比于电流”,所以:“处理器功耗正比于 IPC“。

由单核处理器增加到双核处理器,如果主频不变的话,IPC理论上可以提高一倍,功耗理论上也就最多提高一倍,因为功耗的增加是线性的。

而实际情况是,双核处理器性能达到单核处理器同等性能的时候,前者的主频可以更低,因此功耗的下降也是指数方(三次方)下降的。

反映到产品中就是双核处理器的起跳主频可以比单核处理器更低,性能更好。

由此可见,将来处理器发展的趋势是:为了达到更高的性能,在采用相同微架构的情况下,可以增加处理器的内核数量同时维持较低的主频。

这样设计的效果是,更多的并行提高IPC,较低的主频有效地控制了功耗的上升。

2、2个1G的多核和2G的单核处理器单核CPU也有高频率的,双核CPU也有低频率的。

内存则有DDR DDR2和DDR3之分。

型号频率不同,自然效果也不同。

如果是同时运行多个任务,双核自然是占有优势。

在上网,做工作时,高频率的内存则可以加快存取传输的速度如果内存是同一个型号,那么自然是1G内存+双核快一些,内存的大小不直接关系到存取的速度。

3、编程模型:SIMD VS MIMD?(应用场景、架构优缺点)单指令流多数据流计算机SIMD计算机有n个相同的处理器,每个都有其自己的本地存储器,可以存储数据。

一个由中央控制单元发出的单指令流控制所有处理器的工作。

有N个数据流,每1个处理器操作1个数据。

所有处理器是同步操作的,在每一步中,处理器对于不同的数据元素执行相同的指令。

SIMD计算机比MISD更通用。

许多应用问题可以通过SIMD计算机并行算法求解。

另一个有趣的特点是,这些计算机算法比较容易设计,分析和实现。

局限是只有可被细分为一组相同子问题的那些计算才可以被处理。

有很多的计算,不适合这种模式:这种问题通常使用下面的MIMD计算机解决。

计算机体系结构期末试题-湖南城市学院

题一11.计算机系统结构的层次结构由高到低分别为应用语言机器级,高级语言机器级,汇编语言机器级,操作系统机器级,传统机器语言机器级,微程序机器级12.计算机系统弗林(Flynn)分类法,把计算机系统分成单指令流单数据流(SISD)、单指令流多数据流(SIMD)、多指令单数据流和多指令多数据流四大类。

13.透明指的是客观存在的事物或属性从某个角度看不到,它带来的好处是简化某级的设计,带来的不利是无法控制。

22.数据结构和数据表示之间是什么关系?确定和引入数据表示的基本原则是什么?数据表示是能由硬件直接识别和引用的数据类型。

数据结构反映各种数据元素或信息单元之间的结构关系。

数据结构要通过软件映象变换成机器所具有的各种数据表示实现,所以数据表示是数据结构的组成元素。

(2分)不同的数据表示可为数据结构的实现提供不同的支持,表现在实现效率和方便性不同。

数据表示和数据结构是软件、硬件的交界面。

(2分)除基本数据表示不可少外,高级数据表示的确定和引入遵循以下原则:(1)看系统的效率有否提高,是否减少了实现时间和存储空间。

(2)看引入这种数据表示后,其通用性和利用率是否高。

15.引入数据表示的两条基本原则是:一看系统的效率有否提高;二看数据表示的通用性和利用率是否高。

13.计算机组成指的是计算机系统结构的逻辑实现,包括机器级内的数据流和控制流的组成及逻辑设计等。

计算机实现指的是计算机组成的物理实现,。

21、软件和硬件在什么意义上是等效的?在什么意义上是不等效的?逻辑上等效,性能、价格、实现难易程度上不一样。

22.说明翻译和解释的区别和联系.区别:翻译是整个程序转换,解释是低级机器的一串语句仿真高级机器的一条语句。

联系:都是高级机器程序在低级机器上执行的必须步骤。

19.计算机系统结构也称计算机体系结构,指的是传统机器级的系统结构。

它是软件和硬件/固件的交界面,是机器语言汇编语言程序设计者或编译程序设计者看到的机器物理系统的抽象。

并行程序设计导论PPT课件

消息传递编程模型

特点

各个并行部分之间通过发送和接收消 息来进行通信和同步。

优点

可扩展性好,适用于分布式内存系统 。

缺点

编程复杂,需要显式地管理通信和同 步。

应用场景

适用于大规模并行处理系统、集群计 算等。

数据并行编程模型

特点

优点

将相同的操作同时应用于不同的数据元素 ,实现数据级别的并行性。

编程简单,易于实现并行化。

04

常用并行算法介绍

并行排序算法

如并行快速排序、并行归并排序等,用于大规模数据的排序。

并行图算法

如并行广度优先搜索、并行最短路径算法等,用于图论问题的求解。

并行矩阵运算

如矩阵乘法、矩阵分解等,是科学计算和工程应用中常见的并行算法。

并行数值计算

如并行蒙特卡罗方法、并行有限元方法等,用于数值计算问题的求解。

06

并行程序设计实践

并行程序设计实验环境搭建

硬件环境

选择适合并行计算的硬件设备,如多 核CPU、GPU或分布式计算集群。

网络环境

确保实验环境中的网络连接稳定,以 便进行分布式并行计算。

软件环境

安装并行程序设计所需的操作系统、 编译器、调试器和性能分析工具。

并行程序设计实验项目介绍

矩阵乘法

通过并行计算加速矩阵乘 法运算,提高计算效率。

Intel VTune Amplifier

针对NVIDIA GPU的并行程序性 能分析工具,可以对CUDA程序 进行性能分析和优化。

并行程序优化策略

任务划分与负载均衡

将并行任务划分为多个子任务,并分配 给不同的处理单元,实现负载均衡,提

高并行效率。

数据局部性优化

指令级并行

5

采用的基本技术

2020/7/10

计算机体系结构

6

本章遵循的指令延时

产生结果的指令 使用结果的指令 所需延时

FP ALU op

Another FP ALU op

3

FP ALU op

Store double

2

Load double

FP ALU op

1

Load double

Store double

0

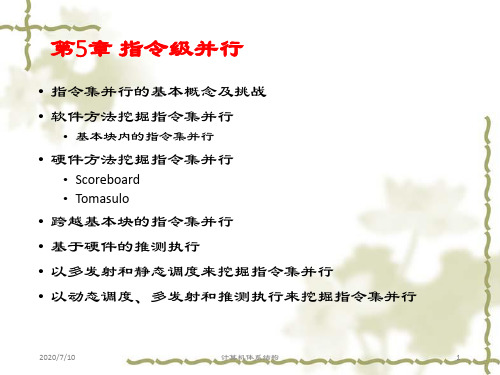

第5章 指令级并行

• 指令集并行的基本概念及挑战 • 软件方法挖掘指令集并行

• 基本块内的指令集并行

• 硬件方法挖掘指令集并行

• Scoreboard • Tomasulo

• 跨越基本块的指令集并行 • 基于硬件的推测执行 • 以多发射和静态调度来挖掘指令集并行 • 以动态调度、多发射和推测执行来挖掘指令集并行

单线程(逻辑上)中并行处理多个数据 (SIMD/Vector execution) 一个程序计数器, 多个执行部件

• 指令级并行

针对单一指令流,多个执行部件并行执行不同的指令

2020/7/10

计算机体系结构

3

Review: 基本流水线

• 流水线提高的是指令带宽(吞吐率),而不是单条指令 的执行速度

• 相关限制了流水线性能的发挥

• 结构相关:需要更多的硬件资源 • 数据相关:需要定向,编译器调度 • 控制相关:尽早检测条件,计算目标地址,延迟转移,预测

• 增加流水线的级数会增加相关产生的可能性

• 异常,浮点运算使得流水线控制更加复杂

• 编译器可降低数据相关和控制相关的开销

• Load 延迟槽 • Branch 延迟槽 • Branch预测

高级计算机系统结构期末考试复习总结

第一章量化设计与分析根底1.计算机性能提升表现在哪些方面:半导体技术不断提高,如特征尺寸和时钟频率;计算机体系结构不断改良,如高级语言编译器、标准化的操作系统和指令更为简单的RISC 体系结构。

2.并行分类:1〕应用程序的并行分类:数据级并行(DLP):同时操作多数据任务级并行(TLP):创立了一些能够独立处理但大量采用并行方式执行的工作任务2〕硬件的体系结构:指令级并行(ILP):在编译器帮助下。

利用流水线的思想开发数据级并行,利用推理执行的思想以中等水平开发数据集并行。

向量体系结构和图像处理单元(GPUs):将单条指令并行应用于一个数据集,来到达数据集并行线程级并行:在紧耦合硬件模型中开发数据集并行或任务及并行,这种模型允许在线程之间进行交互。

请求级并行:在程序员或操作系统制定的大量去耦合任务之间开发并行3.Flynn’s分类是如何分类的?Flynn’s分类主要分为四类:1)单指令流、单数据流(SISD):一条指令处理一个数据,可以利用指令级并行(ILP)2)单指令流、多数据流(SIMD):将大量重复设置的处理单元按一定方式互连成阵列,在单一控制部件CU(Contrul Unit)控制下对各自所分配的不同数据并行执行同一指令规定的操作,主要应用于向量体系结构、多媒体扩展指令和图像处理单元(Graphics processor units) 3)多指令流、单数据流(MISD):用多个指令作用于单个数据流,没有商业实现4)多指令流多数据流(MIMD):每个处理器都提取自己的指令,对自己的数据进行操作,主要用于开发线程级并行TLP〔紧耦合MIMD〕和请求级并行RLP〔松耦合MIMD〕4.什么是“真正〞的计算机体系结构?1)满足目标和功能需求的组成和硬件;2)限制条件下最大化性能:本钱、功耗、可用性;3)包括指令集体系结构(ISA),微体系结构,硬件5.计算题:可靠性的计算平均无故障时间:Mean time to failure (MTTF),MTTF是故障率的倒数。

计算机体系结构指令级并行基础知识详解

计算机体系结构指令级并行基础知识详解计算机体系结构是计算机科学中的一个重要领域,它研究计算机各个组成部分之间的关系和相互作用。

指令级并行是计算机体系结构中的一个重要概念,它可以提高计算机的性能和效率。

本文将详细介绍计算机体系结构指令级并行的基础知识。

一、什么是计算机体系结构指令级并行?计算机体系结构指令级并行是指在计算机指令的执行过程中,同时执行多条指令,以提高计算机的性能和效率。

传统上,计算机执行一条指令需要按照顺序依次执行多个步骤,即取指令、译码、执行、访存和写回。

而指令级并行则允许多个指令的某些步骤并行执行,从而加快指令的执行速度。

二、指令级并行的基本原理1. 流水线技术流水线是指将指令的执行过程分为多个阶段,并使每个阶段同时执行不同的指令。

每个阶段执行完毕后,指令便进入下一个阶段,以此类推。

这样可以使多条指令同时在不同的阶段执行,达到指令级并行的效果。

2. 超标量技术超标量是指在一个时钟周期内,同时发射并执行多条指令。

通过提高处理器的运算能力和硬件资源,可以达到超标量执行多条指令的效果。

三、指令级并行的优势和挑战1. 优势指令级并行可以提高计算机的性能和效率,缩短程序的执行时间。

通过同时执行多条指令,可以充分利用计算机硬件资源,加快指令的执行速度。

2. 挑战指令级并行虽然可以提高计算机的性能,但同时也带来了一些挑战。

例如,指令之间可能存在数据依赖关系,需要解决数据相关性问题。

此外,指令级并行还需要考虑硬件资源分配和调度问题,以充分利用计算机的处理能力。

四、指令级并行的应用指令级并行广泛应用于现代计算机体系结构中。

例如,现代CPU通过流水线和超标量技术实现指令级并行,提高计算机的性能。

同时,指令级并行也被用于并行计算和分布式系统中,以加快任务的执行速度。

五、结论计算机体系结构指令级并行是提高计算机性能和效率的重要手段之一。

通过流水线和超标量技术,可以实现指令的并行执行,加快程序的执行速度。

计算机体系结构知识点汇总

第一章电脑体系结构的基本概念1.电脑系统结构的经典定义程序员所看到的电脑属性,即概念性结构与功能特性。

〔电脑组成:指电脑系统结构的逻辑实现。

电脑实现:电脑组成的物理实现〕2.电脑系统的多级层次结构:1.虚拟机:应用语言机器->高级语言机器->汇编语言机器->操作系统机器2.物理机:传统机器语言机器->微程序机器3.透明性:在电脑技术中,把这种本来存在的事物或属性,但从某种角度看又好似不存在的概念称为透明性。

4.编译:先用转换程序把高一级机器上的程序转换为低一级机器上等效的程序5.解释:对于高一级机器上的程序中的每一条语句或指令,都转去执行低一级机器上的一段等效程序。

6.常见的电脑系统结构分类法有两种:Flynn分类法、冯氏分类法〔按系统并行度P m:计算机系统在单位时间内能处理的最大二进制位数〕进行分类。

Flynn分类法把电脑系统的结构分为4类:单指令流单数据流(SISD)单指令流多数据流(SIMD)多指令流单数据流(MISD)多指令流多数据流(MIMD)IS指令流,DS数据流,CS〔控制流〕,CU〔控制部件〕,PU〔处理部件〕,MM,SM〔表示存储器〕7.电脑设计的定量原理:1.大概率事件优先原理〔分配更多资源,到达更高性能〕2.Amdahl定理:加速比:S n=T0(加速前)T n(加速后)=1(1−Fe)+Fe/Se(Fe为可改良比例〔可改良部分的执行时间/总的执行时间〕,Se为部件加速比〔改良前/改良后〕3.程序的局部性原理:时间局部性:程序即将使用的信息很可能是目前使用的信息。

空间局部性:即将用到的信息可能与目前用到的信息在空间上相邻或相近。

4.CPU性能公式:1.时钟周期时间2.CPI:CPI = 执行程序所需的时钟周期数/IC3.IC(程序所执行的指令条数)8.并行性:电脑系统在同一时刻或者同一时间间隔内进行多种运算或操作。

同时性:两个或两个以上的事件在同一时刻发生。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高等计算机系统结构第3章-指令级并行及其动态开发流水线技术就是指令重叠执行技术,达到加快运算速度的目的。

三种流水线冲突:◆结构冲突(structure hazard):由硬件资源冲突引起(资源冲突)当硬件在指令重叠执行中不能支持指令所有可能的组合时发生的冲突。

(需要更多的硬件资源)◆数据冲突(data hazard):下一条指令要用到上一条指令的结果。

在同时执行的几条指令中,一条指令依赖于前一条指令的数据,却得不到时发出的冲突。

(需要定向,编译器调度)◆控制冲突(control hazard):由转移指令或其他改变PC指令引起.(尽早检测条件,计算目标地址,延迟转移,预测)由于这三种流水线冲突,导致流水线性能降低,不能运作在理想的重叠状态,需要插入停顿周期,从而使流水线性能降低。

指令之间可重叠执行性称为指令级并行性(Instruction Parallelism-ILP)。

因此进一步研究和开发指令之间的并行性,等于拓宽指令重叠执行的可能性,从而能进一步提高流水线的性能。

提高指令级并行度方法:◆流水线动态调度:依赖硬件技术广泛用于桌面电脑和服务去处理器中,包括Pentium III 和Pentium 4,Athlon,MIPS R10000/12000,Sun UltrSPARC III 等◆流水线静态调度:依赖软件技术更多的用于嵌入式处理器中,一些桌面电脑和服务产品也使用,如IA-64系统结构和Intel 的Itanium .术语:◆流水级(pipe stage):流水线由多个流水级组成,通常一条指令由n 级流水级完成。

每个流水级完成指令的部分任务。

◆吞吐量(throughput):单位时间内流出流水线的指令数。

◆机器周期(machine cycle):不同流水线完成指令功能不等,所需时间有长有短,因此设计流水线的关键是合理划分指令功能,使每一流水级完成指令功能的时间大致相等。

机器周期由最长流水级的时间决定,通常等于时钟周期。

第3章指令级并行及其动态开发 3.1 指令级并行概念Visualizing Pipelining第3章指令级并行及其动态开发Visualizing PipeliningI n s t r.O r d e r Time (clock cycles)Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Cycle 1Cycle 2Cycle 3Cycle 4Cycle 6Cycle 7Cycle 5One Memory Port/Structural HazardsI n s t r. O r d e rTime (clock cycles)LoadInstr 1Instr 2Instr 3Instr 4RegALU DMemIfetch RegRegALU DMemIfetch RegRegALU DMemIfetch RegRegALU DMemIfetch Reg Cycle 1Cycle 2Cycle 3Cycle 4Cycle 6Cycle 7Cycle 5RegALU DMemIfetch Reg结构冲突使得必须插入流水气泡I n s t r.O r d e r Time (clock cycles)Load Instr 1Instr 2Stall Instr 3Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Cycle 1Cycle 2Cycle 3Cycle 4Cycle 6Cycle 7Cycle 5Reg A L U DMem Ifetch RegBubble Bubble Bubble Bubble Bubble 改进方法: (1)增加硬件的拷贝数(2)使硬件流水化Data Hazards第3章指令级并行及其动态开发◆Consider the instruction sequence:DADD R1,R2,R3DSUB R4,R1,R3AND R6,R1,R7OR R8,R1,R9XOR R10,R1,R11◆The result in R1is produced after itis required by the last threeinstructions.Data Hazard on R1第3章指令级并行及其动态开发I n s t r.O r d e r DADD R1,R2,R3DSUB R4,R 1,R3AND R6,R 1,R7OR R8,R 1,R9XOR R10,R 1,R11Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Reg A L U DMem Ifetch Reg Time (clock cycles)IF ID/RF EX MEMWB◆RAW(Read after write):先写后读相关如:I: ADD R1,R2,R3J: SUB R4,R1,R3J指令读R1,但I指令还没将结果写入R1最普遍的一种数据冲突。

可以采用旁路机构克服(但不是所有的数据冲突可采用旁路的方法解决)。

◆WAW(Write after write) :写写相关如:I: SUB R1,R4,R3J: ADD R1,R2,R3K: MUL R6,R1,R7这种数据冲突主要出现在写操作过程多于一个流水线机器中,或前一条指令插入Stall,而后面指令继续执行下去的情况。

(即各指令在流水线中所需级数不同时引起WAW)◆WAR(Write after read):先读后写相关如:I: SUB R4,R1,R3J: ADD R1,R2,R3K: MUL R6,R1,R7J指令写R1在I指令读R1前完成,导致I指令读出一个错误的新值这种冲突出现在某些指令写结果较早,而某些指令读源操作数较迟的情况。

因为流水线的自然结构是指令读操作数在写操作数之前,因此种类冲突很少。

以下情形可出现WAR冲突复杂指令支持自动增量的寻址模式需要较迟读操作指令乱序执行使用旁路减少数据冲突引起的停顿(1)第3章指令级并行及其动态开发Minimizing Data Hazard Stalls By Forwarding ◆Forwarding also called bypassing or short-circuiting .◆Forwarding looks at where a result isactually generated, and where it is actually needed, and connects those points in the pipeline.(旁路思想即把结果直接送到需要它的功能部件)Forwarding to Avoid Data Hazard第3章指令级并行及其动态开发Time (clock cycles)I n s t r.O r d e rDADD R 1,R2,R3DSUB R4,R 1,R3AND R6,R 1,R7OR R8,R 1,R9XOR R10,R 1,R11Reg A L UDMemIfetch RegReg A L UDMemIfetch RegReg A L UDMemIfetch RegReg A L UDMemIfetch RegReg A L UDMemIfetch Reg从EX/MEM 和MEM/WB 流水线寄存器到DSUB 和AND 的输入被旁路到ALU 部件的第一个输入端。

OR 操作通过旁路接收数据并非所有的数据冲突可采用旁路的方法解决。

LD R1,0(R2)DSUB R4,R1,R5AND R6,R1,R7OR R8,R1,R9R1最早等到第四拍MEM 结束,才能得到.(即才能从Data Memory 读入,存入暂存器)DSUB 所用的R1最迟在第三拍EX 开始是要准备好,与LD 相差一拍Time (clock cycles)I n s t r.O r d e r LD R1, 0(R2)DSUB R4,R1,R6AND R6,R1,R7OR R8,R1,R9RegALU DMemIfetch RegRegALUDMemIfetch RegRegALUDMemIfetch RegRegALU DMemIfetch Reg说明:这里和结构冲突有些不一样,插入的气泡没有直接影响指令的取入,气泡仅使DSUB 指令进入EX 级推迟一个流水节拍。

气泡是纵向冒出的,造成第4个流水节拍没有启动,而第6个流水节拍时也没有结束指令。

Time (clock cycles)OR R8,R 1,R9I n s t r.O r d e rLD R1, 0(R2)DSUB R4,R1,R6AND R6,R 1,R7Reg A L UDMemIfetch RegRegIfetch A L UDMemRegBubbleIfetchA L UDMemRegBubbleReg Ifetch A L UDMemBubbleRegDependences◆两条指令是相互独立的,则是并行的,其执行顺序允许重排;◆两条指令是相关的,则不是并行的,其执行顺序不允许重排;◆明确指令相关性对 调度的可行性程序并行程度的多少如何利用程序的并行性至关重要。

◆存在三类相关性 数据相关性 名字相关性 控制相关性第3章指令级并行及其动态开发数据相关性(data dependences)◆定义:指令j 相对于指令i 存在数据相关性,则下列条件之一必定成立:指令i 产生的结果被指令j 所用,或指令j 与指令k 数据相关,以及指令k 与指令i 数据相关。

(即存在相关)◆相关性是程序的一种性质◆存在相关性仅仅指出存在冲突(hazard)的可能性,但是否会造成可检测到的冲突,以及是否会造成真正的停顿则是流水线组织的性质。

◆相关性的主要特性相关性预示存在冲突的可能性; 相关性决定必须遵循的计算顺序;相关性决定可被利用的并行性的上限。

第3章指令级并行及其动态开发数据相关性(2)◆消除数据相关性的方法,即克服数据相关性对指令级并行性的限制的方法有两类:保持相关性不变,但设法避免造成冲突----调度法调度法。

即调度指令,将不相关指令插入停顿周期,或改变指令顺序,达到避免出现停顿,又保持相关性不变。

通过变换代码消除相关性----代码变换法代码变换法。