PCI总线接口引脚定义

PCI总线引脚定义

PCI总线引脚定义(资料)PCI Bus Pinout--------------32-Bit Connector StartPin SideB SideA SideB SideA1 -12V TR5T* -12V TRST#2 TCK +12V TCK +12V3 GND TMS GND TMS4 TDO TDI TDO TDI5 +5V +5V +5V +5V6 +5V INTA +5V INTA#7 INTB# INTC# INTB# INTC#8 INTD# +5V INTD# +5V9 PRSNT2~ RSVD PRSNT2~ RSVD10 RSVD +5V(I/0)RSVD +3.3V(I/O)11 PRSNT2# RSVD PRSNT2# RSVD12 GND GND GND KEY13 GND GND GND KEY14 RSVD RSVD RSVD RSVD15 GND RST# GND RST#16 CLK +5V(I/0)CLK +3.3V(I/0)17 GND GNT# GND GNT#18 REQ# GND REQ# GND19 +5V(I/O)RSVD +5V(I/O)RSVD20 AD[31] AD[30] AD[31] AD[30]21 AD[29] +3.3V AD[29] +3.3V22 GND AD[28] GND AD[28]23 AD[27] AD[26] AD[27] AD[26]24 AD[25] GND AD[25] GND25 +3.3V AD[24] +3.3V AD[24]26 C/BE[3]#IDSEL C/BE[3]#IDSEL27 AD[23] +3.3V AD[23] +3.3V28 GND AD[22] GND AD[22]29 AD[21] AD[20] AD[21] AD[20]30 AD[19] GND AD[19] GND31 +3.3V AD[18] +3.3V AD[18]32 AD[17] AD[16] AD[17] AD[16]33 C/BE[2]#+3.3V C/BE[2]#+3.3V34 GND FRAME# GND FRAME#35 TRDY# GND TRDY# GND36 +3.3V TRDY# +3.3V TRDY#37 DEVSEL# GND DEVSEL# GND38 GND STOP# GND STOP#39 LOCK# +3.3V LOCK# +3.3V40 PERR# SDONE PERR# SDONE41 +3.3V SBO# +3.3V SBO#42 SERR# GND SERR# GND43 +3.3V PAR +3.3V PAR44 C/BE[I] #AD[15] C/BE[I] #AD[15]45 AD[14] +3.3V AD[14] +3.3V46 GND AD[13] GND AD[13]47 AD[12] AD[11] AD[12] AD[11]48 AD[10] GND AD[10] GND49 GND AD[09] GND AD[09]50 Key Key GND GND51 Key Key GND GND52 AD[08] C/BE[0]#AD[08] C/BE[0]#53 AD[07] +3.3V AD[07] +3.3V54 +3.3V AD[06] +3.3V AD[06]55 AD[05] AD[04] AD[05] AD[04]56 AD[03] GND AD[03] GND57 GND AD[02] GND AD[02]58 AD[01] AD[00] AD[01] AD[00]59 +5V(I/O)+5V(I/O)+3.3V(I/O)+3.3V(I/O)60 ACK64# REQ64# ACK64# REQ64#61 +5V +5V +5V +5V62 +5V +5V +5V +5V32-Bit Connector EndKey Key Key KeyKey Key Key Key64-bit Connector Start63 RSVD GND RSVD GND64 GND C/BE[7]#GND C/BE[7]#65 C/BE[6]#C/BE[5]#C/BE[6]#C/BE[S]#66 C/BE[4]#+5V(I/O)C/BE[4]#+3.3V(I/O)67 GND PAR64 GND PAR6468 AD[63] AD[62] AD[63] AD[62]69 AD[61] GND AD[61] GND70 +5V(I/O)AD[60] +3.3V(I/O)AD[60]71 AD[59] AD[58] AD[59] AD[58]72 AD[57] GND AD[57] GND73 GND AD[56] GND AD[56]74 AD[55] AD[54] AD[55] AD[54]75 AD[53] +5V(I/O)AD[53] +3.3V(I/O)76 GND AD[52] GND AD[52]77 AD[51] AD[50] AD[51] AD[50]78 AD[49] GND AD[49] GND79 +5V(I/O)AD[48] +3.3V(I/O)AD[43]80 AD[47] AD[46] AD[47] AD[46]81 AD[45] GND AD[45] GND82 GND AD[44] GND AD[44]83 AD[43] AD[42] AD[43] AD[42]84 AD[41] +5V(I/O)AD[41] +3.3V(I/O)85 GND AD[40] GND AD[40]86 AD[39] AD[38] AD[39] AD[38]87 AD[37] GND AD[37] GND88 +5V(I/O)AD[36] +3.3V(I/O) AD[36]89 AD[35] AD[34] AD[35] AD[34]90 AD[33] GND AD[33] GND91 GND AD[32] GND AD[32]92 RSVD RSVD RSVD RSVD93 RSVD GND RSVD GND94 GND RSVD GND RSVD64-bit Connector End。

PCI卡的引脚定义图

本站推出新的以太网的解决方案,就是用RTL8029AS的PCI总线的以太网的网卡。

单片机控制PCI总线的以太网网卡成为现实,PCI总线也进入了嵌入式领域。

整个系统构成如下:我们以PCI标准V2.1为蓝本来做说明,因为PCI V2.2是66Mhz的64 bit总线标准.RTL8029AS PCI网卡只支持V2.1标准(33Mhz,32 bit) ,在上面的定义中,我省略了很多GND的引脚的定义,在标准的定义中,有很多的引脚被定义为GND,主要是用来做信号的屏蔽和隔离的作用.特别是对66Mhz的PCI总线.因为我们用到的总线的频率不高,连线也不长,可以不需要这些GND的引脚.去掉这些GND引脚的好处是方便布线.去掉这些引脚不会影响性能,因为在RTL8139(100Mhz)的网卡里,也是没有连接这些引脚的.我们用的是PCI V2.1版5伏的32位卡的标准.PCI卡分为主(Master),从(Target)两种类型,主卡可以控制PCI总线,从卡不能控制PCI总线.RTL8029AS网卡只能作为从卡,也就是说它只能作为Target,而不能做为主设备.标准的主设备至少有49条线跟PCI总线相连.从设备至少有47条线跟PCI总线相连.要支持中断的话,加一条INTA#引脚(共50或48条引脚).图中引脚名称中带#号的表示该引脚为低电平有效,不带#号的为高电平有效.INTA#是带"#"号的,表示低电平有效,就是说当它为低电平时引起中断,平时为高电平.上图左边的为必须要的引脚,右边的为可选的引脚(我们可以都不用). 因为RTL8029AS 只能作为target设备,所以上面的主设备才有的引脚(REQ#,GNT#),可以不用.(在我提供的demo里,这些引脚还是被连接到逻辑电路EPM7128S里(PAR等引脚也被连到CPLD里,为了将来可以使用RTL8139),但是事实上并没有用到,连到逻辑电路的目的是为了将来可能使用RTL8139(10M/100M自适应网卡)来代替10M的RTL8029AS网卡,因为RTL8139可以做为主设备进行DMA数据传输,所以需要这两个引脚,但是RTL8139需要的控制逻辑要比RTL8029AS复杂).那么对于RTL8029AS来说,只要用从设备的48个引脚.是不是一定要这48条引脚呢?答案是还可以进行简化.下面我将做一个分析:PAR引脚:PAR是奇偶校验引脚,校验AD[31..0]和C/BE[3..0]#.但是因为RTL8029AS不作奇偶校验,也不报告校验错误,因此该引脚也可以不要.PERR#:为校验报告,因为RTL8029AS不作该报告,可以不要.SERR#:系统错误报告,RTL8029AS同样不报告系统错误,可以不要.DEVSEL#:为RTL8029AS的输出引脚,以表示地址译码有效.因为RTL8029AS最慢不会超过4个PCI时钟有效, 一般是第2个PCI时钟便有效.我们提供的demo的PCI的时钟为22.1184Mhz,而单片机的机器周期(总线速度)每秒只有22.1184/12=1.8432Mhz,比PCI总线慢12倍,也就是说不需要经过0.4个单片机的机器周期,RTL8029AS便会输出DEVSEL#有效.对单片机来说,网卡是随时准备好的.因此没有必要去判断该引脚,该引脚也可以不要.TRDY#:为网卡输出的准备好的信号.网卡准备好最慢不会超过8个PCI时钟周期(不超过0.8个单片机机器周期), 对于单片机来说,网卡同样是随时准备好的.该引脚也可以不要.STOP#:RTL8029AS没有这个引脚,所以可以不要.那么PCI的接口信号就被简化为:AD[31..0]C/BE[3..0]#FRAME#IRDY#IDSEL#CLKRST#INTA#共42条引脚,如果不想用中断方式来驱动网卡,那么中断INTA#也可以不要.我的demo 里还是将INTA#连到CPLD里.以方便用户使用.去掉这些引脚的目的,是为了简化逻辑设计,altera提供的标准的PCI核一般至少需要440个LCELL,相当于1万门以上的逻辑,必须使用FLEX10K,APEX20K等大容量的CPLD,而这些芯片都比较贵.而我使用的EMP7128才2500门(共128个LCELL),虽然我用的EPM7128有128个LCELL,但我只用了其中的67个LCELL,用了不到1500门.可见简化接口有着非常重要的意义,就是简化逻辑,降低成本。

PCI插槽引脚信号定义中文说明

PCI 总线起始讯号

5. GNT[4:0]# (PCI BUS GRANT)

PCI 总线控制认可讯号

6. IRDY# (INITIATOR READY)

数据读取写入讯号

7. LOCK# (PCI BUS LOCK)

总线锁住讯号

8. PAR (PCI BUS PARITY)

地址与位传送之同位检错讯号

9. PCLK (PCI CLOCK)

PCI 时脉讯号

10.PGNT# (PCI GRANT TO PERIPHERAL BUS CONTROLLER)

PCI 总线对外部外围装置之需求同意认可讯号

11. PERQ# (PCI REQUEST FROM PERIPHERAL BUS CONTROLLER)

外围处理器对PCI总线要求讯号

12. REQ[4:0]# (PCI BUS REQUEST)

PCI 总线需求讯号

13. RESET# (RESET)

系统重置讯号

14. SERR# (SYSTEM ERROR)

系统错误侦测讯号可产生NMI 不可屏蔽中断

15. STOP# (PCI BUS STOP)

PCI 总线放弃或重试数据传送之讯号

16. TRDY# (TARGET READY)

PCI 总线数据读取传送讯号

17.WSC# (WRITE SNOOP COMPLETE)

I /O APIC 芯片有上时之中断讯息传送讯号。

完整版PCI总线接口引脚定义

MDREQ#/MDPAF/EOT#

MODE[1:0](Bus Mode)11:M模式;10:J模式;01:保留;00:C模式;

TEST(Test Pin)芯片检测管脚,高为检测,低为工作,平时置低;

33

C/BE[2]#

+3.3V

34:

Ground

1

FRAME

#

35

irdY#

Groun]l

36

+3.3V

TRDY;

37

D

jevseL

Groun]l

38「

Ground

stOP;

39

]oc*

+3.3V

40

Perr#

Reserved*

41

+3.3V

Reserved*

42:

「seRI:

Groቤተ መጻሕፍቲ ባይዱn|l

43

+3.3V

J

AD[26]:

24

AD[25]

3roun|l

25

+3.3V

AD[24]:

26

C/BE[3]# |

1

#idsEL

27「

AD[23]

+3.3V

28

Ground

AD[22] 1

29

AD[21]

i

AD[20]:

30

AD[19]|

Groun[l

31:

+3.3V

JI

AD[18] 1

32

AD[17]

(完整版)PCI总线接口引脚定义

由于M模式使用范围比较小,J模式使用起来控制比较复杂,一般使用C模式。

所有模式AD[31:0](Address and Data)地址和时钟复用,首先是一个地址段,后面跟着一个或多个数据段,支持突发模式的读写;C/BE[3:0]#(Bus Command and Byte Enables)总线命令和数据使能复用管脚,在AD 为地址线的时候作为总线命令,在AD为数据线的时候作为数据使能;DEVSEL#(Device Select)有效的时候表示当前设备被选中,作为输入端口;FRAME#(Cyclone Frame)由主设备驱动,用来表示当前设备已经开始接入,总线开始传输数据。

有效:传输数据。

无效:完成最后一个数据的传输;GNT#(Grant)用来表示当前接入的设备已经被接受;IDSL(Initialization Device Select)在配置寄存器读写的时候用做片选信号;INTA#(Interrupt A)PCI中断请求;IRDY#(Initiator Ready)说明当前数据有效,可以并要完成传输;LOCK#(Lock)提示有自动操作,需要消耗若干个时钟来完成操作;PAR(Parity)作为AD和C/BE两部分总线的基偶校验,在传输地址的时候PAR要在地址传输完毕后一个时钟周期保持稳定。

对于数据段,PAR要在IRDY#或者TRDY#有效以后一个时钟周期保持稳定。

一旦PAR数据有效,将保持有效到当前数据或地址段传输结束;PCLK(Clock)系统时钟,9054工作在33MHz;PERR#(Parity Error)用来报告奇偶校验错误,不包括特殊周期;PME#(Power Management Event)唤醒中断;REQ#(Request)请求信号,通知总线判决器,当前设备必须使用总线;RST#(Reset)系统复位;SERR#(System Error)用来报告特殊周期的奇偶校验错误和其他系统错误;STOP#(Stop)要求主系统,停止当前设备的数据传输;TRAY#(Target Ready)目标设备准备完毕,可以传输当前数据;BIGEND#(Big Endian Select)CCS#(Configuration Register Select)低有效的片选信号;EECS(Serial EEPROM Chip Select)选择串行EEPROM;EEDI/DDEO(Serial EEPROM Data In/ Serial EEPROM Data Out)控制串行EEPROM 读写数据;EESK(Serial Data Clock)EEPROM读写时钟;ENUM#(Enumeration)突发输出,用来表示一个使用PCI9054芯片的适配器刚刚从一个CPI总线通道里面加入或者移出;LCLK(Local Processor Clock)本地时钟输入;LEDon/LEDin LED控制;LFRAME#(PCI Buffered FRAME# Signal)指示PCI总线的状态;LINT#(Local Interrupt)本地总线中断。

PCI总线接口详细定义(自己整理)

+3.3 VDC

A54

AD6

Address/Data 6

A55

AD4

Address/Data 4

A56

GND21

Ground

A57

AD2

Address/Data 2

A58

AD0

Address/Data 0

A59

+5V

+3.3V

Signal Rail

+V I/O (+5 V or +3.3 V)

Pin

+5V

+3.3V

Universal

Description

A1

TRST

Test Logic Reset

A2

+12V

+12 VDC

A3

TMS

Test Mde Select

A4

TDI

Test Data Input

A5

+5V

+5 VDC

A6

INTA

Interrupt A

A7

INTC

Interrupt C

A27

+3.3V03

+3.3 VDC

A28

AD22

Address/Data 22

A29

AD20

Address/Data 20

A30

GND12

Ground

A31

AD18

Address/Data 18A32Fra bibliotekAD16

Address/Data 16

A33

+3.3V05

+3.3 VDC

PCI插槽引脚排列顺序,引脚定义,PCI插槽引脚顺序怎样数

+

+电压输入

重要检测点

B42

SERR

系统错误

B43

+

+电压输入

重要检测点

B44

C/BE1

命令字节允许信号

B45

AD14

地址/数据总线

各地址/数据总线的对地阻值均应相同(ADO至AD31)

B46

GND

地

B47

AD12

地址/数据总线

各地址/数据总线的对地阻值均应相同(ADO至AD31)

B48

AD1O

A58

ADO

地址/数据总线

各地址/数据总线的对地阻值均应相同(ADO至AD31)

A59

+5V

+5V电压输入

重要检测点

A60

REQ64

请求64位传送

Bl

-12V

-12V电压输入

重要检测点

B2

TCK

测试时钟

B3

GND

地

B4TLeabharlann O测试数据输出B5

+5V

+5V电压输入

重要检测点吧

B6

+5V

+5V电压输入

重要检测点

B25

+

+电压输入

重要检测点

B26

C/BE3

命令字节允许信号

B27

AD23

地址/数据总线

各地址/数据总线的对地阻值均应相同(ADO至AD31)

B28

GND

地

B29

AD21

地址/数据总线

各地址/数据总线的对地阻值均应相同(ADO至AD31)

B30

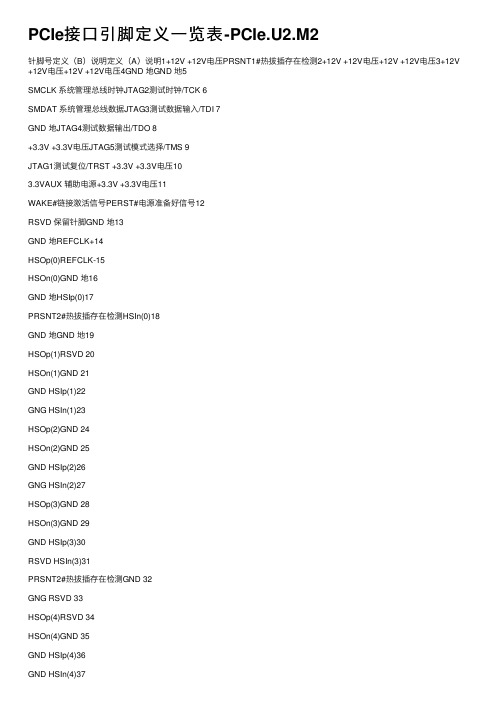

PCIe接口引脚定义一览表-PCIe.U2.M2

PCIe接⼝引脚定义⼀览表-PCIe.U2.M2针脚号定义(B)说明定义(A)说明1+12V +12V电压PRSNT1#热拔插存在检测2+12V +12V电压+12V +12V电压3+12V +12V电压+12V +12V电压4GND 地GND 地5SMCLK 系统管理总线时钟JTAG2测试时钟/TCK 6SMDAT 系统管理总线数据JTAG3测试数据输⼊/TDI 7GND 地JTAG4测试数据输出/TDO 8+3.3V +3.3V电压JTAG5测试模式选择/TMS 9JTAG1测试复位/TRST +3.3V +3.3V电压103.3VAUX 辅助电源+3.3V +3.3V电压11WAKE#链接激活信号PERST#电源准备好信号12RSVD 保留针脚GND 地13GND 地REFCLK+14HSOp(0)REFCLK-15HSOn(0)GND 地16GND 地HSIp(0)17PRSNT2#热拔插存在检测HSIn(0)18GND 地GND 地19HSOp(1)RSVD 20HSOn(1)GND 21GND HSIp(1)22GNG HSIn(1)23HSOp(2)GND 24HSOn(2)GND 25GND HSIp(2)26GNG HSIn(2)27HSOp(3)GND 28HSOn(3)GND 29GND HSIp(3)30RSVD HSIn(3)31PRSNT2#热拔插存在检测GND 32GNG RSVD 33HSOp(4)RSVD 34HSOn(4)GND 35GND HSIp(4)36GND HSIn(4)37HSOp(5)GND 38HSOn(5)GND 39GND HSIp(5)40GND HSIn(5)41HSOp(6)GND 42HSOn(6)GND 43GND HSIp(6)44GND HSIn(6)45HSOp(7)GND 46HSOn(7)GND 47GNDHSIp(7)0号信道发送差分信号对差分信号对参考时钟0号信道接收差分信号对x1带宽模式x4带宽模式48PRSNT2#热拔插存在检测HSIn(7) 49GND GND 50HSOp(8)RSVD 51HSOn(8)GND 52GND HSIp(8) 53GND HSIn(8) 54HSOp(9)GND 55HSOn(9)GND 56GND HSIp(9) 57GND HSIn(9) 58HSOp(10)GND 59HSOn(10)GND 60GND HSIp(10) 61GND HSIn(10) 62HSOp(11)GND 63HSOn(11)GND 64GND HSIp(11) 65GND HSIn(11) 66HSOp(12)GND67HSOn(12)GND 68GND HSIp(12) 69GND HSIn(12) 70HSOp(13)GND 71HSOn(13)GND 72GND HSIp(13) 73GND HSIn(13) 74HSOp(14)GND 75HSOn(14)GND 76GND HSIp(14) 77GND HSIn(14) 78HSOp(15)GND 79HSOn(15)GND 80GND HSIp(15) 81PRSNT2#热拔插存在检测HSIn(15) 82GND GND模式x16带宽模式宽模式。

PCI总线引脚定义

(OPEN)96u电子资料网

(OPEN)96u电子资料网

Ground or Open (Key)96u电子资料网

A1396u电子资料网

GND0596u电子资料网

(OPEN)96u电子资料网

(OPEN)96u电子资料网

Ground or Open (Key)96u电子资料网

A1496u电子资料网

A5396u电子资料网

+3.3V1196u电子资料网

96u电子资料网

96u电子资料网

+3.3 VDC96u电子资料网

A5496u电子资料网

AD696u电子资料网

96u电子资料网

96u电子资料网

Address/Data 696u电子资料网

A5596u电子资料网

AD496u电子资料网

96u电子资料网

96u电子资料网

96u电子资料网

Address/Data 2096u电子资料网

A3096u电子资料网

GND1296u电子资料网

96u电子资料网

96u电子资料网

Ground96u电子资料网

A3196u电子资料网

AD1896u电子资料网

96u电子资料网

96u电子资料网

Address/Data 1896u电子资料网

A3296u电子资料网

A2796u电子资料网

+3.3V0396u电子资料网

96u电子资料网

96u电子资料网

+3.3 VDC96u电子资料网

A2896u电子资料网

AD2296u电子资料网

96u电子资料网

96u电子资料网

Address/Data 2296u电子资料网

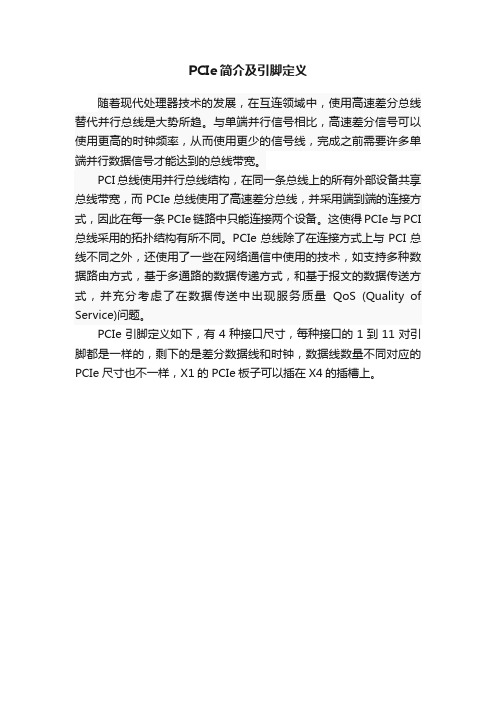

PCIe简介及引脚定义

PCIe简介及引脚定义

随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI 总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe引脚定义如下,有4种接口尺寸,每种接口的1到11对引脚都是一样的,剩下的是差分数据线和时钟,数据线数量不同对应的PCIe尺寸也不一样,X1的PCIe板子可以插在X4的插槽上。

完整版PCI总线接口引脚定义

IDSL(Initialization Device Select)在配置寄存器读写的时候用做片选信号;

INTA#(Interrupt A)PCI中断请求;

IRDY#(Initiator Ready)说明当前数据有效,可以并要完成传输;

LOCK#(Lock)提示有自动操作,需要消耗若干个时钟来完成操作;

33

C/BE[2]#

+3.3V

34:

Ground

1

FRAME

#

35

irdY#

Groun]l

36

+3.3V

TRDY;

37

D

jevseL

Groun]l

38「

Ground

stOP;

39

]oc*

+3.3V

40

Perr#

Reserved*

41

+3.3V

Reserved*

42:

「seRI:

Groun|l

43

+3.3V

从一个CPI总线通道里面加入或者移出;

LCLK(Local Processor Clock)本地时钟输入;

LED on/LEDin LED控制;

LFRAME#(PCI Buffered FRAME# Signal)指示PCI总线的状态;

LINT#(Local Interrupt)本地总线中断。输入到9054,低有效,触发一个PCI中断。 作为输出,等待到一个触发发生;

USERi/BACK0#/LLOCKi#复用管脚

USERo/DREQ0#/LLOCKo#复用管脚

VDD电源

VSS地

PCIe引脚定义和PCIe协议层介绍

PCIe引脚定义和PCIe协议层介绍本文我们将向大家介绍PCIe引脚定义以及PCIe协议层。

1.PCIe引脚定义PCI Express,官方简称PCIe,是计算机总线的一个重要分支, 插槽图片如下:下表列出在边缘(连接器)上的PCI Express卡两侧的导线。

在印刷电路板((PCB))的焊接侧为A侧,并且组件侧的B侧。

PRSNT1# 和PRSNT2# 引脚必须比其余稍短,以确保热插入卡时其余管脚完全插入。

WAKE# 引脚采用全电压唤醒计算机,但必须拉高从备用(电源),以表明该卡是能够唤醒。

2.PCIe协议层PCIE协议中包括应用层、事务层、数据链路层和物理层。

应用层(Appl(ic)ation Layer):应用层是在事务层之上的一层,它处理与连接的设备进行的高级(通信)。

这可能包括配置设备、初始化(寄存器)、发送和接收控制命令等。

事务层(Transac(ti)on Layer):事务层是PCIe协议的核心,它负责将上层软件请求转化为数据传输和交换。

事务层处理内存读写请求、配置空间访问以及其他与连接的设备进行通信的请求。

事务层接收由应用层传来的组成TLP核心部分所需要的(信息),并将数据组装成He(ad)er 和Data(有些TLP没有DATA),计算End CRC (ECRC)。

数据链路层(Data Link Layer):数据链路层接收事务层传过来的TLP包,然后在其前面加上12bit 的Sequence ID,并根据目前所有的信息计算32bit 的CRC (LCRC),并附着在后面。

物理层(Physical Layer):主要职责是处理所有的数据物理传输,发送端数据分发到各个Lane传输(stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加扰(Sc(ram)ble,目的是让0和1分布均匀,去除信道的电磁干扰EMI)去扰(De-scramble),以及8/10或者128/130编码解码,等等。

PCIe 接口 引脚定义 (插槽)

PCIe 接口 引脚定义 (插槽)Pin Side B Connector PinSide A Connector #Name Description#Name DescriptionB1+12v +12 volt powerA1PRSNT#1Hot plug presence detect (热插)X1宽带模式X4宽带模式X8宽带模式B2+12v A2+12v +12 volt power B3RSVD 保留针脚A3+12v B4GND Ground A4GND GroundB5SMCLK SMBus clock (系统管理总线时钟)A5JTAG2TCK (测试时钟)B6SMDAT SMBus data (系统管理总线数据)A6JTAG3TDI (测试数据输入)B7GND Ground A7JTAG4TDO (测试数据输出)B8+3.3v +3.3 volt power A8JTAG5TMS (测试模式选择)B9JTAG1+TRST#A9+3.3v +3.3 volt powerB10 3.3Vaux 3.3v volt power A10+3.3v B11WAKE#Link Reactivation (链接激活信号)A11PWRGDPower Good (电源准备好信号)Mechanical KeyB12RSVD Reserved (保留针脚)A12GNDGroundB13GND Ground A13REFCLK+Reference Clock ,Differential pair B14HSOp(0)Transmitter Lane 0,Differential pairA14REFCLK-B15HSOn(0)A15GND GroundB16GND Ground A16HSIp(0)Receiver Lane 0,Differential pair B17PRSNT#2Hotplug detect A17HSIn(0)B18GND Ground A18GND GroundB19HSOp(1)Transmitter Lane 1,Differential pairA19RSVD Reserved (保留针脚)B20HSOn(1)A20GND GroundB21GND GroundA21HSIp(1)Receiver Lane 1,Differential pair B22GND A22HSIn(1)B23HSOp(2)Transmitter Lane 2,Differential pairA23GND GroundB24HSOn(2)A24GND B25GND GroundA25HSIp(2)Receiver Lane 2,Differential pair B26GND A26HSIn(2)B27HSOp(3)Transmitter Lane 3,Differential pairA27GND GroundB28HSOn(3)A28GND B29GND Ground A29HSIp(3)Receiver Lane 3,Differential pair B30RSVD Reserved (保留针脚)A30HSIn(3)B31PRSNT#2Hot plug detect A31GND GroundB32GNDGround A32RSVDReserved (保留针脚)B33HSOp(4)Transmitter Lane 4,Differential pair A33RSVD Reserved (保留针脚)X8宽带模式X16宽带模式B34HSOn(4)A34GND GroundB35GND GroundA35HSIp(4)Receiver Lane 4,Differential pair B36GND A36HSIn(4)B37HSOp(5)Transmitter Lane 5,Differential pair A37GND GroundB38HSOn(5)A38GND B39GND GroundA39HSIp(5)Receiver Lane 5,Differential pair B40GND A40HSIn(5)B41HSOp(6)Transmitter Lane 6,Differential pair A41GND GroundB42HSOn(6)A42GND B43GND GroundA43HSIp(6)Receiver Lane 6,Differential pair B44GND A44HSIn(6)B45HSOp(7)Transmitter Lane 7,Differential pair A45GND GroundB46HSOn(7)A46GND B47GND GroundA47HSIp(7)Receiver Lane 7,Differential pair B48PRSNT#2Hot plug detect A48HSIn(7)B49GND GroundA49GND GroundB50HSOp(8)Transmitter Lane 8,Differential pair A50RSVD Reserved (保留针脚)B51HSOn(8)A51GND GroundB52GND GroundA52HSIp(8)Receiver Lane 8,Differential pair B53GND A53HSIn(8)B54HSOp(9)Transmitter Lane 9,Differential pair A54GND GroundB55HSOn(9)A55GND B56GND GroundA56HSIp(9)Receiver Lane 9,Differential pair B57GNDA57HSIn(9)B58HSOp(10)Transmitter Lane 10,Differential pair A58GND GroundB59HSOn(10)A59GND B60GND GroundA60HSIp(10)Receiver Lane 10,Differential pair B61GNDA61HSIn(10)B62HSOp(11)Transmitter Lane 11,Differential pair A62GND GroundB63HSOn(11)A63GND B64GND GroundA64HSIp(11)Receiver Lane 11,Differential pair B65GNDA65HSIn(11)B66HSOp(12)Transmitter Lane 12,Differential pair A66GND GroundB67HSOn(12)A67GND B68GND GroundA68HSIp(12)Receiver Lane 12,Differential pairB69GNDA69HSIn(12)B70HSOp(13)Transmitter Lane 13,Differential pair A70GND GroundB71HSOn(13)A71GND B72GND GroundA72HSIp(13)Receiver Lane 13,Differential pair B73GNDA73HSIn(13)B74HSOp(14)Transmitter Lane 14,Differential pair A74GND GroundB75HSOn(14)A75GND B76GND GroundA76HSIp(14)Receiver Lane 14,Differential pair B77GNDA77HSIn(14)B78HSOp(15)Transmitter Lane 15,Differential pair A78GND GroundB79HSOn(15)A79GND B80GND GroundA80HSIp(15)Receiver Lane 15,Differential pair B81PRSNT#2Hot plug present detect A81HSIn(15)B82RSVD#2Hot Plug DetectA82GNDGround。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

由于M模式使用范围比较小,J模式使用起来控制比较复杂,一般使用C模式。

所有模式

AD[31:0](Address and Data)地址和时钟复用,首先是一个地址段,后面跟着一个或多个数据段,支持突发模式的读写;

C/BE[3:0]#(Bus Command and Byte Enables)总线命令和数据使能复用管脚,在AD 为地址线的时候作为总线命令,在AD为数据线的时候作为数据使能;

DEVSEL#(Device Select)有效的时候表示当前设备被选中,作为输入端口;

FRAME#(Cyclone Frame)由主设备驱动,用来表示当前设备已经开始接入,总线开始传输数据。

有效:传输数据。

无效:完成最后一个数据的传输;

GNT#(Grant)用来表示当前接入的设备已经被接受;

IDSL(Initialization Device Select)在配置寄存器读写的时候用做片选信号;

INTA#(Interrupt A)PCI中断请求;

IRDY#(Initiator Ready)说明当前数据有效,可以并要完成传输;

LOCK#(Lock)提示有自动操作,需要消耗若干个时钟来完成操作;

PAR(Parity)作为AD和C/BE两部分总线的基偶校验,在传输地址的时候PAR要在地址传输完毕后一个时钟周期保持稳定。

对于数据段,PAR要在IRDY#或者

TRDY#有效以后一个时钟周期保持稳定。

一旦PAR数据有效,将保持有效到当前数据或地址段传输结束;

PCLK(Clock)系统时钟,9054工作在33MHz;

PERR#(Parity Error)用来报告奇偶校验错误,不包括特殊周期;

PME#(Power Management Event)唤醒中断;

REQ#(Request)请求信号,通知总线判决器,当前设备必须使用总线;

RST#(Reset)系统复位;

SERR#(System Error)用来报告特殊周期的奇偶校验错误和其他系统错误;STOP#(Stop)要求主系统,停止当前设备的数据传输;

TRAY#(Target Ready)目标设备准备完毕,可以传输当前数据;

BIGEND#(Big Endian Select)

CCS#(Configuration Register Select)低有效的片选信号;

EECS(Serial EEPROM Chip Select)选择串行EEPROM;

EEDI/DDEO(Serial EEPROM Data In/ Serial EEPROM Data Out)控制串行EEPROM 读写数据;

EESK(Serial Data Clock)EEPROM读写时钟;

ENUM#(Enumeration)突发输出,用来表示一个使用PCI9054芯片的适配器刚刚从一个CPI总线通道里面加入或者移出;

LCLK(Local Processor Clock)本地时钟输入;

LEDon/LEDin LED控制;

LFRAME#(PCI Buffered FRAME# Signal)指示PCI总线的状态;

LINT#(Local Interrupt)本地总线中断。

输入到9054,低有效,触发一个PCI中断。

作为输出,等待到一个触发发生;

LRESETo#(Local Bus Reset Out)当PCI9054芯片被复位以后,该管脚可以用来驱动其他芯片的RESET#信号;

MDREQ#/MDPAF/EOT#

MODE[1:0](Bus Mode)11:M模式;10:J模式;01:保留;00:C模式;TEST(Test Pin)芯片检测管脚,高为检测,低为工作,平时置低;

USERi/BACK0#/LLOCKi# 复用管脚

USERo/DREQ0#/LLOCKo# 复用管脚

VDD电源

VSS地

C模式:

ADS#(Address Strobe)说明地址有效,总线有新设备接入;

BLAST#(Burst Last)该信号由本地总线控制,表示最后一个字符的传输;

BREQi(Bus Request In)本地总线控制,数据从本地总线输入;

BREQo(Bus Request Out)PCI总线控制,数据从PCI总线输出;

BTERM#(Burst Terminate)作为输入,表示当前突发操作结束,开始下一个突发地址的读写,和PCI9054内部的可编程等待状态生成器一起使用。

作为输出,和READY#一起使用,中断当前突发操作,开始下一个突发操作地址周期;

DP[3:0](Data Parity)奇偶校验数据;

LA[31:2](Address Bus)地址总线;

LBE[3:0]#(Byte Enable)控制数据有效,不同的模式有不同的控制方法;

LD[31:0](Data Bus)数据总线;

LHOLD(Hold Request)发送要求使用本地总线,本地总线决定分配给当前装置以后,判决器发送LHOLDA信号反馈;

LHOLDA(Hold Request)反馈信号;

LSERR#(System Error Interrupt Output)系统错误中断;

LW/R#(Write/?Read)低电平读,高电平写;

READY#(Ready Input/Output)无论主还是从模式,表示数据准备好,有效;

WAIT#(Wait Input/Output)作为输入,控制PCI9054插入等待状态。

作为输出,PCI9054处于Ready状态。