PCB阻抗确认单

Allegro 17.2 布线阻抗分析

Allegro 17.2布线阻抗分析做多层电路板的时候,遇到需要做阻抗要求的时候,一般使用SI9000做阻抗设计。

或者向PCB厂商拿叠层结构信息。

无论哪一种,只是停留在设计层面,在设计PCB的走线线,是否完全做到阻抗一致,还是不确定的。

所以,今天介绍Cadence Allegro 17.2布线阻抗分析是可以让工程师能直观的分析出阻抗的具体情况,能够评估每根走线上的阻抗变化情况,对工程师衡量信号的质量起着关键性的作用。

下面将通过一个实例的方式来讲解使用Cadence Allegro 17.2软件进行布线阻抗分析的具体方法。

(1)选取一个4层电路板的实例文件,如下图所示,选取的这个文件,截图的部分是MCU与SDRAM 存储器的部分,假设需要分析SDRAM走线的阻抗。

(2)选取电路板4层的叠层情况如下,从下图中我们可以看出,这是一个4层电路板,厚度是1.6mm。

其中GND层,VCC层是阻抗线的参考层。

(3) 在叠层管理器的右侧点击Signal Integrity折叠按钮,可以展开信号完整性的计算表格,在这个表格里面可以对布线中所涉及到的单线阻抗和查分阻抗进行预计算。

比如下图中,当在TOP,BOOTOM层布线0.1626mm的单线的时候,布线所具有的阻抗特性是50.699欧姆。

若布线差分线的时候0.1626mm的线宽和0.2032mm的间距,布线所具有的阻抗特性是91.039欧姆。

(4) 接下来我们通过阻抗分析工具来分析SDRAM部分的具体阻抗控制情况,选择Analyze-- Workflow Manager启动分析工具。

如果没这一项,就需要改变Editor,通过File—Change Editor…。

(5)在Impedance Workflow流程中,选择Net Based模式,点击Select Nets弹出网络选择框。

在选择框中选择我们需要分析的网络。

假设需要分析的是SDRAM的地址线,点击选择好相应的SDRAM地址线FMC_A0到FMC_A12,FMC_BA0, FMC_BA1网络后,点击Apply按钮进行确认,然后点击OK退出。

阻抗制作规范操作指引

1、目的:为规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定,使阻抗制作标准化,简单化。

2、范围:适用于本厂客户要求阻抗控制的PCB阻抗设计及CAM制作的阻抗图形设计。

3、参考文件无4、定义4.1特性阻抗(Characteristic Impedance)当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

4.2 差分阻抗(Differential Impedance)二条平行导线与大地绝缘后的阻抗,两条导线与大地彼此之间的阻抗。

5、职责5.1 PE工程部:负责客户阻抗资料的确认和设计制作;5.2 PROD生产部:按照操作指示和制作指示进行生产;5.3 QA品保部:阻抗板在制作过程中的品质监控及确认;5.4 ME工艺部:为阻抗板在制作中提供技术支持。

6、作业内容6.1 客户资料确认6.1.1确认客户压合结构可否满足阻抗控制要求。

6.1.2确认阻抗控制范围是否合理,一般情况下公差标准为±10%。

6.1.3阻抗层控制阻抗线粗设计是否合理,无阻抗线层尽量不做阻抗控制,以降低制作难度。

6.1.4评估客户阻抗控制有否特殊要求,厂内能力能否满足客户要求。

6.2阻抗设计基本原则6.2.1抗设计计算采阻抗计算软件进行计算,根据客户阻抗要求,分别输入介电常数、铜厚、线宽、线距、介电层厚度等相关参数,然后根据我司生产能力制作我司生产工作指示(MI),以指导现场生产。

6.2.2压合结构的确认根据客户要求设计压合结构,除客户指定的压合结构外,压合结构设计的一般原则如下: 6.2.1优先选用厚度较大的基板(尺寸稳定性较好);6.2.2优先选用低成本(或低成本组合)PP;备注:对于同种玻璃布型prepreg,树脂含量高低基本不影响价格,pp厚度与价格无必然联系,特殊PP(如2113,2112,3113,1506,106)价格一般较普通PP(7628, 7630,1080,2116)贵30%以上,为节约成本,在保证压合品质的前提下,PP张数尽量少用,尽量避免使用特殊PP。

PCB线路板阻抗计算公式

PCB线路板阻抗计算公式现在关于PCB线路板的阻抗计算方式有很多种,相关的软件也能够直接帮您计算阻抗值,今天通过polar si9000来和大家说明下阻抗是怎么计算的。

在阻抗计算说明之前让我们先了解一下阻抗的由来和意义:传输线阻抗是从电报方程推导出来(具体可以查询微波理论)如下图,其为平行双导线的分布参数等效电路:从此图可以推导出电报方程取传输线上的电压电流的正弦形式得推出通解定义出特性阻抗无耗线下r=0, g=0 得注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)特性阻抗与波阻抗之间关系可从此关系式推出.Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.叠层(stackup)的定义我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念Oz 本来是重量的单位Oz(盎司)=28.3 g(克)在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下介电常数(DK)的概念电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:ε = Cx/Co = ε'-ε"Prepreg/Core 的概念pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.传输线特性阻抗的计算首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度.在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

PCB阻抗值因素与计算方法.62

PCB阻抗设计及计算简介特性阻抗的定义•何谓特性阻抗〔Characteristic Impedance ,Z0〕•电子设备传输信号线中,其高频信号在传输线中传播时所遇到的阻力称之为特性阻抗;包括阻抗、容抗、感抗等,已不再只是简单直流电的“欧姆电阻〞。

•阻抗在显示电子电路,元件和元件材料的特色上是最重要的参数.阻抗(Z)一般定义为:一装置或电路在提供某特定频率的交流电(AC)时所遭遇的总阻力.•简单的说,在具有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫做阻抗。

设计阻抗的目的•随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。

印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确、无干扰、噪音的传输信号。

•阻抗匹配在高频设计中是很重要的,阻抗匹配与否关系到信号的质量优劣。

而阻抗匹配的目的主要在于传输线上所有高频的微波信号皆能到达负载点,不会有信号反射回源点。

•因此,在有高频信号传输的PCB板中,特性阻抗的控制是尤为重要的。

•中选定板材类型和完成高频线路或高速数字线路的PCB 设计之后,那么特性阻抗值已确定,但是真正要做到预计的特性阻抗或实际控制在预计的特性阻抗值的范围内,只有通过PCB生产加工过程的管理与控制才能到达。

•从PCB制造的角度来讲,影响阻抗和关键因素主要有:–线宽〔w〕–线距〔s〕、–线厚〔t〕、–介质厚度〔h〕–介质常数〔Dk〕εr相对电容率(原俗称Dk介质常数),白容生对此有研究和专门诠释。

注:其实阻焊也对阻抗有影响,只是由于阻焊层贴在介质上,导致介电常数增大,将此归于介电常数的影响,阻抗值会相应减少4%•如上图所示–Z0与线宽W成反比,线宽越大,Z0越小;–Z0与铜厚成反比,铜厚越厚,Z0越小;–Z0与介质厚度成正比,介质厚度越厚,Z0越大;–Z0与介质介电常数的平方根成反比,介电常数越大,Z0越小。

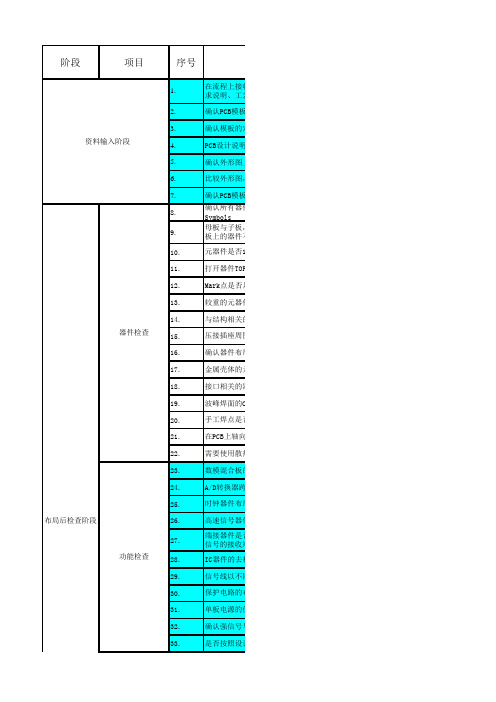

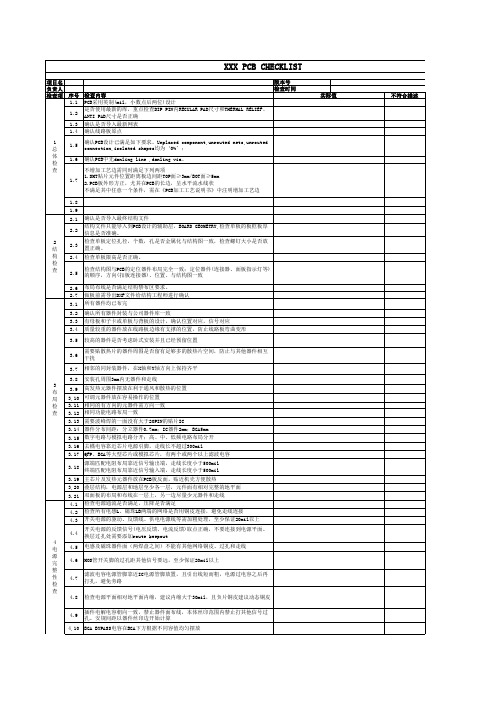

很全面的PCB_checklist_表格

5.

确认外形图上的禁止布放器件和布线区已在PCB模板上体现

6.

比较外形图,确认PCB所标注尺寸及公差无误, 金属化孔和非金属化孔定义准确

7.

确认PCB模板准确无误后最好锁定该结构文件,以免误操作被移动位置

8.

确认所有器件封装是否与公司统一库一致,是否已更新封装库(用viewlog检查运行结果) Symbols

0805及其以下封装求的丝印添加是否正确置有防静电和射频板标识射频板使用的插板方向标识是否对应确标识了槽位名槽位号端口名称护套方向否遗漏位置是否能正确标识器件否符合公司标准要求管脚排列顺序第1脚标志器件的极性标志连接器的方向标识的正确性盘安装的chip元件0805及其以下封装如电阻电容与其焊盘连接的印制线最好从焊盘中心位置对与焊盘连接的印制线必须具有一样的宽度对于线宽小于03mm12mil的引出线可以不考虑此条规定从soicplccqfpsot等器件的焊盘的两端引出板边推荐为大于2mm最小为05mm皮到板边12mm最小为05mm孔径最好不小于板厚的110是否100布通率是否100没有达到100的需要在备注中说明测试点的网络都是经确认可以进行精简的时应该尽量避免出现没有网络连接的死铜孤岛还需注意是否有非法连线未报告的drcottom上的大面积铜箔如无特殊的需要应用网格铜单板用斜网背板用正交网线宽03mm12距05mm20mil区的元件焊盘应设计成花焊盘以免虚焊

29.

信号线以不同电平的平面作为参考平面,当跨越平面分割区域时,参考平面间的连接电容

30.

保护电路的布局是否合理,是否利于分割

31.

单板电源的保险丝是否放置在连接器附近,且前面没有任何电路元件

32.

确认强信号与弱信号(功率相差30dB)电路分开布设

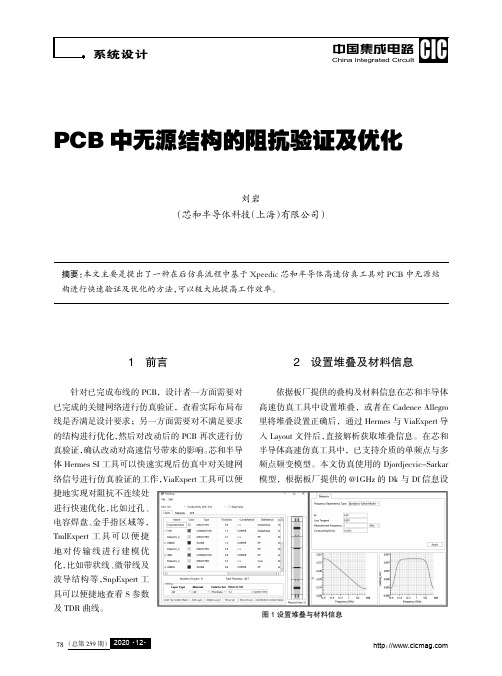

PCB中无源结构的阻抗验证及优化

http ://1前言针对已完成布线的PCB,设计者一方面需要对已完成的关键网络进行仿真验证,查看实际布局布线是否满足设计要求;另一方面需要对不满足要求的结构进行优化,然后对改动后的PCB 再次进行仿真验证,确认改动对高速信号带来的影响。

芯和半导体Hermes SI 工具可以快速实现后仿真中对关键网络信号进行仿真验证的工作,ViaExpert 工具可以便捷地实现对阻抗不连续处进行快速优化,比如过孔、电容焊盘、金手指区域等,TmlExpert 工具可以便捷地对传输线进行建模优化,比如带状线、微带线及波导结构等,SnpExpert 工具可以便捷地查看S 参数及TDR 曲线。

2设置堆叠及材料信息依据板厂提供的叠构及材料信息在芯和半导体高速仿真工具中设置堆叠,或者在Cadence Allegro 里将堆叠设置正确后,通过Hermes 与ViaExpert 导入Layout 文件后,直接解析获取堆叠信息。

在芯和半导体高速仿真工具中,已支持介质的单频点与多频点频变模型。

本文仿真使用的Djordjecvic-Sarkar 模型,根据板厂提供的@1GHz 的Dk 与Df 信息设PCB 中无源结构的阻抗验证及优化刘岩(芯和半导体科技(上海)有限公司)摘要:本文主要是提出了一种在后仿真流程中基于Xpeedic 芯和半导体高速仿真工具对PCB 中无源结构进行快速验证及优化的方法,可以极大地提高工作效率。

图1设置堆叠与材料信息78http ://图3差分对2的模型及TDR 结果图2差分对1的模型及TDR 结果图4金手指处FootPrint、3D 模型及TDR 结果置仿真参数。

Layout 工程师已按照板厂建议的差分线100Ohm 阻抗要求的线宽与间距布线。

下面通过导入Layout 文件进行仿真验证当前设计是否满足阻抗要求,若不满足,则需进一步优化。

3仿真验证关键网络的阻抗由于当前Layout 设计中的关键网络布局一致性较好,可以取具有代表性的网络进行仿真验证。

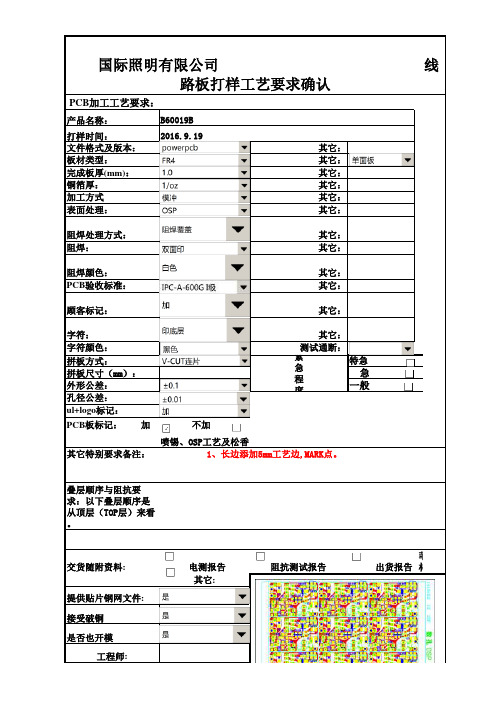

线路板制板确认表

产品名称:打样时间:

文件格式及版本:其它:

板材类型:

其它:完成板厚(mm):其它:铜箔厚:其它:加工方式其它:表面处理:

其它:阻焊处理方式:其它:阻焊:

其它:阻焊颜色:

其它:PCB 验收标准:其它:顾客标记:其它:字符:

其它:字符颜色:测试通断:

拼板方式:

拼板尺寸(mm):外形公差:孔径公差:ul+logo 标记:

叠层顺序与阻抗要求:以下叠层顺序是从顶层(TOP层)来看。

交货随附资料: 电测报告

阻抗测试报告 出货报告菲林

其它:

提供贴片钢网文件:接受破铜是否也开模

工程师:电话:批准人:采购:E-MAIL :

PCB 加工工艺要求:

喷锡、OSP工艺及松香

国际照明有限公司 线

路板打样工艺要求确认

特急一般

B60019B 2016.9.19

PCB 板标记: 加 不加

急紧 急 程 度

PCB图示

其它特别要求备注: 1、长边添加5mm工艺边,MARK点。

powerpcb 阻焊覆盖印底层±0.01白色

±0.1FR4 1/oz 模冲是单面板黑色双面印OSP 1.0 是是

加V-CUT连片IPC-A-600G I级加

电话:传真:交货数量:。

PCB阻抗设计参考(20080720)

Core 3 (Hb3) Pre-peg 4 (Hc4)

L7:P

H

L8:S 15 让我们一起做得更好 ◆ H1:阻焊层厚度,按 0.4mil计算。

PCB阻抗设计参考

◆ W1-W:信号线线底与线顶线宽差值计算:

W1-W差值计算可参考下面的经验值: 基铜铜厚 1/3 1

16

碱性蚀刻(外层) 0.49

PCB阻抗设计参考

◆ H、H1:介质层厚度的计算

H、H1=ΣHb + ΣHc + ΣT

H H1 H H1

L1:S L2:P L3:S L4:S

Pre-peg 1(Hc1) Core 1 (Hb1) Pre-peg 2 (Hc2)

Core 2 (Hb2) Pre-peg 3 (Hc3)

L5:P L6:S

----用于确定阻抗计算模型及阻抗计算参数:W、S

2. 需要进行阻抗控制的信号层所对应的参考层

----用于确定阻抗计算模型

3. 叠层顺序、叠层结构

----用于确定阻抗计算参数:H、H1、Er

4. 铜厚要求

----用于确定阻抗计算参数:T

5. 阻抗控制要求值及公差

5 ----用于客户阻抗要求与阻抗理论计算结果的比对: Zo 让我们一起做得更好

……

PCB阻抗设计参考

◆ 客户须提供完整、正确的阻抗控制要求、设计信息: 以表格形式描述:(推荐!)

6

让我们一起做得更好

PCB阻抗设计参考

◆ 客户须提供完整、正确的阻抗控制要求、设计信息: 以图表形式描述:

7

缺点:未指明信号层对应的参考层、阻抗控制公差。 建议:在资料中注明对应参考层、阻抗控制公差。 让我们一起做得更好 或在客户标准中加以说明。

-GF-F-049 PCB承认书模板 A0

一、 根据AQL 标准二、三、V 割要求及外观检查项目;五、基本电性测试项目,可靠性测试项目内容及试验方法;六、包装检查及要求;与资料对比Reference engineering information注:每批次来料请随货附带来料合格检验报告,初次来料及承认书升级新版本后初次来料请同货附带菲林。

七、PCB图纸详见附页(附图可以增加不能减少);1:单板尺寸视图下图供参考2:拼版尺寸图(拼版尺寸清晰,定位孔等尺寸清晰)模板参考下图3:顶层丝印(丝印等清晰正确)模板参考下图4:底层丝印(丝印等清晰)模板参考下图5:solder层(焊盘等清晰,双面板等需要时加多一页顶层)模板参考下图6:顶层覆铜层(双面板等需要时加多一页)7:底层覆铜层(焊盘等清晰)模板参考下图8:机械层(字迹图印等清晰 V割形式做参考)模板参考下图板材切片检查报告/MICROSECTION INSPECTON REPORT客户Customer: *********照明品名/PN: 2SE40691A周期Code: 客户品名Part No: 样品数Sample Size: PCS 日期Date : 2015-4-29 1、铜厚、焊锡厚、阻焊油墨厚Thickness measurements of Copper,Solder mask(μm)测试仪器Test the instrument:金相显微镜AB EC F板材可焊性、热冲击试验 Solderability &Thermal Shock Test客户Customer: *********照明 品名/PN: 2SE40691A周期Code :客户品名CustomertPart: 样品数Sample Qty:10 PCS日期Date :1.可焊性试验条例(Solderability )Test Method :浸锡时间FLOAT TIME :3-5秒 锡炉温度OVEN TEMPERATURE : 245+/-5℃ 2.试验结果 Test Result :①表面至少95%的地方有良好的润湿性且只有小针孔,剩余部分允许有不润湿和沙眼但这些缺陷不能集中在同一区域At leat95%of the surface area should have good wetting and only small pinhole,dewetting and sand are allowed in the rest of the area,of the ared,and these defects should not concentrate in one area.Yes ②镀通孔内润湿性符合下述图示:( a )The wetting condition of the plated through holes should meet the requirements shown in the following figure.(a) 润湿Wetting (b) 半润湿Half-Wetting (c)不 润湿Non-Wetting 3.热冲击试验条件(Thermal Shock)Test Method:热冲击温度Thermal Shock Temperature: 288±5℃ 热冲击时间Thermal Shock Time: 10±1sec 结果Result:发现Found 未发现Not Found⑤镀层断裂:Plating Crack ⑥起泡Blistering ⑦分层Delamination ⑧层间气泡Laminate V oid ⑨阻焊剥离S/M Peel Off ⑩其它Others。

PCB阻抗知识讲解ppt课件

微带线阻抗计算公式

带线阻抗计算公式

由公式可知无论是哪一种模型,影响其大小的主要因素包括:绝缘材料 的相对介质常数Er,线宽W,介质层厚度(H,D),导线的厚度T。

在实际的制程中,每一项参数都有其制程的变异,这些变异将影响最终线路的 阻抗值。

3.1 介质常数

介质常数是材料的特性,相同频率下不同树脂含量板料的介质常数是不同的,环氧树 脂的介质常数一般是3.5,玻璃纤维布为6.5,树脂含量越高介质常数越小.相同的树脂 含量的材料不同的测试频率情况下介质常数是不同的,一般FR4基材1MHZ为4.7, 1GHZ情况下是4.3,是呈降低趋势, 一般FR4按照4.3计算。

90.34

89.4 96.33 91.91

85.96 92.94 88.23

99.31 100.29 97.99 89.97 91.38 88.62

99.96 101.73

98.2 90.28 92.37 87.41

100.02 101.29 98.45 91.15 92.48 88.48

96.8 99.06 93.61 90.65 91.42

89.5

95.53 106.45 100.66 89.17 90.08 88.59

96.66 97.42 95.37 85.77 88.78 82.64

97.87 99.35 96.46 88.87 89.95 88.11

100.34 101.24 98.94

89 89.78 88.39

从碱性蚀刻后和WF绿油后阻抗测试数据分析可知,WF后测试条阻抗减少10±3.

由表格可知,线宽W 越大,板的阻抗值越低,WF绿油后,由于增加了介质层的后 度,阻抗也会减少,分析得知绿油后阻抗减少值为10±3,均与前面的公式推论符 合。又由于碱性蚀刻后线宽在0.21MM—0.25MM再经绿油后89±4欧姆,能达到该 板的阻抗要求90±9欧姆。所以分析确定碱性蚀刻后线宽的控制范围为 0.23±0.02MM.

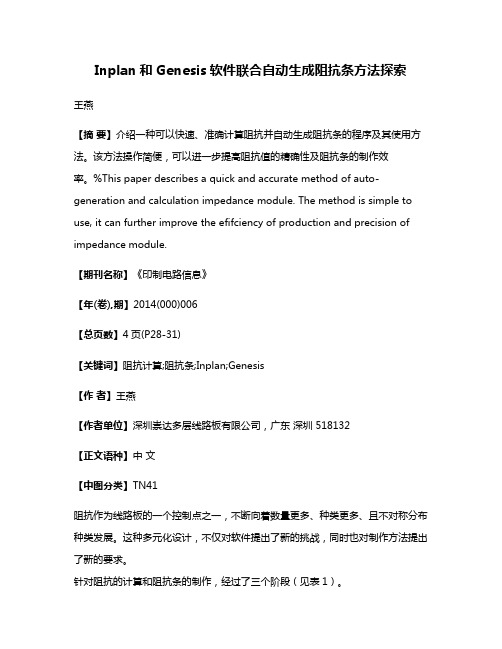

Inplan和Genesis软件联合自动生成阻抗条方法探索

Inplan和Genesis软件联合自动生成阻抗条方法探索王燕【摘要】介绍一种可以快速、准确计算阻抗并自动生成阻抗条的程序及其使用方法。

该方法操作简便,可以进一步提高阻抗值的精确性及阻抗条的制作效率。

%This paper describes a quick and accurate method of auto-generation and calculation impedance module. The method is simple to use, it can further improve the efifciency of production and precision of impedance module.【期刊名称】《印制电路信息》【年(卷),期】2014(000)006【总页数】4页(P28-31)【关键词】阻抗计算;阻抗条;Inplan;Genesis【作者】王燕【作者单位】深圳崇达多层线路板有限公司,广东深圳 518132【正文语种】中文【中图分类】TN41阻抗作为线路板的一个控制点之一,不断向着数量更多、种类更多、且不对称分布种类发展。

这种多元化设计,不仅对软件提出了新的挑战,同时也对制作方法提出了新的要求。

针对阻抗的计算和阻抗条的制作,经过了三个阶段(见表1)。

第一个阶段,效率低,误差大,不利于“多品种、小批量”产品的制作;第二个阶段,效率相对第一阶段有所提升,但仍然处于半自动状态,并且不能充分发挥软件自身的功能,多种软件各自独立,没有实现信息共享。

综合以上两个阶段的不足,目前,阻抗的计算和阻抗条的制作正式步入第三个阶段:使用Inplan和Genesis程序一次性计算阻抗并自动生成阻抗条。

实现了更准确、更快速的阻抗设计,并进一步降低了工作的繁琐性。

本文以一个12层板20组阻抗为例,描述其阻抗计算及阻抗条自动生成过程,通过论述此新程序的使用方法,将新方法和第二阶段的旧方法做一个比较,以说明新方法的优势所在。

XXX_PCB检查表_V0.1

对单元板的位置一致。

6.7 丝印、走线或铺铜等离削边、开窗、板边的间距需要满足至少20mil

6 D

6.8

当细间距的SMT焊盘引脚间需要互联时,应在焊脚外部进行连接,不能在焊盘脚 中间直接连接,铺铜时,挖掉的焊盘中间大于sold的部分

F M

6.9

实连接的连接桥区域(表层、内层)禁止铺铜;实连接处向外扩展1mm的区域内 禁止布器件、走线、铺铜及过孔,避免分板露铜

以Mark点基准点为圆心,直径6mm的圆形区域内不能有与Mark点形状、大小、颜 6.13 色接近的设计(如:焊盘、过孔、亮铜、测试点、表层铺碎铜),两对角Mark

点要有方向设计≥6mm,防止人员误操作时整板贴反

6.14 Mark点不能在无铜区和铺铜区的交界处,且不要放到分割线上,以免影响识别

6.15 不允许焊盘直接放到大面积的亮铜上

3.2 确认所有器件封装与公司器件库一致 3.3 有母板和子卡或单板与背板的设计,确认位置对应,信号对应 3.4 质量较重的器件放在线路板边缘有支撑的位置,防止线路板弯曲变形

3.5 较高的器件是否考虑卧式安装并且已经预留位置

3.6

需要贴散热片的器件周围是否留有足够多的散热片空间,防止与其他器件相互 干扰

6.4

审查兼容不同封装器件的方向是否一致,如1脚标识;兼容布局必须满足工艺设 计规范的要求

6.5

工程需求表单中要求手工写的丝印信息(如散热器丝印、说明文字等)是否已 在PCB上体现(如电源电压和debug)

手工拼板时注意检查实连接位置是否满足对称要求;中心对称拼板辅助块上的

6.6

Mark点要中心对称;镜像对称拼板以x轴为旋转轴,翻转180°后可重合,同时 单一面top/bottom上的mark点要中心对称;手工镜像拼板中需注意Mark点的相

PCB确认表格

5 后锁式座子距板≥0.3mm,翻盖处器件<0.5mm,大器件离座子距离>0.5mm

6 BTB连接器,距连接器<0.5mm处,禁止布局元器件

7 所有连接器必须注明其功能及引脚顺序

8 按键一定要考虑跟客户结构是否有干涉 9 USB在结构允许的前提下尽量使用有定位孔的封装 10 不容易区分的元件,要给出方向性丝印,便于贴片或维修 11

(二) 电子元器件

1 矮小的元器件远离焊盘,高大的元器件远离翻盖座子(或者BTB座子) 2 元器件高度差不宜太过大,对于某些产品结构来说很容易顶屏(或电池)

确认结果

备注

3 正向布局(出FPC方向在板边)连接器,距离板边至少需要预留0.5mm,

4

反向布局(出FPC在板边中中间)连接器,FPC出线方向元器件距离座子≥1.5mm(器件 高度>0.8mm)

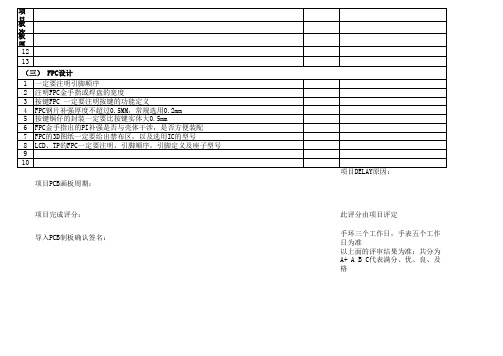

项目PCB画板周期:

项目完成评分:

导入此评分由项目评定

手环三个工作日,手表五个工作 日为准 以上面的评审结果为准:共分为 A+ A B C代表满分、优、良、及 格

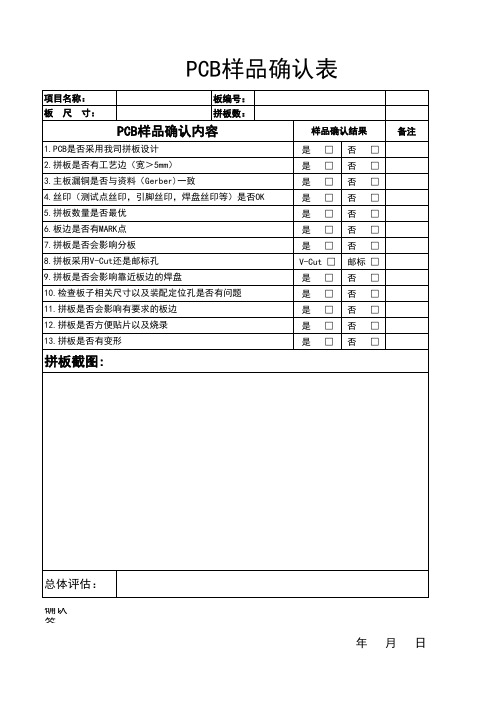

PCB样品确认表

项 目 板 次 板 厚 拼 板

PCB评审确认内容

(一) 焊盘

1 焊盘尺寸不小于1*1mm(除空间局限外) 2 焊盘距离板边距离至少有0.3mm 3 焊盘周边1mm不能出现小的元器件 4 焊盘不能靠近受热易融化的座子以及螺丝孔露铜 5 焊盘之间的间距不小于0.5mm(除了FPC焊盘除外) 6 电池正极焊盘需要远离对地端(包括壳料)

项 目 板 次 板 厚 12 13

(三) FPC设计 1 一定要注明引脚顺序 2 注明FPC金手指或焊盘的宽度 3 按键FPC 一定要注明按键的功能定义 4 FPC钢片补强厚度不超过0.5MM,常规选用0.2mm 5 按键锅仔的封装一定要比按键实体大0.5mm 6 FPC金手指出的PI补强是否与壳体干涉,是否方便装配 7 FPC的3D图纸一定要给出禁布区,以及选用IC的型号 8 LCD、TP的FPC一定要注明,引脚顺序,引脚定义及座子型号 9 10

PCB拼板样品确认表

项目名称: 板 尺 寸:

板编号: 拼板数:

PCB样品确认内容

1.PCB是否采用我司拼板设计 2.拼板是否有工艺边(宽>5mm)

3.主板漏铜是否与资料(Gerber)一致

4.丝印(测试点丝印,引脚丝印,焊盘丝印等)是否OK

5.拼板数量是否最优 6.板边是否有MARK点

7.拼板是否会影响分板

否□ 否□ 否□ 否□ 否□ 否□ 否□ 邮标 □ 否□ 否□ 否□ 否□ 否□

备注

总体评估:确认ຫໍສະໝຸດ 签年月日8.拼板采用V-Cut还是邮标孔

9.拼板是否会影响靠近板边的焊盘

10.检查板子相关尺寸以及装配定位孔是否有问题 11.拼板是否会影响有要求的板边

12.拼板是否方便贴片以及烧录

13.拼板是否有变形

拼板截图:

样品确认结果

是□ 是□ 是□ 是□ 是□ 是□ 是□ V-Cut □ 是□ 是□ 是□ 是□ 是□

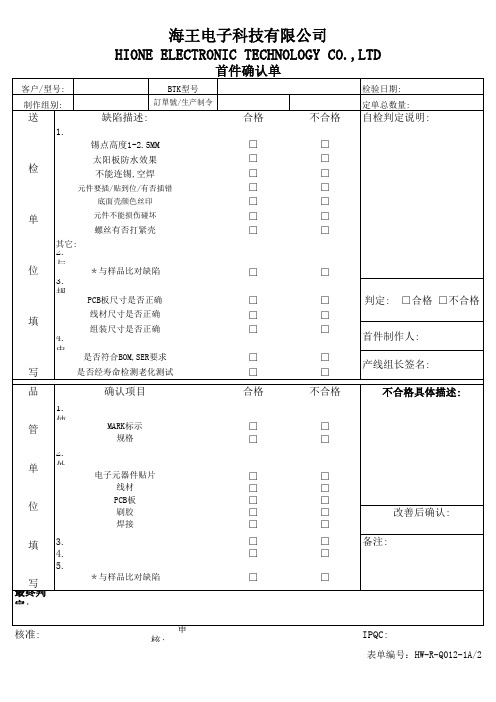

BTK-R-Q012-1A1 首件PCBA确认单

合格 □ □ □ □ □ □ □

不合格 □ □ □ □ □ □ □

பைடு நூலகம்

自检判定说明:

单

其它:

螺丝有否打紧壳

位

2.与样品核对

*与样品比对缺陷

□ □ □ □ □ □ 合格 □ □ □ □ □ □ □ □ □ □

□ □ □ □ □ □ 不合格 □ □ □ □ □ □ □ □ □ □ 备注: 判定: □合格 □不合格

3.规格尺寸 填

PCB板尺寸是否正确 线材尺寸是否正确 组装尺寸是否正确

写

4.电性测试

是否符合BOM,SER要求 是否经寿命检测老化测试

首件制作人: 产线组长签名: 不合格具体描述:

确认项目 1.使用物料是否正确 品 管 单 位 填 写

MARK标示 规格

2.外观是否符合检验规范

电子元器件贴片 线材 PCB板 刷胶 焊接

改善后确认:

3.尺寸是否符合SER 4.电性测试是否符合SER 5.与样品核对

*与样品比对缺陷

最终判定: 核准: 审核: IPQC:

表单编号:HW-R-Q012-1A/2

海王电子科技有限公司

HIONE ELECTRONIC TECHNOLOGY CO.,LTD

首件确认单

客户/型号: 制作组别: BTK型号

訂單號/生产制令

检验日期: 定单总数量:

缺陷描述: 1.外观检验 送 检

锡点高度1-2.5MM 太阳板防水效果 不能连锡,空焊

元件要插/贴到位/有否插错 底面壳颜色丝印 元件不能损伤碰坏

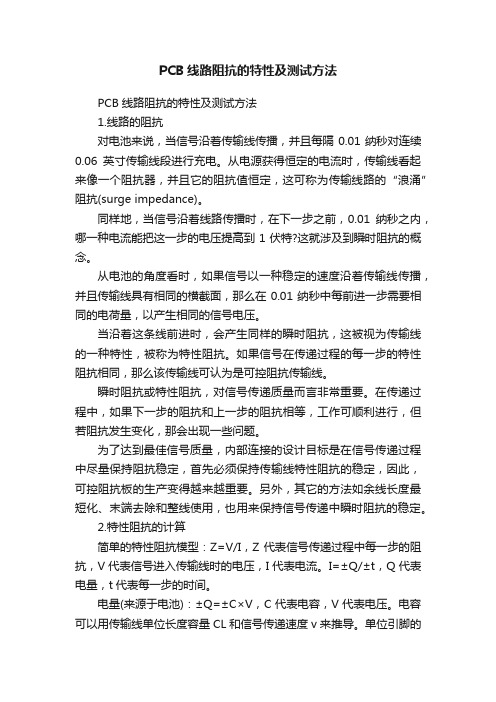

PCB线路阻抗的特性及测试方法

PCB线路阻抗的特性及测试方法PCB线路阻抗的特性及测试方法1.线路的阻抗对电池来说,当信号沿着传输线传播,并且每隔0.01纳秒对连续0.06英寸传输线段进行充电。

从电源获得恒定的电流时,传输线看起来像一个阻抗器,并且它的阻抗值恒定,这可称为传输线路的“浪涌”阻抗(surge impedance)。

同样地,当信号沿着线路传播时,在下一步之前,0.01纳秒之内,哪一种电流能把这一步的电压提高到1伏特?这就涉及到瞬时阻抗的概念。

从电池的角度看时,如果信号以一种稳定的速度沿着传输线传播,并且传输线具有相同的横截面,那么在0.01纳秒中每前进一步需要相同的电荷量,以产生相同的信号电压。

当沿着这条线前进时,会产生同样的瞬时阻抗,这被视为传输线的一种特性,被称为特性阻抗。

如果信号在传递过程的每一步的特性阻抗相同,那么该传输线可认为是可控阻抗传输线。

瞬时阻抗或特性阻抗,对信号传递质量而言非常重要。

在传递过程中,如果下一步的阻抗和上一步的阻抗相等,工作可顺利进行,但若阻抗发生变化,那会出现一些问题。

为了达到最佳信号质量,内部连接的设计目标是在信号传递过程中尽量保持阻抗稳定,首先必须保持传输线特性阻抗的稳定,因此,可控阻抗板的生产变得越来越重要。

另外,其它的方法如余线长度最短化、末端去除和整线使用,也用来保持信号传递中瞬时阻抗的稳定。

2.特性阻抗的计算简单的特性阻抗模型:Z=V/I,Z代表信号传递过程中每一步的阻抗,V代表信号进入传输线时的电压,I代表电流。

I=±Q/±t,Q代表电量,t代表每一步的时间。

电量(来源于电池):±Q=±C×V,C代表电容,V代表电压。

电容可以用传输线单位长度容量CL和信号传递速度v来推导。

单位引脚的长度值当作速度,再乘以每步所需时间t,则得到公式:±C=CL×v×(±)t.综合以上各项,我们可以得出特性阻抗:Z=V/I=V/(±Q/±t)=V/(±C ×V/±t)=V/(CL×v×(±)t×V/±t)=1/(CL×v)可以看出,特性阻抗跟传输线单位长度容量和信号传递速度有关。

PCB阻抗计算参数说明

阻抗计算:1.介电常数 ErEr(介电常数)就目前而言通常情况下选用的材料为 FR-4,该种材料的 Er 特性为随着加载频率的不同而变化,一般情况下 Er 的分水岭默认为 1GHZ(高频)。

目前材料厂商能够承诺的指标<5.4(1MHz),根据我们实际加工的经验,在使用频率为1GHZ 以下的其 Er 认为 4.2 左右。

1.5—2.0GHZ 的使用频率其仍有下降的空间。

故设计时如有阻抗的要求则须考虑该产品的当时的使用频率。

我们在长期的加工和研发的过程中针对不同的厂商已经摸索出一定的规律和计算公式。

⚫7628 --- 4.5 (全部为 1GHz 状态下)⚫2116 --- 4.2⚫1080 --- 3.62.介质层厚度 HH(介质层厚度)该因素对阻抗控制的影响最大故设计中如对阻抗的宽容度很小的话,则该部分的设计应力求准确,FR-4 的H 的组成是由各种半固化片组合而成的(包括内层芯板),一般情况下常用的半固化片为:⚫1080 厚度 0.075MM 、⚫7628 厚度 0.175MM 、⚫2116 厚度 0.105MM 。

3.线宽W对于 W1、W2 的说明:W1此处的 W=W1,W1=W2.规则:W1=W-AW—-设计线宽A—–Etch loss (见上表)走线上下宽度不一致的原因是:PCB 板制造过程中是从上到下而腐蚀,因此腐蚀出来的线呈梯形。

4.绿油厚度:因绿油厚度对阻抗影响较小,故假定为定值 0.5mil。

5.铜箔厚度外层铜箔和内层铜箔的原始厚度规格,一般有0.5OZ、1OZ、2OZ(1OZ 约为35um 或 1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近 1 OZ 左右。

内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个 um。

表层铜箔:可以使用的表层铜箔材料厚度有三种:12um、18um 和 35um。

加工完成后的最终厚度大约是44um、50um和67um,大致相当于铜厚1 OZ、1.5 OZ、2 OZ。