VHDL编写的数字钟

用VHDL编数字时钟

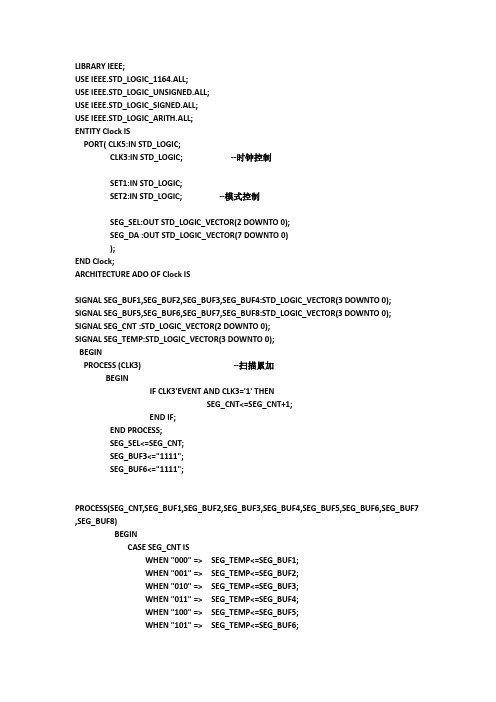

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY Clock ISPORT( CLK5:IN STD_LOGIC;CLK3:IN STD_LOGIC; --时钟控制SET1:IN STD_LOGIC;SET2:IN STD_LOGIC; --模式控制SEG_SEL:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);SEG_DA :OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END Clock;ARCHITECTURE ADO OF Clock ISSIGNAL SEG_BUF1,SEG_BUF2,SEG_BUF3,SEG_BUF4:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL SEG_BUF5,SEG_BUF6,SEG_BUF7,SEG_BUF8:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL SEG_CNT :STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL SEG_TEMP:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS (CLK3) --扫描累加BEGINIF CLK3'EVENT AND CLK3='1' THENSEG_CNT<=SEG_CNT+1;END IF;END PROCESS;SEG_SEL<=SEG_CNT;SEG_BUF3<="1111";SEG_BUF6<="1111";PROCESS(SEG_CNT,SEG_BUF1,SEG_BUF2,SEG_BUF3,SEG_BUF4,SEG_BUF5,SEG_BUF6,SEG_BUF7 ,SEG_BUF8)BEGINCASE SEG_CNT ISWHEN "000" => SEG_TEMP<=SEG_BUF1;WHEN "001" => SEG_TEMP<=SEG_BUF2;WHEN "010" => SEG_TEMP<=SEG_BUF3;WHEN "011" => SEG_TEMP<=SEG_BUF4;WHEN "100" => SEG_TEMP<=SEG_BUF5;WHEN "101" => SEG_TEMP<=SEG_BUF6;WHEN "110" => SEG_TEMP<=SEG_BUF7;WHEN "111" => SEG_TEMP<=SEG_BUF8;WHEN OTHERS => NULL;END CASE;END PROCESS;PROCESS (SEG_TEMP) --显示转换BEGINCASE SEG_TEMP ISWHEN "0000" => SEG_DA<=x"3F";WHEN "0001" => SEG_DA<=x"06";WHEN "0010" => SEG_DA<=x"5B";WHEN "0011" => SEG_DA<=x"4F";WHEN "0100" => SEG_DA<=x"66";WHEN "0101" => SEG_DA<=x"6D";WHEN "0110" => SEG_DA<=x"7D";WHEN "0111" => SEG_DA<=x"07";WHEN "1000" => SEG_DA<=x"7F";WHEN "1001" => SEG_DA<=x"6F";WHEN "1010" => SEG_DA<=x"77";WHEN "1011" => SEG_DA<=x"7B";WHEN "1100" => SEG_DA<=x"39";WHEN "1101" => SEG_DA<=x"3E";WHEN "1110" => SEG_DA<=x"79";WHEN "1111" => SEG_DA<=x"00";END CASE;END PROCESS;PROCESS(Clk5,SET1,SET2)BEGINif(SET1='1' AND SET2='1') then --系统复位SEG_BUF1<="0000";SEG_BUF2<="0000";SEG_BUF4<="0000";SEG_BUF5<="0000";SEG_BUF7<="0000";SEG_BUF8<="0000";elsif(Clk5'event and Clk5='1') thenif(SET1='1' and SET2='0') then --调节小时if(SEG_BUF7=9) thenSEG_BUF7<="0000";SEG_BUF8<=SEG_BUF8+1;elsif(SEG_BUF8>=2 and SEG_BUF7>=3) thenSEG_BUF7<="0000";SEG_BUF8<="0000";elseSEG_BUF7<=SEG_BUF7+1;end if;elsif(SET1='0' and SET2='1') then --调节分钟if(SEG_BUF4=9) thenSEG_BUF4<="0000";if(SEG_BUF5=5) thenSEG_BUF5<="0000";elseSEG_BUF5<=SEG_BUF5+1;end if;elseSEG_BUF4<=SEG_BUF4+1;end if;elsif(SET1='0' and SET2='0') then --正常计数SEG_BUF1<=SEG_BUF1;SEG_BUF2<=SEG_BUF2;SEG_BUF4<=SEG_BUF4;SEG_BUF5<=SEG_BUF5;SEG_BUF7<=SEG_BUF7;SEG_BUF8<=SEG_BUF8;if(SEG_BUF1=9) thenSEG_BUF1<="0000";if(SEG_BUF2=5) thenSEG_BUF2<="0000";if(SEG_BUF4=9) thenSEG_BUF4<="0000";if(SEG_BUF5=5) thenSEG_BUF5<="0000";if(SEG_BUF7=9) thenSEG_BUF7<="0000";SEG_BUF8<=SEG_BUF8+1;elsif(SEG_BUF8>=2 and SEG_BUF7>=3) thenSEG_BUF7<="0000";SEG_BUF8<="0000";elseSEG_BUF7<=SEG_BUF7+1;end if;elseSEG_BUF5<=SEG_BUF5+1;end if;elseSEG_BUF4<=SEG_BUF4+1;end if;elseSEG_BUF2<=SEG_BUF2+1;end if;elseSEG_BUF1<=SEG_BUF1+1;end if;end if;end if;end process;end ADO;引脚绑定:ClK3 PIN_25CLK5 PIN_89SET1 PIN_32SET2 PIN_33SEG_DA[7] PIN_128SEG_DA[6] PIN_142SEG_DA[5] PIN_141SEG_DA[4] PIN_138SEG_DA[3] PIN_137SEG_DA[2] PIN_136SEG_DA[1] PIN_135SEG_DA[0] PIN_133SEG_SEL[2] PIN_127SEG_SEL[1] PIN_126SEG_SEL[0] PIN_125仿真图:。

VHDL数字时钟设计

VHDL数字时钟设计序⾔这个是我在做FPGA界的HelloWorld——数字钟设计时随⼿写下的,再现了数字钟设计的过程⽬标分析1. 时钟具有时分秒的显⽰,需6个数码管。

为了减⼩功耗采⽤扫描法显⽰2. 按键设置时间,需要对按键进⾏消抖3. 时分秒即为2个60进制计数器,⼀个24进制计数器。

模块设计综上所述,我采⽤模块化设计⽅法进⾏设计,绘制框图如下。

1. 时钟分频产⽣各个模块所需频率时钟。

2. 按键处理模块对按键信号进⾏消抖、变长脉冲为短脉冲等处理。

3. 时间控制模块产⽣时间信号或对时间进⾏设置。

4. 数码管驱动模块负责对时间信号BCD码译码为数码管的段码并且扫描输出到数码管。

下⾯对各个模块分别详细叙述时钟分频模块我打算把时钟分频模块做成“数控N分频器”,通过给分频器传⼊数值N来对时钟信号进⾏N分频。

得到的信号频率为原时钟信号的频率/N,占空⽐为1/N。

稍微考虑下其他模块所需时钟:按键处理模块100Hz ,时间控制模块1Hz,数码管驱动50Hz。

⽽输⼊时钟为33.8688MHz。

我不想传⼊的N数值过⼤,我打算先对时钟进⾏两次:第⼀次调⽤时钟分频模块得到1Mhz,第⼆次得到1Khz。

这样N的位数为10可以满⾜需求。

代码如下library IEEE;use IEEE.STD_LOGIC_1164.all;use IEEE.STD_LOGIC_UNSIGNED.all;entity ClkDiv isport(clk_i:IN STD_LOGIC;N_i: IN STD_LOGIC_VECTOR(9 DOWNTO 0);clk_o:OUT STD_LOGIC);end ClkDiv;architecture behavior of ClkDiv issignal count:STD_LOGIC_VECTOR(9 DOWNTO 0):="0000000001";signal clk_temp:STD_LOGIC:='0';beginprocess(clk_i)beginif(clk_i'EVENT and clk_i='1')thenif (count=N_i)thencount<="0000000001";clk_temp<='1';elsecount<=count+1;clk_temp<='0';end if;end if;end process;clk_o<=clk_temp;end behavior;仿真结果如下:2分频:输出信号为f/2Hz,占空⽐1:23分频:输出信号为f/3Hz,占空⽐1:3按键处理模块去抖动根据以往的经验,按键按下弹起电平会有⼀⼩段⽑刺,可能会引起电路误操作,所以要对按键进⾏消抖处理使变为⼲净的矩形信号。

VHDL数字钟设计

VHDL数字钟设计报告一、系统功能概述:1.进行一个具有‘时’、‘分’、‘秒’的十进制数计时功能,‘时’、‘分’、‘秒’各用两个数码管分别显示(小时从00~23,分、秒从00~59);2.可以进行手动校时,校分,校时完毕之后从校正点开始从新计时;3.具有定时功能,可以预设闹钟,并在预定的时间发出闹铃声;4.具有整点报时功能,即从59分50秒起,每隔2秒钟发出一次低音“嘟”的信号,连续5次,最后一次发出高音“嘀”的信号,此信号结束即达到整点。

二、系统组成以及系统各部分的设计:1..⑴系统结构描述:输入输出端口设置port(reset: in std_logic; ----上升沿有效,用于改变工作状态sign: in std_logic;---高电平有效,用来控制校时,定时功能;clk: in std_logic;----计时脉冲;clk2: in std_logic;-----闹铃脉冲;hourmusic1: out std_logic;hourmusic2: out std_logic;music: out std_logic;------闹铃端口;q5: out std_logic_vector(3 downto 0);-------小时高位出口;q4: out std_logic_vector(3 downto 0);-------小时低位出口;q3: out std_logic_vector(3 downto 0);-------分钟高位出口;q2: out std_logic_vector(3 downto 0);-------分钟低位出口;q1: out std_logic_vector(3 downto 0);-------秒钟高位出口;q0: out std_logic_vector(3 downto 0) ---------秒钟低位出口;);end clock;中间变量设置signal qq5,qq4,qq3,qq2,qq1,qq0: std_logic_vector(3 downto 0);——用于计时,校时时‘时’、‘分’、‘秒’的对应中间变量;signal qqhh,qqhl,qqmh,qqml: std_logic_vector(3 downto 0);——用于定时时‘时’、‘分’、‘秒’的对应中间变量;signal qqq5,qqq4,qqq3,qqq2,qqq1,qqq0: std_logic_vector(3 downto 0);——用于显示时‘时’、‘分’、‘秒’的对应中间变量;signal flag: std_logic_vector(2 downto 0);——用来标记计时,定时,校时的状态;signal musica: std_logic;——闹铃的中间变量;signal hourmusic11,hourmusic22: std_logic;——整点报时的中间变量;signal k: std_logic;——用来控制整点报时;①计时电路:process(reset)-------------通过reset上升沿触发调整工作状态;beginif (reset'event and reset='1') thenif flag="100" then-----------若flag等于4,则清零,否则加1;flag<="000";elseflag<=flag+1;end if;end if;end process;process(clk,flag,sign)-------------用于计时,校时,定时;beginif (clk'event and clk='1') thenk<=not k; -----------产生二分频,用来控制后面整点报时;if flag="000" then ------计时环节if qq0="1001" thenqq0<="0000";if qq1="0101" thenqq1<="0000";if qq2="1001" thenqq2<="0000";if qq3="0101" thenqq3<="0000";if qq4="1001" thenqq4<="0000";qq5<=qq5+1;elsif qq5="0010"and qq4="0011" thenqq4<="0000";qq5<="0000";elseqq4<=qq4+1;end if;elseqq3<=qq3+1;end if;elseqq2<=qq2+1;end if;elseqq1<=qq1+1;end if;elseqq0<=qq0+1;end if;②校时电路:elsif (flag="001" and sign='1')then ------校时if qq4="1001" thenqq4<="0000";qq5<=qq5+1;elsif qq5="0010"and qq4="0011" thenqq4<="0000";qq5<="0000";elseqq4<=qq4+1;end if;elsif (flag="010" and sign='1') then -------校分qq1<="0000";qq0<="0000";if qq2="1001" thenqq2<="0000";if qq3="0101" thenqq3<="0000";elseqq3<=qq3+1;end if;elseqq2<=qq2+1;end if;③定时电路:elsif (flag="011" and sign='1') then -----定时if qqhl="1001" thenqqhl<="0000";qqhh<=qqhh+1;elsif qqhh="0010"and qqhl="0011" thenqqhh<="0000";qqhl<="0000";elseqqhl<=qqhl+1;end if;elsif (flag="100" and sign='1')then -----定分if qqml="1001" thenqqml<="0000";if qqmh="0101" thenqqmh<="0000";elseqqmh<=qqmh+1;end if;elseqqml<=qqml+1;end if;end if;end if;end process;④显示:process(flag)beginif flag="000" then ----计时状态,显示计时qqq0<=qq0;qqq1<=qq1;qqq2<=qq2;qqq3<=qq3;qqq4<=qq4;qqq5<=qq5;elsif flag="001" then----校时状态,显示校时qqq5<=qq5;qqq4<=qq4;qqq3<=qq3;qqq2<=qq2;qqq1<="0000";qqq0<="0001";elsif flag="010" then-----校分状态,显示校分qqq5<=qq5;qqq4<=qq4;qqq3<=qq3;qqq2<=qq2;qqq1<="0000";qqq0<="0010";elsif flag="011" then-----定时状态,显示定时qqq5<=qqhh;qqq4<=qqhl;qqq3<=qqmh;qqq2<=qqml;qqq1<="0000";qqq0<="0011";elsif flag="100" then-----定分状态,显示定分qqq5<=qqhh;qqq4<=qqhl;qqq3<=qqmh;qqq2<=qqml;qqq1<="0000";qqq0<="0100";end if;end process;⑤报时:process(flag)beginif flag="000" thenif qq5=qqhh and qq4=qqhl and qq3=qqmh and qq2=qqml then if qq1="0000" thenmusica<=clk2;end if;end if;end if;end process;process(k) ---整点报时环节,当59分50秒时,每过两秒报时响一下,beginif (qq3="0101" and qq2="1001" and qq1="0101") and (qq0="1000" or qq0="1001") thenhourmusic22<=k;elsif (qq3="0101"and qq2="1001" and qq1="0101") thenhourmusic11<=k;end if;(2)各进程功能总结:①process(reset):手动上升沿触发,每来一次脉冲,状态变量flang加1,改变一种状态,当flang等于4时,flang清零,从新改变状态;②process(clk,flag,sign):clk上升沿触发,当flang为“000”,完成正常计时;当flang为“001”且校正开关sign为高电平,完成校时功能;当flang为“010”且校正开关sign为高电平,完成校分功能;当flang为“011”且校正开关sign为高电平,完成定时功能;当flang为“100”且校正开关sign为高电平,完成定分功能;③process(flag)1:完成显示功能:当flang为“000”时,显示正常计时的变量;当flang为“001”或“010”时(校时);显示校时校分变量;当flang为“011”或“100”时(定时),显示定时定分变量;④process(flag)2:完成闹铃功能:当flang为“000”(正常计时状态)时,若计时和定时相等,则将clk2(引入的一个高频信号)给闹铃引脚(music,接speaker),闹铃响;⑤process(k):k为clk进程中的一个二分频变量,完成整点报时功能:当计时为59分50秒时,hourmusic11赋值为k,即每隔两秒出现一次高电平,一共四次;当计时为59分58秒时,hourmusic22赋值为k,即每隔两秒出现一次高电平,一共一次;2. 下载时选择的开发系统模式以及管脚此系统下载时使用模式7进行下载:3.实验电路结构图:结构图NO.7:此电路适合于设计时钟、定时器、秒表等。

VHDL编程--数字钟

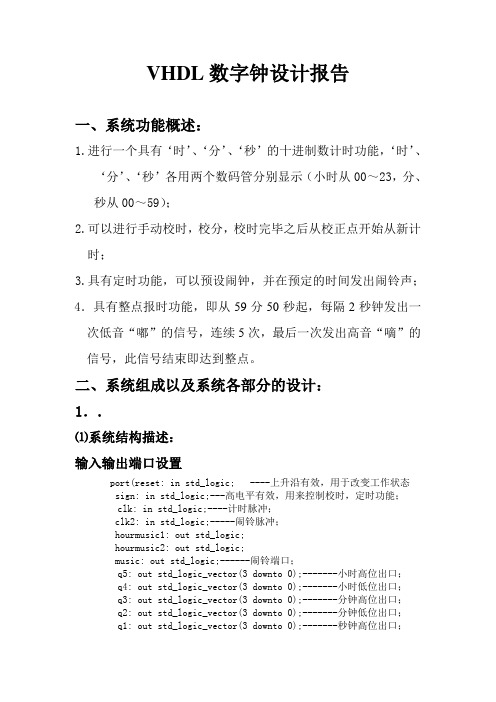

一、数字钟要求:1、能进行正常的时、分、秒计时功能,分别由6个数码管显示24h、60min、60s。

2、可以进行当前时间设置。

二、应用系统功能的详细说明该数字钟使用的是二十四时计时制。

计时时间范围从00:00:00到23:59:59。

当时间及时到23:59:59时,钟面跳转到00:00:00重新下一轮计时。

该数字钟总共有三个按钮,分别是md1控制数字钟的开关,md2(1)控制数字钟的正常运行还是时间设置和md2(0)控制对时还是对分的设置。

md1:为0时,数字钟电源关闭;为1时,数字钟电源开启。

md2(1):为0时,数字钟正常运行;为1时,数字钟进入设置状态。

md2(0):为0时,数字钟对时进行设置;为1时,数字钟对分进行设置。

三、主要模块的算法描述1、扫描显示模块scan6由于试验箱上的8只显示数码管只有16个接脚,当显示四个以上时,每次只能显示一位,所以要显示六位要轮流输出,即扫描显示。

人的视觉暂留大约为1/30s,所以每只数码管闪动频率为32Hz即可。

那么8只数码管轮流显示一遍,2、计时模块hourten,huoroen,minten,minone,secten,secone计时模块共分为6个部分,分别是时、分、秒的十位和个位。

由每位之间的逻辑关系以及md1和md2来控制正常计数、进位和对小时分钟的设置。

3、译码模块dec7s把计时模块输出的时、分、秒各位的二进制数翻译成能在七段数码管上显示的七位二进制码,能够显示0~9各个数字。

四、程序的源代码清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity digital_clock isport(clk:in std_logic; --扫描频率,>=256Hz clk1:in std_logic; --计时频率,1Hzmd1:in std_logic; --开关,0时有效md2:in std_logic_vector(1 downto 0); --时间设置dout:out std_logic_vector(6 downto 0); --译码显示ms:out std_logic_vector(5 downto 0)); --扫描控制end digital_clock;architecture one of digital_clock issignal sel:std_logic_vector(2 downto 0);signal hou1,hou2,min1,min2,sec1,sec2:std_logic_vector(3 downto 0);signal time:std_logic_vector(3 downto 0);begin---------------------------------------------scan6scan6:process(clk1,hou1,hou2,min1,min2,sec1,sec2)beginif clk1'event and clk1='1' thenif sel="101" thensel<="000";elsesel<=sel+1;end if;end if;case sel iswhen "000"=>ms<="000001";time<=hou1;when "001"=>ms<="000010";time<=hou2;when "010"=>ms<="000100";time<=min1;when "011"=>ms<="001000";time<=min2;when "100"=>ms<="010000";time<=sec1;when "101"=>ms<="100000";time<=sec2;when others=>ms<="100000";time1=sec2;end case;end process scan6;---------------------------------------------hourtenhourten:process(clk,hou2,min1,min2,sec1,sec2,md1,md2)beginif clk'event and clk='1' thenif (hou1&hou2&min1&min2&sec1&sec2="001000110101100101011001") then hou1<="0000"; --当23:59:59时,时十位归0elsif (hou1&hou2="00100011"and md1&md2="001") thenhou1<="0000"; --当设置小时,时位是23时,时十位归0elsif ((hou2&min1&min2&sec1&sec2="10010101100101011001")or(hou2="1001"and md1&md2="001")) thenhou1<=hou1+1; --当正常计时,时间是x9:59:59时,或设置小时,end if; --时位是x9时,时十位加1end if;end process hourten;---------------------------------------------houronehourone:process(clk,min1,min2,sec1,sec2,md1,md2,hou1)beginif clk'event and clk='1' thenif (hou1&hou2&min1&min2&sec1&sec2="001000110101100101011001") then hou2<="0000"; --当23:59:59时,时个位归0elsif (hou2&min1&min2&sec1&sec2="001000110101100101011001") thenhou2<="0000"; --当x9:59:59时,时个位归0elsif ((hou2="1001"or hou1&hou2="00100011")and(md1&md2="001")) thenhou2<="0000"; --当设置小时,时位是x9或23时,时个位归0 elsif (min1&min2&sec1&sec2="0101100101011001)or(md1&md2="001")then hou2<=hou2+1; --当正常计时,时间是xx:59:59时,或设置小时,时个位加1 end if;end if;end process hourone;---------------------------------------------mintenminten:process(clk,min2,sec1,sec2,md1,md2)beginif clk'event and clk='1' thenif (min1&min2&sec1&sec2="0101100101011001") thenmin1<="0000"; --当xx:59:59时,分十位归0elsif (min1&min2="01011001"and md1&md2="000")thenmin1<="0000"; --当设置分钟,分位是59时,分十位归0elsif (min2&sec1&sec2="100101011001")or --正常计时,时间是xx:x9:59时,或(min2="1001"and md1&md2="000") then --设置分钟,时间是x9,分十位加1min1<=min1+1;end if;end if;end process minten;---------------------------------------------minoneminone:process(clk,sec1,sec2,md1,md2)beginif clk'event and clk='1' thenif (min2&sec1&sec2="100101011001") thenmin2<="0000"; --当xx:x9:59时,分个位归0elsif (min2="1001"and md1&md2="000") thenmin2<="0000"; --当设置分钟,分位是x9时分个位归0elsif (sec1&sec2="01011001")or(md1&md2="000") thenmin2<=min2+1; --正常计时,时间是xx:xx:59时,或设置分钟,分个位加1 end if;end if;end process minone;---------------------------------------------sectensecten:process(clk)beginif clk'event and clk='1' thenif (sec1&sec2="01011001") then --当时间是xx:xx:59时,秒十位归0sec1<="0000";elsif sec2="1001"then --当秒位是x9时,秒十位加1sec1<=sec1+1;end if;end if;end process secten;--------------------------------------------seconesecone:process(clk)beginif clk'event and clk='1' thenif sec2="1001" then --当秒位是x9时,秒个位归0sec2<="0000";else sec2<=sec2+1; --否则加1end if;end if;end process secone;------------------------------------------dec7sdec7s:process(time)begincase time iswhen "0000"=>dout<="0111111";when "0001"=>dout<="0000110";when "0010"=>dout<="1011011";when "0011"=>dout<="1001111";when "0100"=>dout<="1100110";when "0101"=>dout<="1101101";when "0110"=>dout<="1111101";when "0111"=>dout<="0000111";when "1000"=>dout<="1111111";when "1001"=>dout<="1101111";when others=>dout<="0111111";end case;end process dec7s;end one;。

基于VHDL语言的数字钟设计

信息与通信工程学院数字电路与逻辑设计实验题目:基于VHDL语言的数字钟设计班级:姓名:学号:日期:指导教师:一.摘要数字钟是一个将“时”、“分”、“秒”显示于人的视觉器官的计时装置。

它的基本功能是计时,计时周期为24小时,显示满刻度23时59分59秒;或者计时周期为12小时并配有上下午指示,显示满刻度为11时59分59秒,通过六个七段数码管显示出来。

本实验主要在理论分析和具体的软硬件实现上,基于VHDL语言编写源代码,使用软件Quartus II 进行处理,再配合具体电路连接,实现一个多功能的数字钟。

关键词:数字钟;VHDL语言;七段数码管二.设计任务要求设计实现一个数字钟。

1.24小时制,显示刻度从0:0:0到23:59:59 。

2.12小时制,显示刻度从0:0:0到11:59:59 。

3.12/24小时制可切换,12小时制下上下午有不同显示(上午发光二极管不亮,下午发光二极管亮)。

4.可手动校对时间,能对时和分进行校正。

5.整点报时功能。

6.闹铃功能,可设置闹铃时间,当计时到预定时间时,蜂鸣器发出闹铃信号,闹铃时间为5秒,可提前终止闹铃。

7.可认为设置时间为倒计时模式8.可切到屏保模式,六个数码管显示为“supper”字样。

三.设计思路和总体设计框图1.设计思路程序设计主要分为四个模块,第一部分,做分频器,分出一秒的时钟用来计数,再分出一个中频时钟用来扫描显示数码管,我选择的频率是50kHZ;第二部分,做计数器,秒随时钟沿计数进1,分钟随着秒计数60次进一,而小时,由于有12/24小时制的切换,时的计数有两个信号来进行,一个信号hour1是分60进一在0到23循环计数,另一个信号hour2是分60进一在0到11循环计数;第三部分,做扫描显示六个七段数码管,通过选通信号6矢量cat来依次使六个数码管亮,数码管每两位对应相应的时分秒;第四部分,其他输入输出单元,比如数字钟的时间修正,闹铃等,这些都是基于前三个部分,做起来难度不大。

利用VHDL语言设计的数字钟

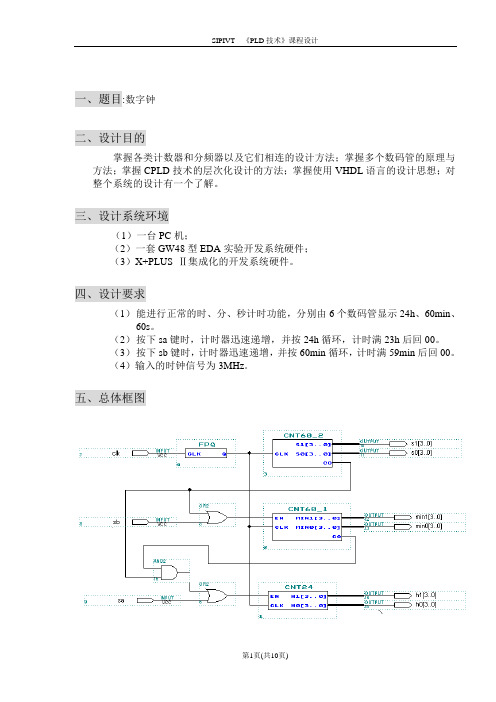

一、题目:数字钟二、设计目的掌握各类计数器和分频器以及它们相连的设计方法;掌握多个数码管的原理与方法;掌握CPLD技术的层次化设计的方法;掌握使用VHDL语言的设计思想;对整个系统的设计有一个了解。

三、设计系统环境(1)一台PC机;(2)一套GW48型EDA实验开发系统硬件;(3)X+PLUS Ⅱ集成化的开发系统硬件。

四、设计要求(1)能进行正常的时、分、秒计时功能,分别由6个数码管显示24h、60min、60s。

(2)按下sa键时,计时器迅速递增,并按24h循环,计时满23h后回00。

(3)按下sb键时,计时器迅速递增,并按60min循环,计时满59min后回00。

(4)输入的时钟信号为3MHz。

五、总体框图六、模块及模块功能(1)模块CNT60_2 该模块为60进制计数器,计时输出为秒的数值,在计时到59时送出进位信号CO,因为硬件有延时,所以模块CNT60_2在此模块变为00时加1,符合实际。

A、模块B、程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt60_2 isport(clk:in std_logic;s1,s0:out std_logic_vector(3 downto 0);co:out std_logic);end cnt60_2;architecture behav of cnt60_2 isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0);beginif clk'event and clk='1' thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0:="1001";elsif cnt0<"1001" thencnt0:=cnt0+1;else cnt0:="0000";if cnt1<"0101" thencnt1:=cnt1+1;else cnt1:="0000";co<='0';end if;end if;end if;s1<=cnt1;s0<=cnt0;end process;end behav;C、流程图D、波形仿真(2)模块CNT60_1 该模块为60进制计数器,计时输出为分的数值,在EN信号有效且时钟到来时,计数器加1。

用VHDL语言编写的数字钟程序

永州职业技术学院课程设计课程名称:EDA技术实用教程题目:基于FPGA的数字钟设计系、专业:电子技术系应用电子年级、班级:07级电子大专学生姓名:**指导老师:***时间:2008年12月目录一、系统设计………………………………………………………..1.1设计要求……………………………………………………1.1.1任务………………………………………………..1.1.2要求……………………………………………….1.1.3题目分析…………………………………………二.方案论证与比较…………………………………2.1方案一…………………………………………2.2 方案二…………………………………………2.3 方案三…………………………………………三、设计思路……………………………………………………3.1硬件模块………………………………………………3.2软件模块………………………………………………….四、调试情况………………………………………………….五、系统调试…………………………………………………六、心得体会……………………………………………………... 附:参考文献……………………………………………………..用VHDL语言编写的数字钟程序摘要:本设计要求一个12进制或24进制的具有时、分、秒计时功能的数字钟,并要求能进行时、分、秒调整,每逢时有报时功能。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

本设计基于FPGA芯片的数字钟的设计,通过多功能数字钟的设计思路,详细叙述了整个系统的硬件、软件实现过程,实现了时间的显示和修改功能、报时功能等,并尽可能的减少误差,使得系统可以达到实际数字钟的允许误差范围内。

关键词:FBGA、数码管、按键一、系统设计1.1 设计要求1.1.1 任务设计并制作一个数字钟,通过设计,掌握电子设计的一般思路,学习电子设计的一般方法。

基于VHDL的数字时钟设计

目录1 概述...................................................................... 错误!未定义书签。

1.1数字时钟的工作原理 (1)1.2设计任务 (1)2 系统总体方案设计 (2)3 VHDL模块电路设计 (3)3.1模块实现 (3)3.1.1分频模块pinlv (3)3.1.2按键去抖动模块qudou (5)3.1.3按键控制模块self1 (6)3.1.4秒、分六十进制模块cantsixty (7)3.1.5时计数模块hourtwenty (9)3.1.6秒、分、时组合后的模块 (9)3.1.7数码管显示模块 (10)3.2数字时钟的顶层设计原理图 (13)3.3系统仿真与调试 (14)结束语 (16)参考文献 (17)致谢 (18)附录源程序代码 (19)1 概述1.1数字时钟的工作原理数字钟电路的基本结构由两个60进制计数器和一个24进制计数器组成,分别对秒、分、小时进行计时,当计时到23时59分59秒时,再来一个计数脉冲,则计数器清零,重新开始计时。

秒计数器的计数时钟CLK为1Hz的标准信号,可以由晶振产生的50MHz信号通过分频得到。

当数字钟处于计时状态时,秒计数器的进位输出信号作为分钟计数器的计数信号,分钟计数器的进位输出信号又作为小时计数器的计数信号,每一秒钟发出一个中断给CPU,CPU采用NIOS,它响应中断,并读出小时、分、秒等信息。

CPU对读出的数据译码,使之动态显示在数码管上。

1.2 设计任务设计一个基于VHDL的数字时钟,具体功能要求如下:1.在七段数码管上具有时--分--秒的依次显示。

2.时、分、秒的个位记满十向高位进一,分、秒的十位记满五向高位进一,小时按24进制计数,分、秒按60进制计数。

3.整点报时,当计数到整点时扬声器发出响声。

4.时间设置:可以通过按键手动调节秒和分的数值。

此功能中可通过按键实现整体清零和暂停的功能。

(完整word版)24小时数字钟VHDL语言

数字钟的设计」、任务要求:(1) 设计一个数字钟。

(2) 具有时,分,秒计数显示功能,以24小时循环计时(3) 具有清零,调节小时、分钟功能。

(4) 具有整点报时功能,整LED灯花样显示。

1、系统框图:T荃点捱吋盘花畔亦,*5fS*.三、模块说明(含程序代码)1.秒模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_ un sig ned.all;en tity SECOND isport(clk,clr:in std_logic;----时钟/清零信号sec1,sec0:out std」ogic_vector(3 downto 0);----秒高位/低位co:out std」ogic); 输出/进位信号end SECOND;architecture SEC of SECOND isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0);--- 计数beginif clr='1' then----当ckr为1时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'eve nt and clk='1' the nif ent仁"0101" and cnt0="1000" then----当记数为58(实际是经过59个记时脉冲) co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9 时cnt0:=cnt0+1;----计数elsecntO:="OOOO";if cnt1<"0101" then----高位小于 5 时 cnt1:=cnt1+1; elsecnt1:="0000"; co<='0'; end if; end if; end if; sec1<=c ntl; sec0<=c ntO; end process; end SEC;秒模块仿真波形mwmnnmuuuumjumnmnnnnnmmjuuuuumnR秒模块原理图Ei i 1Jsecip. 0J «oD[3.4]coi insti. . 1 B 1. .iVW 召当clr=1时,秒的高低位清零;当 clr=0时,来一个时钟信号 sec0加1,当sec0加到九时清零,co=1, secl 加1。

vhdl实验报告--数字钟

VHDL实验报告一、实验目的1、设计一个24小时制数字钟,要求能显示时,分,秒,并且可以手动调整时和分。

2、通过复杂实验,进一步加深对VHDL语言的掌握程度。

二、实验原理数字钟的主体是计数器,它记录并显示接收到的秒脉冲个数,其中秒和分为模60计数器,小时是模24计数器,分别产生3位BCD码。

BCD码经译码,驱动后接数码管显示电路。

秒模60计数器的进位作为分模60计数器的时钟,分模60计数器的进位作为模24计数器的时钟。

为了实现手动调整时间,在外部增加了setm(调整分),seth(调整时)按键,当这两个按键为低电平时,电路正常计时,当为高电平时,分别调整分,时。

同时在外部还增加了一个清零按键clr.和消抖动电路。

三、实验步骤1、单元模块设计部分1)消抖动电路关键部分signal key_in1,key_in2:std_logic:='0';beginprocess(clk,key_in)beginif clk'event and clk='1' thenkey_in1<=key_in;key_in2<=key_in1;if key_in='1' and key_in1='1' and key_in2='1' then key_out<='1';else key_out<='0';end if;2) 模60计数器程序关键部分:signal md_temp,mg_temp:std_logic_vector(3 downto 0);beginprocess(clk,clr)beginif clr='1' thenmd_temp<="0000"; mg_temp<="0000";elsif set='1' thenmd_temp<=setl; mg_temp<=seth;elsif clk'event and clk='1' thenif md_temp="1001" thenmd_temp<="0000";mg_temp<=mg_temp+'1';else md_temp<=md_temp+'1';if md_temp="1001" and mg_temp="0101" thenmd_temp<="0000";mg_temp<="0000";2、模24计数器程序关键部分signal hd_temp,hg_temp:std_logic_vector(3 downto 0);beginprocess(clk,clr,set,setl,seth)isbeginif set='1' then hd_temp<=setl; hg_temp<=seth;elsif clr='1' then hd_temp<="0000"; hg_temp<="0000";elsif clk'event and clk='1' thenif hg_temp="0010" and hd_temp="0011" thenhd_temp<="0000"; hg_temp<="0000";elsif hd_temp="1001" thenhg_temp<=hg_temp+'1' hd_temp<="0000";else hd_temp<=hd_temp+'1';end if;end if;end process ;3、清零和调时部分显示部分关键程序process (sd,sg,md,mg,hd,hg)begincase sd iswhen "0000" =>sl<="1111110";when "0001" =>sl<="0110000";when "0010" =>sl<="1101101";when "0011" =>sl<="1111001";when "0100" =>sl<="0110011";when "0101" =>sl<="1011011";when "0110" =>sl<="1011111";when "0111" =>sl<="1110000";when "1000" =>sl<="1111111";when "1001" =>sl<="1111011";when others =>sl<="0000000";end case;if clk_g'event and clk_g='1' thenif sel="101" thensel<="000";else sel<=sel+'1';end if;end if;process(sel,sd,sl,sg,sh,md,ml,mg,mh,hd,hl,hg,hh)begincase sel iswhen"000"=>led<=sl;led_which<=sd;when"001"=>led<=sh;led_which<=sg;when"010"=>led<=ml;led_which<=md;when"011"=>led<=mh;led_which<=mg;when"100"=>led<=hl;led_which<=hd;when"101"=>led<=hh;led_which<=hg;when others=>led<="0000000";led_which<="0000";end case;4、顶层文件关键程序port(clk,clk_g:in std_logic;-----clk_g是用在数码管显示里面的信号clr: in std_logic;------clr=1时清零setm,seth:in std_logic;---------setm为1时调分,seth为1时调时setd,setg:in std_logic_vector(3 downto 0);----调整时间的时候,setd调整的是低位setg 调整高位led:out std_logic_vector(6 downto 0);sel_out: out std_logic_vector(2 downto 0);led_which: out std_logic_vector(3 downto 0));---输出的是秒分时的哪一个beginu1:de_shake port map (clk=>clk,key_in=>clr,key_out=>clro);u2:de_shake port map (clk=>clk,key_in=>setm,key_out=>setmo);u3:de_shake port map (clk=>clk,key_in=>seth,key_out=>setho);u4:s60 port map (clk=>clk,clr=>clro,sd=>sdl,sg=>sgh,fenmaichong=>fenmaichong o);u5:m60 port map (clk=>fenmaichongo,clr=>clro,md=>mdl,mg=>mgh,xiaoshimaichong=> xiaoshimaichongo,setl=>setd,seth=>setg,set=>setmo);u6:h24 port map (clk=>xiaoshimaichongo,clr=>clro,hd=>hdl,hg=>hgh,set=>setho,se tl=>setd,seth=>setg);u7:led_xs port map (clk_g=>clk_g,sd=>sdl,sg=>sgh,md=>mdl,mg=>mgh,hd=>hdl, hg=>hgh,led=>led,sel_out=>sel_out,led_which=>led_which);四、实验结果及分析本设计,满足了本次试验设计的任务要求,能显示时分秒,并且可以手动调节分和时。

数字钟VHDL

VHDL实验报告:数字钟一:数字钟的功能1:具有以二十四小时计时、显示、整点报时、时间设置和闹钟的功能。

设计精度要求为1S。

二.功能描述1 . 系统输入:系统状态及校时、定时转换的控制信号为k、trans、set;时钟信号clk,采用1024Hz;系统复位信号reset。

输入信号均由按键产生。

系统输出:LED显示输出,蜂鸣器声音信号输出。

2. 计时:正常工作状态下,每日按24h计时制计时并显示,蜂鸣器无声,逢整点报时。

3. 校时:在计时状态显示下,按下“set键”,进入“小时”校准状态,之后按下“k键”则进入“分”校准状态,继续按下“k 键”则进入“秒复零”状态,第三次按下“k 键”又恢复到正常计时显示状态。

A:“小时”校准状态:在“小时”校准状态下,显示“小时”数码管以1Hz的频率递增计数。

B:“分”校准状态:在“分”校准状态下,显示“分”的数码管以1Hz的频率递增计数。

C:“秒”复零状态:在“秒复零”状态下,显示“秒”的数码管复零。

4. 整点报时:蜂鸣器在“59”分钟的第“51”、“53”、“55”、“57‘秒发频率为512Hz的低音,在“59”分钟的第“59”秒发频率为1024Hz的高音,结束时为整点。

5. 显示:要求采用扫描显示方式驱动6个LED数码管显示小时、分、秒。

闹钟:闹钟定时时间到,蜂鸣器发出周期为1s的“滴”、“滴”声,持续时间为10s;闹钟定时显示。

6. 闹钟定时设置:在闹钟定时显示状态下,按下“set键”,进入闹钟的“时”设置状态,之后按下“k键”进入闹钟的“分”设置状态,继续按下“k 键”则进入“秒”设置状态,第三次按下“k键”又恢复到闹钟定时显示状态。

A:闹钟“小时”设置状态:在闹钟“小时”设置状态下,显示“小时”的数码管以1Hz的频率递增计数。

B:闹钟:“分”设置状态:在闹钟“分”设置状态下,显示“分”的数码管以1Hz的频率递增计数。

三:仿真。

分主控模块、计时校时模块、闹钟设定模块、选择显示模块、整点报时及闹铃模块、分频模块、动态显示模块。

基于VHDL语言的二十四进制数字钟

module clock(clk,ena,tt5,tt4,tt3,tt2,tt1,tt0,speak); input clk,ena; output [7:0]tt5; output [7:0]tt4; output [7:0]tt3; output [7:0]tt2; output [7:0]tt1; output [7:0]tt0; reg [7:0]tt5; reg [7:0]tt4; reg [7:0]tt3; reg [7:0]tt2; reg [7:0]tt1; reg [7:0]tt0; reg [3:0]t5; reg [3:0]t4; reg [3:0]t3; reg [3:0]t2; reg [3:0]t1; reg [3:0]t0; output speak; wire x,xa,xb,xc,xd,xe;

闹钟在 23 点 59 分 module example6(clk,clr,ena,cout,t); input clk ,clr,ena; output [3:0] t; output cout; reg cout; reg [3:0] t; always @(posedge clr or posedge clk) begin if (clr) t='b0000; else if (ena) begin if(t<='b0100) begin t=t+1; cout=0; end else begin t=0; cout=1; end end end endmodule module example10(clk,clr,ena,cout,t); input clk ,clr,ena; output [3:0] t; output cout; reg cout; reg [3:0] t; alwaysk) begin if (clr) t='b0000; else if (ena) begin if(t<='b1000) begin t=t+1; cout=0;

VHDL数字时钟

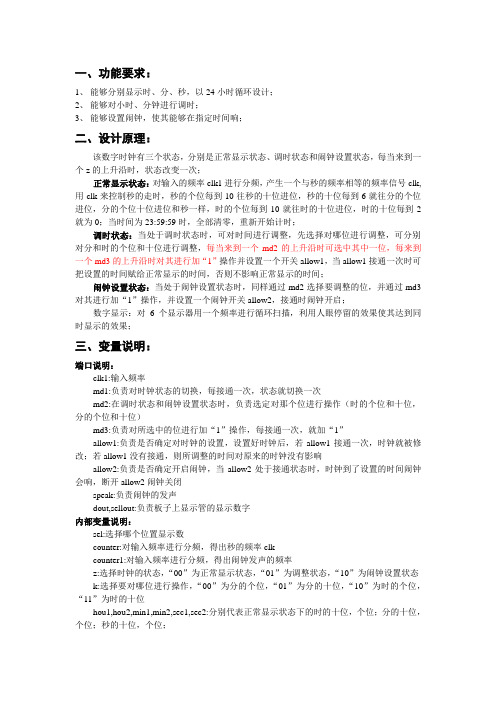

一、功能要求:1、能够分别显示时、分、秒,以24小时循环设计;2、能够对小时、分钟进行调时;3、能够设置闹钟,使其能够在指定时间响;二、设计原理:该数字时钟有三个状态,分别是正常显示状态、调时状态和闹钟设置状态,每当来到一个z的上升沿时,状态改变一次;正常显示状态:对输入的频率clk1进行分频,产生一个与秒的频率相等的频率信号clk,用clk来控制秒的走时,秒的个位每到10往秒的十位进位,秒的十位每到6就往分的个位进位,分的个位十位进位和秒一样,时的个位每到10就往时的十位进位,时的十位每到2就为0;当时间为23:59:59时,全部清零,重新开始计时;调时状态:当处于调时状态时,可对时间进行调整,先选择对哪位进行调整,可分别对分和时的个位和十位进行调整,每当来到一个md2的上升沿时可选中其中一位,每来到一个md3的上升沿时对其进行加“1”操作并设置一个开关allow1,当allow1接通一次时可把设置的时间赋给正常显示的时间,否则不影响正常显示的时间;闹钟设置状态:当处于闹钟设置状态时,同样通过md2选择要调整的位,并通过md3对其进行加“1”操作,并设置一个闹钟开关allow2,接通时闹钟开启;数字显示:对6个显示器用一个频率进行循环扫描,利用人眼停留的效果使其达到同时显示的效果;三、变量说明:端口说明:clk1:输入频率md1:负责对时钟状态的切换,每接通一次,状态就切换一次md2:在调时状态和闹钟设置状态时,负责选定对那个位进行操作(时的个位和十位,分的个位和十位)md3:负责对所选中的位进行加“1”操作,每接通一次,就加“1”allow1:负责是否确定对时钟的设置,设置好时钟后,若allow1接通一次,时钟就被修改;若allow1没有接通,则所调整的时间对原来的时钟没有影响allow2:负责是否确定开启闹钟,当allow2处于接通状态时,时钟到了设置的时间闹钟会响,断开allow2闹钟关闭speak:负责闹钟的发声dout,sellout:负责板子上显示管的显示数字内部变量说明:sel:选择哪个位置显示数counter:对输入频率进行分频,得出秒的频率clkcounter1:对输入频率进行分频,得出闹钟发声的频率z:选择时钟的状态,“00”为正常显示状态,“01”为调整状态,“10”为闹钟设置状态k:选择要对哪位进行操作,“00”为分的个位,“01”为分的十位,“10”为时的个位,“11”为时的十位hou1,hou2,min1,min2,sec1,sec2:分别代表正常显示状态下的时的十位,个位;分的十位,个位;秒的十位,个位;hou1n,hou2n,min1n,min2n,:分别代表处于调时状态时的时和分的十位和个位;seth1,seth2,setm1,setm2:分别代表处于闹钟设置状态的时和分的十位和个位;h1,h2,m1,m2,s1,s2:分别代表最终显示在板子上的时、分、秒的十位和个位;四、源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity zhong isport(clk1:in std_logic;md1:in std_logic;-----xuan ze zhuang taimd2:in std_logic;------xuan ze she zhi na ge wei zhimd3:in std_logic;------jia yiallow1:in std_logic;allow2:in std_logic;speak:out std_logic;-----nao zhongdout:out std_logic_vector(6 downto 0);-------shu chuselout:out std_logic_vector(5 downto 0));-----xuan ze xian shi end zhong;architecture one of zhong issignal sel:std_logic_vector(2 downto 0);signal hou1:std_logic_vector(3 downto 0);signal hou2:std_logic_vector(3 downto 0);signal min1:std_logic_vector(3 downto 0);signal min2:std_logic_vector(3 downto 0);signal hou1n:std_logic_vector(3 downto 0);signal hou2n:std_logic_vector(3 downto 0);signal min1n:std_logic_vector(3 downto 0);signal min2n:std_logic_vector(3 downto 0);signal seth1:std_logic_vector(3 downto 0);signal seth2:std_logic_vector(3 downto 0);signal setm1:std_logic_vector(3 downto 0);signal setm2:std_logic_vector(3 downto 0);signal sec1:std_logic_vector(3 downto 0);signal sec2:std_logic_vector(3 downto 0);signal h1:std_logic_vector(3 downto 0);signal h2:std_logic_vector(3 downto 0);signal m1:std_logic_vector(3 downto 0);signal m2:std_logic_vector(3 downto 0);signal s1:std_logic_vector(3 downto 0);signal s2:std_logic_vector(3 downto 0);signal counter:std_logic_vector(8 downto 0);-----------secondsignal countern1:std_logic_vector(7 downto 0);----------speakersignal clk:std_logic;----------secondsignal clkn1:std_logic;-----speakersignal k:std_logic_vector(1 downto 0);---------xuan ze xian shisignal z:std_logic_vector(1 downto 0);------00 zheng chang ;01 tiao zheng;10 nao ling;-------------------------------------------------beginfen:process(clk1)beginif(clk1'event and clk1='1')thenif(counter="110000000")thencounter<="000000000";clk<=not clk;elsecounter<=counter+'1';end if;if(countern1="10000000")thencountern1<="00000000";elseclkn1<=not clkn1;end if;end if;end process fen;-------------------------------------------kong:process(md2)beginif( md2'event and md2='1')thenif(k="11")thenk<="00";elsek<=k+1;end if;end if;end process kong;process(md1)beginif(md1'event and md1='1')thenif(z="10")thenz<="00";elsez<=z+1;end if;end if;end process;----------------------------------------------choice:process(clk1)beginif clk1'event and clk1='1' thenif sel="101" thensel<="000";elsesel<=sel+1;end if;end if;end process choice;-------------------------------------------zheng chang xian shi-----------------------------------------------hour1hou_1:process(clk,hou2,min1,min2,sec1,sec2)beginif clk'event and clk='1' thenif (hou1="0010" and hou2="0011" and min1="0101" and min2="1001" and sec1="0101" andsec2="1001") thenhou1<="0000";elsif (hou2="1001"and min1="0101" and min2="1001" and sec1="0101" and sec2="1001") thenhou1<=hou1+1;end if;end if;if(allow1='1' and z="01")thenhou1<=hou1n;end if;end process hou_1;-----------------------------------------------hour2hou_2:process(clk,min1,min2,sec1,sec2,hou1)beginif clk'event and clk='1' thenif (hou1="0010" and hou2="0011"and min1="0101" and min2="1001" and sec1="0101" andsec2="1001") thenhou2<="0000";elsif hou2="1001"and(min1="0101" and min2="1001" and sec1="0101" and sec2="1001") thenhou2<="0000";elsif (min1="0101" and min2="1001" and sec1="0101" and sec2="1001")thenhou2<=hou2+1;end if;end if;if(allow1='1' and z="01")thenhou2<=hou2n;end if;end process hou_2;-----------------------------------------------min1min_1:process(clk,min2,sec1,sec2)beginif clk'event and clk='1' thenif (min1="0101" and min2="1001" and sec1="0101" and sec2="1001") then min1<="0000";elsif (min2="1001"and sec1="0101" and sec2="1001") thenmin1<=min1+1;end if;end if;if(allow1='1' and z="01")thenmin1<=min1n;end if;end process min_1;----------------------------------------------min2min_2:process(clk,sec1,sec2)beginif clk'event and clk='1' thenif (min2="1001" and sec1="0101" and sec2="1001")thenmin2<="0000";elsif (sec1="0101" and sec2="1001")thenmin2<=min2+1;end if;end if;if(allow1='1' and z="01")thenmin2<=min2n;end if;end process min_2;---------------------------------------------second1sec_1:process(clk)beginif clk'event and clk='1' thenif (sec1="0101" and sec2="1001")thensec1<="0000";elsif sec2="1001"thensec1<=sec1+1;end if;end if;if(allow1='1' and z="01")thensec1<="0000";end if;end process sec_1;--------------------------------------------second2sec_2:process(clk)beginif clk'event and clk='1' thenif sec2="1001" thensec2<="0000";else sec2<=sec2+1;end if;end if;if(allow1='1' and z="01")thensec2<="0000";end if;end process sec_2;-----------------------------------------------------------------------------------shi jian tiao zheng process(md3)-----------hour1beginif(z="01")thenif(k="11")thenif(md3'event and md3='1')thenif(hou1n="0010")thenhou1n<="0000";elsehou1n<=hou1n+1;end if;end if;end if;end if;end process;process(md3)-----------hour2beginif(z="01")thenif(k="10")thenif(md3'event and md3='1')thenif(hou2n="1001")or(hou1n="0010" and hou2n="0011")then hou2n<="0000";elsehou2n<=hou2n+1;end if;end if;end if;end if;end process;process(md3)-----------min1beginif(z="01")thenif(k="01")thenif(md3'event and md3='1')thenif(min1n="0110")thenmin1n<="0000";elsemin1n<=min1n+1;end if;end if;end if;end if;end process;process(md3)------------min2beginif(z="01")thenif(k="00")thenif(md3'event and md3='1')thenif(min2n="1001")thenmin2n<="0000";elsemin2n<=min2n+1;end if;end if;end if;end if;end process;--------------------------------------------------------------------------------------she zhi nao zhong sethour1:process(md3)beginif(z="10")thenif(k="11")thenif(md3'event and md3='1')thenif(seth1="0010")thenseth1<="0000";elseseth1<=seth1+1;end if;end if;end if;end if;end process sethour1;-------------------------------------------sethour2:process(md3)beginif(z="10")thenif(k="10")thenif(md3'event and md3='1')thenif(seth2="1001")or(seth2="0010" and seth2="0100")then seth2<="0000";elseseth2<=seth2+1;end if;end if;end if;end if;end process sethour2;-------------------------------------------setmin1:process(md3)beginif(z="10")thenif(k="01")thenif(md3'event and md3='1')thenif(setm1="0110")thensetm1<="0000";elsesetm1<=setm1+1;end if;end if;end if;end if;end process setmin1;----------------------------------------------setmin2:process(md3)beginif(z="10")thenif(k="00")thenif(md3'event and md3='1')thenif(setm2="1001")thensetm2<="0000";elsesetm2<=setm2+1;end if;end if;end if;end if;end process setmin2;----------------------------------------------------------------------------------------nao zhongspeaker:process(clk1,hou1,hou2,min1,min2)beginif clk1'event and clk1='1'thenif(allow2='1')thenif seth1=hou1 and seth2=hou2 and setm1=min1 and setm2=min2 thenspeak<=clkn1;elsespeak<='0';end if;end if;end if;end process speaker;--------------------------------------------------------------------------------------disp:process(sel,md1,hou1,hou2,min1,min2,sec1,sec2,seth1,seth2,setm1,setm2) beginif sel="000" thenselout<="111110";case h1 iswhen "0000"=>dout<="1000000";--0when "0001"=>dout<="1111001";--1when "0010"=>dout<="0100100";--2when others =>dout<="1000000";--0end case;elsif sel="001" thenselout<="111101";case h2 iswhen "0000"=>dout<="1000000";--0when "0001"=>dout<="1111001";--1when "0010"=>dout<="0100100";--2when "0011"=>dout<="0110000";--3when "0100"=>dout<="0011001";--4when "0101"=>dout<="0010010";--5when "0110"=>dout<="0000010";--6when "0111"=>dout<="1111000";--7when "1000"=>dout<="0000000";--8when "1001"=>dout<="0010000";--9when others=>dout<="1000000";end case;elsif sel="010" thenselout<="111011";case m1 iswhen "0000"=>dout<="1000000";--0 when "0001"=>dout<="1111001";--1 when "0010"=>dout<="0100100";--2 when "0011"=>dout<="0110000";--3 when "0100"=>dout<="0011001";--4 when "0101"=>dout<="0010010";--5 when others=>dout<="1000000";--0 end case;elsif sel="011" thenselout<="110111";case m2 iswhen "0000"=>dout<="1000000";--0 when "0001"=>dout<="1111001";--1 when "0010"=>dout<="0100100";--2 when "0011"=>dout<="0110000";--3 when "0100"=>dout<="0011001";--4 when "0101"=>dout<="0010010";--5 when "0110"=>dout<="0000010";--6 when "0111"=>dout<="1111000";--7 when "1000"=>dout<="0000000";--8 when "1001"=>dout<="0010000";--9 when others=>dout<="1000000";--0 end case;elsif sel="100" thenselout<="101111";case s1 iswhen "0000"=>dout<="1000000";--0 when "0001"=>dout<="1111001";--1 when "0010"=>dout<="0100100";--2 when "0011"=>dout<="0110000";--3 when "0100"=>dout<="0011001";--4 when "0101"=>dout<="0010010";--5 when others=>dout<="1000000";--0 end case;elsif sel="101" thenselout<="011111";case s2 iswhen "0000"=>dout<="1000000";--0 when "0001"=>dout<="1111001";--1 when "0010"=>dout<="0100100";--2 when "0011"=>dout<="0110000";--3 when "0100"=>dout<="0011001";--4 when "0101"=>dout<="0010010";--5when "0110"=>dout<="0000010";--6when "0111"=>dout<="1111000";--7when "1000"=>dout<="0000000";--8when "1001"=>dout<="0010000";--9when others=>dout<="1000000";--0end case;end if;if z="00" then---------------zheng chang xian shih1<=hou1;h2<=hou2;m1<=min1;m2<=min2;s1<=sec1;s2<=sec2;elsif z="01"thenh1<=hou1n;h2<=hou2n;m1<=min1n;m2<=min2n;s1<="0000";s2<="0000";elsif z="10" then ----------------nao zhong xian shi h1<=seth1;h2<=seth2;m1<=setm1;m2<=setm2;s1<="0000";s2<="0000";end if;end process disp;------------------------------------------end one;11。

(2024版)vhdl数字时钟设计

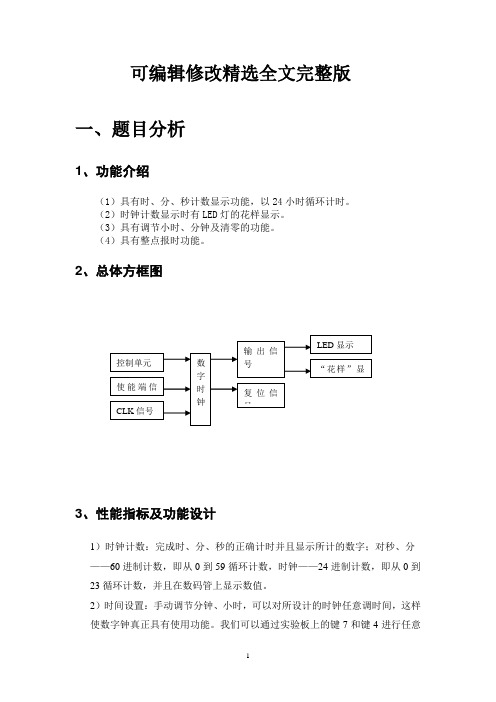

可编辑修改精选全文完整版一、题目分析1、功能介绍(1)具有时、分、秒计数显示功能,以24小时循环计时。

(2)时钟计数显示时有LED灯的花样显示。

(3)具有调节小时、分钟及清零的功能。

(4)具有整点报时功能。

2、总体方框图3、性能指标及功能设计1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。

2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。

我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以根据我们自己任意时间的复位。

4)蜂鸣器在整点时有报时信号产生,蜂鸣器报警。

产生“滴答.滴答”的报警声音。

5)LED灯在时钟显示时有花样显示信号产生。

即根据进位情况,LED不停的闪烁,从而产生“花样”信号。

二、选择方案1、方案选择方案一:根据总体方框图及各部分分配的功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分的调整以及小时的调整和一个顶层文件构成。

采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。

显示:小时采用24进制,而分钟均是采用6进制和10进制的组合。

方案二:根据总体方框图及各部分分配的功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分的调整以及小时的调整和一个顶层文件构成。

采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。

显示:小时采用24进制,而分钟和秒均60进制。

终上所述,考虑到试验时的简单性,故我选择了方案二。

三、细化框图根据自顶向下的方法以及各功能模块的的功能实现上述设计方案应系统细化框图:四、编写程序、仿真和分析1、秒计数器1)VHDL 语言描述程序见附录 2)秒计数器的仿真波形图3)波形分析利用60进制计数器完成00到59的循环计数功能,当秒计数至59时,再来一个时钟脉冲则产生进位输出,即enmin=1;reset 作为复位信号低电平有效,数字时钟控制单元 时调整 分调整使能端信号 CLK 信号时显示 分显示 秒显示24进制 60进制 60进制LED 显示整点报花样显即高电平时正常循环计数,低电平清零。

VHDL数字钟设计

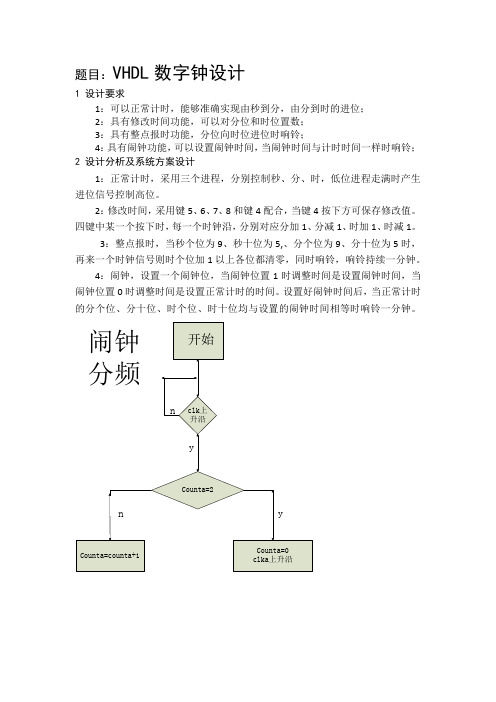

题目:VHDL数字钟设计1 设计要求1:可以正常计时,能够准确实现由秒到分,由分到时的进位;2:具有修改时间功能,可以对分位和时位置数;3:具有整点报时功能,分位向时位进位时响铃;4:具有闹钟功能,可以设置闹钟时间,当闹钟时间与计时时间一样时响铃;2 设计分析及系统方案设计1:正常计时,采用三个进程,分别控制秒、分、时,低位进程走满时产生进位信号控制高位。

2:修改时间,采用键5、6、7、8和键4配合,当键4按下方可保存修改值。

四键中某一个按下时,每一个时钟沿,分别对应分加1、分减1、时加1、时减1。

3:整点报时,当秒个位为9、秒十位为5,、分个位为9、分十位为5时,再来一个时钟信号则时个位加1以上各位都清零,同时响铃,响铃持续一分钟。

4:闹钟,设置一个闹钟位,当闹钟位置1时调整时间是设置闹钟时间,当闹钟位置0时调整时间是设置正常计时的时间。

设置好闹钟时间后,当正常计时的分个位、分十位、时个位、时十位均与设置的闹钟时间相等时响铃一分钟。

3系统以及模块硬件电路设计下载时选择的开发系统模式以及管脚定义(注:采用模式“0”)4 系统的VHDL设计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dc_1 isport( clk,alarm,close,set:in std_logic;--走时频率,闹钟频率,修改控制键,脑中设置控制键choice: in std_logic_vector(3 downto 0);--模式选择键组合speak : out std_logic; --喇叭频率来源s1,s2,m1,m2,h1,h2 :out std_logic_vector(3 downto 0));--时间输出,依次是秒个位,秒十位,分个位,分十位,时个位,时十位end;architecture a of dc_1 issignal s_1,s_2,m_1,h_1,m_2,h_2 : std_logic_vector(3 downto 0);--存正常走时的时间,不能存修改的时间signal ss1,ss2,mm1,hh1,mm2,hh2 : std_logic_vector(3 downto 0);--转存所有时间,赋值给输出signal as1,as2,am1,ah1,am2,ah2 : std_logic_vector(3 downto 0):--存放闹钟设定值signal clksp,x,y: std_logic;--整点报时低频信号,分走满的进位信号,时走满的进位信号signal n:std_logic_vector(1 downto 0); --控制分频产生clksp beginprocess(alarm)begin --get low frequency of strike on the hour if alarm'event and alarm='1' thenif n="10" thenn<="00";clksp<=not clksp;else n<=n+1;end if;end if;end process;process(clk)beginif clk'event and clk='1' then --second if(s_1="0101" and s_2="1001") thens_1<="0000";s_2<="0000";x<='1';elsif (s_2="1001") thens_2<="0000";s_1<=s_1+1;x<='0';else s_2<=s_2+1;x<='0';end if;end if;end process;process(clk) --adjust the second to match minute and hour beginif clk'event and clk='1' then ss1<=s_1;ss2<=s_2;end if;end process;process(clk)begin if close='1' then m_1<=mm1;m_2<=mm2; --minute elsif clk'event and clk='0' thenif s_2="1001" and s_1="0101" thenif m_2="1001" thenm_2<="0000";if (m_1="0101") thenm_1<="0000";y<='1';else m_1<=m_1+1;y<='0';end if;else m_2<=m_2+1;y<='0';end if;end if;end if;end process;process(clk)beginif clk'event and clk='1' then ---change minute if set='0' thenif choice="0000" thenmm1<=m_1;mm2<=m_2;elsif choice="0001" thenif (mm2="1001" and mm1="0101") thenmm2<="0000";mm1<="0000";elsif mm2="1001" thenmm2<="0000";mm1<=mm1+1;else mm2<=mm2+1;end if;elsif choice="0010" thenif (mm2="0000" and mm1="0000") thenmm2<="1001";mm1<="0101";elsif (mm2="0000") thenmm2<="1001";mm1<=mm1-1;else mm2<=mm2-1;end if;end if;end if;end if;end process;process(clk) --hour beginif close='1' then h_1<=hh1;h_2<=hh2;elsif clk'event and clk='0' thenif x='1' and y='1' thenif (h_1="0010" and h_2="0100") thenh_1<="0000" ;h_2<="0000";elsif(h_2="1001") thenh_2<="0000";h_1<=h_1+1;else h_2<=h_2+1;end if;end if;end if;end process;process(clk)beginif clk'event and clk=’1’ then --change hour if set='0' thenif choice="0000" thenhh1<=h_1;hh2<=h_2;elsif choice="0100" thenif (hh2="0100" and hh1="0010") thenhh2<="0000";hh1<="0000";elsif hh2="1001" thenhh2<="0000";hh1<=hh1+1;else hh2<=hh2+1;end if;elsif choice="1000" thenif (hh2="0000" and hh1="0000") thenhh2<="0100";hh1<="0010";elsif (hh2="0000") thenhh2<="1001";hh1<=hh1-1;else hh2<=hh2-1;end if;end if;end if;end if;end process;process(clk,set) --set alarm beginif clk'event and clk='1' thenif set='1' thenif choice="0001" then --set second if (as2="1001" and as1="0101") thenas2<="0000";as1<="0000";elsif as2="1001" thenas2<="0000";as1<=as1+1;else as2<=as2+1;end if;elsif choice="0010" then --set minif (am2="1001" and am1="0101") thenam2<="0000";am1<="0000";elsif am2="1001" thenam2<="0000";am1<=am1+1;else am2<=am2+1;end if;elsif choice="0100" then --set hour if (ah2="0100" and ah1="0010") thenah2<="0000";ah1<="0000";elsif ah2="1001" thenah2<="0000";ah1<=ah1+1;else ah2<=ah2+1;end if;end if;end if;end if;end process;process(clk)begin --display if set='1' thens1<=as1;s2<=as2;m1<=am1;m2<=am2;h1<=ah1;h2<=ah2;elses1<=s_1;s2<=s_2;m1<=mm1;m2<=mm2;h1<=hh1;h2<=hh2;end if;end process;process(clk)begin --alarm control and speaker control if set='0' thenif (mm1=am1 and mm2=am2 and hh1=ah1 and hh2=ah2) thenspeak<=alarm;elsif mm1="0101" and mm2="1001" and ss1="0101" thenif ss2="0010" or ss2="0100" or ss2="0110" or ss2="1000" thenspeak<=clksp;end if;elsif mm1="0000" and mm2="0000" and ss1="0000" and ss2="0000" thenif hh1="0000" and hh2="0000" thenspeak<='0';elsespeak<=alarm;end if;else speak<='0';end if;end if;end process;end;5 结论以及结果说明在windows系统下运行MAX+PLUSII10.2软件,编译仿真成功后,连接引脚,实验箱选择EPF10K10LC84-4。

VHDL课程设计(数字钟)

1.设计任务及要求:

设计任务:设计一台能显示时、分、秒的数字钟。具体要求如下:

(1)由实验箱上的时钟信号经分频产生秒脉冲;

(2)计时计数器用24进制计时电路;

(3)可手动校时,能分别进行时、分的校正;

(4)整点报时;

(5)选做:可设置闹时功能,当计时计到预定时间时,扬声器发出闹铃信号,闹铃时间为4s,并可提前终止闹铃。

end if;

end if;

if sethour='1' then

h0:=h0+1;

if h0="1010" then

h0:="0000";

h1:=h1+1;

ifh0="0100"and h1="0010"

then h0:="0000";h1:="0000";

end if;

end if;

end if;

3.2.3.秒计时模块

将“秒计时脉冲”clk接信号源单元的1HZ脉冲信号,此时秒显示将从00计时到59,然后回到00,重新计时。在秒位进行计时的过程中。

秒计时器是由一个60进制的计数器构成的,具有置数和计数功能。其中rst为置数信号,当rst为1时,秒计时器置数。clk为驱动秒计时器的时钟,sec1、sec0为秒计时器的高位和低位输出。

begin

if(clk1'event and clk1='1') then

if(count="10") then

count:=(others=>'0');

tmp<=not tmp;

VHDL课程设计---多功能数字钟

多功能电子时钟报告一、实验目的1.学习数字系统设计的自顶向下设计法及控制器的设计。

2.加深利用EDA技术实现数字系统的体会。

二、实验仪器及器件1.EDA 开发软件(Quartus7.2)(1套)2.电脑(1台)3.实验板(1个)三、实验要求及设计方案1.设计一个具有24进制计时、显示、整点报时、时间设置和闹钟功能的数字钟,要求时钟的最小分辨率时间为1s。

2.数字钟的设计方案如下:系统输入:mode为计时显示和闹钟定时显示转换输入;set为校时和定时设置的时、分、秒转换输入;k为校时的时、分、秒手动加1输入;4*4矩阵键盘为闹钟设置调节闹钟的时、分、秒、时钟的清零以及暂停;clk40M为板载时钟信号;reset为系统复位信号。

输入信号均由按键和4*4矩阵键盘产生。

系统输出:七段数码管显示输出;蜂鸣器(bell)声音信号输出(用LED灯代替)。

3.多功能数字钟系统功能的具体描述如下:计时:正常工作状态下,每日按24小时计时制计时并显示,蜂鸣器逢整点报时。

校时:在计时显示状态下,按下“set键”,进入“小时”校时状态,再次按下“set键”,进入“分”校时状态,继续按下“set键”,进入“秒”校时状态,第四次按下“set键”又回复到正常计时显示状态。

1)“小时”校时状态:进入“小时”校时状态后,显示“小时”的数码管闪烁,每按动“k”键一次,“小时”+1,若不按动“k”键则小时数不变,一直按下“k”键则小时数以4Hz的频率递增计数。

2)“分”校时状态:进入“分”校时状态后,显示“分”的数码管闪烁,每按动“k”键一次,“分”+1,若不按动“k”键则分数不变,一直按下“k”键则分数以4Hz的频率递增计数。

3)“秒”校时状态:进入“秒”校时状态后,显示“秒”的数码管闪烁,每按动“k”键一次,“秒”+1,若不按动“k”键则秒数不变,一直按下“k”键则秒数以4Hz的频率递增计数。

整点报时:蜂鸣器在“59”分钟的第51、53、55、57秒发出频率为512Hz的低音,在“59”秒发出频率为1024Hz的高音,结束时为整点。

用vhdl设计的数字钟

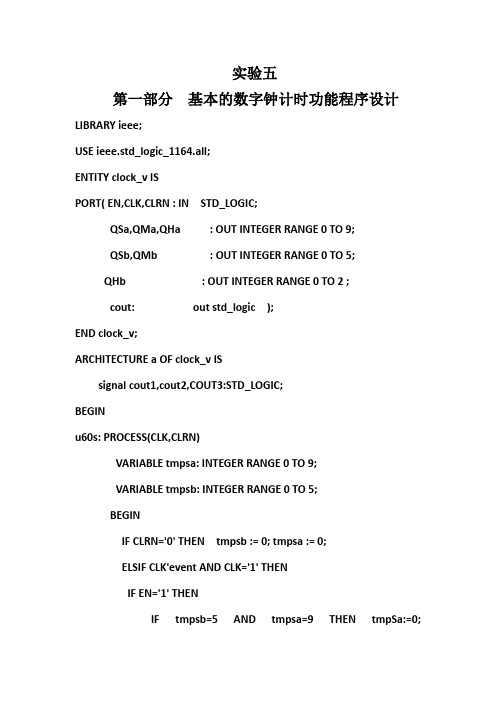

实验五第一部分基本的数字钟计时功能程序设计LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY clock_v ISPORT( EN,CLK,CLRN : IN STD_LOGIC;QSa,QMa,QHa : OUT INTEGER RANGE 0 TO 9;QSb,QMb : OUT INTEGER RANGE 0 TO 5;QHb : OUT INTEGER RANGE 0 TO 2 ;cout: out std_logic );END clock_v;ARCHITECTURE a OF clock_v ISsignal cout1,cout2,COUT3:STD_LOGIC;BEGINu60s: PROCESS(CLK,CLRN)VARIABLE tmpsa: INTEGER RANGE 0 TO 9;VARIABLE tmpsb: INTEGER RANGE 0 TO 5;BEGINIF CLRN='0' THEN tmpsb := 0; tmpsa := 0;ELSIF CLK'event AND CLK='1' THENIF EN='1' THENIF tmpsb=5 AND tmpsa=9 THEN tmpSa:=0;tmpSb:=0 ;COUT1<='1';ELSIF tmpSa=9 THEN tmpSa:=0; tmpSb:=tmpSb+1; COUT1<='0';ELSE tmpSa:=tmpSa+1;COUT1<='0';END IF;END IF;END IF ;QSA<=tmpsa;QSB<=tmpsb;END PROCESS u60s;u60M: PROCESS(cout1,CLRN)VARIABLE tmpMa: INTEGER RANGE 0 TO 9;VARIABLE tmpMb: INTEGER RANGE 0 TO 5;BEGINIF CLRN='0' THEN tmpMb := 0; tmpMa := 0;ELSIF COUT1'event AND COUT1='1' THENIF EN='1' THENIF tmpMb=5 AND tmpMa=9 THEN tmpMa:=0; tmpMb:=0 ;COUT2<='1';ELSIF tmpMa=9 THEN tmpMa:=0; tmpMb:=tmpMb+1; COUT2<='0';ELSE tmpMa:=tmpMa+1;COUT2<='0';END IF;END IF;END IF ;QMA<=tmpMa;QMB<=tmpMb;END PROCESS u60M;u24H: PROCESS(COUT2,CLRN)VARIABLE tmpHa: INTEGER RANGE 0 TO 9;VARIABLE tmpHb: INTEGER RANGE 0 TO 2;BEGINIF CLRN='0' THEN tmpHb := 0; tmpHa := 0;ELSIF COUT2'event AND COUT2='1' THENIF EN='1' THENIF tmpHb=2 AND tmpHa=3 THEN tmpHa:=0; tmpHb:=0 ;COUT3<='1';ELSIF tmpHa=9 THEN tmpHa:=0; tmpHb:=tmpHb+1; COUT3<='0';ELSE tmpHa:=tmpHa+1;COUT3<='0';END IF;END IF;END IF ;QHA<=tmpHa;QHB<=tmpHb;COUT<=COUT3;END PROCESS u24H;END a;第二部分带校时电路的数字钟电路设计程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY zhuantaiji ISPORT ( CLK ,RESET: IN STD_LOGIC;y : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END zhuantaiji;ARCHITECTURE behav OF zhuantaiji ISTYPE states IS (st0, st1, st2, st3,st4);SIGNAL STX : states ;BEGINCOMREG : PROCESS(CLK,RESET) BEGIN IF RESET ='1' THEN STX <=st0;ELSIF CLK'EVENT AND CLK = '1' THENCASE STX ISWHEN st0 => STX <= st1;WHEN st1 => STX <= st2;WHEN st2 => STX <= st3;WHEN st3=> STX <= st0;WHEN OTHERS => STX <= st0;END CASE ;END IF;END PROCESS COMREG ;COM1: PROCESS(STX) BEGINCASE STX ISWHEN st0 => y <= "111" ;WHEN st1 => y <= "011" ;WHEN st2 => y <= "101" ;WHEN st3=> y <= "110";WHEN OTHERS =>y<="111";END CASE ;END PROCESS COM1 ;END behav;第三部分定时器控制电路及定时时间存储电路设计程序LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY ctrl_memo ISPORT( reset,k1,up_key: IN STD_LOGIC;Q_hourb : OUT INTEGER RANGE 0 TO 2;Q_houra : OUT INTEGER RANGE 0 TO 9;Q_minueb : OUT INTEGER RANGE 0 TO 5;Q_minuea : OUT INTEGER RANGE 0 TO 9);END ctrl_memo;ARCHITECTURE a OF ctrl_memo ISBEGINPROCESS(reset,k1,up_key)VARIABLE Q_tmpma: INTEGER RANGE 0 TO 9;VARIABLE Q_tmpmb: INTEGER RANGE 0 TO 5;VARIABLE Q_tmpha: INTEGER RANGE 0 TO 9;VARIABLE Q_tmphb: INTEGER RANGE 0 TO 2;BEGINIF reset='0' THEN Q_tmpma:= 0; Q_tmpmb:= 0;Q_tmpha:= 0; Q_tmphb:= 0;ELSIF up_key'event AND up_key='1' THENIF k1='1' THENIF Q_tmphb=2 AND Q_tmpha=3 THEN Q_tmphb:=0; Q_tmpha:=0 ;ELSIF Q_tmpha=9 THEN Q_tmpha:=0; Q_tmphb:=Q_tmphb+1;ELSE Q_tmpha:=Q_tmpha+1;END IF;elseIF Q_tmpmb=5 AND Q_tmpma=9 THEN Q_tmpmb:=0; Q_tmpma:=0 ;ELSIF Q_tmpma=9 THEN Q_tmpma:=0; Q_tmpmb:=Q_tmpmb+1;ELSE Q_tmpma:=Q_tmpma+1;END IF;END IF;END IF ;Q_hourb<=Q_tmphb; Q_houra<=Q_tmpha;Q_minueb<=Q_tmpmb; Q_minuea<=Q_tmpma;END PROCESS ;END a;仿真波形如下:第四部分正常计时时间和定时时间输出选择切换电路设计程序LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY NOR_ARM_CTL ISPORT(k2: IN STD_LOGIC;QSAI,QMAI,QHAI:IN INTEGER RANGE 0 TO 9;QSBI,QMBI:IN INTEGER RANGE 0 TO 5;QHBI:IN INTEGER RANGE 0 TO 2;QH_ARM_A,QM_ARM_A: IN INTEGER RANGE 0 TO 9;QH_ARM_B: IN INTEGER RANGE 0 TO 2;QM_ARM_B: IN INTEGER RANGE 0 TO 5;Q_HAO,Q_MAO,Q_SAO:OUT INTEGER RANGE 0 TO 9;Q_HBO: OUT INTEGER RANGE 0 TO 2;Q_MBO,Q_SBO : OUT INTEGER RANGE 0 TO 5);END NOR_ARM_CTL;ARCHITECTURE a OF NOR_ARM_CTL ISBEGINQ_HAO<=QHAI WHEN K2='1' ELSE QH_ARM_A;Q_HBO<=QHBI WHEN K2='1' ELSE QH_ARM_B;Q_MAO<=QMAI WHEN K2='1' ELSE QM_ARM_A;Q_MBO<=QMBI WHEN K2='1' ELSE QM_ARM_B;Q_SAO<=QSAI WHEN K2='1' ELSE 0;Q_SBO<=QSBI WHEN K2='1' ELSE 0;END a;仿真波形如下第五部分正常计时时间和闹铃时间比较器电路程序设计LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY BIJIAOQI ISPORT( CLk0: IN STD_LOGIC;QH_A,QM_A: IN INTEGER RANGE 0 TO 9;QH_B: IN INTEGER RANGE 0 TO 2;QM_B: IN INTEGER RANGE 0 TO 5;HARM_A,MARM_A: IN INTEGER RANGE 0 TO 9;HARM_B: IN INTEGER RANGE 0 TO 2;MARM_B: IN INTEGER RANGE 0 TO 5;SPEAK: OUT STD_LOGIC);END BIJIAOQI;ARCHITECTURE a OF BIJIAOQI ISSIGNAL Y: STD_LOGIC;BEGINSPEAK<=CLK0 AND Y;Y<='1' WHEN (QH_A=HARM_A) AND (QM_A=MARM_A) AND (QH_B=HARM_B) AND(QM_B=MARM_B) ELSE '0';END a;仿真波形如下第六部分校园打铃系统功能电路设计程序1.时间比较器设计程序LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY COMP_TIME ISPORT( K3: IN STD_LOGIC;Q_HA,Q_MA: IN STD_LOGIC_VECTOR(3 DOWNTO 0);Q_HB: IN STD_LOGIC_VECTOR(1 DOWNTO 0);Q_MB: IN STD_LOGIC_VECTOR(2 DOWNTO 0);Q_Y: OUT STD_LOGIC);END COMP_TIME;ARCHITECTURE a OF COMP_TIME ISSIGNAL QTIME:STD_LOGIC_VECTOR(12 DOWNTO 0);BEGINQTIME<=Q_HB & Q_HA & Q_MB & Q_MA;PROCESS(QTIME,K3)BEGINIF K3='1' THENCASE QTIME ISWHEN "0001101010000" => Q_Y<='1';WHEN "0001111000000" => Q_Y<='1';WHEN "0001111010000" => Q_Y<='1';WHEN "0010000110101" => Q_Y<='1';WHEN "0010001000101" => Q_Y<='1';WHEN "0010010110000" => Q_Y<='1';WHEN "0010011010000" => Q_Y<='1';WHEN "0100000110101" => Q_Y<='1';WHEN "0100001000101" => Q_Y<='1';WHEN "0100010110000" => Q_Y<='1';WHEN "0101000000000" => Q_Y<='1';WHEN "0101000010000" => Q_Y<='1';WHEN "0101001010101" => Q_Y<='1';WHEN "0101010000101" => Q_Y<='1';WHEN "0101011010000" => Q_Y<='1';WHEN "0101100000000" => Q_Y<='1';WHEN "0101101000101" => Q_Y<='1';WHEN "0101101010101" => Q_Y<='1';WHEN "0101111000000" => Q_Y<='1';WHEN "0110010000000" => Q_Y<='1';WHEN "0110011000101" => Q_Y<='1';WHEN "0110011010101" => Q_Y<='1';WHEN "1000001000000" => Q_Y<='1'; WHEN OTHERS=> Q_Y<='0';END CASE;ELSECASE QTIME ISWHEN "0001101000000" => Q_Y<='1';WHEN "0001110110000" => Q_Y<='1';WHEN "0001111000000" => Q_Y<='1';WHEN "0010000100101" => Q_Y<='1';WHEN OTHERS=> Q_Y<='0';END CASE;END IF;END PROCESS;END a;2电铃响铃时间15秒设计程序说明:因为比较器的输出QY高电平时间为1分钟,如果不作处理,则电铃将响1分钟。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA课程设计实验报告题目:VHDL编写的数字钟设计学院:电子信息学院专业:电子与通讯工程姓名:朱振军基于FPGA的VHDL数字钟设计一、功能介绍1.在七段数码管上具有时--分--秒的依次显示。

2.时、分、秒的个位记满十向高位进一,分、秒的十位记满五向高位进一,小时按24进制计数,分、秒按60进制计数。

3.整点报时,当计数到整点时扬声器发出响声。

4.时间设置:可以通过按键手动调节秒和分的数值。

此功能中可通过按键实现整体清零和暂停的功能。

5.LED灯循环显示:在时钟正常计数下,LED灯被依次循环点亮。

待增加功能:1.实现手动调节闹铃时间,在制定时间使扬声器发声。

2.实现微妙的快速计数功能,可实现暂停、保存当前时间、继续计数的功能。

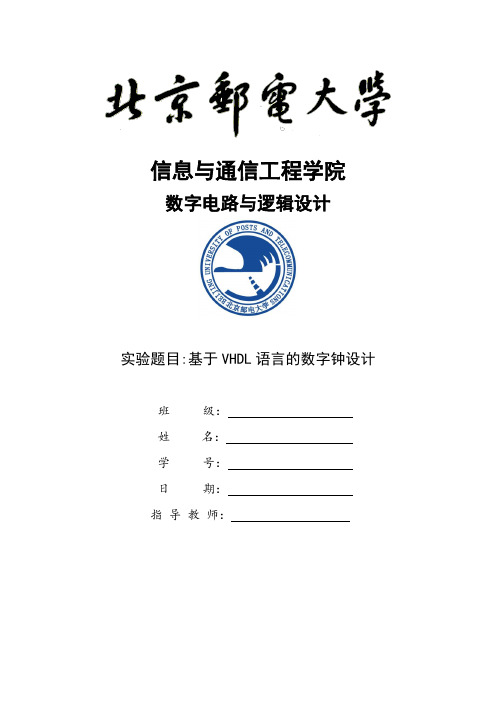

二、设计方案本文数字钟的设计采用了自顶向下分模块的设计。

底层是实现各功能的模块,各模块由vhdl语言编程实现:顶层采用原理图形式调用。

其中底层模块包括秒、分、时三个计数器模块、按键去抖动模块、按键控制模块、时钟分频模块、数码管显示模块共7个模块。

设计框图如下:图一数字钟系统设计框图由图1可以清晰的看到数字钟系统设计中各功能模块间连接关系。

系统时钟50MHZ经过分频后产生1秒的时钟信号,1秒的时钟信号作为秒计数模块的输入信号,秒计数模块产生的进位信号作为分计数模块的输入信号,分计数模块的进位信号作为时计数模块的输入信号。

秒计数模块、分计数模块、时计数模块的计数输出分别送到显示模块。

由于设计中要使用按键进行调节时间,而按键的动作过程中存在产生得脉冲的不稳定问题,所以就牵扯到按键去抖动的问题,对此系统中设置了按键去抖动模块,按键去抖动模块产生稳定的脉冲信号送入按键控制模块,按键控制模块根据按键的动作对秒、分、时进行调节。

图二数字钟的顶层设计原理图三、设计过程由数字钟的顶层设计原理图可知:系统的外部输入即为系统的时钟信号CLK =50MHZ,系统的外部输出有蜂鸣器信号buzzer,LED显示信号LED[3..1]和shan(与按键去抖动模块的o3相连),数码管显示信号xianshi[7..0],数码管位选信号xuanze[7..0]。

下面将对内部功能模块进行详细说明;1.分频模块pinlv对系统的时钟50MHZ进行分频,设置不同长度的计数值,当系统时钟clk有变化时计数器开始计数,当计数到某个值时输出一个信号,计数值不同输出信号的周期也就不同,从而实现了对系统时钟进行不同的分频,产生不同频率的信号。

由VHDL语言生成的模块图和程序说明如下:图三分频模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity pinlv isport( clk:in std_logic;--系统时钟输入端口clk2ms:out std_logic;clk500ms:out std_logic;clk1s:out std_logic);--各频率信号的输出端口end;architecture beh of pinlv isbeginp1:process(clk) –进程p1variable count1:integer range 0 to 49999999; beginif(clk'event and clk='1')then count1:=count1+1;--在clk 的上升沿计数if count1<=24999999 then clk1s<='0';elsif count1<=49999999 then clk1s<='1'; else count1:=0;--产生周期为1s的时钟信号end if;end if;end process p1;--结束进程p1p2:process(clk)—进程p2variable count2:integer range 0 to 99999; beginif(clk'event and clk='1')then count2:=count2+1;--在clk上升沿计数if count2<=49999 then clk2ms<='0';elsif count2<=99999 then clk2ms<='1';--产生周期为2ms的扫描信号end if;end if;end process p2;--结束进程p2p3:process(clk)—进程p3variable count3:integer range 0 to 24999999;beginif(clk'event and clk='1')then count3:=count3+1;在clk上升沿计数if count3<=12499999 thenclk500ms<='0';elsif count3<=24999999 then clk500ms<='1';else count3:=0;产生周期为500ms的时钟信号end if;end if;end process p3; end beh;2.按键去抖动模块qudou本设计用到FPGA开发板上的四个按键,由于按键有反应时间、抖动的问题,可能当按键被按一次时而系统感应到几次,造成误差。

所以应该进行按键消抖的处理,让每按一次键系统只感应到一次按键。

可以采用软件延时,触发反相器等方式进行消除抖动,本设计中采用软件延时的方式。

由VHDL语言生成的模块图和程序说明如下:图四按键去抖动模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity qudou isport(clk,k1,k2,k3,k4:in std_logic;o1,o2,o3,o4:outstd_logic);--设置按键输入信号输出端口end;architecture beh of qudou isbeginprocess(clk,k1,k2,k3,k4)variable cant1:integer;variable cant2:integer;variable cant3:integer;variable cant4:integer;beginif clk'event and clk='1' thenif k1='1' then cant1:=0;end if;--设置计数初值if k2='1' then cant2:=0;end if; --设置计数初值if k3='1' then cant3:=0;end if;if k4='1' then cant4:=0;end if; --设置计数初值if cant1>2499999 then o1<='0';else o1<='1';--延时0.5send if;if cant2>2499999 then o2<='0';else o2<='1'; --延时0.5send if;if cant3>2499999 then o3<='0'; else o3<='1'; --延时0.5send if;if cant4>2499999 then o4<='0'; else o4<='1'; --延时0.5send if;cant1:=cant1+1; --加一计数cant2:=cant2+1; --加一计数cant3:=cant3+1; --加一计数cant4:=cant4+1; --加一计数end if;end process;end beh;--设置计数初值在quartus II 开发环境中进行仿真验证图五 按键去抖动仿真效果图由于0.5s 太长,在本仿真中设置了很小的一个量10clk ,从图中可以看出基本实现了按键去抖动的效果。

无论按键怎么抖动,输出总是保持稳态10clk ,当下一个触发来了以后,就可以触发单稳态。

3,按键控制模块self1本设计中使用了两个按键进行对时钟的暂停和调秒操作,当ok2按下时时钟暂停,再按ok3则进行秒个位的加一计数,每按一次进行加一处理。

当调节好时间后,在按ok2键重新开始计数。

由VHDL 语言生成的模块图和程序说明如下:图六 按键控制模块library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity self1 is port( c:in std_logic;ok2:in std_logic;ok3:in std_logic; ck:out std_logic); end ;--设置端口architecture bea of self1 is signal m:std_logic; signal t:std_logic;beginp1:process(ok2,ok3,c)—ok2和ok3触发进程beginif ok2'event and ok2='0' then m<=not m;--由ok2 的动作产生m 的电平信号 end if;if m='1' then ck<=not(ok3);--把按键ok3的脉冲信号给输出else ck<=c;--否则把正常计数时钟给输出end if;end process p1;--结束进程 end bea;4,秒、分六十进制模块cantsixty本设中秒、分的六十进制是由个位的十进制和十位的六进制进行组合实现的。

当个位记到9时自动向高位进一,同时个位自动清零。

当十位记到5并且个位记到9时,自动产生一个进位脉冲,同时个位和十位分别从零开始重新计数。

由VHDL 语言生成的模块图和程序说明如下:图七 六十进制模块library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cantsixty isport(clk:in std_logic; reset:in std_logic;out1:out std_logic_vector(3 downto 0);out2:out std_logic_vector(3 downto 0);c:out std_logic); end;architecture beh of cantsixty is signal ss1,ss2:std_logic_vector( 3 downto 0);beginp1:process(clk,reset) beginif(reset='0')thenss1<="0000";ss2<="0000";elsif(clk'event and clk='1')then if ss1="1001" and ss2="0101" then c<='1';--当计数到59时产生进位信号 else c<='0';--否则不产生 end if;if ss1="1001" then ss1<="0000"; if ss2="0101" then ss2<="0000"; else ss2<=ss2+1; end if;else ss1<=ss1+1;--计数过程 end if;end if;end process p1;--结束进程out1<=ss1;out2<=ss2;--把信号送输出 end beh;在quartus II 开发环境中进行仿真验证:图八 六十进制波形仿真图由上图可见,当1s 的时钟信号加入时,个位out1从0到9不断循环,而且当个位out1记到9时产生一个进位信号 使十位out2加一,以此类推就实现了六十进制计数。