PrimeTime基本命令介绍(比较全)

EDA工具课程之PrimeTime

Company Logo

五、PrimeTime命令简介

指定生成的时钟

create_generated_clock [-name clock_name] -source master_pin [-divide_by divide_factor | -multiply_by multiply_factor] [-duty_cycle percent] source_objects pt_shell> create_generated_clock -multiply_by 2 -duty_cycle 60 -source [get_pins CLK] [get_pins foo1]

三、PrimeTime进行时序分析的流程

3、 说明时序例外情况(timing exceptions) -设置多周期路径(multicycle paths) -设置虚假路径(false paths) -定义最大和最小延时、路径分割(path segmentation)和失效弧 (disabled arcs)

Company Logo

三、PrimeTime进行时序分析的流程

1、 建立设计环境 - 建立搜索路径(search path)和链接路径(link path) - 读入设计和库 (read_verilog和read_db) - 链接顶层设计 -建立运作条件、连线负载模型、端口负载、驱动和传输时间

Company Logo

五、PrimeTime命令简介

创建时钟

create_clock -period period_value [-waveform edge_list] [-name clock_name] [source_objects]

PrimeTime_的基本概念

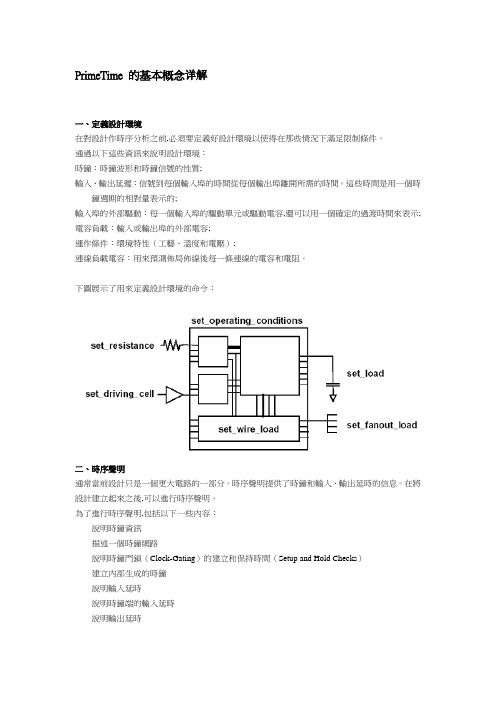

PrimeTime 的基本概念一、定義設計環境在對設計作時序分析之前,必須要定義好設計環境以使得在那些情況下滿足限制條件。

通過以下這些資訊來說明設計環境:時鐘:時鐘波形和時鐘信號的性質;輸入、輸出延遲:信號到每個輸入埠的時間從每個輸出埠離開所需的時間。

這些時間是用一個時鐘週期的相對量表示的;輸入埠的外部驅動:每一個輸入埠的驅動單元或驅動電容,還可以用一個確定的過渡時間來表示; 電容負載:輸入或輸出埠的外部電容;運作條件:環境特性(工藝、溫度和電壓);連線負載電容:用來預測佈局佈線後每一條連線的電容和電阻。

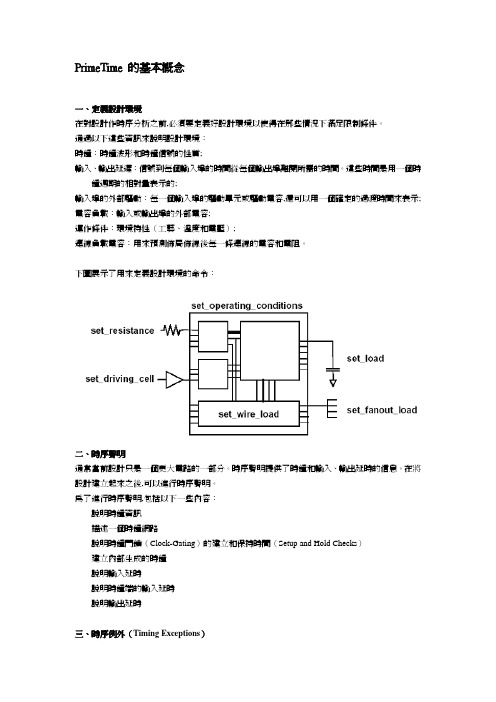

下圖展示了用來定義設計環境的命令:二、時序聲明通常當前設計只是一個更大電路的一部分。

時序聲明提供了時鐘和輸入、輸出延時的信息。

在將設計建立起來之後,可以進行時序聲明。

為了進行時序聲明,包括以下一些內容:說明時鐘資訊描述一個時鐘網路說明時鐘門鎖(Clock-Gating)的建立和保持時間(Setup and Hold Checks)建立內部生成的時鐘說明輸入延時說明時鐘端的輸入延時說明輸出延時三、時序例外(Timing Exceptions)PrimeTime缺省地認為所有的電路都是單時鐘週期的。

這意味著電路在一個時鐘週期之內將資料從一條路徑的開始端傳遞到結束端。

在某些情況下,電路不是工作在這樣的方式下。

對具體的一條路徑來說不適用單始終週期時序,所以必須對這些缺省的時序假設作例外說明。

否則,時序分析將不能反映真實電路的工作情況。

主要有以下一些內容:單時鐘週期(缺省)路徑延時限制設置失敗(False)路徑設置最大和最小路徑延時設置多時鐘週期路徑路徑說明方法有效地說明例外情況例外情況的優先順序報告例外情況忽略例外情況去除例外聲明四、報告的生成在定義了時序聲明和例外情況之後,可以生成時序分析報告,有助於定位設計中的違規之處。

在進行時序分析的時候,PrimeTime會跟蹤電路中所有的路徑,然後根據電路說明、庫、聲明和例外情況計算設計的延時。

PrimeTime基本命令介绍(比较全)

PrimeTime基本命令一、R un Prime Time1.module add synnew2.primetime & 启动图形界面3.pt_shell –f RUN.tcl | tee –I run.log 用命令行启动脚本二.一些命令的叙述1.Setup time : data required time – data arrival time2.Hold time : data arrival time – data required time3.Report_analysis_coverage :看一下所有错误的基本情况-status violated-check “setup hold”-sort_by slack-sort_by check_type4.Report_timing :显示the worst slack for setup time5.Report_timing –delay max :看setup time6.Report_timing –delay min :看hold time7.Pt_shell –x “restore_session orca_savesession” :继续原来保存的信息8.Set sh_enable_page_mode true : 分页显示9.Report_lib libname :看库的信息10. Report_timing –group SYS_clk :看某个时钟的信息11. Pre CTS clock Uncertainty = clock skew + clock jitter +marginPost CTS clock Uncertainty = clock jitter + margin还要加上Set_propagated_clock [all_clocks]12. Report_timing –path full_clock :可以显示clock的详细信息13. Report_timing –from E,Report_timing –to Z,Report_timing –from G –to FF4/D :显示详细路径的信息14. Report_port –input_delay –output_delay inoutpad,Report_port –input_delay inputpadReport_port –ouput_delay outputpad: 看port的信息15. Report_timing –input_pins :可以看到net的delay16. Report_lib –timing_arcs libname cellname:看库单元的时序信息17. Report_cell –connections –verbose Instance_name :看单元的信息28. Report_timing –max_paths 2 –nworst 2 :可以看两条path的两个最坏的timing,default为1。

门级静态时序分析与PrimeTime使用

第六章门级静态时序分析 PrimeTime一、PrimeTime简介PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys 其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有多哥时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境-建立搜索路径(search path)和链接路径(link path)-读入设计和库-链接顶层设计-建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)-定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)-说明输入、输出端口的延时3、说明时序例外情况(timing exceptions)-多周期路径(multicycle paths)-不合法路径(false paths)-说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告-检查时序-生成约束报告-生成路径时序报告二、静态时序分析中路径延时的计算静态时序分析工具一般将电路网表看成一个拓扑图,图中的节点(node)代表电路中的引脚(pin)。

Primetime时序分析流程与方法

PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有多哥时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境- 建立搜索路径(search path)和链接路径(link path)- 读入设计和库- 链接顶层设计- 建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)- 定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)- 说明输入、输出端口的延时3、说明时序例外情况(timing exceptions)- 多周期路径(multicycle paths)- 不合法路径(false paths)- 说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告- 检查时序- 生成约束报告- 生成路径时序报告开始先建立目录并将PrimeTime本身所带的一个例子拷到新建的目录下,在下面的内容中将要用到这个例子。

Primetime时序分析流程与方法

Primetime时序分析流程与方法PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查,Setup and hold checks,重新覆盖和去除检查,Recovery and removal checks,时钟脉冲宽度检查(Clock pulse width checks) 时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点,endpoint,主从时钟分离,Master-slave clock separation,有多哥时钟的寄存器对层次敏感的时钟,Level-sensitive clocking,组合电路的反馈环,Combinational feedback loops,设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境such as wages, subsidies to give some support, the new finds at national, provincial and municipal engineering laboratories, research centers and otherSome research funding support from the platform. Second, business methods of science are diverse. Innovative investment methods, expanding investment channels, to investment to achieve tangible results. At present, in the County completed project is our invitation to workcan make good use of resources, rich with enterprise information, contacts, and other resources for investment by business, not only low cost and high efficiency. Relatives and friends also can use outside resources, we must actively take the initiative to strengthen contacts with them, making full use of their resources, for the County investment broker. The town streets, industrial development focal points to pick a strong backbone of investment, aimed at more recent relocation ofBeijing-Tianjin-Tangshan, Yangtze River Delta and other economically developed areas, the implementation of resident merchants. Internet merchants, so ... ... Investment, investment, investment policy on the Internet "play" and let customers know more about ... ... and the ... ... and yearn for. ... ... Make full use of the Internet for valuable business information, communicating and negotiating with that as a clue. Investment firm into line and encourage qualified enterprises toactively introduce strategic partners, through mergers, asset restructuring, equity investment, transfer, technological innovation and other forms of enterprise- 建立搜索路径,search path,和链接路径,link path,- 读入设计和库- 链接顶层设计- 建立运作条件、违线负载模型、端口负载、驱动和传输时间2、说明时序声明,约束,- 定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency) - 说明输入、输出端口的延时3、说明时序例外情况,timing exceptions,- 多周期路径,multicycle paths,- 不合法路径(false paths)- 说明最大和最小延时、路径分割,path segmentation,和失效弧,disabled arcs, 4、进行分析和生成报告- 检查时序- 生成约束报告- 生成路径时序报告开始先建立目录并将PrimeTime本身所带的一个例子拷到新建的目录下,在下面的内容中将要用到这个例子。

PrimeTime操作步骤

PrimeTime操作步骤ZhangXiandongRevision 0.1File Path: \\192.168.1.122\digitalic\Pub\SHARED\yexianyang\PrimeTime.docCopyright @ 2006-2010 Tianjin Topbroad Microelectronics Co., Ltd. All rights reserved. The material in this document constitutesTable Of Contents1 Open Issues (3)Open Feature Issues (3)Open Implementation Issues (3)2 PrimeTime 的概述介绍 (4)2.1 PrimeTime 的功能特点 (4)2.2 PrimeTime进行时序分析的流程 (5)2.3 PrimeTime中的对象 (5)2.3.1对象的概念 (5)2.3.2 在PrimeTime中使用对象 (6)2.3.3 针对collection的操作 (6)2.3.4 属性 (8)2.3.5 查看命令 (8)3静态时序分析前的具体准备工作 (8)3.1 设置查找和链接路径 (8)3.2 读入设计文件 (9)3.3 链接 (10)3.4 设置静态时序分析参数 (10)3.5 进行静态时序分析并生成报告 (11)4 Revision Changes (13)Copyright @ 2006-2010 Tianjin Topbroad Microelectronics Co., Ltd. All rights reserved. The material in this document constitutes1 Open IssuesList all open issues. Include short description of resolution when closed. This should not be detailed.Open Feature Issues1Issue:Resolution:2Issue:Resolution:3Issue:Resolution:Open Implementation Issues1Issue:Resolution:2Issue:Resolution:Copyright @ 2006-2010 Tianjin Topbroad Microelectronics Co., Ltd. All rights reserved. The material in this document constitutes2 PrimeTime 的概述介绍一般来说,要分析或检验一个电路设计的时序方面的特征主要有两种手段:动态时序仿真 (Dynamic Timing Simulation)和静态时序分析(Static Timing Analysis)。

PrimeTime

--Setting False Paths • False paths是指在时序分析时可以被忽略的 路径。 • 使用set_false_path命令指定设计中的false paths。 • 当(约束)目标是一个时序节点,false path仅仅应用于两个节点之间。而当(约束) 目标是一个时钟,false path将应用于所有 该时钟控制的源节点(-from)到目标节点(-to) 的路径。

Divide-by-2 Clock Definition

-Generated Clock

生成时钟是指由 电路生成的时钟, 而不是直接用外 部的资源。一个 简单的例子—适 中的二分频(如 下图),每个生 成的时钟都必须 用命令 create_generated _clock定义,此 命令指出生成时 钟的源的引脚或 端口

Multicycle Hold Timing Exceptions

在输入数据 后的第三个 时钟上升沿 建立检查

保持检 查时间 比默认 的早2个 时钟周 期

建立

默认 的保 持

总结

• set_multicycle_path -setup 2 -from ..-to .. 命令 中-setup后的数指定了在哪个时钟沿执行建立 检查,默认为1。 • set_multicycle_path -hold 2 -from .. -to ..命令中hold后的数指定了保持检查从默认位置向后移 动的周期数,默认为0. • (hold cycles) = (setup option value) – 1 – (hold option value) • By default, hold cycles = 1 – 1 – 0 = 0. • 上图中, hold cycles = xception Paths

PrimeTime使用说明(中文)

Tcl 与 pt_shell 的使用

6

第三章 Tcl 与 pt_shell 的使用

Tcl 是 Tool Command Language 的缩写,由于 PrimeTime 的命令语言是基于 Tcl 标准的,所以在这一章里我想大致介绍一下 Tcl 在 PrimeTime 中的基本使用。 除了一些最常用的 Tcl 命令之外,主要介绍了 pt_shell 中有关对象和属性的操 作。

关键词:

静态时序分析 形式验证 PrimeTime Formality Tcl

目录

第一章 绪论 1.1 静态时序分析 1.2 时序验证技术

第二章 PrimeTime 简介 2.1 PrimeTime 的特点和功能 2.2 PrimeTime 进行时序分析的流程 2.3 静态时序分析中所使用的例子 2.4 PrimeTime 的用户界面

PrimeTime 简介

3

第二章 PrimeTime 简介

正如本文前面所提到的,静态时序分析方法由于有着更快的分析速度等优点, 正在被更多的设计者们所重视。PrimeTime 是 Synopsys 的静态时序分析软件,常 被用来分析大规模、同步、数字 ASIC。PrimeTime 适用于门级的电路设计,可以和 Synopsys 公司的其它 EDA 软件非常好的结合在一起使用。

事实上,大多数 synopsys 公司的 EDA 工具都是基于 Tcl 标准的。例如在第二 章的图 2-1 中可以看到的综合软件 Design Compiler 也是。由于都基于 Tcl 标准, PrimeTime 中的大多数命令以及命令参数都和 Design Compiler 中是相同的。

§3.1 Tcl 中的变量 我们可以把 Tcl 看作是一种比较高级的语言,它很容易理解和使用,所以这里 对它的介绍也是很简单的。 与变量有关的有下列操作: 1)定义变量:set 变量名 变量值

静态时序分析综述报告以及primetime简介

静态时序分析综述报告——孙声震1.静态时序分析静态时序分析(STA)就是套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。

1.1 背景仿真技术是ASIC设计过程中应用最多的验证手段,然而,现在的单片集成系统设计正在将仿真时间推向无法容忍的极限。

在最后的门级仿真阶段,针对的是几十乃至几百万门的电路,对仿真器第一位的要求是速度和容量,因此,性能(仿真速度)和容量(能够仿真的设计规模)是验证中的关键因素。

传统上采用逻辑仿真器验证功能时序,即在验证功能的同时验证时序,它以逻辑模拟方式运行,需要输入向量作为激励。

随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,而最大的问题是难以保证足够的覆盖率。

鉴于此,这种方法已经越来越少地用于时序验证,取而代之的是静态时序分析技术。

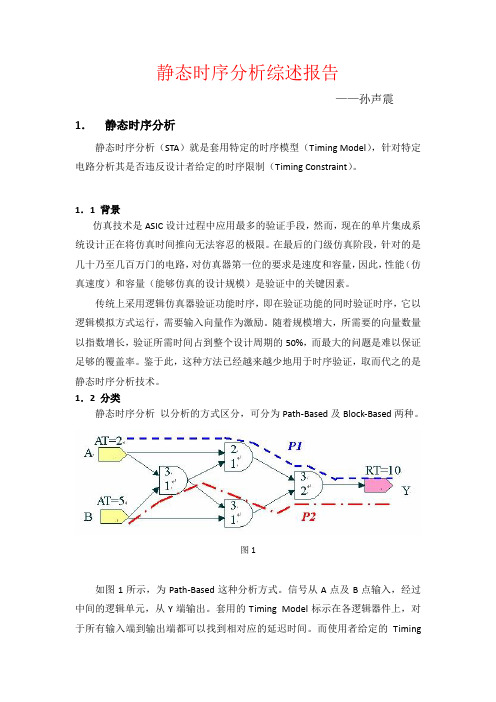

1.2 分类静态时序分析以分析的方式区分,可分为Path-Based及Block-Based两种。

图1如图1所示,为Path-Based这种分析方式。

信号从A点及B点输入,经过中间的逻辑单元,从Y端输出。

套用的Timing Model标示在各逻辑器件上,对于所有输入端到输出端都可以找到相对应的延迟时间。

而使用者给定的TimingConstraint为:1. 信号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2. 信号B到达电路输入端的时间点为5(AT=5)。

3. 信号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

针对P1及P2 两条路径(Path)来做分析。

P1的起始点为A,信号到达时间点为2。

经过第1个逻辑器件之后,由于有2单位的延迟时间,所以信号到达这个器件输出的时间点为4(2+2)。

依此类推,信号经由P1到达输出Y的时间点为7(2+2+3)。

在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

EDA技术Synopsys公司STA工具PrimeTime介绍ppt课件

ASIC设计中心

PrimeTime命令

EDA技术实验

1 设计输入

PT不能读取RTL源文件,它是静态分析引擎, 只能读取映射后的设计,包括db、verilog、 vhdl等格式的文件。 pt_shell> read_db –netlist_only <filename>.db

2018/11/15 2 ASIC设计中心

PT

EDA技术实验

PT是Synopsys的sign-off quality的STA 工具,是一个单点的全芯片、门级静态时 序分析器。 PrimeTime工作在设计的门级层次,并 且和Synopsys其它工具整合得很紧密。

2018/11/15

3

ASIC设计中心

2018/11/15

7

ASIC设计中心

PT进行时序分析的流程

EDA技术实验

进行时序分析:

在作好以上准备工作的基础上,可以对电路 进行静态时序分析,生成constraint reports 和path timing reports。

2018/11/15

8

ASIC设计中心

PrimeTime的用户界面

读入设计(和库文件) 链接顶层设计 对必要的操作条件进行设置,这里包括了线上负载 的模型、端口负载、驱动、以及转换时间等

2018/11/15

5

ASIC设计中心

PT进行时序分析的流程

EDA技术实验

指定时序约束(timing constraints)

定义时钟周期、波形、不确定度(uncertainty)、延 时(latency) 指明输入输出端口的延时等

PT

EDA技术实验

基本特点和功能:

建立和保持时间的检查(setup and hold checks) 时钟脉冲宽度的检查 门控时钟检查(clock-gating checks) recovery and removal checks unclocked registers 未约束的时序端点(unconstrained timing endpoints) multiple clocked registers 组合反馈回路(combinational feedback loops) 基于设计规则的检查,包括对最大电容、最大传输时间、 最大扇出的检查等。

primetime dmsa 变量-概述说明以及解释

primetime dmsa 变量-概述说明以及解释1.引言1.1 概述在进行Primetime DMSA (Delay Mode Setup Assist) 变量分析之前,我们首先需要了解Primetime DMSA 是什么以及它在电路设计中扮演的角色。

Primetime DMSA 是半导体行业中一种常用的时序分析工具,它用于评估和优化集成电路的时序约束。

时序约束是指对电路中各个时序参数的限制,例如时钟频率、数据延迟等。

随着集成电路设计的复杂性和规模的不断增大,时序的分析和优化变得越来越重要。

Primetime DMSA 提供了强大的功能,能够帮助设计师在各种约束条件下进行时序分析,并辅助设计师进行设计优化。

它可以通过对电路中各个时序变量进行敏感性分析,帮助设计师找到对性能影响最大的变量,从而进行有针对性的优化。

本文将重点介绍Primetime DMSA 中的三个关键变量:变量A、变量B和变量C。

这些变量在电路设计中具有重要的影响,对电路的性能和可靠性都有一定的影响。

通过深入分析这些变量的特性和作用,我们可以更好地理解其对电路时序的影响,进而为工程师提供更准确的设计指导和优化建议。

接下来的章节将详细介绍这些变量的定义、测量方法以及对电路性能的影响。

2.1 将着重讨论变量A,2.2 将深入探讨变量B,而2.3 则将把光芒投射到变量C上。

最后一节结论将总结对这些变量的影响,并为读者提供一些值得注意的结论和启示。

通过本文的阅读,读者将能够更全面地了解Primetime DMSA 变量的重要性以及如何进行时序的优化。

希望本文能为读者提供有用的信息,并对电路设计师在Primetime DMSA 分析中的决策过程提供一定的指导。

1.2 文章结构文章结构:本文主要分为引言、正文和结论三个部分。

其中,引言部分包括概述、文章结构和目的。

正文部分主要介绍primetime dmsa 变量的相关内容,其中包括变量A、变量B和变量C的介绍和影响。

PrimeTime 的基本概念详解

PrimeTime 的基本概念详解一、定義設計環境在對設計作時序分析之前,必須要定義好設計環境以使得在那些情況下滿足限制條件。

通過以下這些資訊來說明設計環境:時鐘:時鐘波形和時鐘信號的性質;輸入、輸出延遲:信號到每個輸入埠的時間從每個輸出埠離開所需的時間。

這些時間是用一個時鐘週期的相對量表示的;輸入埠的外部驅動:每一個輸入埠的驅動單元或驅動電容,還可以用一個確定的過渡時間來表示; 電容負載:輸入或輸出埠的外部電容;運作條件:環境特性(工藝、溫度和電壓);連線負載電容:用來預測佈局佈線後每一條連線的電容和電阻。

下圖展示了用來定義設計環境的命令:二、時序聲明通常當前設計只是一個更大電路的一部分。

時序聲明提供了時鐘和輸入、輸出延時的信息。

在將設計建立起來之後,可以進行時序聲明。

為了進行時序聲明,包括以下一些內容:說明時鐘資訊描述一個時鐘網路說明時鐘門鎖(Clock-Gating)的建立和保持時間(Setup and Hold Checks)建立內部生成的時鐘說明輸入延時說明時鐘端的輸入延時說明輸出延時三、時序例外(Timing Exceptions)PrimeTime缺省地認為所有的電路都是單時鐘週期的。

這意味著電路在一個時鐘週期之內將資料從一條路徑的開始端傳遞到結束端。

在某些情況下,電路不是工作在這樣的方式下。

對具體的一條路徑來說不適用單始終週期時序,所以必須對這些缺省的時序假設作例外說明。

否則,時序分析將不能反映真實電路的工作情況。

主要有以下一些內容:單時鐘週期(缺省)路徑延時限制設置失敗(False)路徑設置最大和最小路徑延時設置多時鐘週期路徑路徑說明方法有效地說明例外情況例外情況的優先順序報告例外情況忽略例外情況去除例外聲明四、報告的生成在定義了時序聲明和例外情況之後,可以生成時序分析報告,有助於定位設計中的違規之處。

在進行時序分析的時候,PrimeTime會跟蹤電路中所有的路徑,然後根據電路說明、庫、聲明和例外情況計算設計的延時。

门级静态时序分析与PrimeTime使用

第六章门级静态时序分析 PrimeTime一、PrimeTime简介PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys 其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有多哥时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境-建立搜索路径(search path)和链接路径(link path)-读入设计和库-链接顶层设计-建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)-定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)-说明输入、输出端口的延时3、说明时序例外情况(timing exceptions)-多周期路径(multicycle paths)-不合法路径(false paths)-说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告-检查时序-生成约束报告-生成路径时序报告二、静态时序分析中路径延时的计算静态时序分析工具一般将电路网表看成一个拓扑图,图中的节点(node)代表电路中的引脚(pin)。

PrimeTime时序分析流程和方法

PrimeTime时序分析流程和方法基本特点和功能:时序检查方面:建立和保持时序的检查(Setupandholdcheck)重新覆盖和去除检查(Recoveryandremovalcheck)时钟脉冲宽度检查(Clockpulewidthcheck)时钟门锁检查(Clock-gatingcheck)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Mater-laveclockeparation)有多哥时钟的寄存器对层次敏感的时钟(Level-enitiveclocking)设计规则检查,包括最大电容(ma某imumcapacitance)、最大传输时间(ma某imumtranition)和最大扇出(ma某imumfanout)-建立搜索路径(earchpath)和链接路径(linkpath)-读入设计和库-链接顶层设计-建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)-定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)-说明输入、输出端口的延时3、说明时序例外情况(timinge某ception)-多周期路径(multicyclepath)-不合法路径(falepath)-说明最大和最小延时、路径分割(pathegmentation)和失效弧(diabledarc)4、进行分析和生成报告-检查时序-生成约束报告-生成路径时序报告开始cp–r$SYNOPSYS/doc/pt/tutorial.cdtutorial确认目录中有以下这些文件:AM2910.dbThedeign.dbforthetop-levelofthedeignCONTROL.dbThedeign.dbfortheCONTROLblockREGCNT.dbT hedeign.dbfortheREGCNTblockUPC.dbThedeign.dbfortheUPCblockY.data TheStampdatafilefortheYblockY.modTheStampmodelfilefortheYblockY_ lib.dbThelibrary.dbfortheYblockSTACK_lib.dbThelibrary.dbfortheSTACKblockpt_lib.dbThetechnol ogylibrary.dbtack.qtm.ptThequicktimingmodelcriptforthetackblockoptimize.d chThedc_helloptimizationcript例子是一个AM2910微处理器,如图所示模块图。

PrimeTimeSI相关运用及概念

PrimeTime –SI 相关运用及概念PrimeTime SI主要分析两种信号串扰:delay和static noise(noise bump or glitch)。

PrimeTime SI认为两种情况不存在信号串扰:1)aggressor和victim之间的耦合电容非常小;2)aggressor和victim的信号transition time不相互交叠。

在不交叠的时候,如果aggressor 对victim产生的glitch足够大,使victim的逻辑发生变化,则PrimeTime SI也会考虑。

如何使用PrimeTime SI进行crosstalk delay分析(analysis mode : on-chip variation)基于PrimeTime命令、library以及脚本,额外的步骤如下:1)使能PrimeTime SIset_app_var si_enable_analysis true2)读取SPEF文件中包含的耦合电容信息(确认SPEF包含耦合电容信息,StarRC是否有相应的option?)read_parasitics –keep_capacitive_coupling file_name.spf3)设置PrimeTime SI performance相关参数(选择设置set_app_var)PrimeTime脚本中crosstalk report的相关命令report_si_bottleneckreport_delay_calculation -crosstalk -from pin -to pinExample:PrimeTime SI是如何运行的(two iteration)1)基于victim net上bump voltage的值(通过设置threshold)过滤掉影响很小的aggressor net;2)把没有被过滤的net作为initial net来进行crosstalk分析,也可自己定义;3)Delay calculation计算timing delay分为两个阶段,第一阶段为悲观估计,工具首先假设所有的aggressor会对victim在同一时刻产生信号串扰,找出worst-case delay values;第二阶段考虑timing window 以及crosstalk的contribution,即通过分析aggressor net的transition time以及direction看是否会影响到victim net。

PrimeTime 时序分析流程和方法

PrimeTime 时序分析流程和方法PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有多哥时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境- 建立搜索路径(search path)和链接路径(link path)- 读入设计和库- 链接顶层设计- 建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)- 定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)- 说明输入、输出端口的延时3、说明时序例外情况(timing exceptions)- 多周期路径(multicycle paths)- 不合法路径(false paths)- 说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告- 检查时序- 生成约束报告- 生成路径时序报告开始先建立目录并将PrimeTime本身所带的一个例子拷到新建的目录下,在下面的内容中将要用到这个例子。

PrimeTime 时序分析流程和方法

PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。

它能分析大规模、同步、数字ASICS的时序。

PrimeTime工作在设计的门级层次,并且和Synopsys其它工具整合得很紧密。

基本特点和功能:时序检查方面:建立和保持时序的检查(Setup and hold checks)重新覆盖和去除检查(Recovery and removal checks)时钟脉冲宽度检查(Clock pulse width checks)时钟门锁检查(Clock-gating checks)设计检查方面:没有时钟端的寄存器没有时序约束的结束点(endpoint)主从时钟分离(Master-slave clock separation)有xx时钟的寄存器对层次敏感的时钟(Level-sensitive clocking)组合电路的反馈环(Combinational feedback loops)设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout)PrimeTime 时序分析流程和方法:在时序分析之前需要做的步骤:1、建立设计环境-建立搜索路径(search path)和链接路径(link path)-读入设计和库-链接顶层设计-建立运作条件、连线负载模型、端口负载、驱动和传输时间2、说明时序声明(约束)-定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency)-说明输入、输出端口的xx3、说明时序例外情况(timing exceptions)-多周期路径(multicycle paths)-不合法路径(false paths)-说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs)4、进行分析和生成报告-检查时序-生成约束报告-生成路径时序报告开始先建立目录并将PrimeTime本身所带的一个例子拷到新建的目录下,在下面的内容中将要用到这个例子。

EDA技术_Synopsys公司STA工具PrimeTime介绍

Perform a full analysis and examine the results

check_timing report_cell report_clock report_design report_hierarchy report_wire_load report_port report_reference report_path_group report_net report_lib report_timing report_constraint report_bottleneck report_analysis_coverage

create_clock set_clock_uncertainty set_clock_latency set_clock_transition set_input_delay set_output_delay

Specify the environment and analysis conditions

EDA技术实验 技术实验

Synopsys公司 公司STA工具 工具PrimeTime 公司 工具

2010-12-29

1

静态时序分析STA

EDA技术实验 技术实验

静态时序分析( 静态时序分析(Static Timing Analysis)技术 ) 是一种穷尽分析方法,用以衡量电路性能。 是一种穷尽分析方法,用以衡量电路性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PrimeTime基本命令

一、R un Prime Time

1.module add synnew

2.primetime & 启动图形界面

3.pt_shell –f RUN.tcl | tee –I run.log 用命令行启动脚本

二.一些命令的叙述

1.Setup time : data required time – data arrival time

2.Hold time : data arrival time – data required time

3.Report_analysis_coverage :看一下所有错误的基本情况

-status violated

-check “setup hold”

-sort_by slack

-sort_by check_type

4.Report_timing :显示the worst slack for setup time

5.Report_timing –delay max :看setup time

6.Report_timing –delay min :看hold time

7.Pt_shell –x “restore_session orca_savesession” :继续原来保存的信息

8.Set sh_enable_page_mode true : 分页显示

9.Report_lib libname :看库的信息

10. Report_timing –group SYS_clk :看某个时钟的信息

11. Pre CTS clock Uncertainty = clock skew + clock jitter +margin

Post CTS clock Uncertainty = clock jitter + margin还要加上

Set_propagated_clock [all_clocks]

12. Report_timing –path full_clock :可以显示clock的详细信息

13. Report_timing –from E,

Report_timing –to Z,

Report_timing –from G –to FF4/D :显示详细路径的信息

14. Report_port –input_delay –output_delay inoutpad,

Report_port –input_delay inputpad

Report_port –ouput_delay outputpad: 看port的信息

15. Report_timing –input_pins :可以看到net的delay

16. Report_lib –timing_arcs libname cellname:看库单元的时序信息

17. Report_cell –connections –verbose Instance_name :看单元的信息

28. Report_timing –max_paths 2 –nworst 2 :可以看两条path的两个最坏的timing,

default为1。

29. Report_timing –slack_lesser_than

-slack_greater_than

-to –rise_to –fall_to

-from –rise_from –fall_from

-through –rise_through –fall_through

-exclude –rise_exclude –fall_exclude

30. Report_clock_timing :看clock skew,latency or transition等信息

31. get_pins –of_objects instance_name : Find all pin names for a specific cell.

32. all_fanin –flat –start –to FF1/D :All the start point pins to a specific end point.

33. all_inputs –clock CLK1 : Find all input ports constrained by a clock

34. all_outputs :Find all output ports.

35. all_registers –level_sensitive –data_pins :Find the data pin names of all latches.

36. all_connected U1/Z : Find the net connected to a pin.

37.report_constraint –all :List all violations, sorted by clock domain

38.report_timing –nets :可以看到Fanout

-significant_digits 3 :显示小数点后3位

39. get_alternative_lib_cell –lib lib_name instance_name:找功能相同的单元

40. report_net –connections –verbose netname

41. report_bottleneck –cost_type fanout_endpoint_cost: Identify cells involved in

multiple violations.

.synopsys_pt.setup

alias h {history}

alias page_on {set sh_enable_page_mode true}

alias page_off {set sh_enable_page_mode false}

history keep 200

set sh_enable_line_editing true

三、一个基本的脚本文件

./RUN.tcl

Scripts/variables.tcl 四、下面为./RUN.tcl 的实例

#Run script for ORCA

set search_path {. ./scripts ./libs ./des }

append link_path tech_lib.db RAM_lib.db

source ./scripts/variables.tcl

#Read all gate-level design files

read_verilog my_full_chip.v

link_design ORCA

read_sdf –analysis_type on_chip_variation orca.sdf.gz

print_message_info; quit

#Terminate on PrimeTime and Tcl errors

set sh_script_stop_severity E

#Report missing SDF delays or timing checks

redirect –append ./EW.log \

{report_annotated_delay; report_annotated_check} redirect –append ./EW.log {print_message_info}

#显示Warning&Error

set sh_source_emits_line_numbers W

source –echo –verbose ./scripts/constraints.tcl

#For further debugging

check_timing –verbose

#Generate initial reports

report_analysis_coverage

#save the session

save_session –replace orca_savesession。