第二章 嵌入式系统的基本知识

如何使用C语言进行嵌入式系统开发

如何使用C语言进行嵌入式系统开发第一章:引言嵌入式系统是一种专门设计用于特定应用领域的计算机系统,它通常由硬件平台和软件系统组成。

C语言作为一种高级编程语言,广泛应用于嵌入式系统开发中。

本文将介绍如何使用C语言进行嵌入式系统开发。

第二章:了解嵌入式系统在使用C语言进行嵌入式系统开发之前,我们需要了解嵌入式系统的基本概念和特点。

嵌入式系统通常运行在资源受限的环境中,因此需要对系统资源的管理和利用进行精确控制。

嵌入式系统的开发过程需要考虑实时性、可靠性、功耗等因素。

第三章:基础知识在使用C语言进行嵌入式系统开发之前,我们需要掌握一些基础知识。

首先是C语言的基本语法和特性,包括数据类型、运算符、控制语句等。

其次是嵌入式系统开发中常用的硬件知识,例如芯片架构、外设接口等。

还需要了解一些常用的嵌入式开发工具,如编译器、调试器等。

第四章:选择适合的开发平台嵌入式系统开发需要选择适合的开发平台。

常见的开发平台包括单片机、嵌入式Linux系统、实时操作系统等。

根据具体应用需求选择合适的开发平台,同时要考虑开发工具的可用性和便利性。

第五章:编写嵌入式系统应用程序使用C语言进行嵌入式系统开发的核心是编写应用程序。

在编写应用程序时,需要根据系统需求设计合适的算法和数据结构,实现功能模块。

同时要考虑资源的合理利用和性能的优化,以保证系统的稳定运行。

第六章:调试和测试嵌入式系统开发过程中,调试和测试是至关重要的环节。

通过调试和测试可以发现和解决系统中的问题,保证系统的可靠性和稳定性。

在调试和测试过程中,可以使用一些专业的嵌入式开发工具,如JTAG、Logic Analyzer等,来辅助分析和调试。

第七章:性能优化嵌入式系统通常具有资源受限的特点,因此性能优化是非常重要的。

通过代码优化、算法改进、资源管理等手段,可以提高系统的实时性、运行速度和功耗效率。

在进行性能优化时,需要仔细分析系统的瓶颈和热点,针对性地进行优化操作。

嵌入式系统设计的基础知识

嵌入式系统设计的基础知识嵌入式系统是指嵌入到其他设备中,完成特定功能的计算机系统。

常见的嵌入式系统包括智能手机、数字电视机顶盒、汽车电子、工业自动化等领域。

因为嵌入式系统通常空间、能耗、成本要求都非常严苛,所以它们和通用计算机相比有很多不同之处。

本文将从嵌入式系统设计的角度,介绍嵌入式系统设计的基础知识。

一、嵌入式系统的硬件设计基础知识嵌入式系统的硬件设计是指对嵌入式系统的各个硬件组成部分进行设计、选型、集成、排布的过程。

嵌入式系统的硬件设计必须考虑以下几个方面。

1.芯片选型单片机(MCU)是嵌入式系统常用的芯片,由于嵌入式系统对芯片的集成度要求很高,常用的MCU都集成了很多模拟和数字外设如模数转换器(ADC)、通用异步收发器(UART)、同步串行收发器(SPI)、I2C接口等,可以很方便地与外部设备进行通讯。

当然,其他器件如FPGA、DSP等也可以作为嵌入式系统的芯片。

2.电源选择嵌入式系统的电源选择不仅要考虑芯片的输入电压特性,还要考虑嵌入式系统的整体功耗和稳定性,特别是对于多电压需求的系统更要注意电源的设计。

3.尺寸和布局嵌入式系统的尺寸和布局既要考虑外部尺寸限制,又要考虑内部线路的布局和信号的传输特性。

因为一旦系统原型被制作出来,改动就会变得十分困难,这就要求硬件设计人员对布局的精确把握和对参数的准确计算。

4.时钟电路嵌入式系统内的各个部件需要同步,通常需要一个精确的时钟电路驱动。

在时钟电路的设计中,要考虑功耗、抗干扰性等因素。

二、嵌入式系统的软件设计基础知识嵌入式系统的软件设计是指嵌入式系统的固件设计、操作系统选择和软件架构的设计等多个方面。

在开发嵌入式系统时,软件设计是非常重要的一个环节。

1.固件设计在开发嵌入式系统时,需要编写固件程序,这是嵌入式系统的基础软件。

固件程序通常被编写在C语言或某些汇编语言中。

编写固件程序时,需要考虑程序的规模、执行速度、可维护性、代码安全性等多重因素。

嵌入式系统——基础知识

嵌入式系统——基础知识操作系统OS控制和管理计算机软硬件资源,合理组织计算机工作流程,方便用户使用计算机的系统软件。

可将OS看成是应用程序与硬件间的接口或虚拟机。

OS功能:进程管理、存储管理、文件管理、设备管理、网络和通信管理等。

嵌入式操作系统EOS运行在嵌入式硬件平台上,对整个系统及其所操作的部件装置等资源进行统一协调、指挥和控制的系统软件。

EOS特点:微型化、可裁剪性、实时性、高可靠性、易移植性重点关注:高实时性、硬件相关依赖性、软件固化、应用专用性、网络功能。

实时操作系统TROS能使计算机及时响应外部事件请求,并能及时控制所有实时设备与实时任务协调运行,且能在规定时间内完成事件处理的OS。

RTOS基本要求:1、逻辑功能正确:RTOS的计算必须产生正确的结果;2、时间正确:RTOS的计算必须在预定的周期内完成。

RTOS应满足条件:1、多任务系统;2、任务的切换时间应与系统中的任务书无关;3、中断延时的时间可预知并尽可能短。

无论在什么情况下,OS完成任务所需的时间应该是在程序设计时就可预知的。

嵌入式实时操作系统ERTOS用于嵌入式系统,对系统资源和多个任务进行管理,且具有高可靠性、良好可裁剪性等优良性能的,为应用程序提供运行平台和实时服务的微型系统软件。

ERTOS最重要的三项服务:1、多任务管理2、内存管理3、外围资源管理嵌入式微处理器(特点)1、对实时多任务OS有很强的支持能力;2、具有功能很强的存储区域保护功能;3、处理器结构可扩展;4、低功耗;微处理器主要发展方向:小体积、高性能、低功耗微处理器分类:MCU、MPU、DSP、SOC嵌入式系统发展方向1、嵌入式开发是一项系统工程,嵌入式系统厂商不仅要提供嵌入式软硬件系统本身,还需要提供强大的硬件开发工具与软件支持包;2、网络化、信息化的要求随着因特网技术的成熟、宽带的提高而日益提高,使得以往单一功能的设备功能不再单一,结构更加复杂;3、网络互连成为必然趋势(IEEE1394、USB、CAN、Bluetooth等网络接口);4、精简系统内核、算法、降低功耗和软硬件成本;5、提供友好的多媒体人机界面。

嵌入式系统相关知识点总结

嵌入式系统相关知识点总结嵌入式系统(Embedded Systems)是一种专门设计和用途的计算机系统,用于控制设备和机器的各个方面,通常被嵌入到所控制的设备中。

嵌入式系统是一个开放的领域,涵盖了面向硬件和软件的多个方面。

在本文中,我将总结一些与嵌入式系统相关的重要知识点。

一、嵌入式系统的基础知识:1.什么是嵌入式系统:嵌入式系统是一种专门设计和用途的计算机系统,被嵌入到所控制的设备中。

2.嵌入式系统的特点:实时性、可靠性、功耗低、体积小、成本低、资源有限等。

3.嵌入式系统的分类:实时嵌入式系统、网络嵌入式系统、移动嵌入式系统、无线嵌入式系统等。

4.嵌入式系统的组成:硬件平台(处理器、内存、输入输出接口等)和软件平台(操作系统、驱动程序等)。

二、嵌入式系统的硬件知识:1. 存储器:RAM(随机访问存储器)、ROM(只读存储器)、Flash memory(闪存)等。

2.处理器:常见的处理器包括ARM、MIPS、x86等,需要根据应用需求选择适合的处理器。

3.输入输出接口:串口、并口、USB、以太网等用于与外设通信。

4.性能优化:资源有限的嵌入式系统需要优化性能和资源利用,例如使用中断处理、多任务处理等技术。

三、嵌入式系统的软件知识:1. 操作系统(OS):嵌入式系统通常使用实时操作系统(RTOS),如FreeRTOS、Linux、VxWorks等,用于管理任务、内存、进程和资源。

2.设备驱动程序:用于控制和管理硬件设备,例如串口驱动、触摸屏驱动等。

3.编程语言:C/C++是嵌入式系统开发中常用的编程语言,还有汇编语言适用于对性能要求较高的关键模块。

4.软件开发工具:编译器、调试器、仿真器等用于嵌入式软件的开发和调试。

四、嵌入式系统的开发流程:1.系统需求分析:明确系统的功能、性能、成本等需求,并进行需求分析和规划。

2.硬件设计与开发:选择合适的硬件平台,设计硬件电路,并进行原型制作和测试。

3.软件设计与开发:进行软件系统的设计和开发,包括操作系统选择、驱动程序编写、应用程序开发等。

嵌入式系统基础知识

8

通用计算机与嵌入式系统对比

特征 形式和类型

•

通用计算机 看得见的计算机。 按其体系结构、运算速度 和结构规模等因素分为大 、中、小型机和微机。 通用处理器、标准总线和 外设。 软件和硬件相对独立。

•

嵌入式系统

看不见的计算机。 形式多样,应用领域广泛 ,按应用来分。

组成

•

•

面向应用的嵌入式微处 理器,总线和外部接口 多集成在处理器内部。 软件与硬件是紧密集成 在一起的。 采用交叉开发方式,开 发平台一般是通用计算 机,运行 平台是嵌入 式系统。 大部分不能再编程

2、Windows CE

17

1.3 嵌入式操作系统举例

1.3.2 开源版嵌入式操作系统 嵌入式Linux(Embedded Linux)

具有低成本、多种硬件平台支持、优异的性能和良好的 网络支持等优点 uCLinux、RT-Linux、Embedix、 XLinux、PoketLinux、红旗嵌入式Linux等

开发方式

•

开发平台和运行平台都是 通用计算机

•

二次开发性

•

应用程序可重新编制

•

1.1 嵌入式系统概述

1.1.3 嵌入式系统的发展 嵌入式系统发展的4个阶段:

① 以单芯片为核心的可编程控制器形式的系统 ② 以嵌入式CPU为基础、以简单操作系统为核心的嵌入式

系统 ③ 以嵌入式操作系统为标志的嵌入式系统 ④ 以Internet为标志的嵌入式系统

3

第1章 嵌入式系统基础知识

本章课程:

1.1 嵌入式系统概述 1.2 嵌入式系统的组成 1.3 嵌入式操作系统举例 1.4 嵌入式系统开发概述 1.5 小结

嵌入式系统设计课程大纲

嵌入式系统设计课程大纲第一章:课程介绍(100字)本章主要介绍嵌入式系统设计课程的目的、重要性以及学习该课程的基本要求。

通过本章的学习,学生将对嵌入式系统设计的概念有一个明确的认知。

第二章:嵌入式系统基础知识(200字)本章将重点介绍嵌入式系统的基本概念、发展历程以及其在各个领域中的应用。

同时,将深入讲解嵌入式系统设计所需的硬件和软件基础知识,包括单片机、传感器、通信接口等概念和原理。

第三章:嵌入式系统设计流程(250字)本章将详细介绍嵌入式系统设计的流程及其各个环节的具体要求。

包括需求分析、系统设计、软硬件开发、测试调试等阶段,以及各个阶段所需的工具和方法。

第四章:嵌入式系统开发工具和环境(200字)本章将介绍常用的嵌入式系统开发工具和环境,包括集成开发环境(IDE)、仿真器、调试器等。

学生将学习如何选择和使用适合项目需求的工具,并掌握相关的调试技巧。

第五章:嵌入式系统通信协议(150字)本章将介绍嵌入式系统中常用的通信协议,包括串口通信、SPI、I2C、CAN等。

学生将学习各种通信协议的原理、特点以及在实际项目中的应用场景。

第六章:嵌入式系统电源管理(150字)本章将重点介绍嵌入式系统中电源管理的原理和方法。

学生将学习如何有效地管理系统电源,以提高系统的稳定性和节能效果。

第七章:嵌入式系统安全性设计(200字)本章将介绍嵌入式系统安全性设计的重要性以及相关的技术要求。

学生将学习如何设计安全可靠的嵌入式系统,包括访问控制、数据加密等方面的知识。

第八章:嵌入式操作系统(150字)本章将介绍常用的嵌入式操作系统,包括实时操作系统(RTOS)、Linux嵌入式系统等。

学生将学习这些操作系统的原理、特点和适用场景,以及如何进行系统移植和调试。

第九章:嵌入式系统性能优化(200字)本章将讲解如何对嵌入式系统进行性能优化,包括系统响应时间的优化、功耗优化以及资源利用率的提高。

学生将学习相关的优化技术和方法,并通过实践项目进行实际应用。

嵌入式系统的基础知识

嵌入式系统的基础知识嵌入式系统是一种特殊类型的计算机系统,它的设计是为了执行特定的功能,例如:控制家电、汽车系统,医疗设备、工业控制等。

它们通常集成了控制器、传感器、执行器等电子元件与软件,并且运行在嵌入式操作系统下。

在这篇文章中,我们将探讨嵌入式系统的基本知识。

一. 嵌入式系统的构成嵌入式系统的构成主要包含三部分:硬件、软件和操作系统。

硬件:主要由中央处理器(CPU)、存储器、输入输出(IO)接口、通信接口、传感器、执行器等组成。

软件:它们是嵌入式系统中最重要的部分。

在嵌入式系统中,软件被分为两部分:应用软件和系统软件,其中,应用软件是用来实现用户需求的,而系统软件则是用来管理、控制硬件并协调应用软件的。

操作系统:嵌入式操作系统通常是针对特定应用的,尺寸小、运行速度快,它们与通用操作系统(如Windows或Linux)不同,通常不提供完整的文件系统和图形用户界面(GUI)。

二. 嵌入式系统的特点1. 实时性要求高嵌入式系统通常需要在非常短的时间内完成各种操作。

举例来说,医疗设备必须在极短的时间内提供准确的心电图,汽车防抱死刹车系统必须能够在几毫秒内对车轮做出反应。

实时性是嵌入式系统在市场上成功的关键。

2. 多种输入输出接口输入输出接口是嵌入式系统最重要的组成部分之一,因为这些接口是用来控制硬件和与外部世界联系的。

嵌入式系统通常具有不同类型的接口,例如:数字和模拟输入输出,以及通信接口如UART、I2C、SPI和网络接口等。

3. 尺寸小、功耗低由于嵌入式系统通常被集成到产品中,所以它们的尺寸必须小,并且需要耗电少以保证长时间的运行。

4. 稳定性高嵌入式系统通常需要持续运行数年,同时必须保证稳定性和可靠性,因为它们的系统组成部分与生产过程紧密相关,而崩溃会导致成本大幅增加。

三. 嵌入式系统的设计过程1. 需求分析在嵌入式系统的开发过程中,需求分析是最重要的阶段,因为只有正确地定义了所需求,才能有效地设计嵌入式系统。

嵌入式系统基础知识

嵌入式系统基础知识在当今科技飞速发展的时代,嵌入式系统已经成为了我们生活中无处不在的一部分。

从智能手机、智能家居设备到汽车电子、医疗设备等,嵌入式系统的应用几乎涵盖了各个领域。

那么,什么是嵌入式系统呢?它又有着怎样的特点和构成呢?接下来,让我们一起走进嵌入式系统的世界,来了解一下它的基础知识。

嵌入式系统,简单来说,就是一种嵌入到其他设备或系统中的专用计算机系统。

它的主要目的是为了控制、监测或执行特定的任务,而不是像我们常见的个人电脑那样进行通用的计算和数据处理。

嵌入式系统具有以下几个显著的特点。

首先是专用性。

它是为特定的应用而设计的,具有明确的功能和性能要求。

比如,汽车中的电子控制单元(ECU)就是专门用于控制发动机、变速器等部件的工作,其设计和功能都是围绕着汽车的运行和性能优化展开的。

其次是实时性。

在很多应用场景中,嵌入式系统需要在规定的时间内完成特定的任务。

例如,飞机的飞行控制系统必须能够实时响应飞行员的操作指令,确保飞行的安全和稳定。

再者是低功耗。

由于很多嵌入式设备是依靠电池供电的,如便携式医疗设备、智能手表等,因此降低功耗以延长电池寿命就显得至关重要。

然后是可靠性和稳定性。

嵌入式系统通常运行在较为恶劣的环境中,需要长时间稳定工作,不能出现故障或错误。

此外,嵌入式系统的体积通常较小,以适应设备的空间限制。

一个典型的嵌入式系统通常由硬件和软件两大部分组成。

硬件方面,包括处理器、存储器、输入输出设备等。

处理器是嵌入式系统的核心,负责执行指令和处理数据。

常见的嵌入式处理器有微控制器(MCU)和数字信号处理器(DSP)等。

存储器用于存储程序和数据,包括只读存储器(ROM)、随机存取存储器(RAM)和闪存(Flash)等。

输入输出设备则用于与外界进行交互,如传感器、按键、显示屏、通信接口等。

软件方面,主要包括操作系统、驱动程序和应用程序。

操作系统是管理嵌入式系统资源的核心软件,如实时操作系统(RTOS),它能够确保系统的实时性和可靠性。

嵌入式系统基础知识

嵌入式系统基础知识嵌入式系统是指将计算机系统嵌入到特定的物理设备或系统中,以实现特定功能的计算机系统。

它在现代社会中得到广泛应用,如智能手机、家用电器、汽车控制系统等。

在这篇文章中,我们将介绍嵌入式系统的基础知识。

一、什么是嵌入式系统?嵌入式系统是指将计算机硬件和软件嵌入到特定的物理设备中,以实现特定功能的计算机系统。

与传统的通用计算机系统不同,嵌入式系统的硬件资源有限且固定,软件运行在实时环境下,并需要满足特定的功耗和性能要求。

二、嵌入式系统的组成1. 处理器:嵌入式系统的处理器通常是一种低功耗、高性能的专用芯片,如ARM、MIPS等。

它们具有较小的封装和低功耗特性,非常适用于嵌入式系统。

2. 存储器:嵌入式系统通常包括闪存、RAM等类型的存储器。

闪存用于存储程序代码和数据,RAM用于临时存储数据。

3. 输入/输出设备:嵌入式系统通常具备各种输入/输出设备,如触摸屏、键盘、麦克风、扬声器等。

这些设备可以实现与用户的交互和数据的输入输出。

4. 操作系统:嵌入式系统通常运行一个专门为其开发的实时操作系统,如嵌入式Linux、VxWorks等。

这些操作系统能够保证实时性和稳定性,并提供丰富的驱动和软件支持。

5. 开发工具:嵌入式系统的开发通常需要使用特定的开发工具,如编译器、调试器、仿真器等。

这些工具可以帮助开发人员进行代码的编写、调试以及性能评估。

三、嵌入式系统的特点1. 实时性:嵌入式系统通常需要在给定的时间要求内响应用户的操作或者产生相应的输出。

因此,实时性是嵌入式系统的重要特点之一。

2. 硬件资源有限:嵌入式系统的硬件资源有限且固定,这意味着开发人员需要在有限的资源下设计和实现功能。

3. 低功耗:嵌入式系统通常需要长时间运行,并且对电池寿命有较高的要求。

因此,低功耗是设计嵌入式系统时需要考虑的重要因素。

4. 可靠性:嵌入式系统通常运行在一些关键的应用领域,如医疗设备、航空航天等。

因此,嵌入式系统需要具备高度的可靠性和安全性。

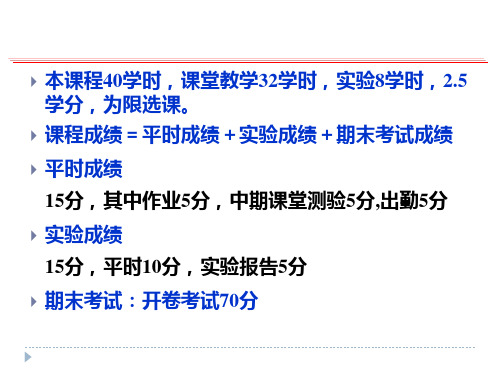

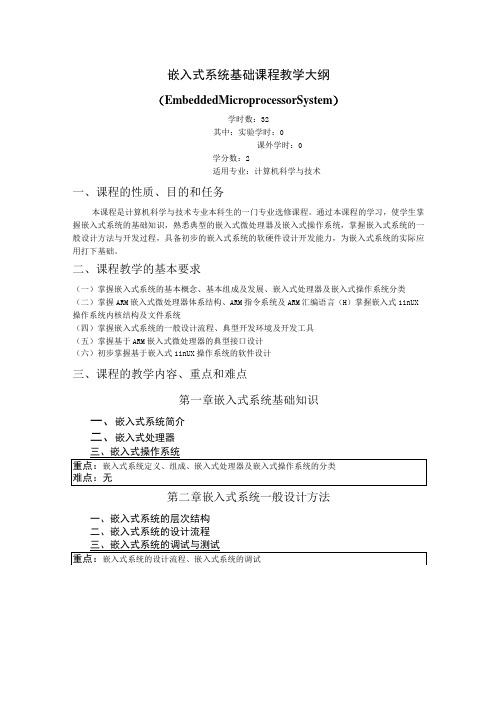

《嵌入式系统基础》课程教学大纲

嵌入式系统基础课程教学大纲(EmbeddedMicroprocessorSystem)学时数:32其中:实验学时:0课外学时:0学分数:2适用专业:计算机科学与技术一、课程的性质、目的和任务本课程是计算机科学与技术专业本科生的一门专业选修课程。

通过本课程的学习,使学生掌握嵌入式系统的基础知识,熟悉典型的嵌入式微处理器及嵌入式操作系统,掌握嵌入式系统的一般设计方法与开发过程,具备初步的嵌入式系统的软硬件设计开发能力,为嵌入式系统的实际应用打下基础。

二、课程教学的基本要求(一)掌握嵌入式系统的基本概念、基本组成及发展、嵌入式处理器及嵌入式操作系统分类(二)掌握ARM嵌入式微处理器体系结构、ARM指令系统及ARM汇编语言(H)掌握嵌入式1inUX 操作系统内核结构及文件系统(四)掌握嵌入式系统的一般设计流程、典型开发环境及开发工具(五)掌握基于ARM嵌入式微处理器的典型接口设计(六)初步掌握基于嵌入式1inUX操作系统的软件设计三、课程的教学内容、重点和难点第一章嵌入式系统基础知识一、嵌入式系统简介二、嵌入式处理器第二章嵌入式系统一般设计方法一、嵌入式系统的层次结构二、嵌入式系统的设计流程第三章ARM处理器体系结构及指令系统一、ARM微处理器的体系结构二、指令系统三、基于ARM体系的汇编语言程序设计第四章基于ARM处理器的硬件平台设计一、基于微处理器的嵌入式系统的硬件设计二、存储系统的分析与设计三、通用I/O接口的设计第五章嵌入式1inux操作系统一、1i1IUX及其应用二、嵌入式1inux内核三、嵌入式1inUX文件系统第六章嵌入式1inux系统的Boot1oader设计一、Boot1oader的基本概念二、Boot1oader的具体实现重点:Boot1oader的基本概念难点:BOOt1Oader的具体实现第七章嵌入式1inux程序设计基础一、嵌入式1inUX开发基础二、1inUX的常用工具三、嵌入式1inUX操作系统的开发工具四、交叉开发环境重点:嵌入式1inUX操作系统的开发工具、难点:交叉开发环境第八章嵌入式1inux系统的驱动开发一、1inUX下的设备驱动程序简介二、设备驱动程序的开发过程三、典型设备驱动程序设计分析第九章嵌入式网络程序设计一、嵌入式以太网基础知识二、以太网接口设计三、1in1IX网络编程实现重点:以太网接口设计、1inUX网络编程实现难点:1inUX网络编程实现第十章嵌入式1inux图形用户界面编程一、1inux图形开发基础二、嵌入式1inIIX图形用户界面简介四、课程各教学环节要求(一)作业根据课程学习需要,安排适当课外作业。

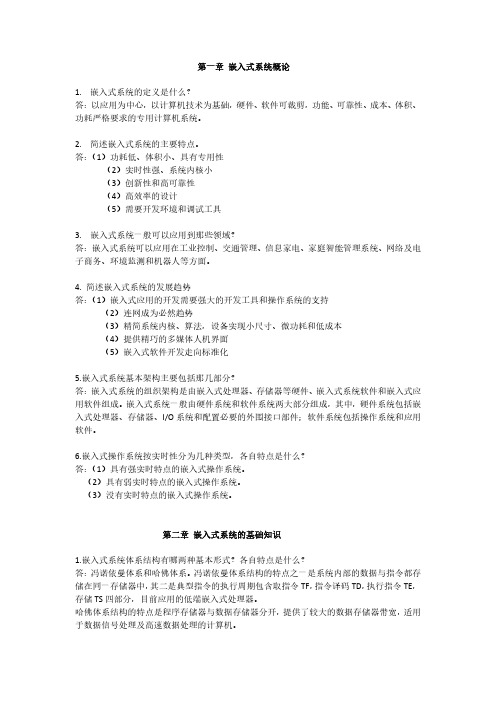

嵌入式系统设计教程(第2版)简答题答案.pdf

第一章嵌入式系统概论1.嵌入式系统的定义是什么?答:以应用为中心,以计算机技术为基础,硬件、软件可裁剪,功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

2.简述嵌入式系统的主要特点。

答:(1)功耗低、体积小、具有专用性(2)实时性强、系统内核小(3)创新性和高可靠性(4)高效率的设计(5)需要开发环境和调试工具3. 嵌入式系统一般可以应用到那些领域?答:嵌入式系统可以应用在工业控制、交通管理、信息家电、家庭智能管理系统、网络及电子商务、环境监测和机器人等方面。

4. 简述嵌入式系统的发展趋势答:(1)嵌入式应用的开发需要强大的开发工具和操作系统的支持(2)连网成为必然趋势(3)精简系统内核、算法,设备实现小尺寸、微功耗和低成本(4)提供精巧的多媒体人机界面(5)嵌入式软件开发走向标准化5.嵌入式系统基本架构主要包括那几部分?答:嵌入式系统的组织架构是由嵌入式处理器、存储器等硬件、嵌入式系统软件和嵌入式应用软件组成。

嵌入式系统一般由硬件系统和软件系统两大部分组成,其中,硬件系统包括嵌入式处理器、存储器、I/O系统和配置必要的外围接口部件;软件系统包括操作系统和应用软件。

6.嵌入式操作系统按实时性分为几种类型,各自特点是什么?答:(1)具有强实时特点的嵌入式操作系统。

(2)具有弱实时特点的嵌入式操作系统。

(3)没有实时特点的嵌入式操作系统。

第二章嵌入式系统的基础知识1.嵌入式系统体系结构有哪两种基本形式?各自特点是什么?答:冯诺依曼体系和哈佛体系。

冯诺依曼体系结构的特点之一是系统内部的数据与指令都存储在同一存储器中,其二是典型指令的执行周期包含取指令TF,指令译码TD,执行指令TE,存储TS四部分,目前应用的低端嵌入式处理器。

哈佛体系结构的特点是程序存储器与数据存储器分开,提供了较大的数据存储器带宽,适用于数据信号处理及高速数据处理的计算机。

2.在嵌入式系统中采用了哪些先进技术?答:(1)流水线技术(2)超标量执行(3)总线和总线桥3.简述基于ARM架构的总线形式答:ARM架构总线具有支持32位数据传输和32位寻址的能力,通过先进微控制器总线架构AMBA支持将CPU、存储器和外围都制作在同一个系统板中。

嵌入式系统及应用-Chapter02-嵌入式硬件系统

输入/输出接口和设备

• 嵌入式系统的大多数输入/输出接口和部分 设备已经集成在嵌入式微处理器中。 • 输入/输出接口主要有中断控制器、DMA、 串行和并行接口等,设备主要有定时器 (Timers)、计数器(counters)、看门 狗(watchdog timers)、RTC、UARTs、 PWM(Pulse width modulator)、AD/DA、 显示器、键盘和网络等。

由硬件完成部分软件功能,硬件复 杂性增加,芯片成本高

减少代码尺寸,增加指令的执行周 期数 大量的混杂型指令集,有简单快速 的指令,也有复杂的多周期指令, 符合HLL(high level language) 硬件完成 复杂的寻址模式,支持内存到内存 寻址 微码 寄存器较少

由软件完成部分硬件功能,软件复 杂性增加,芯片成本低

• 嵌入式系统的存储器包括主存和外存。

• 大多数嵌入式系统的代码和数据都存储在处 理器可直接访问的存储空间即主存中。

• 系统上电后在主存中的代码直接运行。主存 储器的特点是速度快,一般采用ROM、EPROM、 Nor Flash、SRAM、DRAM等存储器件。

存储器

• 目前有些嵌入式系统除了主存外,还有外 存。外存是处理器不能直接访问的存储器, 用来存放各种信息,相对主存而言具有价 格低、容量大的特点。 • 在嵌入式系统中一般不采用硬盘而采用电 子盘做外存,电子盘的主要种类有 NandFlash、 SD (Secure Digital)卡、 CompactFlash、SmartMedia、Memory Stick、MultiMediaCard、、 DOC(Disk On Chip)等。

Total Embedded Control Market Shipments by Type

嵌入式系统基础知识

处理器

嵌入式系统软件平台

在设计简单的应用程序时,可以不使用操作系 统,但在设计较复杂的程序时,可能就需要一个 操作系统来管理和控制存储器、多任务和各种 资源等. 实时嵌入式系统其最大特点就是程序的执行具 有确定性。μC/OS和μC Linux是广泛应用的实 时嵌入式操作系统,而WindowsCE2.0就是一个 多任务分时系统。

2) 单片机(嵌入式应用)属于专用计算机,主

要用于智能仪表及传感器、智能家电、智能办公 设备、汽车及军事电子设备等系统。

单片机是应工业测控的需要而诞生的,它的结构与指令功能 都是按照工业控制要求设计的,故又称单片微控制器。

MCU (Microcontroller Unit)。

单片机特点: (1)体积小,重量轻;

1

嵌入式系统的定义及体系结构 2 嵌入式系统的应用领域 3 什么是单片机

4 单片机的基本组成

5 嵌入式系统开发流程

应用场合

汽车电子 消费电子 工业控制

网络应用 无线通讯

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005

家用电器:洗碗机,洗衣机,电 视。。。。 手持电子:蓝牙耳机,游戏机,PDA 娱乐产品:数码音乐,CD,DC,DV 计算机外围:LCD,Mouse,Keyboard

嵌入式linux课程大纲

嵌入式linux课程大纲第一章:引言嵌入式系统概述嵌入式Linux的优势和特点学习目标和课程安排第二章:Linux基础知识2.1 Linux操作系统简介- Linux的起源和发展- Linux的基本组成和特点- 嵌入式Linux的应用领域2.2 Linux内核与设备驱动- Linux内核的基本结构和模块- 设备驱动的基本概念和分类- 设备驱动的开发与调试2.3 Linux系统编程- Linux系统调用和API- 进程管理和线程库- 文件操作和IO控制第三章:嵌入式系统硬件基础3.1 嵌入式系统硬件结构- CPU和内存- 总线和外设- 接口和通信3.2 嵌入式系统开发板介绍- 嵌入式开发板的分类和选择- 开发板的基本组成和功能- 开发板与嵌入式Linux的配合使用3.3 嵌入式系统调试技术- 调试工具和方法- 嵌入式系统的调试流程- 常见问题和解决方法第四章:嵌入式Linux系统构建4.1 嵌入式Linux系统概述- 嵌入式Linux系统的构成和特点- 嵌入式Linux系统的架构和分层4.2 嵌入式Linux系统的交叉编译- 交叉编译环境的搭建- 编译器和工具链的选择- 交叉编译的基本过程和注意事项4.3 嵌入式Linux的文件系统- 文件系统的基本概念和分类- 常用嵌入式Linux文件系统的介绍 - 文件系统的制作和定制第五章:嵌入式应用开发5.1 嵌入式应用程序设计- 嵌入式应用程序的特点和需求- 嵌入式应用程序的开发流程- 常用的开发工具和集成环境5.2 嵌入式网络应用开发- 嵌入式网络编程模型- 嵌入式网络应用的开发步骤- 嵌入式网络应用实例分析5.3 嵌入式图形界面开发- 嵌入式图形界面的概述- 嵌入式图形界面的开发工具和库- 基于Qt的嵌入式图形界面开发第六章:嵌入式Linux系统优化与安全6.1 嵌入式系统性能优化- 嵌入式系统性能优化的重要性- 嵌入式系统性能优化的方法和工具 - 常见性能问题的分析和解决6.2 嵌入式系统安全设计- 嵌入式系统安全性的重要性- 嵌入式系统的安全设计原则- 嵌入式系统的安全加固措施第七章:实践项目7.1 项目需求分析- 了解项目背景和需求- 提取关键功能和要求7.2 系统设计与实施- 系统架构设计- 软硬件选择和配置- 功能模块设计和编码7.3 系统测试与优化- 系统功能测试- 性能测试和优化- 安全测试和漏洞修复第八章:总结与展望课程学习总结嵌入式Linux行业发展前景进一步学习和研究的建议本大纲旨在全面介绍嵌入式Linux的基础知识和开发技术,帮助学习者快速入门并掌握嵌入式Linux系统的开发和应用。

嵌入式系统知识点总结

嵌入式系统知识点总结1.什么是嵌入式系统?嵌入式系统是以应用为中心,以计算机技术为基础,采用可裁剪软硬件,适用于对功能、功耗、体积、大小可靠性等有严格要求的专用计算机系统。

2.嵌入式计算机系统同通用型计算机系统的区别?1)嵌入式系统通常是面向特定应用,而通用pc机则需要支持大量的、需求多样的应用程序2)嵌入式系统的软硬件必修高效的设计,量体裁衣、去除冗余,而通用pc对软硬件要求没有嵌入式系统那么高。

3)嵌入式系统为了提高速度和可靠性,一般将软件固化在芯片或者单片机中,而通用pc一般将软件放入存储器中。

4)嵌入式系统不具备自主开发能力,通用pc拥有强大的开发能力。

5)嵌入式系统是面向特定应用的,它的升级换代也与具体产品同步的进行。

3.嵌入式系统组成?嵌入式处理器、嵌入式外围设备、嵌入式应用软件、嵌入式操作系统。

4.ARM是什么?Arm(advanced RISC Machine)的三层含义:1)一个公司名称。

2)一种技术名称3)是一种微处理器的通称。

5.嵌入式处理器有哪些?MIPS、Power PC、SH处理器、ARM6.ARM处理器的特点有哪些?1)体积小、低功耗、成本低、性能高2)大量使用寄存器3)支持Thumb (16位)和ARM(32位)双指令集4)指令长度是固定的5)寻址方式灵活简单7.嵌入式处理器选择时考虑的主要因素?1)处理性能(如时钟频率、寄存器大小等)2)技术指标(外围设备、支持芯片等)3)功耗(特别是手持设备等消费类电子产品)4)软件支持工具5)是否内置调试工具6)供应商是否提供评估板8.ARM-XScale-PXA270三者之间的区别于联系?ARM是一种微处理器的通称;XScale处理器是基于ARMv5TE体系结构的解决方案,是一款高性能、高性价比、低功耗的处理器;PXA270则是采用Xscale内核(微结构体系框架),集成了许多常用的外围接口,是一款高性能、低功耗、功能强大的嵌入式应用处理器产品。

嵌入式系统基础知识

嵌入式系统基础知识一、内容概述嵌入式系统基础知识是电子工程、计算机科学和自动化领域的重要部分。

本文旨在全面介绍嵌入式系统的基本概念、主要组成部分、应用领域以及发展趋势。

文章首先定义了嵌入式系统的含义和特性,然后概述了其硬件和软件组成部分,包括微处理器、存储器、输入输出接口、操作系统、编程语言等。

文章将探讨嵌入式系统的应用领域,如消费电子、工业控制、汽车电子、医疗设备等。

文章还将概述当前嵌入式系统的发展趋势,如物联网、人工智能、云计算等技术的融合,以及面临的挑战,如功耗、实时性、安全性等问题。

读者可以全面了解嵌入式系统的基础知识,为深入学习和实践打下坚实的基础。

1. 嵌入式系统的定义和发展概述嵌入式系统是一种专用计算机系统,它通常被设计为执行特定的功能或任务,如控制机械设备、监视环境、数据处理或网络服务。

嵌入式系统与通用计算机系统的主要区别在于它们专为特定应用定制,并在广泛领域中进行应用。

嵌入式系统通常被嵌入在更大的设备或系统中,如汽车、医疗设备、航空航天设备、家用电器等。

它们具有低功耗、高性能、高可靠性和实时响应等特性。

随着物联网(IoT)、人工智能(AI)和大数据技术的快速发展,嵌入式系统正成为实现这些技术的关键部分。

嵌入式系统融合了计算机技术、电子技术和传感器技术,通过简化软硬件功能以适应严格的性能和尺寸要求,同时提高能效和可靠性。

它们不仅在工业自动化和消费电子产品领域得到了广泛应用,还渗透到了智能城市、智能交通系统等多个新兴领域中。

嵌入式系统经历了多年的发展,从早期的微控制器到现代的智能嵌入式系统,其功能和性能得到了极大的提升。

随着技术的进步,嵌入式系统的应用领域将继续扩大,其重要性也将不断提升。

2. 嵌入式系统的重要性及其应用领域随着科技的飞速发展,嵌入式系统已经深入到社会的各个领域,成为现代信息社会不可或缺的重要组成部分。

嵌入式系统的重要性主要体现在以下几个方面:嵌入式系统作为信息技术的重要分支,在推动工业自动化、智能化进程中发挥着关键作用。

嵌入式系统基础知识总结

嵌入式系统基础知识总结嵌入式系统基础知识总结嵌入式系统是用来控制或者监视机器、装置、工厂等大规模设备的系统。

以下是关于嵌入式系统基础知识总结,欢迎大家认真阅读!1、嵌入式系统的定义(1)定义:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

(2)嵌入式系统发展的4个阶段:无操作系统阶段、简单操作系统阶段、实时操作系统阶段、面向Internet阶段。

(3)知识产权核(IP核):具有知识产权的、功能具体、接口规范、可在多个集成电路设计中重复使用的功能模块,是实现系统芯片(SOC)的基本构件。

(4)IP核模块有行为、结构和物理3级不同程度的设计,对应描述功能行为的不同可以分为三类:软核、固核、硬核。

2、嵌入式系统的组成包含:硬件层、中间层、系统软件层和应用软件层(1)硬件层:嵌入式微处理器、存储器、通用设备接口和I/O接口。

嵌入式核心模块=微处理器+电源电路+时钟电路+存储器Cache:位于主存和嵌入式微处理器内核之间,存放的是最近一段时间微处理器使用最多的程序代码和数据。

它的主要目标是减小存储器给微处理器内核造成的存储器访问瓶颈,使处理速度更快。

(2)中间层(也称为硬件抽象层HAL或者板级支持包BSP).它将系统上层软件和底层硬件分离开来,使系统上层软件开发人员无需关系底层硬件的具体情况,根据BSP层提供的接口开发即可。

BSP有两个特点:硬件相关性和操作系统相关性。

设计一个完整的BSP需要完成两部分工作:A、嵌入式系统的硬件初始化和BSP功能。

片级初始化:纯硬件的初始化过程,把嵌入式微处理器从上电的默认状态逐步设置成系统所要求的工作状态。

板级初始化:包含软硬件两部分在内的初始化过程,为随后的系统初始化和应用程序建立硬件和软件的运行环境。

系统级初始化:以软件为主的初始化过程,进行操作系统的初始化。

B、设计硬件相关的设备驱动。

(3)系统软件层:由RTOS、文件系统、GUI、网络系统及通用组件模块组成。

嵌入式系统基础知识

嵌入式系统基础知识嵌入式系统这一概念已经不再只是计算机专业人士的专属领域,而是面向更广泛的学科和行业。

它涉及到硬件和软件,需要对多学科进行深入的学习和了解。

本文就嵌入式系统的基础知识进行探讨,包括硬件、软件、应用领域等方面。

一、嵌入式系统的概念和特点嵌入式系统是一种集成了计算机硬件和软件的计算机系统,其目的是完成特定任务。

相对于通用计算机而言,嵌入式系统更加具有针对性和专业性。

其特点主要有以下几个方面:1. 任务导向:嵌入式系统的设计和开发是基于特定的任务和应用领域,比如汽车电子、医疗设备、智能家居等等。

因此在设计过程中,需要深入了解任务和所处领域的特点和需求。

2. 实时性:嵌入式系统往往要求具备很高的实时性,即需要在极短的时间内完成任务和数据处理,例如航空航天、军事等领域。

3. 资源受限:相对于通用计算机,嵌入式系统在硬件和软件资源方面都有所限制,需要针对性地进行优化。

在资源方面受限的情况下,嵌入式系统需要同时兼顾高效性和低能耗性。

4. 协作性:嵌入式系统通常是由多个组成部分构成,比如传感器、控制器、数据存储等等,这些部分需要协同完成任务。

5. 可靠性:嵌入式系统往往要求具备很高的可靠性和安全性,一旦发生故障,可能会带来重大的后果。

二、嵌入式系统的硬件基础嵌入式系统的硬件基础可以分为以下几个方面:1. 处理器芯片:是嵌入式系统最核心的部件,可以进行数据处理和控制操作。

2. 存储设备:包括闪存和RAM等,其中闪存用于存储程序,RAM用于存储数据。

3. 输入输出设备:包括显示器、键盘、鼠标、摄像头、传感器等,通过这些设备实现用户和系统的交互。

4. 通信模块:可以连接互联网、局域网或其他嵌入式系统,实现数据的传输和共享。

5. 电源系统:嵌入式系统需要用电才能正常工作,电源系统需要提供稳定的电压和电流。

6. 外壳:为了保护嵌入式系统免受物理伤害,通常需要加上合适的外壳,同时还可以提升美观性和舒适度。

三、嵌入式系统的软件基础嵌入式软件用于操作嵌入式系统的硬件,实现特定的任务和功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

位于地址A的字包含的半字位于地址A和A+2;

字节 字节 字节 字节 地址A A+1 A+2 A+3

存储器格式

存储器系统有两种映射机制: 小端存储器系统:

在小端格式中,高位数字存放在高位字节 中。因此存储器系统字节0连接到数据线7~0(低位 大端模式 对齐)。 低位地址 高位地址

CISC的主要缺点

指令使用频度不均衡。

高频度使用的指令占据了绝大部分的执行时间,扩充的 复杂指令往往是低频度指令。 VLSI的出现,使单芯片处理机希望采用规整的硬联逻辑 实现,而不希望用微程序,因为微程序的使用反而制约 了速度提高。(微码的存控速度比CPU慢5-10倍)。 复杂指令增加硬件的复杂度,使指令执行周期大大加长, 直接访存次数增多,数据重复利用率低。

总线 高速输入输出接口 输入输出设备 存储器

嵌入式微处理器

每个嵌入式系统至少包含一个嵌入式微处 理器 嵌入式微处理器体系结构可采用冯•诺依曼 (Von Neumann)结构或哈佛(Harvard) 结构

主存储器 地址 数据 地址 CPU 数据存储器 数据 地址 PC CPU

MOV r8,#8 冯•诺依曼结构

大端: 小端:

0xddddddd0

4b cd

73 f6

da 00

0xddddddd0

00 da

嵌入式微处理器的分类

按体系结构的不同可分为五大类

ARM MIPS POWER PC X86 SH系列

500

Units (millions)

400 300 200 100 0 1997 1998 1999 2000

大端存储器系统:

0x12 0x34 0x56 0x78

在大端格式中,高位数字存放在低位字节 低位地址 高位地址 0x78 0x56 0x34 0x12 中。因此存储器系统字节 0连接到数据线31~24(高位

对齐) 。

小端模式

0x12345678字数据的大小端存储方式

大端的数据存放格式

最高有效字节 位于最低地址 最高有效字节的地址 就是该word的地址

Writeback

1

2

3

4

5

6

LDR

MOV AND ORR

Fetch

Decode

Fetch

Execute

Decode Fetch

该例中,用6周期执行了4条指令 指令周期数 (CPI) = 1.5

分支流水线举例

周期

地址

0x8000 0x8004 0x8008 0x8FEC 0x8FF0 0x8FF4

RISC的提出与发展

Load/Store结构提出: CDC6600(1963)-CRAY1(1976) RISC思想最早在IBM公司提出,但不叫RISC, IBM801处理器是公认体现RISC思想的机器。 1980年,Berkeley的Patterson和Dizel提出RISC名 词,并研制了RISC-,实验样机。 1981年Stenford的Hennessy研制MIPS芯片。 85年后推出商品化RISC: MIPS1(1986)和SPARC V1(1987)

ARM MIPS Hitachi SH PowerPC

Source: Andrew Allison, Inside The New Computer Industry, January 2001

Embedded RISC Processor Shipments

32位浪潮的到来

16,000 14,000 12,000

大量复杂指令的控制逻辑不规整,不适于VLSI工艺

软硬功能分配

不利于先进指令级并行技术的采用 流水线技术

RISC基本设计思想

减小CPI: CPUtime=Instr_Count * CPI * Clock_cycle

精简指令集:保留最基本的,去掉复杂、使用频 度不高的指令

采用Load/Store结构,有助于减少指令格式, 统一存储器访问方式 采用硬接线控制代替微程序控制

CISC:复杂指令集(Complex Instruction Set Computer) 具有大量的指令和寻址方式,指令长度可变 8/2原则:80%的程序只使用20%的指令 大多数程序只使用少量的指令就能够运行。 RISC:精简指令集(Reduced Instruction Set Computer) 只包含最有用的指令,指令长度固定

1

2

3

4

5

6

Decode Execute

Fetch Decode Execute Fetch Decode Fetch

该例中用6个时钟周期执行了6条指令 所有的操作都在寄存器中(单周期执行) 指令周期数 (CPI) = 1

LDR 流水线举例

周期

操作

ADD SUB Fetch Decode Execute Fetch Decode Execute Fetch Decode Execute Data

Execute

PC指向正被取指的指令,而非正在执行的指令

最佳流水线

周期

操作

ADD SUB MOV AND ORR EOR CMP RSB Fetch Decode Execute Fetch Decode Execute Fetch Decode Execute Fetch Decode Execute Fetch

地址A+3 高地址

实例

变量A:word A=0x f6 73 4b cd,在内存中的起始地 址为0x b3 20 45 00 变量B:half word B=218,在内存中的起始地址为 0x dd dd dd word d0 问题: half B=218与word C=218在内

0xb3204500 0xb3204500 存中的存放方式有何不同?请分大端和小 f6 cd 73 4b 端两种情况说明。

1

操作

BL X XX ADD SUB MOV Fetch Decode Execute

2

3

4

5

Linkret

Adjust

Fetch

Decode Fetch

Fetch

Decode Execute

Fetch Decode Execute Fetch

Decode

Fetch

流水线被阻断 注意:内核运行在ARM状态

为增加处理器指令流的速度,ARM7 系列使用3级流水线. 允许多个操作同时处理,比逐条指令执行要快。

ARM

PC

Thumb

PC

Fetch

从存储器中读取指令

PC - 4

PC-2

Decode

解码指令 寄存器读(从寄存器Bank) 移位及ALU操作 寄存器写(到寄存器Bank )

PC - 8

PC - 4

指令

取指

取指

流 水 线 1

译码1 译码2 执行1 执行2

流 水 线 2

译码1 译码2 执行1 执行2

数据回写

流水线技术中涉及到的两个问题

相关:在一个流水线系统中,如果第二条指 令需要用到第一条指令的结果,这种情况叫 做相关。 目前解决这个问题的方法是乱序执行。 条件转移 分支预测技术

CISC和RISC

DSP、ARM9

哈佛体系结构

冯.诺曼结构处理器指令流 的定时关系示意图

2、流水线技术

流水线(Pipeline)技术:几个指令可以并行执行 • 提高了CPU的运行效率

• 内部信息流要求通畅流动

Add Sub Cmp 时间 取指 译码 取指 执行add 译码 取指 执行sub 译码 执行cmp

指令流水线—以ARM为例

C H A P T E R

2

嵌入式系统的 基本知识

本节提要

1 嵌入式系统硬件基础 2 嵌入式系统软件基础 3 嵌入式操作系统

4

嵌入式系统设计方法

如人的大脑,决定了硬件的操作模 式。通过良好的操作系统以及应用 程序,把硬件功能发挥到极至。

嵌入式系统软件部分

如人的手、脚、神经等部位,决定 了嵌入式系统的先天功能。如运算 能力和I/O接口等。

确保数据通道快速执行每一条指令

使CPU硬件结构设计变得更为简单

CISC与RISC的数据通道

开始

IF

ID

ALU

Mቤተ መጻሕፍቲ ባይዱM

微操作通道

REG

退出

CISC:寻址方式复杂

开始

IF

ID

REG

ALU

MEM

退出

单通数据通道

RISC:Load/Store结构

CISC的背景和特点

背景: 存储资源紧缺, 强调编译优化 增强指令功能,设置一些功能复杂的指令,把 一些原来由软件实现的、常用的功能改用硬件 的(微程序)指令系统来实现 为节省存储空间,强调高代码密度,指令格式 不固定,指令可长可短,操作数可多可少 寻址方式复杂多样,操作数可来自寄存器,也 可来自存储器 采用微程序控制,执行每条指令均需完成一个 微指令序列 CPI > 5,指令越复杂,CPI越大。

典型的高性能RISC处理器

SUN公司的SPARC(1987) MIPS公司的SGI:MIPS(1986)

HP公司的PA-RISC,

IBM, Motorola公司的PowerPC