从最简的4条指令CPU实现了解CPU设计

FPGA简单CPU设计过程学习

FPGA简单CPU设计过程学习FPGA(Field Programmable Gate Array)是指一种具有可重新配置的硬件功能的集成电路。

它可以通过设置内部的逻辑模块和连线来实现不同的数字电路功能。

在FPGA中设计一个简单的CPU,可以加深对数字电路设计和计算机体系结构的理解。

以下是FPGA简单CPU设计的过程学习。

首先,需要了解CPU的基本组成部分。

一个简单的CPU通常包括取指单元(Instruction Fetch Unit,IFU)、译码单元(Decode Unit,DU)、执行单元(Execution Unit,EU)和存储器单元(Memory Unit,MU)。

IFU负责从存储器中读取指令,并将其传递给DU进行解码。

DU根据指令的类型和需要的操作数,决定要执行的操作,并将操作数传递给EU。

EU执行指令的操作,并将结果返回给MU。

然后,需要根据CPU的组成部分和指令集设计相应的模块。

IFU模块可以包括一个指令寄存器(Instruction Register,IR),用于存储当前指令。

DU模块可以包括一个指令解码器(Instruction Decoder),用于解码IR中的指令,并将操作码、目的寄存器地址和源寄存器地址传递给EU。

EU模块可以包括一个算术逻辑单元(Arithmetic Logic Unit,ALU),用于执行算术运算,并将结果传递给MU。

MU模块可以包括两个寄存器文件(Register File),分别用于存储源寄存器和目的寄存器的值。

在实际的FPGA设计中,可以使用硬件描述语言(Hardware Description Language,HDL)进行设计。

常用的HDL包括VHDL和Verilog。

使用HDL来描述CPU的各个模块,并进行逻辑仿真和综合,可以在FPGA上实现对CPU的验证和测试。

设计完成后,可以将CPU的设计烧录到FPGA中,并通过外部输入设备(如键盘)和输出设备(如显示器)来测试CPU的功能。

精简指令集和复杂指令集的区别

精简指令集和复杂指令集的区别RISC(精简指令集计算机)和CISC(复杂指令集计算机)是当前CPU的两种。

它们的区别在于不同的CPU设计理念和⽅法。

CPU架构是⼚商给属于同⼀系列的CPU产品定的⼀个规范,主要⽬的是为了区分不同类型CPU的重要标⽰早期的CPU全部是CISC架构,它的设计⽬的是要⽤最少的机器语⾔指令来完成所需的计算任务。

⽐如对于乘法运算,在CISC架构的CPU 上,您可能需要这样⼀条指令:MUL ADDRA, ADDRB就可以将ADDRA和ADDRB中的数相乘并将结果储存在ADDRA中。

将ADDRA, ADDRB中的数据读⼊寄存器,相乘和将结果写回内存的操作全部依赖于CPU中设计的逻辑来实现。

这种架构会增加CPU结构的复杂性和对CPU⼯艺的要求,但对于编译器的开发⼗分有利。

⽐如上⾯的例⼦,C程序中的a*=b就可以直接编译为⼀条乘法指令。

今天只有Intel及其兼容CPU还在使⽤CISC架构。

RISC架构要求软件来指定各个操作步骤。

上⾯的例⼦如果要在RISC架构上实现,将ADDRA, ADDRB中的数据读⼊寄存器,相乘和将结果写回内存的操作都必须由软件来实现,⽐如:MOV A, ADDRA; MOV B, ADDRB; MUL A, B; STR ADDRA, A。

这种架构可以降低CPU的复杂性以及允许在同样的⼯艺⽔平下⽣产出功能更强⼤的CPU,但对于编译器的设计有更⾼的要求。

复杂指令集计算机(CISC) 长期来,计算机性能的提⾼往往是通过增加硬件的复杂性来获得.随着集成电路技术.特别是VLSI(超⼤规模集成电路)技术的迅速发展,为了软件编程⽅便和提⾼程序的运⾏速度,硬件⼯程师采⽤的办法是不断增加可实现复杂功能的指令和多种灵活的编址⽅式.甚⾄某些指令可⽀持⾼级语⾔语句归类后的复杂操作.⾄使硬件越来越复杂,造价也相应提⾼.为实现复杂操作,微处理器除向程序员提供类似各种寄存器和机器指令功能外.还通过存于只读存贮器(ROM)中的微程序来实现其极强的功能,傲处理在分析每⼀条指令之后执⾏⼀系列初级指令运算来完成所需的功能,这种设计的型式被称为复杂指令集计算机(Complex Instruction Set Computer-CISC)结构.⼀般CISC计算机所含的指令数⽬⾄少300条以上,有的甚⾄超过500条.精简指令集计算机(RISC) 采⽤复杂指令系统的计算机有着较强的处理⾼级语⾔的能⼒.这对提⾼计算机的性能是有益的.当计算机的设计沿着这条道路发展时.有些⼈没有随波逐流.他们回过头去看⼀看过去⾛过的道路,开始怀疑这种传统的做法:IBM公司没在纽约Yorktown的JhomasI.Wason研究中⼼于1975年组织⼒量研究指令系统的合理性问题.因为当时已感到,⽇趋庞杂的指令系统不但不易实现.⽽且还可能降低系统性能.1979年以帕特逊教授为⾸的⼀批科学家也开始在美国加册⼤学伯克莱分校开展这⼀研究.结果表明,CISC存在许多缺点.⾸先.在这种计算机中.各种指令的使⽤率相差悬殊:⼀个典型程序的运算过程所使⽤的80%指令.只占⼀个处理器指令系统的20%.事实上最频繁使⽤的指令是取、存和加这些最简单的指令.这样-来,长期致⼒于复杂指令系统的设计,实际上是在设计⼀种难得在实践中⽤得上的指令系统的处理器.同时.复杂的指令系统必然带来结构的复杂性.这不但增加了设计的时间与成本还容易造成设计失误.此外.尽管VLSI技术现在已达到很⾼的⽔平,但也很难把CISC的全部硬件做在⼀个芯⽚上,这也妨碍单⽚计算机的发展.在CISC中,许多复杂指令需要极复杂的操作,这类指令多数是某种⾼级语⾔的直接翻版,因⽽通⽤性差.由于采⽤⼆级的微码执⾏⽅式,它也降低那些被频繁调⽤的简单指令系统的运⾏速度.因⽽.针对CISC的这些弊病.帕特逊等⼈提出了精简指令的设想即指令系统应当只包含那些使⽤频率很⾼的少量指令.并提供⼀些必要的指令以⽀持操作系统和⾼级语⾔.按照这个原则发展⽽成的计算机被称为精简指令集计算机(Reduced Instruction Set Computer-RISC)结构.简称RISC.CISC与RISC的区别 我们经常谈论有关"PC"与"Macintosh"的话题,但是⼜有多少⼈知道以Intel公司X86为核⼼的PC系列正是基于CISC体系结构,⽽ Apple 公司的Macintosh则是基于RISC体系结构,CISC与RISC到底有何区别? 从硬件⾓度来看CISC处理的是不等长指令集,它必须对不等长指令进⾏分割,因此在执⾏单⼀指令的时候需要进⾏较多的处理⼯作。

CPU常用操作指令

CPU常用操作指令汇编语言是一种低级别的计算机程序语言,用于直接控制和操作计算机的中央处理器(CPU)。

在编写汇编语言程序时,需要使用一系列的操作指令来完成各种任务。

下面是一些常用的CPU操作指令及其功能的汇编语言示例。

1.MOV:将数据从一个位置传输到另一个位置。

示例:MOVAX,BX;将BX寄存器的内容传送到AX寄存器2.ADD/SUB:进行加法或减法操作。

示例:ADDAX,BX;将BX寄存器的内容加到AX寄存器SUBAX,BX;从AX寄存器中减去BX寄存器的内容3.INC/DEC:将操作数的值增加或减少1示例:INCAX;将AX寄存器的值增加1DECBX;将BX寄存器的值减少14.CMP:比较两个操作数的值,设置标志寄存器的状态以供条件跳转指令使用。

示例:CMPAX,BX;比较AX和BX寄存器的值5.JMP:无条件跳转到指定地址。

6.JE/JNE:根据标志寄存器的状态,执行条件跳转。

7.AND/OR/XOR:进行逻辑与、逻辑或或逻辑异或操作。

示例:ANDAX,BX;将AX和BX寄存器的值进行逻辑与操作ORAX,BX;将AX和BX寄存器的值进行逻辑或操作XORAX,BX;将AX和BX寄存器的值进行逻辑异或操作8.PUSH/POP:将数据压入栈或从栈中弹出数据。

示例:PUSHAX;将AX寄存器的值压入栈中POPBX;从栈中弹出数据,并将其存入BX寄存器9.CALL/RET:调用子程序或从子程序返回。

示例:CALL subroutine ; 调用名为"subroutine"的子程序RET;从子程序返回到调用位置10.INT:触发中断。

示例:INTn;触发编号为n的中断这些是一些常用的CPU操作指令的示例,每个指令都有具体的功能和用法。

在汇编语言编程中,根据具体的需求选择合适的指令来完成要求的任务。

因为汇编语言直接与硬件进行交互,所以熟悉这些操作指令对于理解和优化程序性能非常重要。

CPU常用操作指令

CPU常用操作指令CPU常用操作指令是指在汇编语言中使用的一些常见的指令,用于完成各种任务和操作。

这些指令可以用于数据传输、算术运算、逻辑运算、条件分支等各种操作。

下面我将列举一些常见的CPU操作指令,并介绍它们的用途和示例。

1.MOV指令:用于将数据从一个地方移动到另一个地方。

例如,将一个寄存器中的值移动到另一个寄存器中,或将一个内存单元中的值移动到一个寄存器中。

示例:MOVAX,BX;将BX中的值移动到AX中MOV[BX],10;将值10存储到BX所指向的内存单元中2.ADD指令:用于执行整数的加法操作。

可以将两个寄存器中的值相加,或将一个寄存器中的值与一个立即数相加。

示例:ADDAX,BX;将AX和BX中的值相加,并将结果存储到AX中ADDAX,10;将AX中的值与10相加,并将结果存储到AX中3.SUB指令:用于执行整数的减法操作。

可以将两个寄存器中的值相减,或将一个寄存器中的值与一个立即数相减。

示例:SUBAX,BX;将AX和BX中的值相减,并将结果存储到AX中SUBAX,10;将AX中的值减去10,并将结果存储到AX中4.MUL指令:用于执行无符号整数的乘法操作。

可以将一个寄存器中的值与另一个寄存器中的值相乘,并将结果存储到两个乘积寄存器中。

示例:MOVAX,10;将值10存储到AX中MOVBX,5;将值5存储到BX中MULBX;将AX中的值与BX中的值相乘,并将结果存储到AX和DX中5.DIV指令:用于执行无符号整数的除法操作。

可以将一个寄存器中的值与另一个寄存器中的值相除,并将商存储到一个寄存器中,余数存储到另一个寄存器中。

示例:MOVAX,20;将值20存储到AX中MOVBX,5;将值5存储到BX中DIVBX;将AX中的值除以BX中的值,并将商存储到AX中,余数存储到DX中6.AND指令:用于执行逻辑与操作。

可以将一个寄存器中的值与另一个寄存器中的值进行逻辑与运算,并将结果存储到一个寄存器中。

CPU实验报告范文

CPU实验报告范文一、实验目的本次实验的目的是设计和实现一个简单的中央处理器(CPU),通过实践掌握CPU的基本工作原理和实现方法。

二、实验原理1.CPU的基本概念中央处理器(CPU)是计算机的核心部件,负责执行计算机指令和控制计算机的操作。

它由运算器、控制器和寄存器组成。

运算器负责执行算术和逻辑运算,包括加法、减法、乘法、除法等。

控制器负责指挥CPU的工作,通过控制总线实现对内存和其他外部设备的访问。

寄存器是CPU内部的存储器,用于暂时存放指令、数据和中间结果。

2.CPU的实现方法CPU的实现采用组合逻辑电路和时序逻辑电路相结合的方法。

组合逻辑电路是由逻辑门构成的电路,它的输入只依赖于当前时刻的输入信号,输出也只与当前时刻的输入信号有关。

而时序逻辑电路则包含存储元件,其输出不仅与当前时刻的输入信号有关,还与之前的输入信号有关。

CPU的实现过程主要包括以下步骤:(1)设计指令集:确定CPU支持的指令集,包括指令的格式和操作码。

(2)设计控制器:根据指令集设计控制器,确定各个指令的执行过程和控制信号。

(3)设计运算器:根据指令集设计运算器,确定支持的算术和逻辑运算。

(4)设计寄存器:确定需要的寄存器数量和位数,设计寄存器的输入输出和工作方式。

3.实验环境和工具本次实验使用的环境和工具如下:(1)硬件环境:计算机、开发板、示波器等。

(2)软件环境:Win10操作系统、Vivado开发工具等。

三、实验步骤1.设计指令集根据实验要求,我们设计了一个简单的指令集,包括加法、减法、逻辑与、逻辑或和移位指令。

每个指令有特定的操作码和操作数。

2.设计控制器根据指令集设计了一个控制器。

控制器根据指令的操作码产生相应的控制信号,控制CPU内部寄存器、运算器和总线的操作。

3.设计运算器根据指令集设计了一个运算器。

运算器包括加法器、减法器、与门和或门等。

它通过输入的操作数和控制信号完成相应的运算操作。

4.设计寄存器根据实验需求确定了所需的寄存器数量和位数。

cpu执行指令基本过程

cpu执行指令基本过程嘿,朋友!咱今天来聊聊 CPU 执行指令那点事儿。

你知道吗?CPU 就像是一个超级忙碌的小管家,一刻不停地处理着各种指令。

那它到底是怎么干活的呢?咱先来说说取指令。

这就好比你去图书馆找一本书,CPU 得先找到它要执行的指令在哪儿。

想象一下,这就像是在一个巨大的书架上准确地找到那本特定的“书”,可不容易啊!然后是译码。

找到指令后,CPU 得搞清楚这指令到底是啥意思。

这就像你收到一封密码信,得先把它翻译成能看懂的话。

接下来是执行。

这可是关键步骤,就像你明白了任务,然后动手去做一样。

CPU 会根据译码的结果进行计算、数据处理等等操作。

比如说,让两个数字相加,或者把数据从一个地方搬到另一个地方。

最后是写回。

这就好比你完成了一项任务,得把结果汇报给上级。

CPU 把执行的结果写回到寄存器或者内存中,以备后续使用。

你说,这 CPU 忙前忙后的,像不像一个勤劳的小蜜蜂?而且它的速度那叫一个快,眨个眼的功夫,可能就处理了好多好多指令。

比如说,你在玩游戏的时候,画面的每一帧变化,都是 CPU 在背后快速地执行着一系列的指令,让游戏能顺畅地运行。

要是 CPU 偷懒一下,那游戏可能就卡顿啦,多烦人!再比如,你用电脑处理文档,输入一个字,CPU 就得马上做出反应,显示在屏幕上。

这速度,简直了!所以说啊,CPU 执行指令的基本过程虽然看似复杂,但是它却默默地为我们的各种电子设备提供了强大的支持。

没有它的辛勤工作,咱们哪能享受到这么便捷的科技生活呢?总之,CPU 执行指令的过程虽然咱平时看不见摸不着,但它却实实在在地影响着我们生活的方方面面,是不是很神奇?。

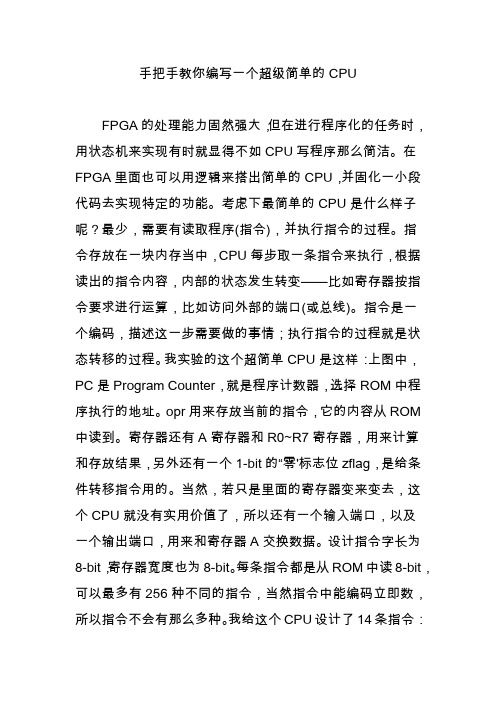

手把手教你编写一个超级简单的CPU

手把手教你编写一个超级简单的CPUFPGA的处理能力固然强大,但在进行程序化的任务时,用状态机来实现有时就显得不如CPU写程序那么简洁。

在FPGA里面也可以用逻辑来搭出简单的CPU,并固化一小段代码去实现特定的功能。

考虑下最简单的CPU是什么样子呢?最少,需要有读取程序(指令),并执行指令的过程。

指令存放在一块内存当中,CPU每步取一条指令来执行,根据读出的指令内容,内部的状态发生转变——比如寄存器按指令要求进行运算,比如访问外部的端口(或总线)。

指令是一个编码,描述这一步需要做的事情;执行指令的过程就是状态转移的过程。

我实验的这个超简单CPU是这样:上图中,PC是Program Counter,就是程序计数器,选择ROM中程序执行的地址。

opr用来存放当前的指令,它的内容从ROM 中读到。

寄存器还有A寄存器和R0~R7寄存器,用来计算和存放结果,另外还有一个1-bit的“零'标志位zflag,是给条件转移指令用的。

当然,若只是里面的寄存器变来变去,这个CPU就没有实用价值了,所以还有一个输入端口,以及一个输出端口,用来和寄存器A交换数据。

设计指令字长为8-bit,寄存器宽度也为8-bit。

每条指令都是从ROM中读8-bit,可以最多有256种不同的指令,当然指令中能编码立即数,所以指令不会有那么多种。

我给这个CPU设计了14条指令:跳转指令有2条,无条件转移和Z条件转移,转移范围为5-bit相对地址,即-16~+15。

带立即数指令有4条,因为指令才8-bit,立即数只好分配4-bit了。

装入A寄存器的高4位或低4位,以及与A做加减法。

R0~R7寄存器只能与A 寄存器进行copy和比较操作。

影响zflag标志的指令有位测试指令TESTB, 比较指令COMP和加减法指令。

指令空间并没有用完,可以根据需要再补充指令。

用Verilog语言来写这个CPU的状态转移部分:module cpu0(clk, Iaddr, Ibus, PortI, PortO);input clk;output [9:0] Iaddr;input [7:0]Ibus;input [7:0] PortI;output reg [7:0] PortO;reg [9:0] pc;reg [7:0] RA;reg [7:0] Rn[0:7];reg zflag;assign Iaddr=pc;reg [7:0] opr;always @(posedge clk)opr wire [1:0]opc1=opr[7:6];wire [5:0] opx=opr[5:0];wire [1:0]opc2=opr[5:4];wire [3:0] imm4=opr[3:0];wire [2:0]sel=opr[2:0];reg branch;always @(posedge clk) beginpc branch if(~branch) beginif(opc1==2'd3)if(opr[5] | zflag) beginpc branch endendendalways @(posedge clk) beginif(~branch) beginif(opc1==2'd1 &&opc2==2'd0)Rn[sel] endendalways @(posedge clk) beginif(~branch) begincase(opc1)2'd0:beginif(opx==6'd0)RA end2'd1: beginif(opc2==2'd1)RA end2'd2: begincase(opc2)2'd0: RA[7:4] 2'd1: RA[3:0] 2'd2:RA 2'd3: RA endcaseendendcaseendendalways@(posedge clk) beginif(~branch) beginif(opc1==2'd0 && opx==6'd1)PortO endendalways @(posedge clk)beginif(~branch) beginif(opc1==2'd1) begincase(opc2)2'd3: zflag 2'd2: zflag endcaseendif(opc1==2'd2)beginif(opc2[1])zflag endendendendmodule除了指令所描述的寄存器的操作外,还多了一个branch寄存器和条件判断,这是做什么呢?请注意,PC寄存器所指的是下一条要执行的指令地址(默认总是pc 写测试程序了,没有编译器,汇编程序都得自己写呢。

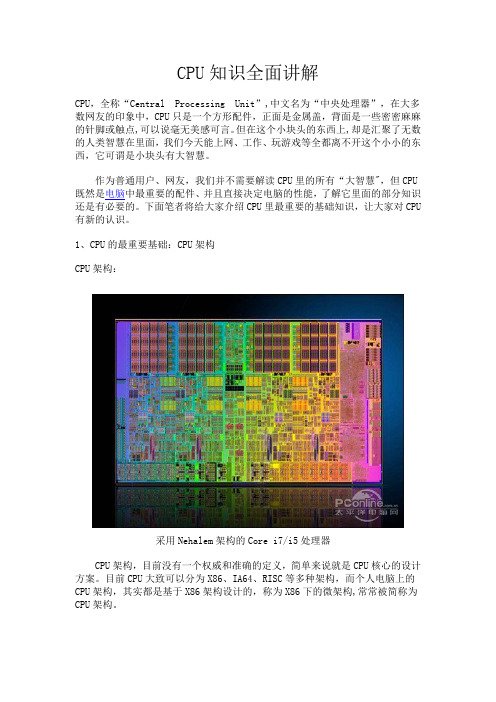

CPU知识全面讲解

CPU知识全面讲解CPU,全称“Central Processing Unit”,中文名为“中央处理器”,在大多数网友的印象中,CPU只是一个方形配件,正面是金属盖,背面是一些密密麻麻的针脚或触点,可以说毫无美感可言。

但在这个小块头的东西上,却是汇聚了无数的人类智慧在里面,我们今天能上网、工作、玩游戏等全都离不开这个小小的东西,它可谓是小块头有大智慧。

作为普通用户、网友,我们并不需要解读CPU里的所有“大智慧",但CPU 既然是电脑中最重要的配件、并且直接决定电脑的性能,了解它里面的部分知识还是有必要的。

下面笔者将给大家介绍CPU里最重要的基础知识,让大家对CPU 有新的认识。

1、CPU的最重要基础:CPU架构CPU架构:采用Nehalem架构的Core i7/i5处理器CPU架构,目前没有一个权威和准确的定义,简单来说就是CPU核心的设计方案。

目前CPU大致可以分为X86、IA64、RISC等多种架构,而个人电脑上的CPU架构,其实都是基于X86架构设计的,称为X86下的微架构,常常被简称为CPU架构。

更新CPU架构能有效地提高CPU的执行效率,但也需要投入巨大的研发成本,因此CPU厂商一般每2-3年才更新一次架构。

近几年比较著名的X86微架构有Intel的Netburst(Pentium 4/Pentium D系列)、Core(Core 2系列)、Nehalem(Core i7/i5/i3系列),以及AMD的K8(Athlon 64系列)、K10(Phenom 系列)、K10。

5(Athlon II/Phenom II系列).Intel以Tick-Tock钟摆模式更新CPU自2006年发布Core 2系列后,Intel便以“Tick—Tock”钟摆模式更新CPU,简单来说就是第一年改进CPU工艺,第二年更新CPU微架构,这样交替进行。

目前Intel正进行“Tick”阶段,即改进CPU的制造工艺,如最新的Westmere架构其实就是Nehalem架构的工艺改进版,下一代Sandy Bridge架构将是全新架构。

cpu的基本指令

cpu的基本指令(实用版)目录1.CPU 的基本指令概述2.CPU 的基本指令的类型3.CPU 的基本指令的应用4.CPU 的基本指令的发展趋势正文【1.CPU 的基本指令概述】CPU 的基本指令,也被称为机器指令,是计算机硬件能够直接识别和执行的指令。

它们是计算机程序员与计算机硬件之间的桥梁,通过这些指令,程序员可以告诉计算机如何执行各种任务。

CPU 的基本指令可以完成各种基本的操作,如数据传输、算术运算、逻辑运算、跳转等。

【2.CPU 的基本指令的类型】CPU 的基本指令主要分为以下几种类型:(1)数据传输指令:这类指令主要用于在寄存器和内存之间传输数据。

例如,将一个数值从寄存器 A 传输到寄存器 B 的指令。

(2)算术运算指令:这类指令主要用于完成各种算术运算,如加法、减法、乘法、除法等。

例如,将寄存器 A 中的数值与寄存器 B 中的数值相加,并将结果存储在寄存器 C 中的指令。

(3)逻辑运算指令:这类指令主要用于完成各种逻辑运算,如与、或、非、异或等。

例如,对寄存器 A 和寄存器 B 中的数值进行“与”运算,并将结果存储在寄存器 C 中的指令。

(4)跳转指令:这类指令主要用于改变程序的执行顺序。

例如,根据某个条件决定是否跳转到指定地址继续执行程序的指令。

(5)循环指令:这类指令主要用于实现循环操作。

例如,重复执行一段指令直到满足某个条件为止的指令。

【3.CPU 的基本指令的应用】CPU 的基本指令在各种计算机程序中都有广泛的应用。

例如,在编写一个简单的计算器程序时,需要使用数据传输指令将用户输入的数字存储到寄存器中,使用算术运算指令完成加法、减法等运算,使用逻辑运算指令判断运算结果的正负,使用跳转指令根据用户输入的选项决定程序的执行流程等。

【4.CPU 的基本指令的发展趋势】随着计算机技术的发展,CPU 的基本指令也在不断演变。

未来的 CPU 指令集可能会更加简洁、高效,以适应更高性能、更低功耗的计算需求。

计算机组成原理考试试卷

计算机组成原理考试试卷一、选择题(每题2分,共20分)1. 在计算机系统中,CPU指的是什么?A. 中央处理器B. 存储器C. 输入设备D. 输出设备2. 计算机的存储器分为哪两大类?A. 内部存储器和外部存储器B. 只读存储器和随机存取存储器C. 静态存储器和动态存储器D. 硬盘存储器和固态存储器3. 以下哪个是计算机的输入设备?A. 打印机B. 鼠标C. 显示器D. 键盘4. 计算机的指令执行过程通常包括哪几个步骤?A. 取指令、分析指令、执行指令B. 存储指令、分析指令、执行指令C. 取指令、存储指令、执行指令D. 分析指令、存储指令、执行指令5. 以下哪个是计算机的输出设备?A. 硬盘B. 打印机C. 扫描仪D. 键盘6. 计算机的总线分为哪几种类型?A. 数据总线、地址总线、控制总线B. 内部总线、外部总线C. 串行总线、并行总线D. 逻辑总线、物理总线7. 计算机的存储器的容量通常用哪个单位来表示?A. 位B. 字节C. 赫兹D. 毫秒8. 计算机的内存条通常指的是什么类型的存储器?A. 只读存储器B. 随机存取存储器C. 缓存存储器D. 辅助存储器9. 在计算机系统中,操作系统的主要作用是什么?A. 管理计算机硬件资源B. 执行用户程序C. 提供用户界面D. 存储数据10. 计算机的CPU中,ALU指的是什么?A. 算术逻辑单元B. 地址逻辑单元C. 应用逻辑单元D. 辅助逻辑单元二、填空题(每空1分,共10分)11. 计算机的五大基本部件包括________、________、存储器、输入设备和输出设备。

12. 计算机的指令系统包括指令格式和________。

13. 在计算机系统中,________是用于存储程序和数据的部件。

14. 计算机的CPU由________和控制单元组成。

15. 计算机的存储器的存储单元地址从________开始。

三、简答题(每题5分,共20分)16. 简述计算机指令的执行过程。

精简指令集cpu的特点

精简指令集cpu的特点1.简化指令集:RISCCPU的指令集非常精简,通常只包含几十条指令,每条指令都非常简单,且执行时间一致。

这使得CPU的设计和实现更加简单,也提高了指令的执行效率。

2.单周期执行:RISCCPU的每条指令在执行过程中只需要一个时钟周期。

当CPU执行一条指令时,它会按照固定的步骤执行,从取指令、译码、执行、访存、写回等阶段依次进行。

这种单周期执行的特点使得RISCCPU的执行效率更高。

3.高效的流水线:RISCCPU通常采用流水线结构来提高指令的执行效率。

流水线将指令的各个执行阶段分开,使得多条指令可以同时进入流水线进行执行,从而实现指令的并行处理,提高了CPU的吞吐量。

4.小型高速缓存:RISCCPU通常具有较小但高速的缓存,包括指令缓存和数据缓存。

这些缓存用于存储最常用的指令和数据,可以提高CPU对内存的访问速度,进而提高整体的执行效率。

5.数据流和控制流分离:RISCCPU将数据流和控制流分离,通过专门的寄存器来存储和传递控制信息。

这样可以提高CPU对错误处理、分支预测等方面的处理能力。

6.高度可扩展性:RISCCPU的特点使得其在设计和制造时更易于进行扩展和升级。

开发者可以根据需求自由添加新的特性和功能,而不需要重新设计整个处理器。

7.低功耗设计:RISCCPU的设计注重低功耗和高能效。

通过简化指令集和减少冗余的硬件功能,RISCCPU可以在相同处理能力的情况下比CISCCPU低功耗,这使得RISCCPU在嵌入式系统和移动设备中具有更好的应用前景。

总而言之,精简指令集的CPU具有简化的指令集、单周期执行、高效的流水线、高速缓存、数据流和控制流分离、可扩展性和低功耗设计等特点。

这些特点使得RISCCPU在执行效率、可靠性、可扩展性和能效方面具有优势,广泛应用于各种计算机和嵌入式系统中。

cpu的基本指令

cpu的基本指令摘要:一、CPU简介1.CPU的定义与作用2.CPU的发展历程二、CPU的基本指令1.指令集简介2.常见的基本指令a.数据传输指令b.算术指令c.逻辑指令d.跳转指令e.调用和返回指令三、CPU的工作原理1.指令的执行2.控制单元的作用3.寄存器和内存的作用四、CPU的性能评价1.频率2.核心数量3.缓存4.制程工艺五、CPU的应用领域1.个人电脑2.服务器3.嵌入式设备4.超级计算机正文:CPU(中央处理器)是计算机的核心部件,主要负责解释和执行指令,以完成各种计算和操作。

CPU的发展历程可以追溯到20世纪40年代,经历了多次的技术变革,如今已经发展到了多核、高频率、低功耗的阶段。

CPU的基本指令是CPU执行操作的基础。

指令集是CPU支持的指令的集合,不同的CPU架构有不同的指令集。

常见的基本指令包括数据传输指令(如MOV、PUSH、POP等)、算术指令(如ADD、SUB、MUL、DIV等)、逻辑指令(如AND、OR、NOT等)、跳转指令(如JMP、JZ、JNZ等)以及调用和返回指令(如CALL、RET等)。

CPU的工作原理是接收和解析指令,然后根据指令的操作完成相应的计算和操作。

在这个过程中,控制单元负责解析指令并控制各个部件的工作;寄存器和内存用于暂存数据和指令。

在评价CPU性能时,我们通常会关注以下几个指标:频率(即主频,表示CPU每秒钟可以执行的时钟周期数)、核心数量(表示CPU可以同时执行的任务数量)、缓存(用于暂存热数据,提高CPU的运行速度)以及制程工艺(即生产工艺,影响CPU的功耗和性能)。

CPU在各个领域都有广泛的应用,如个人电脑、服务器、嵌入式设备和超级计算机。

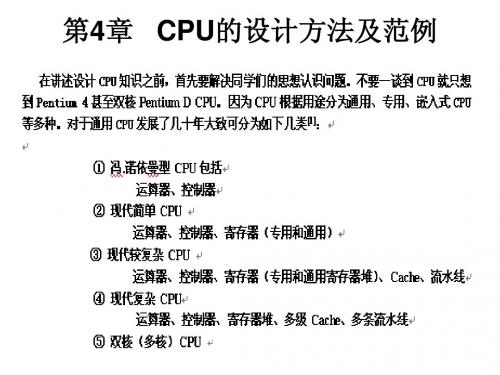

第4章 CPU的设计方法及范例

非常简单CPU不具有应用价值,仅用来说明 设计过程。不过,只要我们能正确设计出只有4条 指令的CPU,就可以设计出拥有40条指令的CPU, 甚至更多·· ·。难道这样还有怀疑吗?当然不能期 望马上就有创新,但这个CPU是拥有自主知识产 权的。或者有些同学会这样想,我以后并非从事 硬件的工作,更不可能从事设计CPU的专业,我 也相信这是事实。但是,这绝对有利于我们掌握 计算机的工作原理,也有利于从事各种软、硬件 开发和计算机科学等领域的研究、教学工作。

图4.9 通用CPU的状态图

其实CPU就是一个复杂的有限状态机 【冯· 诺依曼机的理论是基于图灵(Turing) 机理论的,而图灵机就是一个有限状态 机】。通过确定状态及其对应的微操作, 就可明确CPU为了取数据(或指令),指 令译码和执行指令集中每一条指令所必须 要完成的步骤。 问题:什么是图灵机理论?

1966年美国计算机协会设立“图灵奖”,被视为计算机科学界的最高荣誉

它的“纸带”相当于作业薄,读写头相当于人的眼 睛、手、笔,对于输入集{x1,x2,…xn},r(i, 0)= xi,i= 1,2,..n相当于“抄题”,而映射f 的读写变换相当于人脑判断确定下一步的行为且 指挥手和笔如何去动作和书写。它高度概括地回 答了什么是运算,不但为计算复杂度理论提供了 研究工具,而且为20世纪50年代计算机的设计提 供了思想基础,即Moore机和Mealy机。【注:当 出现状态Sy或Sn时,即得到了Turing 机的运算结 论Yes或No,这时即S(t)∈{ Sy,Sn }时停机】

二、建立数据通路的原理和方法

1.存贮器数据通路的原理

2.CPU内部的数据通路(两种不同的方案)

三、CPU内部寄存器控制信号的定义和确定方法

2.决定每个部件应完成的功能(详见图4.14)

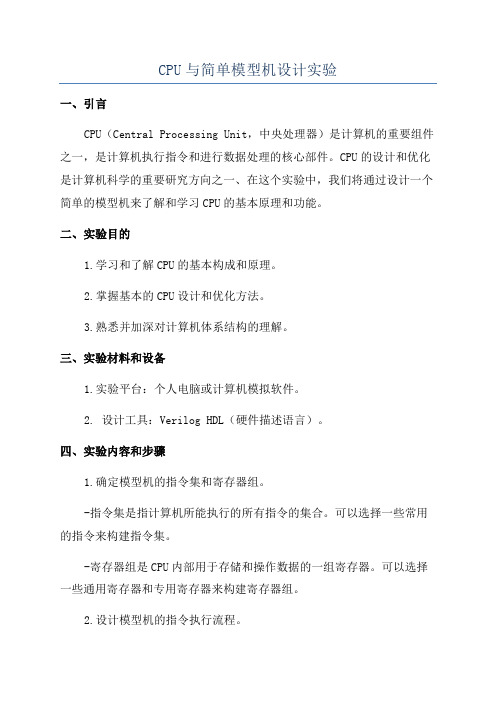

CPU与简单模型机设计实验

CPU与简单模型机设计实验一、引言CPU(Central Processing Unit,中央处理器)是计算机的重要组件之一,是计算机执行指令和进行数据处理的核心部件。

CPU的设计和优化是计算机科学的重要研究方向之一、在这个实验中,我们将通过设计一个简单的模型机来了解和学习CPU的基本原理和功能。

二、实验目的1.学习和了解CPU的基本构成和原理。

2.掌握基本的CPU设计和优化方法。

3.熟悉并加深对计算机体系结构的理解。

三、实验材料和设备1.实验平台:个人电脑或计算机模拟软件。

2. 设计工具:Verilog HDL(硬件描述语言)。

四、实验内容和步骤1.确定模型机的指令集和寄存器组。

-指令集是指计算机所能执行的所有指令的集合。

可以选择一些常用的指令来构建指令集。

-寄存器组是CPU内部用于存储和操作数据的一组寄存器。

可以选择一些通用寄存器和专用寄存器来构建寄存器组。

2.设计模型机的指令执行流程。

-指令执行流程是指CPU执行每个指令时所经过的步骤和操作。

可以使用流程图或状态转移图来描述指令执行流程。

3.设计并实现CPU的数据通路。

-数据通路是指CPU内部的数据传输路径和控制信号。

可以使用各种逻辑门和触发器来实现数据通路。

4.设计并实现模型机的控制部件。

-控制部件是CPU内部用于控制指令执行流程的部件。

可以使用有限状态机或控制存储器等方法来实现控制部件。

5.编写并调试模型机的控制程序。

-控制程序是指一段能够实现特定功能的指令序列。

可以使用汇编语言来编写和调试控制程序。

6.运行和测试设计的模型机。

-在模型机上执行一些简单的指令,观察和分析其执行结果,进行性能测试和优化。

五、实验结果与分析通过完成以上实验内容,我们将得到一个简单的模型机,并能够执行一些简单的指令。

我们可以通过观察和分析指令的执行结果,了解和学习CPU的基本原理和功能。

此外,我们还可以根据实际情况对模型机进行性能测试和优化,以提升其执行效率和性能。

CPU架构:CPU架构详细介绍

CPU架构:CPU架构详细介绍1 概述CPU架构是CPU商给CPU产品定的⼀个规范,主要⽬的是为了区分不同类型的CPU。

⽬前市场上的CPU分类主要分有两⼤阵营,⼀个是intel、AMD为⾸的复杂指令集CPU,另⼀个是以IBM、ARM为⾸的精简指令集CPU。

不同品牌的CPU,其产品的架构也不相同,Intel、AMD的CPU是X86架构,IBM公司的CPU是PowerPC架构,ARM公司的CPU是ARM架构,国内的飞腾CPU也是ARM架构。

此外还有MPIS架构、SPARC架构、Alpha架构。

2 X86架构X86架构(The X86 architecture)是微处理器执⾏的计算机语⾔指令集。

X86指令集是美国Intel公司为其第⼀块16位CPU(i8086)专门开发的,美国IBM公司1981年推出的世界第⼀台PC机中的CPU--i8088(i8086简化版)使⽤的也是X86指令。

同时电脑中为提⾼浮点数据处理能⼒⽽增加的X87芯⽚系列数字协处理器则另外使⽤X87指令,,包括后来 Intel 80186、80286、80386以及80486,由于以“86”作为结尾,以后就将X86指令集和X87指令集统称为X86指令集。

虽然随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到今天的Pentium 4(以下简为P4)系列,但为了保证电脑能继续运⾏以往开发的各类应⽤程序以保护和继承丰富的软件资源,所以Intel公司所⽣产的所有CPU仍然继续使⽤X86指令集,所以它的CPU仍属于X86系列。

x86架构CPU主要应⽤领域:个⼈计算机、服务器等。

在PC端市场Wintel组合(windows系统 + intel处理器)占据了⼤部分江⼭,另外⼀部分有ADM占领。

⽬前国内有兆芯,从AMD和VIA获取授权,研发⾃⼰的X86CPU,有其它国产CPU + 国产操作系统(linux系)可以⽤于教育和事业单位以及军⼯⾏针对的是特殊⽤户,国产CPU和操作系统想进⼊民⽤市场,由于性能、价格以及⽣态系统等,仍需要继续优化打磨以及⼀个合适契机。

cpu指令集有多少种

cpu指令集有多少种你知道电脑cpu的指令集有多少种吗?小编来像你介绍!下面由店铺给你做出详细的cpu指令集介绍!希望对你有帮助!cpu指令集介绍一(1)CISC指令集CISC指令集,也称为复杂指令集,英文名是CISC,(Complex Instruction Set Computer的缩写)。

在CISC微处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。

其实它是英特尔生产的x86系列(也就是IA-32架构)CPU 及其兼容CPU,如AMD、VIA的。

即使是现在新起的X86-64(也被成AMD64)都是属于CISC的范畴。

要知道什么是指令集还要从当今的X86架构的CPU说起。

X86指令集是Intel为其第一块16位CPU(i8086)专门开发的,IBM1981年推出的世界第一台PC机中的CPU—i8088(i8086简化版)使用的也是X86指令,同时电脑中为提高浮点数据处理能力而增加了X87芯片,以后就将X86指令集和X87指令集统称为X86指令集。

虽然随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到过去的PII至强、PIII至强、Pentium 3,最后到今天的Pentium 4系列、至强(不包括至强Nocona),但为了保证电脑能继续运行以往开发的各类应用程序以保护和继承丰富的软件资源,所以Intel公司所生产的所有CPU仍然继续使用X86指令集,所以它的CPU仍属于X86系列。

由于Intel X86系列及其兼容CPU(如AMD Athlon MP、)都使用X86指令集,所以就形成了今天庞大的X86系列及兼容CPU阵容。

x86CPU目前主要有intel的服务器CPU和AMD 的服务器CPU两类。

(2)RISC指令集RISC是英文“Reduced Instruction Set Computing ” 的缩写,中文意思是“精简指令集”。

简单CPU系统设计及实现

简单CPU系统设计及实现首先,我们需要确定CPU系统的架构。

在本例中,我们将采用单周期处理器设计,该设计非常简单且易于实现。

在该架构中,每个指令在一个时钟周期内完成执行。

接下来,我们需要确定指令集的构成。

在本例中,我们将使用基本的指令集,包括算术操作指令(如加法、减法、乘法、除法)、逻辑操作指令(如与、或、异或)和数据传输指令(如存储、加载和移动数据)。

在开始设计CPU系统之前,我们需要确定CPU寄存器的数量和宽度。

在本例中,我们将使用8个寄存器,每个寄存器的宽度为8位。

这些寄存器将分别用于存储通用数据、存储器地址和指令。

现在我们可以开始设计CPU的数据路径。

数据路径是指数据在CPU内部通过的路径。

在单周期处理器中,数据路径包括指令存储器、程序计数器、寄存器文件、算术逻辑单元(ALU)和存储器。

指令存储器用于存储程序的指令,可以通过程序计数器(PC)来访问。

PC是一个寄存器,它存储下一条指令的地址。

每个时钟周期,PC增加1,以指向下一条指令。

寄存器文件用于存储CPU的寄存器,可以通过寄存器地址来访问。

寄存器文件包括8个通用寄存器。

ALU用于执行算术和逻辑运算。

它从寄存器文件中读取操作数,并将结果写回寄存器文件。

存储器用于存储数据,包括程序的指令和变量。

存储器有两个口,一个用于读取操作,一个用于写入操作。

设计数据路径后,我们需要设计控制单元。

控制单元控制数据路径中的信号流动。

在单周期处理器中,控制单元通常由指令解码器和控制逻辑组成。

指令解码器将二进制指令解码为对数据路径的控制信号。

控制逻辑基于解码的指令生成控制信号。

在实现CPU系统之前,我们需要设计指令的编码方式。

在本例中,我们将使用定长编码,每个指令都有相同的长度,例如8位。

现在我们可以开始实现CPU系统。

我们可以使用硬件描述语言(HDL)来描述和实现CPU系统的各个部分。

常用的HDL包括VHDL和Verilog。

我们可以使用仿真工具来验证CPU系统的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

control mode---combination logic

ir[7:0]------Instruction Register 单字节指令

ir[7], ir[6]-----2 bit operation code (I7,I6)

ir[5:0]------6 bit address 直接寻址

Acc[7:0]------accumulator register

(addr) => acc

CASEX = 5’b 00 10 x !sel_to_oa 发rc

{2’b00,ir[5:0]}→ o_a, M →o_d ADD, !sel_acc_in, en_acc, !ck

{1’b0,acc}+{1’b0,o_d} → {cy,acc}

CASEX = 5’b 01 10 x sel_to_oa

T

t0

3T

t1

T

f /3

本时序属保守型

f /6描述框图 (行为对象)

o_d[7:0] sel_pc_in

外部 数据 总线

复位 启动 首地址

转移

ir_en

pc_ld pc_add_1

!ck

sel_to_oa

pc 取指

reset [7:0]

!ck ir [7:0]

o_a[7:0] 外部 地址 总线

casex = {ir[7:6], t, cy}

wr

!(wc & ck)

rc !ck

5’b 5’b

xx 0x

01 10

x x

的非

ir_en

pc_add_1 sel_pc_in 5’b xx 01 x sel_to_oa

pc_ld

5’b 11 10 0

sel_acc_in 5’b 01 10 x acc_en 5’b 0x 10 x

q[1] <= q[0];

q[2] <= q[1];

end

end

always @(posedge ck0) begin if ((cyc==2'b11) | (cyc==2'b00)) begin cyc <= 2'b01 & !reset; end else begin cyc[0] <= cyc[1] & !reset; cyc[1] <= cyc[0] & !reset; end end

第二章 CPU设计概论

❖2.0.0 从最简的4条指令CPU, 看 CPU的设计(verilog)与测试验证

固定2周期、冯诺曼型、复位启动、D/A分用 ADD 整数加法 LDA 取数 STA 存数 JNC 非进位转移

最简的4条指令CPU设计

❖ 2.0.1 4条指令CPU的指令格式与功能:自定义

design of CPU--4 item instruction, 2 cycle, Data 8 bit

ir[7] ir[6] instruction operation

0 0 ADD Acc, addr Acc <= (Acc) + (addr) 要先取数到Acc

0 1 LDA Acc, addr Acc <= (addr)

1 0 STA addr, Acc addr <= Acc

1 1 JNC addr

指令 汇编符

指令 码 地址(6位) 76 543210

加法 ADD addr

00 xxxxxx

取数 LDA addr

01 xxxxxx

送存 STA addr

10 xxxxxx

非进位转移 JNC addr

11 xxxxxx

指令功能

指令执行周期微操作及其控制信号与CLK

t[1]

说明

(acc)+ (addr) => acc 注:作加法要先 将第一操作数取 到累加器

ADD wc

5’b 00 10 x 5’b 10 01 x

❖ 2.0.5 4条指令CPU的指令微操作流程图

取指令

t[0]操作

CASEX= 5’b xx 01 x sel_pc_in sel_to_oa pc → o_a

发rc M → o_d ir_en, !ck o_d → ir pc_add_1, !ck pc+1 → pc

always @(posedge clk)

begin

if ((q==3'b111) | (q==3'b011)

|(q==3'b110) | (q==3'b101)

|(q==3‘b000)) //非法态恢复

q <=3'b001;

else

begin

//保证CK居中

q[0] <= q[2]; //可使用↑↓

{2’b00,ir[5:0]}→o_a, 发rc, sel_acc_in, en_acc, !ck M → o_d → acc

(acc) => addr

CASEX = 5’b 10 10 x !sel_to_oa

{2’b00,ir[5:0]} → o_a 发wr,wc打开3态,写存贮器 acc → o_d → M (wr=wc&ck)

pc <= addr, when Cy=0

Cy-------------Carry of Adder

PC[7:0]--------program counter

t[1:0]---------2 cycle

ck-------------in cycle, contain clock

❖ 2.0.2 4条指令CPU的外特性

:

reset clk

CPU 4条

o_a[7:0] 外部地址总线 o_d[7:0] 外部数据总线(双向) wr 写存贮器(高有效)信号 rc 读存贮器(高有效)信号

存贮器写命令wr=~(wc&ck)

❖ 2.0.3 4条指令CPU的周期时序: 固定 2周期时序波形图

T=1/f

与指令无关

clk

f MHz

ck

2’b00,ir[5:0]

指令部件

取数 !ck

D Q cy

cn8 ADD reset

ir[7:6] cy

ck

wc

3态门 B

cl

sel_acc_in

ALU

k F

[7:0]

!ck acc

A

[7:0]

acc_en

ADD

运算器

t[1:0] wr rc

存贮器

Timer Controller Combination logic

cy=0 addr => pc

CASEX = 5’b 11 10 0 sel_pc_in, pc_ld, cy=0,!ck

{2’b00,ir[5:0]} → pc

设: CASEX = {ir[7:6],t[1:0], Cy} 复位启动:if reset=1,8’h3f → pc

❖ 2.0.5-1 4条指令CPU的指令操作:Timer描述(定义声明省略)