计算机系统综合设计

计算机系统综合课程设计实验总结

计算机系统综合课程设计实验总结一、引言计算机系统综合课程设计实验是计算机科学与技术相关专业的一门重要实践课程,旨在通过实际操作和综合实验任务,让学生全面了解计算机系统的组成和工作原理,培养学生的综合应用能力和问题解决能力。

本文旨在对该实验进行总结和回顾,介绍实验的目的、内容、实施过程和取得的成果。

二、实验目的计算机系统综合课程设计实验的目的是通过设计和实现一个简化的计算机系统,包括处理器、内存、I/O设备等,加深对计算机硬件和软件的理解,培养学生的系统思维和综合应用能力。

通过实验,学生能够掌握计算机系统的基本结构和工作原理,熟悉计算机体系结构、操作系统、编译原理等相关知识,提高自己的实践能力和创新能力。

三、实验内容本次实验的内容主要包括以下几个方面:1. 计算机系统的基本组成:学生需要了解并实现计算机系统的各个部分,包括处理器、内存、I/O设备等,理解它们之间的功能和相互作用关系。

2. 处理器设计与实现:学生需要设计并实现一个简化的处理器,包括指令集、寄存器、控制单元等。

通过设计处理器,学生能够深入理解指令的执行过程和计算机的运行机制。

3. 内存管理和地址映射:学生需要设计并实现一个简化的内存管理系统,包括地址映射、虚拟内存、分页机制等。

通过实现内存管理系统,学生能够理解内存的分配与回收原理,掌握地址映射的方法和技巧。

4. I/O设备的设计与实现:学生需要设计并实现一个简化的I/O设备,包括输入设备和输出设备。

通过设计I/O设备,学生能够了解I/O设备的工作原理和驱动程序的编写方法。

四、实施过程本次实验的实施过程主要包括以下几个阶段:1. 系统设计和规划:在实验开始前,学生需要对整个实验进行系统设计和规划,确定实验的目标、内容和实施方案。

2. 硬件和软件开发:学生根据实验的设计要求,开始进行硬件和软件的开发工作。

他们需要使用相应的开发工具和编程语言,实现计算机系统的各个组成部分。

3. 调试和测试:在开发完成后,学生需要对实验系统进行调试和测试,确保系统的功能和性能达到设计要求。

《计算机系统综合设计》计算机系统课程设计m

2 系统设计与实现

根据系统需求,设计和 实现计算机系统的各个 模块。

3 系统测试与调试

进行系统测试,并解决 系统中的错误和问题。

课程设计步骤

1

项目选择

选择一个适合的计算机系统设计项目。

需求分析

2

分析系统的需求,并编写需求文档。

3

系统设计

设计计算机系统的结构和模块。

系统实现

4

根据设计,实现系统的各个模块。

5

测试与调试

测试系统,发现并解决问题。

项目总结

6

总结项目经验,提出改进建议。

课程设计评估

笔试成绩

考察学生对计算机系统设计的理解和掌握程度。

项目成果

根据计算机系统设计项目的质量和完成程度进 行评估。

课程设计经验分享

团队合作

分享团队合作的经验和技巧, 以及如何解决合作中的问题。

问题解决

分享解决计算机系统设计中遇 到的问题的方法和心得。

《计算机系统综合设计》 计算机系统课程设计

这是一门重要的计算机系统课程,旨在培养学生设计和实现计算机系统的能 力。本课程将提供综合的设计经验和实践知识,帮助学生成为优秀的计算机 系统工程师。

课程设计目标

综合技术应用

通过设计和实现计算机系 统,提高学生的综合技术 应用能力。

问题解决能力

培养学生分析和解决实际 计算机系统问题的能力。

团队合作精神

通过合作设计项目,培养 学生的团队合作和沟通能 力。

课程设计要求

编程能力

具备扎实的编程基础和良好的 代码风格。

系统架构

理解计算机系统的各个组成部 分和它们之间的交互关系。

问题解决

能够分析和解决复杂的计算机 系统问题。

翟玉庆 东南大学计算机学院

数字逻辑电路实验 微型机与接口技术 课程实验 计算机系统综 合课程设计 科研实践 毕业设计 硬件实验

6

引入课程设计的重要性

• • • • 通过综合实践提高动手能力 通过小组合作学会与人沟通 通过实际问题提高分析能力 通过开放课题学会探索研究

7

计算机系统综合课程设计

•

– – –

课程目标

提高学生的计算机系统综合认识能力 培养学生基于系统优化应用的思维意 识 提高学生的创新能力

•

– – –

存在问题

由于采用全程跟踪和答辩式验收方 法,教师投入的精力很大 助教协助力量不够 学生能力参差不齐,给系统综合课程设计

•

– –

建设计划

完善课程设计框架,适应分类培养需 要 争取成为国家精品课程

21

计算机系统综合课程设计

•

– – –

课程资源

计算机系统综合课程设计网站截图.doc

– –

14

计算机系统综合课程设计

•

–

• • • •

措施

四个开放

开放的实践环境 开放的设计方法 开放的目标要求 开放的评价体系

–

• • • •

四个不限定

不限定学生设计的总体结构 不限定学生具体实施设计的步骤 不限定最终的目标与验证方法 不限定学生实施自己设计的时间和地点

–

教师全程跟踪,加强验收管理

15

/zhkcsj/index.htm

学生作品实例 教材目录

22

今后的工作

• • • 加强实践环节师资和助教力量 以课程设计为切入点,优化实 践教学体系建设 强化实践考核环节,探索更好 的实践考核方法

23

谢谢!

17

计算机系统综合课程设计

计算机控制系统 设计

计算机控制系统设计引言计算机控制系统是一种通过计算机对特定设备或过程进行控制和监测的系统。

计算机控制系统广泛应用于工业自动化、交通运输、通信等领域,可以提高生产效率和产品质量,减少人力成本和人为错误。

本文将介绍计算机控制系统设计的基本原理和步骤,包括硬件设计、软件设计和系统集成等方面的内容。

硬件设计计算机控制系统的硬件设计是指选择合适的电子元器件和设计电路来实现控制系统的功能。

硬件设计通常包括以下几个方面:1. 选择合适的控制器控制器是计算机控制系统的核心组成部分,负责接收输入信号、处理数据并输出控制信号。

常见的控制器有微处理器、PLC(可编程逻辑控制器)等。

在选择控制器时,需要考虑控制系统的需求和性能要求。

2. 传感器和执行器选择传感器和执行器用于将实际物理量(如温度、压力、位置等)转换为电信号或控制信号。

在硬件设计中,需要选择适合的传感器和执行器,并设计相应的电路来与控制器连接。

3. 电源电路设计电源电路是提供控制系统所需的电能的基础设施,需要设计合适的电源电路来保证控制器和其他电子元器件的正常工作。

软件设计软件设计是计算机控制系统中不可或缺的一部分,它通过编写计算机程序来实现控制系统的逻辑功能。

软件设计主要包括以下几个方面:1. 确定系统需求在进行软件设计之前,需要明确系统的功能需求和性能要求。

这些需求可以通过系统规格说明书、用户需求分析等方式来获取。

2. 设计控制算法控制算法是计算机控制系统的核心部分,它决定了系统如何对输入信号做出反应并生成相应的控制信号。

在软件设计中,需要根据系统需求和控制原理设计合适的控制算法。

3. 编写程序在设计控制算法之后,需要将算法转化为实际的计算机程序。

程序可以使用各种编程语言来实现,如C、C++、Python 等。

编写程序时需要考虑可读性、可维护性和性能等方面的因素。

系统集成系统集成是将硬件设计和软件设计进行整合的过程,目的是确保计算机控制系统的各个组成部分能够正常协同工作。

基于RISC-V的计算机系统综合实验设计

计算机工程与设计COMPUTER ENGINEERING AND DESIGNApr.2021Vol.42 No.42021年4月第42卷第4期基于RISC-V 的计算机系统综合实验设计孙卫真1!刘雪松朱威浦2 !向 勇3 +(1首都师范大学 信息工程学院,北京100048; 2.中国科学院计算技术研究所,北京101407;3.清华大学 计算机科学与技术系,北京100084)摘要:针对目前高校计算机系统各课程实验衔接不紧密、实验成本较高的问题!提出设计基于小型FPGA 开发板、以 RISC-V CPU 和Rut 操作系统内核为核心的计算机系统综合实验平台。

硬件实验以在低成本FPGA 芯片上搭建picorv32 RISC-V CPU 为核心!软件实验以在硬件实验基础上移植Rut 编写的rCore 教学操作系统为核心。

以较低成本在同一平台 完成计算机组成原理与操作系统实验设计!使其形成一个有机的整体,在资源与成本有限的情况下构建一个较为完整的实验体系。

实例结果表明!实验平台以软硬件协作的方式,适应技术的发展!及时更新实验内容!可满足高校计算机系统教学综合实验的基本要求。

关键词:RISC-V &系统编程语言;组成原理实验&操作系统实验&软硬件协作中图法分类号:TP301 文献标识号:A 文章编号:1000-7024 (2021 041159-07doi : 10. 16208/j. issnl 000-7024. 2021. 04. 037De?ign for comprehen?ive laboratory of computer?y?tem ba?ed onRISC-VSUN Wei-zhen 1, LIU Xue-song 1, ZHU Wei-pu 2, XIANG Yong 3+(1. I n f o r m a t i o n E n g i n e r i n g C o l e g e , C a p i t a l N o r m a l U n i v e r s i t y # B e i j n g 10048, C h i n a ;2. I n s t i u t e o f C o m p u t i n g T e c h n o l o g y , C h i n e s e A c a d e m y o f S c i e n c e s , B e i j n g 101407 , C h i n a ;3. Department of Computer Science and Technology , Tsinghua University , Beijing 100084 , China)Abstract: A i m i n g a t r y i n g t o i m p r o v e t h e e x p e r i m e n t a l c o n e c t i o n a m o n g t h e c o m p u t e r s y s t e m c o u r s e s i n t h e u n i v e r s i t e s a n d r e - d u c e t h e x p e r i m e n t c o s t #a c o m p r e h e n s i v e c o m p u t e r s y s t e m e x p e r i m e n t a l p l a t f o r m b a s e d o n a s m a lF PG Ab o a r d a n d a t e a c h i n g o p e r a t i o n s y s t e m w a s p r o p o s e d . T h e h a r d w a r e e x p e r i m e n t w a s b u i l d i n g a s y s t e m o n c h i p (S o C ) w i t h p i c o r v 32 R I S C -V C P U o n a l o w -c o s t F P G A c h i p . T h e s o f t w a r e e x p e r i m e n t w a s t r a n s p l a n t i n g t h e r C o r e t e a c h i n g o p e r a t i o n s y s t e m w r i t e n b y R u s t o n t h e i r o w n S o C . T h e c o m p u t e r c o m p o s i t o n p r i n c i p l e a n d o p e r a t i o n s y s t e m e x p e r i m e n t a l d e s i g n o n t h e s a m e p l a t f o r m a t a l o w e r c o s t wa s F o m p l e t e d #a n d a n o r g a n i F w h o l e w a s f o r m e d . T h e e x p e r i m e n t a l s y s t e m w a s a r e l a t i v e F o m p l e t e p l a t f o r m w i t h l i m i t e d F o s t s . E x a m p l e s h o w t h a t #t h e x p e r i m e n t a l F o n t e n t s a r e t i m e l y u p d a t e d f o r t r a F i n g F o m p u t e r t e F h n o l o g y t r e n d s i n a s o f t w a r e -h a r d - w a r e c o p e r a t i v e m a n e r t o m e t h e b a s i c r e q u i r e m e n t s o f c o m p u t e r s y s t e m t e a c h i n g e x p e r i m e n t s i n u n i v e r s i t e s .Keywords :RI S C -V ; s y s t e m p r o g r a m mi n g l a n g u a g e ; c o m p o s i t o n p r i n c i p l e e x p e r i m e n t ; o p e r a t i n g s y s t e m e x p e r i m e n t ; s o f t w a r e h a r d w a r e c o p e r a t i v e4引言目前,高校进行计算机系统教学实验主要有以下几种教学方式:其一是使用纯硬件搭建实验平台,虽该方式可深入接触计算机硬件模块,但实验操作机械死板、硬件平台开发成本较高;其二是采用软件系统仿真的方式,该方法成本较低、易于上手,但受教育者不能在实验过程中较好体会到计算机与硬件的紧密结合!为了优化上述问题,实现设计目标,本文从硬件支持、 处理器构建、系统编程语言选择三方面考虑,构建计算机 系统实验平台。

系统的总体设计方案

• 4.软、硬件选择

• 根据系统需要和资源约束,进行计算机软、 硬件的选择。计算机软、硬件的选择,对 于管理信息系统的功能具有很大影响。大 型管理信息系统软、硬件的采纳可以采用 招标等方式进行。

• 软件的选择包括操作系统,数据库管理系 统,汉字系统,设计系统,设计语言和应 用软件包等软件的选择。

• 随着计算机科学与技术的飞速发展,计算 机软、硬件的升级与更新速度也很快。新 系统的建设应当尽量避免先买设备,再进 行系统设计的情况。

• (4)选择调用 • 在分类查询模块的箭头尾部标有一个菱形

符号。表示选择调用,如果条件为真,则 调用按A模块,为假时调用B模块。如图520所示5)循环调用 • 当一个模块M反复地调用模块A和模块B时,

在调用箭头尾部则标以一个弧形符号。如 图5-21所示。

M

A

B

• 模块、调用、信息传递这三种符号是结构 图的基本符号,选择调用、循环调用这两 种符号是附加符号。

计算机网络系统的设计主要包括中小型主机方案与微机网络方案的选取网络互连结构及通信介质的选型局域网拓朴结构的设计网络应用模式及网络操作系统的选型网络协议的选择网络管理进程用户等工作

欢迎

系统设计要求

1.简明性 2.灵活性和适应性 3.完整性 4.可靠性 5.安全性 6.经济性

系统功能结构的划分

管理信息系统的各子系统可以看作是 系统目标下层的功能。对其中每项功能还 可以继续分解为第三层、第四层……甚至 更多的功能。

这也是输入设计的一项重要内容。输 入设计最重要的问题是保证输入数据的正 确性。对数据进行必要的校验,是保证输 入正确的重要环节。

输入格式设计

输入设计的重要内容就是设计好原始 单据的格式。 设计原始单据的原则是: (1) 便于填写 (2) 便于归档。 (3) 单据的格式应能保证输入精度。

计算机网络综合布线系统设计

浅谈计算机网络综合布线系统设计摘要:随着计算机网络布线系统在我国社会各个领域中的广泛应用,系统所具备的功能也得到了相关部门的高度重视,在科学技术快速发展的今天,传统的计算机网络布线已经无法满足目前各个领域的发展需求。

综合布线系统作为一种标准通用的信息传输系统,目前已经逐步取代了传统的计算机网络布线。

本文通过对传统布线中存在的问题进行分析,并在此基础上比较传统布线与结构化布线之间的区别,从而结合综合布线系统设计的原则介绍其设计方案在生活中的实际应用情况。

关键词:计算机网络;综合布线;系统设计随着我国互联网技术的不断发展,各个领域对计算机网络布线系统也提出了较高的要求。

为了能够充分满足各个领域的需求,采用综合布线系统来对计算机网络进行设计是不容忽视的。

综合布线系统指的是按照标准的、统一的和简单的结构化方式对建筑物内的通信线路进行科学合理的编制和布置,从而达到对通信线路进行优化和完善的目的,使其作用能够更好的发挥出来,以此来促进社会各个领域的可持续发展。

一、传统布线中存在的问题计算机网络传统布线缺少先进技术和设备的支持,虽然也能够在一定程度上具备相关领域所需的功能,但是随着科技不断发展,传统布线呈现出来的问题也越来越明显。

这些问题主要表现在以下几个方面:1.1各个专业设计之间无法有效协调在计算机网络布线的线路上,涉及了许多不同的专业,而且各个专业之间均存在着密不可分的联系,如果想要整个布线系统正常运行,就必须保证各个专业之间协调一致。

但就传统的网络布线而言,各个专业之间存在过多的牵制,无法实现有效协调,从而导致设施的管道错综复杂,相关工作人员如果想要制定出一套妥善的方案,就必须对设计图纸进行多次汇总,不仅浪费时间,而且最终的方案也不尽人意。

1.2布线成本高在计算机网络布线过程中,由于各个专业无法达到协调一致,从而导致在布线的时候时常会出现重复施工的情况,这样不仅在很大程度上造成了人员的浪费,而且还会造成材料的大量浪费,增加了计算机网络布线的成本。

系统 设计

系统设计系统设计是指对计算机系统进行全面的规划和设计,以满足用户需求和系统要求的过程。

这个过程主要包括以下几个方面:1. 需求分析:系统设计的第一步是对用户需求进行分析和理解。

这包括与用户和相关利益相关者交流,了解他们的需求,目标和期望。

通过需求分析,确定系统的功能需求、性能需求、安全需求等。

2. 架构设计:在系统设计的过程中,架构设计是一个重要的步骤。

架构设计确定系统的整体结构,包括组件的划分、模块之间的关系和接口设计等。

架构设计需要综合考虑系统的可扩展性、可维护性、可靠性等方面的要求。

3. 数据设计:在系统设计中,数据设计是一个关键的环节。

数据设计包括对数据模型的设计和数据库设计。

通过数据设计,确定系统中的数据结构、数据的存储方式和访问方式等。

4. 接口设计:系统设计还涉及接口的设计。

接口设计包括系统与外部系统的接口和内部模块之间的接口。

在接口设计中,需要考虑接口的可用性、安全性和可扩展性等方面的要求。

5. 系统安全设计:安全设计是系统设计中的一个重要方面。

系统安全设计包括用户身份认证、访问控制、数据加密等。

通过系统安全设计,确保系统在设计和实施阶段都能够有效保护用户的数据和系统的安全。

6. 软件设计:在系统设计中,还需要进行软件设计。

软件设计包括对软件架构、算法和数据结构等的设计。

通过软件设计,确保系统的软件能够满足用户需求,并具有良好的性能、可扩展性和可维护性。

7. 测试设计:在系统设计的过程中,还需要进行测试设计。

测试设计包括对系统的功能进行测试和性能测试。

通过测试设计,确保系统在实际运行中能够正确、高效地工作。

通过以上的系统设计过程,可以确保系统能够满足用户需求,并具备良好的性能、可靠性和安全性。

系统设计是一个复杂的过程,需要综合考虑多个方面的需求和要求。

因此,在系统设计过程中需要认真分析和理解用户需求,并通过合理的设计来实现系统的要求和目标。

计算机一体化课程设计

计算机一体化课程设计一、教学目标本课程旨在让学生掌握计算机一体化课程的基本知识和技能,培养学生的计算机操作能力和信息素养。

具体目标如下:1.知识目标:使学生了解计算机的基本概念、原理和应用,掌握操作系统、办公软件、网络通信等基本操作技能。

2.技能目标:培养学生能够熟练运用计算机解决实际问题,提高学生的创新能力和实践能力。

3.情感态度价值观目标:培养学生对计算机科学的兴趣和好奇心,增强学生的信息安全和隐私保护意识,培养良好的信息技术使用习惯。

二、教学内容本课程的教学内容主要包括以下几个部分:1.计算机基础知识:计算机概述、硬件系统、软件系统、数据通讯与网络基础。

2.操作系统:Windows、Linux、macOS等操作系统的使用和管理。

3.办公软件:Microsoft Office、WPS Office等办公软件的应用技巧。

4.网络通信:Internet的基本概念、网络协议、网络安全与防护。

5.程序设计:C语言、Python等编程语言的基础知识和应用。

三、教学方法为了提高教学效果,本课程将采用多种教学方法相结合的方式进行教学:1.讲授法:通过讲解计算机基本概念、原理和操作方法,使学生掌握相关知识。

2.讨论法:学生针对实际问题进行讨论,培养学生的思维能力和解决问题的能力。

3.案例分析法:通过分析典型案例,使学生了解计算机技术在实际应用中的作用。

4.实验法:安排实验室实践环节,让学生动手操作,提高实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用权威、实用的教材,为学生提供系统、全面的学习资料。

2.参考书:提供相关的参考书籍,丰富学生的知识储备。

3.多媒体资料:制作精美的PPT、教学视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:配备计算机、网络设备等实验设备,为学生提供实践操作的机会。

五、教学评估为了全面、客观地评估学生的学习成果,本课程将采用以下评估方式:1.平时表现:通过观察学生的课堂表现、参与度、小组合作等,评估学生的学习态度和积极性。

计算机网络综合布线设计方案

某某市政务网系统设计需求某某大学职业技术学院设计人员:一. 概述:1.市委机要局机房作为整个网络的中心机房,为了保证网络的安全和保密性从市到区县均采用电信提供的专线连接。

2.其中市到4个区县都是电信专线SDH线路。

3.市级用户包含市委市政府两栋大楼里的所有用户。

原来的网络为大家上互联网用的,为了网络安全,本次局域网内网系统,全部新建。

1号办公大楼有6层,楼层高为3米,楼长度为60米,每层用户数量为在75个信息点,其中网络中心设在3层中间的房间。

2号办公大楼为5层,楼层高为3米,楼长度为70米,每层用户数量为55个信息点。

4.县级用户包含县委、县政府两栋楼。

每栋楼有4层,每层楼用户数量大概在20人左右。

二、设计原则市区的结构化综合布线系统(PDS)的建设是一个综合的、统一的信息系统工程,将满足当前和将来网络通讯技术的发展,实现语音、数据和图像信息的传输。

本方案将提供全面完整和可扩展性强的解决方案,以实现系统实施灵活性和连贯性。

方案在设计中充分理解用户对智能化工程建设的要求,对系统现在以及将来的应用及连接需求进行综合分析,在系统需要扩容和扩展时而进行下一步实施时,可以方便并且平滑的实现。

三、综合布线示意图(只要求市委市政府)四.网络拓扑结构图图纸说明江州市政务系统,数据中心放置在1号办公楼的3楼,是整个江州市政府网络的核心,包括核心交换机和服务器以及出口路由器。

因此是建设的重点,为了增加带宽,提高访问速度,数据中心的主要网络设备都采用光纤连接。

备及链路冗余,把各县区的路由出口设备都连接到核心防火墙上以提高整个网络的安全性和可靠性。

Web、FTP、WINS、DHCP、DNS服务器的主要数据都是存放在与其相连的数据库服务器上,数据服务器内的大容量磁盘阵列可以很好的满足服务器的需求,其中个服务器与核心防火墙相连。

数据中心到江州市下辖各县都是通过租用电信的dhc专线,这样可以提供数据的保密性。

因为是远程连接,所以数据中心到各县采用路由器而不采用交换机。

计算机系统综合设计实验报告

《计算机系统综合设计》报告目录1.设计目标 (2)2.1 分析启动引导代码 (2)2.1.1 设计方案 (2)2.1.2 实现方法 (3)2.2 mips汇编算法分析 (5)2.2.1设计方案 (5)2.2.2 实现方法............................................................................................... 错误!未定义书签。

2.3 GPIO设计 (6)2.3.1设计方案 (6)2.3.2 实现方法............................................................................................... 错误!未定义书签。

2.4 UART3 输入输出 (7)2.4.1设计方案 (7)2.4.2 实现方法............................................................................................... 错误!未定义书签。

2.5 交叉调用(GPIO输入串口输出) (7)2.5.1 设计方案 (7)2.5.2 实现方法............................................................................................... 错误!未定义书签。

2.6 RT-Thread 操作系统开发 (7)2.6.1 设计方案 (7)2.6.2 实现方法............................................................................................... 错误!未定义书签。

3.1 分析启动引导代码 (7)3.2 mips汇编算法分析 (8)3.3 GPIO 设计 (8)3.4 UART3 输入输出 (8)3.5 交叉调用(GPIO输入串口输出) (8)3.6 RT-Thread 操作系统开发 (9)4.设计结论 (9)1.设计目标该设计要完成的主要内容,包括:(1)分析启动引导代码(2)mips汇编算法分析(3)GPIO输入输出(4)UART3输入输出(5)RT-Thread操作系统开发2.设计实现2.1 分析启动引导代码2.1.1 设计方案学习MIPS指令集,参考mips32-instructions.pdf文件,结合运行结果理解代码,对启动引导代码start.s文件进行注释2.1.2 实现方法2.2 mips汇编算法分析2.2.1设计方案用mips汇编语言完成完全树的中序遍历算法,c++语言的二叉树的前序遍历的非递归形式如下:2.3 GPIO设计2.3.1设计方案将LED灯、开关与电路板自选端口连接,设计c语言代码实现通过开关控制流水灯效果,按键后每个小灯依次发光500ms开关接AC97_DI[36]2.4 UART3 输入输出2.4.1设计方案在main.cpp文件主函数main() 中使用printf() 函数,由于此文件中包含了头文件stdio.h所以会跳转到stdio.h中。

武汉工程大学《计算机操作系统课程设计报告》附录源码

武汉工程大学计算机科学与工程学院综合设计报告设计名称:操作系统综合设计设计题目:进程同步与死锁学生学号:专业班级:学生姓名:学生成绩:指导教师(职称):张立(讲师)完成时间:14年2月17日至14年2 月28日武汉工程大学计算机科学与工程学院制说明:1、报告中的第一、二、三项由指导教师在综合设计开始前填写并发给每个学生;四、五两项(中英文摘要)由学生在完成综合设计后填写。

2、学生成绩由指导教师根据学生的设计情况给出各项分值及总评成绩。

3、指导教师评语一栏由指导教师就学生在整个综合设计期间的表现、设计完成情况、报告的质量及答辩等方面,给出客观、全面的评价。

4、所有学生必须参加综合设计的答辩环节。

凡不参加答辩者,其成绩一律按不及格处理。

答辩小组成员应由2人及以上教师组成。

5、报告正文字数一般应不少于5000字,也可由指导教师根据本门综合设计的情况另行规定。

6、平时表现成绩低于6分的学生,其综合设计成绩按不及格处理。

7、此表格式为武汉工程大学计算机科学与工程学院提供的基本格式(适用于学院各类综合设计),各教研室可根据本门综合设计的特点及内容做适当的调整,并上报学院批准。

答辩记录表成绩评定表学生姓名:学号:班级:五、Abstract:Process synchronization and deadlock is the operation of the main learningsystem research, synchronization between the process system process is a direct interaction between processes, is a cooperative process conscious behavior.However, there is a sync relationship between consumers and producers oftypical example, only by producers to produce products, consumer to consumer,between consumers and producers of action need certain coordination. Similarly,the two process is sometimes also have such a dependency, it should be certainthat their synchronization mechanism execution order.Bankers algorithm Dijkstra is the most representative of the algorithm to avoid deadlock, this algorithm can be used for the banking system because of its cashloans. Bankers algorithm is advancing in the premise to ensure the system security. The first securitycheck to process requests, to determine the allocation of resources or not, so as to ensure the safety of the system, avoid deadlock.Research on resource allocation strategies in the operating system also have similar problems, the system of limited resources for multiple processes, mustguarantee the resources of the process to return the resource in limited time, for other processes resources. If the resource is not allocated by the process ofcircular waiting for resources will occur, the process cannot continueto executethe deadlock phenomenon.On the understanding and analysis of the essential meaning of process synchronization and deadlock the core thought as well as the state of thealgorithm, the realization of design in general, including in the design ofalgorithms, and each algorithm module ideas through a flow chart, block code,and test, and finally program test. The design is a simple simulation program by compiling and debugging a system dynamic allocation ofresources,synchronization and deadlock observation conditions, and by using the appropriate algorithm, effectively prevent and avoid deadlock occurred目录摘要 (II)Abstract (III)第一章课题背景 (1)1.1 课题背景及目的 (1)1.2 课题内容及分析 (1)第二章设计简介及设计方案论述 (2)2.1 设计简介 (2)2.2 设计方案论述 (2)2.3 设计流程图 (3)第三章详细设计 (6)3.1 算法思想 (6)3.1.1基本思想 (6)3.2算法描述及数据结构 (6)3.2.1生产者/消费 (6)3.2.2银行家算法 (6)第四章设计结果及分析 (7)4.1 生产者/消费者调试界面 (7)4.1.1 主程序界面 (7)4.1.2 菜单界面 (7)4.2 银行家算法调试界面 (9)4.2.1 主程序界面................................................................................................ . (9)4.2.2 菜单界面 (10)总结 (12)致谢 (13)参考文献 (14)附录主要程序代码 (15)摘要进程同步与死锁是操作系统研究中主要的学习课题,多进程的系统中进程之间的同步关系是进程之间直接的相互作用,是合作进程间有意识的行为。

基于微程序控制器的《计算机系统综合设计》课程设计指导书

基于微程序控制器的《计算机系统综合设计》课程设计指导书计算机科学与技术学院计科教研室基于微程序控制器的简单机器指令的设计是在TEC-8实验箱上完成的,因此,要求学生必须深刻理解TEC-8实验箱所包含的主要硬件模块的工作原理:算术逻辑单元ALU、双端口寄存器组、数据开关SD7~SD0、双端口RAM、程序计数器PC、地址寄存器AR、指令寄存器IR、微程序控制器、控制信号切换电路、2选1选择器以及与这些模块相对应的指示灯等,详细内容参见TEC-8实验箱实验指导书。

下面就与课程设计相关的重点内容扼要介绍一下。

一、基于微程序控制器的机器指令的执行原理指令周期:取指周期+执行周期,无论是取指周期还是执行周期,都包含了多个微操作,即多个微控制信号。

对所有指令来说,指令的取指周期所包含的控制信号是完全一样的,而执行周期中的控制信号,则因指令而异。

二、TEC-8实验箱电路逻辑图三、指令格式1、TEC-8实验箱原有的指令2、课程设计拟新增加的指令四、TEC-8实验箱的控制信号根据机器指令功能、格式和数据通路所需的控制信号,TEC-8采用如上图所示的微指令格式。

微指令字长40位,顺序字段11位(判别字段P4~P0,后继微地址NµA5~NµA0),控制字段29位,微命令直接控制。

判别字段P4~P0的功能如下表。

下面分析根据后继微地址NµA5~NµA0、判别位P1和指令操作码如何实现微程序分支的。

微地址01H中的微指令是一条功能为取指令的微指令,在T3的上升沿,从双端口存储器中取出的指令写入指令寄存器IR。

在这条微指令中,后继微地址为20H,判别位P1为1、其他判别位均为0。

因此根据微地址转移逻辑,很容易就知道,下一条微指令的微地址是:NµA5-T = NµA5NµA4-T = NµA4NµA3-T = NµA3 or P1 and IR7-INµA2-T = NµA2 or P1 and IR6-INµA1-T = NµA1 or P1 and IR5-INµA0-T = NµA0 or P1 and IR4-I新产生的微地址NµA5-T~NµA0-T在T3的下降沿写入微地址寄存器µAR,实现了微程序流程图图所要求的根据指令操作码进行微程序分支。

计算机综合信息系统的设计与开发

计算机综合信息系统的设计与开发作者:刘鸿旗王海龙来源:《科技资讯》 2011年第33期刘鸿旗1 王海龙2(1,内蒙古阿拉善太西煤集团股份有限公司内蒙古阿拉善 750329;2,内蒙古阿拉善经济开发区气象局内蒙古阿拉善 750336)摘要:为了适应变化的形势获得竞争优势,各单位需要不断引进新的技术和管理手段,而稳定可靠的计算机综合信息系统,可以提高办公效率,减少单位开支,随着现代计算机技术的不断更新和进步,利用计算机综合信息系统对综合信息进行处理,可以最大限度的减轻相关管理人员工作方面的工作量。

关键词:计算机综合信息系统 jsp struts hibernate oracle计算机综合信息系统的目的是为了方便各个企事业单位中各职能部门间能快速准确的传达信息,进行信息的交互。

在功能方面实现部门间可以快捷的进行信息交流,信息发布、文件的上传下载等。

设计该系统的目的是为了减少不必要的工作量、提高管理的工作效率。

1 系统开发技术计算机综合信息系统是基于B/S结构的服务系统,它的开发主要采用JSP、struts2、hibernate等编程技术,结合后台数据库oracle 10g综合应用完成本系统。

利用UML建模技术,实现用户的功能描述。

以上技术相结合,较好的完成了计算机系综合信息系统。

2 系统的分析与设计本计算机系综合信息系统主要分为前台界面框架、信息发布管理、业务管理、文件上传下载、系统管理、用户管理这六大模块。

根据本系统服务对象的不同,本系统分为上级部门、下级部门、管理员三种用户。

下级部门可以对自己的基本信息进行查看和修改,查看文件列表并选择相应文件进行下载及操作等;上级部门可以对自己的基本信息进行查看和修改,发布单位内部最新动态及实时任务,对下级部门的工作进行在线考核等;管理员可以对系统功能进行开启或关闭,批量录入单位工作人员的信息,实现各部门之间信息的互通,上传相应的文件和发布相关的信息等。

2.1 系统的需求与分析基于不同用户对象的应用程序是不一样的,用户对象包括上级部门、下级部门和管理层。

计算机综合课程设计实验平台建设及应用

Ex e i nt lTe h l g n a a e e t p rme a c no o y a d M n g m n

Vo _ 6 NO 1 Oc .2 0 l2 . 0 t 0 9

计算 机 综合 课 程 设 计 实验 平 台建 设 及应 用

吴 强 , 全 胜 , 晓 蔚 杨 王

ma ge e s tm f r c na m nt yse o om pu e c m pr he i e ou s de i a t e tr o e nsv c r e sgn nd h de i o e pe i e pltor sgn f x rm nt a f m t O sr n he t e i biiy,i no tv o ius e s,a o p e nsv a iy ofs u n s t e gt n he d sgn a lt n vai e c nso n s nd c m r he ie qu lt t de t . K e r s:c m pr he i our ede in; S C ;i e a e r w a e a o t r y wo d o e nsve c s sg O nt gr t d ha d r nd s f wa e;t a hig m o e c n de

不仅 是 指 大型 机计 算 机 、 个 人 计 算 机 , 表 现 在 机 或 也 群系统 , 以及 广 泛应 用 于 工业 、 民用 等领 域 中 的 嵌入 式 系 统 中 。整个 计 算 机 系 统 的 开 发 不 仅 包 含 了单 个 或 多个 C U、 关 接 口 电路 , 包 含 了 操 作 系 统 、 P 相 也 网

I S 1 02 S N 0

. . . . . . . . . . . . . . . . . . . . . . . . . .

数电实验丨模型机(CPU)综合设计报告

简易计算机系统综合设计设计报告一、设计目的完整、连贯地运用《数字逻辑》所学到的知识,熟练掌握EDA工具基本使用方法,为学习好后续《计算机原理》课程做铺垫。

二、设计内容①按照给定的数据通路、数据格式和指令系统,使用EDA工具设计一台用硬连线逻辑控制的简易计算机;②要求灵活运用各方面知识,使得所设计的计算机具有较佳的性能;③对所设计计算机的性能指标进行分析,整理出设计报告。

④设计出各个部分的分部件,包括:时序部件:指令寄存器IR,C寄存器,Z寄存器,指令计数器PC,时钟SM,通用寄存器组,IN部件,OUT部件,存储器RAM组合部件:ALU、指令译码器,控制器,位移逻辑,3-1多路复用器。

三、详细设计3.1设计的整体架构3.1.1整个模型机分为14个模块,由若干个时序部件模块、组合逻辑电路模块以及三态门、逻辑门组成。

其中时序部件模块有SM、指令寄存器IR,存储器RAM、指令计数器PC、通用寄存器G_REGISTER、IN模块、OUT模块、Zf模块、Cf模块,组合逻辑电路模块有8重3-1多路复用器、指令译码器command_decoder、控制信号模块CTL、ALU、移位逻辑。

设计的模型机原理图如下:3.1.2数据格式与指令系统3.1.2.1数据格式数据字采用8位二进制定点补码表示,其中最高位(第7位)为符号位,小数点可视为最左或最右,其数值表示范围分别为:-1≤X<+1或-128≤X<+127。

3.1.2.2寻址方式指令的高4位为操作码,低4位分别用2位表示目的寄存器和源寄存器的编号,或表示寻址方式。

共有2种寻址方式。

⑴寄存器直接寻址当R1和R2均不是“11”时,R1和R2分别表示两个操作数所在寄存器的地址(寄存器编号),其中R1为目标寄存器地址,R2为源寄存器地址。

R1或R2的值指定的寄存器00A寄存器01B寄存器10C寄存器⑵寄存器间接寻址当R1或R2中有一个为“11”时,表示相应操作数的地址在C寄存器中。

计算机课程设计报告(模板)

计算机综合课程设计报告( 2012 -- 2013 学年第一学期)课程名称:计算机综合课程设计题目:院系:班级:组号:组长:组员:指导教师:小组成绩:日期:年月日计算机综合课程设计任务书一、提交文档要求1、每组提交课程设计报告:包括:设计目的、要求、开发的组织过程(并着重说明小组在整个开发过程中的组织、协调、开发方案、算法等变动情况)、使用的开发环境、系统开发计划(包括:系统规划、功能、任务量估算、人员安排、进度等)、系统分析、系统设计、系统编程和调试的过程说明、最终本系统解决的问题、系统使用说明书(包括功能介绍,系统安装与配置,数据库设置,系统运行、操作界面说明,操作过程说明,异常情况操作说明等)。

2、每组提交最终完整的程序(软件)代码(要求在关键变量、函数、代码处有注解和说明,并可以在文档显示页面上下载,可以编译、链接和运行)-以软盘、U盘或电子文档形式提交。

3、每个人需要提供课程设计的心得体会、感想、建议、小结等(内容中必须明确写明你在课程设计中承担的工作、所发挥的作用,其余内容自由发挥,可以手写,字数不少于1000字)。

二、程序开发要求1、每个同学必须亲自编写一段程序代码,并明确所承担的开发文档内容,否则课程设计考核不及格。

2、系统原则上一般不设置用户登录界面,如果需要时,系统的登录界面,应标明各类用户名和密码,或者直接确认进入系统。

3、运行的系统中只能有一个数据库,并且和程序放在同一个目录下。

4、程序中调用数据库时,应采用相对路径,不能采用绝对路径。

如果采用ODBC,程序应能够自动设置,不能手工设置。

5、数据库、表、字段的名称和程序中的变量名称应该使用英文或易阅读的英文缩写,不能采用汉语拼音的缩写。

6、系统中所需要的数据量应该满足系统所有功能演示的要求。

三、任务分配四、考核方式由各组的组长给自己的组员(包括组长自己)打分。

评分依据是开发系统过程中的每个人承担任务的工作量、难度、作用以及提交的文档质量和程序开发的要求是否达到。

计算机网络系统设计方案

计算机网络系统计算机网络系统就是利用通信设备和线路将地理位置不同、功能独立的多个计算机系统互联起来,以功能完善的网络软件实现网络中资源共享和信息传递的系统。

通过计算机的互联,实现计算机之间的通信,从而实现计算机系统之间的信息、软件和设备资源的共享以及协同工作等功能,其本质特征在于提供计算机之间的各类资源的高度共享,实现便捷地交流信息和交换思想。

计算机网络建立的主要目的是实现计算机资源的共享。

计算机资源主要是指计算机硬件、软件与数据。

连网计算机之间遵循共同的网络协议。

稳定的计算机网络平台是建设的基础,决定了某市图书馆、档案馆、城建档案馆数字化和信息化建设水平。

本次网络上的需求主要包括:1、建设某市图书馆、档案馆、城建档案馆的外网、内网和智能化网:外网主要作为互联网和内部局域网使用,外网考虑无线全覆盖;内网主要承载各内部应用业务以及与上级内网连接。

智能化网是增强安防等级、提高内部管理水平和效率的重要手段。

2、建设安全保障体系:根据业务和办公的不同的安全级别要求以及有关政策要求,结合网络和应用实际情况,划定不同的安全域。

为保证网络系统的完整性,各套网络的核心交换机、接入交换机、无线设备等采用同一品牌。

某市图书馆、档案馆、城建档案馆网络系统是一个多业务融合的网络,符合目前的技术趋势和业界的潮流,采用星型拓扑结构的组网方式。

各部门的内网使用万兆骨干,双核心采用虚拟化技术实现全冗余备份,千兆接入技术达到用户的理想网络带宽,为用户提供优质的内网网络接入服务;外网部分使用千兆骨干单核心,千兆接入达到用户的理想带宽,为客户提供优质的外网网络接入服务。

建设一套智能化网络,使用万兆骨干,双核心采用虚拟化技术实现全冗余备份,千兆接入技术达到高速、高保真的设备监视等数据传送服务。

外网、内网及智能化网主要采用两层构架。

内网、智能化网核心层均采用2台万兆核心交换机,2台核心交换机之间采用2条光链路互联;外网核心层采用1台万兆核心交换机。

《计算机系统综合设计》计算机系统课程设计me

在课程设计中,学生被分为若干小组进行协作。通过小组内的讨论和分工,学生们的团队 协作能力得到了有效提升,这对于他们未来的工作和学习都是非常有益的。

理论知识与实践结合

本课程设计的另一个重要目标是使学生能够将所学的理论知识与实际操作相结合。通过实 际设计,学生们对计算机系统的组成和工作原理有了更深入的理解。

1 2

加强时间管理培训

在未来的课程设计中,应加入时间管理方面的培 训,帮助学生合理安排时间,确保设计进度和质 量。

分层次布置任务

根据学生技能水平的不同,分层次布置设计任务, 避免部分学生因任务过难而无法完成。

3

强化测试环节

加强对学生测试环节的监督和指导,确保学生充 分测试系统的各项功能,提高作品的质量。

04

课程设计实施过程

设计阶段

需求分析

明确设计目标,收集和分析用户需求, 确定系统功能和性能要求。

系统架构设计

根据需求分析结果,设计系统的整体 架构,包括硬件和软件结构、模块划 分等。

数据结构设计

定义系统中的数据类型、数据关系和 数据流程,设计合适的数据结构以支 持系统功能。

界面设计

设计用户界面,包括菜单、窗口、对 话框等,确保用户友好、易于操作。

应用软件

办公软件、游戏等,满足用户特定需 求。

计算机系统性能评价

运算速度

中央处理器的运算速度,影响 计算机处理任务的速度。

存储容量

存储器能够存储的数据和程序 的大小。

可靠性

计算机系统的稳定性和数据安 全保护能力。

可维护性

计算机系统的故障修复和升级 能力。

03

课程设计题目解析

课程设计题目解析

• 请输入您的内容

CPU设计

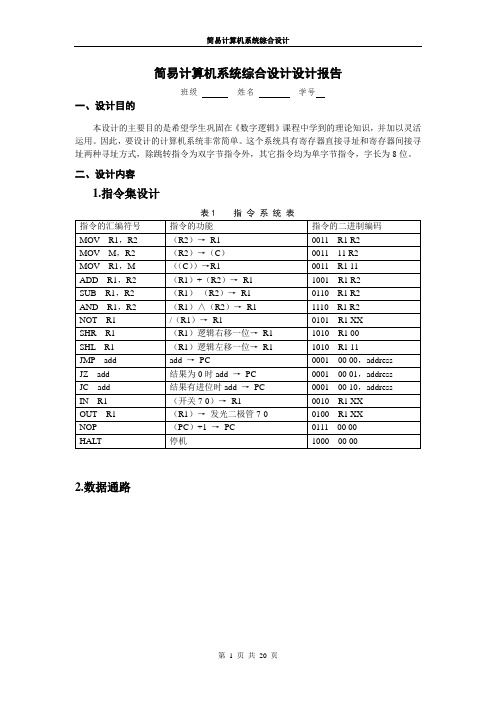

简易计算机系统综合设计设计报告班级姓名学号一、设计目的本设计的主要目的是希望学生巩固在《数字逻辑》课程中学到的理论知识,并加以灵活运用。

因此,要设计的计算机系统非常简单。

这个系统具有寄存器直接寻址和寄存器间接寻址两种寻址方式,除跳转指令为双字节指令外,其它指令均为单字节指令,字长为8位。

二、设计内容1.指令集设计2.数据通路控制信号三、详细设计3.1设计的整体架构时序电路模块–产生时钟脉冲数据通路和控制器Alu模块—alu运算顶层图如下:3.2各模块的具体实现时序电路模块:依次产生时钟脉冲t1、t2、t3、t4、t5,分别对应cpu执行的5个阶段:t1--更新pc,对应Lod PC时钟t2--加载pc,获取指令,对应Lod MARt3--译码,根据指令获得Ra,Rb,对应Lod IRt4--执行,获得Alu运算的操作数Sa、Sb,对应Lod Sa,Lod Sb t5--写回,将数据写回内存或寄存器。

语言如下:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY shixu1 ISPORT (reset : IN STD_LOGIC := '0';clock : IN STD_LOGIC;qd : IN STD_LOGIC := '0';t1 : OUT STD_LOGIC;t2 : OUT STD_LOGIC;t3 : OUT STD_LOGIC;t4 : OUT STD_LOGIC;t5 : OUT STD_LOGIC);END shixu1;ARCHITECTURE BEHAVIOR OF shixu1 ISTYPE type_fstate IS (idle,st1,st4,st2,st3,st5); SIGNAL fstate : type_fstate;SIGNAL reg_fstate : type_fstate;BEGINPROCESS (clock,reg_fstate)BEGINIF (clock='1' AND clock'event) THENfstate <= reg_fstate;END IF;END PROCESS;PROCESS (fstate,reset,qd)BEGINIF (reset='1') THENreg_fstate <= idle;t1 <= '0';t2 <= '0';t3 <= '0';t4 <= '0';t5 <= '0';ELSEt1 <= '0';t2 <= '0';t3 <= '0';t4 <= '0';t5 <= '0';CASE fstate ISWHEN idle =>IF (qd = '1') THENreg_fstate <= st1;ELSEreg_fstate <= idle;END IF;t3 <= '0';t1 <= '0';t2 <= '0';t4 <= '0';t5 <= '0';WHEN st1 =>reg_fstate <= st2;t3 <= '0';t1 <= '1';t2 <= '0';t4 <= '0';t5 <= '0';WHEN st4 =>reg_fstate <= st5;t3 <= '0';t1 <= '0';t2 <= '0';t4 <= '1';t5 <= '0';WHEN st5 =>reg_fstate <= st1;t3 <= '0';t1 <= '0';t2 <= '0';t4 <= '0';t5 <= '1';WHEN st2 =>reg_fstate <= st3;t3 <= '0';t1 <= '0';t2 <= '1';t4 <= '0';WHEN st3 =>reg_fstate <= st4;t3 <= '1';t1 <= '0';t2 <= '0';t4 <= '0';t5 <= '0';WHEN OTHERS =>t1 <= 'X';t2 <= 'X';t3 <= 'X';t4 <= 'X';report "Reach undefined state"; END CASE;END IF;END PROCESS;END BEHAVIOR;数据通路和控制器模块exp_cpu_vhd:输入:t1~t5为时钟脉冲,cout是运算所得结果的进位,zero判断所得结果是否为0,为0的话zero为1,aludata[7..0]是运算所得的结果,sw_in[7..0]是输入端;输出:newpcout[7..0]是下一个pc的值,mpcout[3..0] ,mpcc[3..0]为指令的高4位,dr1[7..0]、dr2[7..0]是传入alu的两个操作数的值,q[7..0]为out指令输出的值,bus_data[7..0]是总线上的数据,rac[7..0],rbc[7..0],rcc[7..0]为当前寄存器ra、rb、rc的值zhiling[7..0]为当前指令,pcout[7..0]是当前pc的值,saa[7..0],sbb[7..0]为当前暂存器sa、sb的值,Marr[7..0]为当前地址寄存器的值,lh2[1..0],sh2[1..0]为指令低4位的前两位和后两位,然后在数据通路和控制器里面再分模块来写语言如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity cpu_exp5 isport(t1,t2,t3,t4,t5:in std_logic;aludata,sw_in:in std_logic_vector(7 downto 0);cout,zero:in std_logic;newpcout:out std_logic_vector(7 downto 0);mpcout,mpcc:out std_logic_vector(3 downto 0);dr1,dr2,q,bus_data,rac,rbc,rcc,zhiling,pcout:out std_logic_vector(7 downto 0);saa,sbb,marr:out std_logic_vector(7 downto 0);lh2,sh2:out std_logic_vector(1 downto 0);jadd:out std_logic_vector(7 downto 0));end cpu_exp5;architecture rtl of cpu_exp5 istype ram is array(0 to 30) of std_logic_vector(7 downto 0); --30*8 ram--指令存储器寄存器ra、rb、rc初值为1、2、3. ra=1 rb=2 rc=3 signal ram8:ram:=("00110001", --mov ra,rb 0 ra=2 rb=2 rc=3 "00111000", --mov rc,ra 1 ra=2 rb=2 rc=2"00110111", --mov rb,m(rc) 2 m(2)=3 ra=2 rb=3 rc=2"10010001", --add ra,rb 3 ra=5 rb=3 rc=2"01100011", --sub ra,m(rc) 4 m(2)=3 ra=2 rb=3 rc=2"11101011", --and rb,m(rc) 5 ra=2 rb=3 rc=2"01010001",--not ra 6 ra=253 rb=3 rc=2"10100100",--shr rb 7 ra=253 rb=1 rc=2"10100011",--shl ra 8 ra=250 rb=1 rc=2"00010000", --jmp add 9"00001110", --10 -> m(14)=15"10010001", --add ra,rb 11"01100011", --sub ra,rc 12"11101011", --and rb,rc 13"01010001", --not ra 14"10010010",--add ra,rc15 ra=252 rb=1 rc=2"01100000", --sub ra,ra 16 ra=0 rb=1 rc=2"00010001", --jz add 17 ra=0 rb=1 rc=2"00001111", --18 m(16)->20"10010001", --add ra,rb 19"01010001",--no tra 20 ra=255 rb=1 rc=2"10010011", --add ra,m(rc) 21 ra=2 rb=1 rc=2"00010010", --jc add 22 ra=2 rb=1 rc=2"00010000", -- 23 ->25"01100011", --sub ra,rc 24 ra=0 rb=1 rc=2"10010001", --add ra,rb 25"00100100", --in rb 26 ra=0 rb=XX rc=2"01000001", --out ra 27"01110000", --nop 28 ra=0 rb=XX rc=2"10010001", --add 29others=>x"00"); --initialize zhiling--数据存储器signalram81:ram:=(x"01",x"02",x"03",x"04",x"05",x"06",x"07",x"08",x"09",x"0A",x"0B",x"0C",x"0D" ,x"0E",x"0F","00010100","00011001",x"05",others=>x"00"); --15 20 25--将存储器分为指令存储器和数据存储器signal mar,mar1,ir,bus_reg,bus_zhiling,next_ir:std_logic_vector(7 downto 0);signal ra:std_logic_vector(7 downto 0):="00000001";signal rb:std_logic_vector(7 downto 0):="00000010";signal rc:std_logic_vector(7 downto 0):="00000011";--pc初值为“XXXXXXXX”newpc为“00000000”signal pc:std_logic_vector(7 downto 0):="XXXXXXXX";signal newpc:std_logic_vector(7 downto 0):="00000000";signal sa,sb,sa1,sb1:std_logic_vector(7 downto 0);signal r1,r2,r22:std_logic_vector(1 downto 0);shared variable ldpc:std_logic:='0';signal mpc:std_logic_vector(3 downto 0);signal drr1,drr2,q1,jadd1:std_logic_vector(7 downto 0);beginsh2<=r2;dr1<=drr1;dr2<=drr2;q<=q1;bus_data<=bus_reg;rac<=ra;rbc<=rb;rcc<=rc;zhiling<=ir;lh2<=r1;mpcc<=mpc;saa<=sa;sbb<=sb;pcout<=pc;newpcout<=newpc;jadd<=jadd1;--加载pcct1:process(t1) --lod pcbeginif t1='1' and t1'event thenpc<=newpc;end if;end process;process(pc)beginbus_zhiling<=ram8(conv_integer(pc));end process;ct2:process(t2) --quzhibeginif t2='1' and t2'event thenir<=bus_zhiling;end if;end process;--译码先分解指令成为高4位mpc ,r1和r2。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机系统综合设计

设计报告

组长:张冠群(09003105)

成员:杨俊(09003209)

孙啸寅(09003112)

万乾坤(09003218)

李传佑(09003214)

刘森(09003110)

黄河(09003206)

东南大学计算机科学与工程学院

二OO六年九月

注:本设计报告中各个部分如果页数不够,请大家自行扩页,原则是一定要把报告写详细,能说明本组设计的成果和特色,能够反应小组中每个人的工作。

报告中应该叙述设计中的每个模块。

设计报告将是评定每个人成绩的一个重要组成部分。

注:这里只列出文件的列表,BIOS程序及.v文件具体代码请参见光盘。

CPU的vwf图

Cs138的vwf图

CTC的vwf图

Int32的vwf图

UART的vwf图

LCD的vwf图

LED的vwf图

PWM的vwf图

WDT的vwf图(此处为了演示方便,暂时把初值置为8)

SOC的vwf图。