软考网络工程师必过教材

网络工程师必看书籍

转贴]网络工程师考试总结网络工程师考试要想做网络工程师最权威的国家认可的就是计算机软考的中级网络工程师,只有考上这个才能成为网络工程师。

证书由人事部和信息产业部同时颁发,很有权威性~也是政府唯一认可的职称证书:要考网络工程师需要学习的有:1、《网络工程师教程》,必看,当作指导性的大纲来看,它可以使你网络知识的结构更加清晰与合理。

由于教程不完全覆盖考试内容,获取其他资料作为知识的深化和补充是绝对必须的,下面的推荐与大纲介绍的基本同步。

2、《数据通信原理》,包括通信原理和交换技术的内容,在上午肯定有一二道大题,只看教程不够。

对这本书不一定看得太深,即使没有任何基础通上一两遍也不困难,可以让你提高一大步。

这部分相关的内容还包括《信号与系统》,不想做硬件的朋友我觉得就不用看了。

3、网络体系结构和协议,这部分看教程即可。

4、局域网技术,先看教程,然后找一本CCNA英文教材看一遍。

这样有三个好处:比教程更深入;同时提高专业英语水准;顺便学习CISCO路由器和交换机的基础知识。

5、广域网技术看教程,这部分A TM是重点,需要找别的资料深化一下(因为它流行,如CISCO流行一个道理)。

6、网络互连,先看教程。

路由方面的知识教程上不够,建议有Linux环境,看看UNIX系统中的路由配置。

CCNP的教程不必要全看,路由和交换看看就行,中文的也可以。

7、网络操作系统,如上,研究linux就可以。

上午题目里面会有。

8、网络管理上,教程中本章前面对局域网的管理部分非常好,是每一个网络管理员都应该耳熟能详的经验。

后面的SNMP不太深,但是也差不多够了,想深化的找一本《网络管理》,对snmp会有更认识。

9、网络安全,教程很概念化,如果想深入一点,看看《计算机密码学》,对加密技术能有更多感性认识(如RSA的原理,一次一密乱码本),但不用太深入。

如果有条件,还可以感受一下win2000在安全方面对身份认证,鉴别,访问控制等技术的具体实现。

网络安全工程师书籍

网络安全工程师书籍1. "网络安全工程师指南" by 李明本书是一本全面介绍网络安全工程师必备技能和工具的指南。

从网络攻击与防御的基本概念开始讲解,详细说明了各种网络攻击方法和如何应对。

同时,本书还介绍了网络安全工程师的日常工作职责,以及使用常见的安全工具和技术来保护企业网络的方法。

2. "网络安全技术入门与实战" by 张强这本书适合初学者了解网络安全基础知识和入门实践。

书中详细介绍了网络安全的基本概念、原理和常见攻击手法,并提供了一些实战案例和演示实验供读者学习。

此外,作者还分享了一些实用的网络安全工具和技术,帮助读者提升实际应用能力。

3. "网络安全体系建设与运维" by 王涛该书主要关注企业网络安全体系的建设与运维,介绍了安全策略设计、漏洞管理、入侵检测、安全事件应急等方面的知识和实践经验。

读者能够学习到如何制定企业的安全策略,进行风险评估和漏洞管理,以及应对各种安全事件的应急处置方法。

4. "网络安全技术与实战" by 陈云这本书重点介绍了网络安全领域中的技术和实践。

作者通过案例分析和实际操作,详细解释了网络威胁的种类和防范手段。

此外,书中还介绍了网络安全的最佳实践、安全事件响应流程和日志分析技术等内容,帮助读者提升对网络安全的理解和实践能力。

5. "网络安全攻防实战" by 赵鹏本书围绕网络攻击和防御展开,通过实战案例和演练来讲解网络安全技术。

作者分享了一些常见的攻击技术和手法,并介绍了相应的防御方法和工具。

此外,还提供了一些实际的渗透测试和漏洞修复的案例,帮助读者通过实践经验提升自身的网络安全能力。

2024年软件资格考试网络工程师(中级)(基础知识、应用技术)合卷试卷与参考答案

2024年软件资格考试网络工程师(基础知识、应用技术)合卷(中级)自测试卷(答案在后面)一、基础知识(客观选择题,75题,每题1分,共75分)1、(单选题)以下关于TCP/IP协议分层结构的描述中,错误的是:A. TCP/IP协议分层结构分为四层:应用层、传输层、网络层、链路层B. 网络层主要负责IP地址的分配和路由选择C. 传输层主要负责端到端的数据传输,如TCP和UDP协议D. 应用层主要负责应用程序之间的通信,如HTTP、FTP等协议2、(多选题)以下关于IP地址的描述中,正确的是:A. IP地址分为A、B、C、D、E五类B. A类地址的网络地址部分占8位,主机地址部分占24位C. B类地址的网络地址部分占16位,主机地址部分占16位D. C类地址的网络地址部分占24位,主机地址部分占8位3、以下关于网络拓扑结构的描述,不正确的是()。

A. 网络拓扑结构是指网络中各个节点和链路的连接方式。

B. 星型拓扑结构中,中心节点是网络的瓶颈。

C. 环型拓扑结构中,每个节点都需要处理来自其他节点的数据。

D. 树型拓扑结构中,任意两个节点之间可能存在多条路径。

4、关于IP地址的分类,以下说法正确的是()。

A. A类IP地址的第一个字节范围是0到127。

B. B类IP地址的第一个字节范围是128到191。

C. C类IP地址的第一个字节范围是192到223。

D. D类IP地址的第一个字节范围是224到239。

5、在TCP/IP协议族中,以下哪个协议负责传输文件的传输过程?A. TCP(传输控制协议)B. UDP(用户数据报协议)C. IP(互联网协议)D. FTP(文件传输协议)6、在OSI七层模型中,哪一层负责在网络中寻找目的主机?A. 应用层B. 表示层C. 会话层D. 网络层7、题目:以下哪种网络协议主要用于数据传输的可靠性和完整性?A. TCP(传输控制协议)B. UDP(用户数据报协议)C. HTTP(超文本传输协议)D. FTP(文件传输协议)8、题目:在OSI七层模型中,负责网络层以下的数据传输控制的是哪一层?A. 物理层B. 数据链路层C. 网络层D. 传输层9、在OSI模型中,负责处理网络层以下的数据传输的是哪一层?A. 传输层B. 网络层C. 数据链路层D. 物理层 10、在TCP/IP模型中,用于实现网络层功能的协议是?A. IP协议B. TCP协议C. UDP协议D. HTTP协议11、题目:在TCP/IP协议族中,负责网络层路由选择的协议是:A. IP协议B. TCP协议C. UDP协议D. HTTP协议12、题目:以下关于以太网标准802.3的说法中,错误的是:A. 以太网标准802.3定义了物理层和数据链路层的规范B. 以太网标准802.3规定了CSMA/CD(载波侦听多点接入/碰撞检测)介质访问控制方法C. 以太网标准802.3规定了最大传输单元(MTU)为1500字节D. 以太网标准802.3规定了物理层接口类型,如10BASE-T、100BASE-TX等13、在计算机网络中,OSI模型中的哪一层负责处理数据传输的可靠性和顺序性?选项:A. 物理层B. 数据链路层C. 网络层D. 传输层14、在TCP/IP模型中,哪个协议负责处理数据包的路由和寻址?选项:A. IP协议B. TCP协议C. UDP协议D. HTTP协议15、题目:以下关于TCP/IP模型的四层结构描述正确的是?A. 应用层、传输层、网络层、数据链路层B. 物理层、数据链路层、网络层、传输层C. 应用层、网络层、传输层、会话层D. 物理层、网络层、传输层、会话层16、题目:在OSI七层模型中,负责提供无连接数据传输服务的层是?A. 应用层B. 表示层C. 传输层D. 数据链路层17、在TCP/IP协议栈中,负责处理数据包在网络中的传输和路由选择的是哪个协议?选项:A. IP协议B. TCP协议C. UDP协议D. HTTP协议18、以下哪个技术可以实现网络的虚拟化?选项:A. VLAN(Virtual Local Area Network)B. VPN(Virtual Private Network)C. NAT(Network Address Translation)D. DHCP(Dynamic Host Configuration Protocol)19、在TCP/IP协议族中,负责将数据从源主机传输到目的主机的是哪一层?20、以下哪个网络设备用于在网络层对数据包进行路由选择?21、在计算机网络中,以下哪一项不是OSI模型的七层结构之一?A. 物理层B. 数据链路层C. 应用层D. 网络层E. 传输层22、以下哪种网络拓扑结构具有较好的扩展性和冗余性?A. 星型拓扑B. 环型拓扑C. 树型拓扑D. 网状拓扑23、在OSI七层模型中,哪一层负责处理端到端的消息传输,并提供错误恢复和流控制?A. 物理层B. 数据链路层C. 网络层D. 传输层E. 会话层24、在IP地址分类中,属于私有IP地址范围的是哪一个选项?A. 10.0.0.0 - 10.255.255.255B. 172.16.0.0 - 172.31.255.255C. 192.168.0.0 - 192.168.255.255D. 以上全部都是25、以下哪种网络拓扑结构具有较好的扩展性和故障隔离能力?()A. 星型拓扑B. 环型拓扑C. 树型拓扑D. 网状拓扑26、在TCP/IP协议族中,以下哪个协议负责处理网络层的地址转换?()A. ARP(地址解析协议)B. RARP(反向地址解析协议)C. IP(互联网协议)D. ICMP(互联网控制消息协议)27、在OSI七层模型中,负责建立、管理和终止表示层实体之间的通信的是哪一层?A. 会话层B. 传输层C. 表示层D. 应用层28、以下哪种协议不属于TCP/IP模型的应用层?A. HTTPB. FTPC. SMTPD. IP29、在计算机网络中,以下哪种传输介质具有最高的带宽和传输速率?A. 同轴电缆B. 双绞线C. 光纤D. 无线传输 30、以下哪个协议是用于实现网络设备之间进行物理层和数据链路层通信的?A. TCP/IPB. IPX/SPXC. UDPD. ARP31、下列哪个协议用于在计算机网络中传输文件?A、ARPB、FTPC、DHCPD、ICMP32、在OSI七层模型中,哪一层负责提供透明的数据帧传输,并维护一个节点到另一个节点的链路?A、物理层B、数据链路层C、网络层D、传输层33、在OSI模型中,负责处理数据加密、压缩和纠错的层次是?A. 应用层B. 表示层C. 会话层D. 网络层34、以下哪项不是TCP/IP模型中的网络层协议?A. IP协议B. ARP协议C. DNS协议D. HTTP协议35、在OSI七层模型中,负责处理端到端的数据传输错误检测与纠正的是哪一层?A. 物理层B. 数据链路层C. 网络层D. 传输层36、下列哪种协议用于自动分配IP地址给网络中的设备?A. ARP(地址解析协议)B. DHCP(动态主机配置协议)C. DNS(域名系统)D. ICMP(互联网控制消息协议)37、以下关于网络层协议的描述中,哪一项是错误的?A. IP协议负责数据的寻址和路由选择B. ICMP协议用于处理网络中的不可达消息和错误报告C. ARP协议用于将IP地址解析为物理地址D. TCP协议提供面向连接的服务,保证数据的可靠传输38、在OSI七层模型中,以下哪一层负责建立、管理和终止数据传输的连接?A. 网络层B. 传输层C. 会话层D. 应用层39、下列关于IPv4地址分类的叙述中,错误的是哪一项?A. A类地址默认子网掩码为255.0.0.0。

信息安全工程师软考书籍

信息安全工程师软考书籍信息安全工程师是一个关键的职业,他们负责保护和维护组织的信息系统安全。

为了成为一名合格的信息安全工程师,学习合适的教材是非常必要的。

本文将介绍一些值得推荐的软考书籍,帮助您准备和通过信息安全工程师的考试。

一、《信息安全工程师教材》这本教材是软考信息安全工程师考试的官方教材,由中国电子工业出版社出版。

它全面而系统地介绍了信息安全的基本概念、原理和技术,并重点阐述了网络安全、系统安全、密码学、应用安全等内容。

这本书的编写团队由多位业界专家和教育界人士组成,具有很高的权威性,可以帮助考生全面理解信息安全工程师的知识要点。

二、《信息安全工程师考试指南》这本书是一本辅导类教材,由多位从业经验丰富的信息安全工程师和培训导师编写。

它结合了考试大纲的要求,精选了重点和难点内容,以通俗易懂的语言进行解释和讲解。

它还提供了大量的案例分析和习题训练,帮助考生巩固理论知识,并掌握解题的技巧和方法。

这本书在内容的覆盖面和实用性上都非常出色,是备考的重要参考资料。

三、《信息安全技术与实践》这本书是由清华大学出版社出版的一本经典教材,它以信息安全的实践应用为主线,全面介绍了信息安全领域的重要技术和方法。

书中内容涵盖了网络安全、数据安全、应用安全、物理安全等多个方面,并且结合了真实案例进行讲解和分析。

这本书注重理论知识与实践的结合,能够帮助考生理解信息安全技术的本质和应用场景。

四、《信息安全工程师备考指南》这本书是由国内知名的IT培训机构编写的备考指南,主要面向软考信息安全工程师的考试要求。

它全面梳理了考试大纲的重点和难点,列出了重要的知识点和技能要求,并提供了详细的解题思路和方法。

这本书还附带了大量的习题和模拟试题,考生可以通过练习来检验和提升自己的复习效果。

这本书适合那些对考试重点和考点不太了解的考生,能够帮助他们有针对性地进行备考。

五、《信息安全工程师考试全真模拟卷》这本书是一套信息安全工程师考试的全真模拟试题,由多位软考考官和从业专家编写。

2024版考软考网络工程师请看最新第五版教材内容

促进网络工程师的职业发展

网络工程师考试是网络工程师职业发展的重要里程碑,通过考试可以获得相应的职业资格证书,提升个人职业竞 争力,为未来的职业发展打下基础。

2024/1/27

4

考试内容与要求

模式(ATM)等。

广域网的应用

广域网被用于连接分布在不同 地理位置的企业分支机构、数 据中心和云计算资源,实现远 程办公、视频会议、在线教育 等应用。

10

互联网协议及应用

2024/1/27

互联网协议的概念

互联网协议(IP)是TCP/IP协议族中 的核心协议,负责在网络上路由和传 输数据。

互联网协议的应用

掌握日志分析方法,通过查看设备日 志定位并排除故障。

工具使用与故障排除

熟悉常用网络故障排除工具的使用方 法,如ping、traceroute、telnet等。

2024/1/27

16

04

网络安全技术与实践

2024/1/27

17

网络安全概念与威胁分析

网络安全概念

网络安全是指通过采用各种技术和管理措 施,保护计算机网络系统免受未经授权的 访问、攻击、破坏或篡改,确保网络系统 的机密性、完整性和可用性。

计算机网络基础知识

2024/1/27

7

计算机网络概念与分类

计算机网络的定义

计算机网络是由一组自主的计算机互联而成的集合,这些计算机使用相同的通 信协议,以便在网络中共享资源。

计算机网络的分类

根据网络覆盖的地理范围,计算机网络可分为局域网(LAN)、城域网(MAN) 和广域网(WAN)。

软考网络工程师复习(背熟必过秘籍)---必看

网络工程师重点目录网络基础................................ 错误!未定义书签。

第一章数据通信基础 ................................ - 3 - 第二章局域网技术 .................................. - 5 - 第三章广域网和接入网技术 ......................... - 16 - 第四章因特网 ...................................... - 22 - 第五章路由器与交换配置 ............................ - 32 - 第六章网络安全 .................................... - 46 - 第七章网络管理 ................................... - 53 - 第八章计算机基础知识 ............................. - 66 -第一章 数据通信基础一、基本概念码元速率:单位时间内通过信道传送的码元个数,如果信道带宽为T 秒,则码元速率1B T =。

若无噪声的信道带宽为W ,码元携带的信息量n 与码元种类N 关系为2log N n =,则极限数据速率为22log 2log N N R B W ==有噪声的极限数据速率为(1)2log S N C W += 1010log S N dB =其中W 为带宽,S 为信号平均功率,N 为噪声平均功率,S N 为信噪比电波在电缆中的传播速度为真空中速率的2/3左右,即20万千米/秒编码:单极性码:只有一个极性,正电平为0,零电平为1;级性码:正电平为0,负电平为1;双极性码:零电平为0,正负电平交替翻转表示1。

这种编码不能定时,需要引入时钟归零码:码元中间信号回归到零电平,正电平到零电平转换边为0,负电平到零电平的转换边为1。

软件工程师必读教材推荐

软件工程师必读教材推荐在如今信息技术日新月异的时代,软件工程师是一个备受追捧的职业。

他们的工作涉及到设计、开发、测试和维护复杂的软件系统,因此需要持续学习和充实自己的知识库。

本文将向大家推荐一些广受好评的软件工程师必读教材,帮助读者进一步提升他们的技能和知识水平。

1. 《软件工程》(Ian Sommerville)《软件工程》是一本经典教材,由英国计算机科学家Ian Sommerville撰写。

本书全面阐述了软件工程的基本概念、原理和方法,内容包括软件需求、软件设计、软件测试、软件维护等。

该书内容详尽且易于理解,适合作为软件工程的入门教材。

2. 《代码大全》(Steve McConnell)《代码大全》是一本著名的软件工程书籍,由Steve McConnell撰写。

该书主要讲解了编写高质量代码的原则和技巧,包括命名规范、代码风格、错误处理、测试等方面。

此外,该书还介绍了代码重构及性能优化的实践方法。

对于想要提高代码质量和编程技能的软件工程师来说,这是一本不可多得的教材。

3. 《设计模式:可复用面向对象软件的基础》(Erich Gamma等人)《设计模式:可复用面向对象软件的基础》是四位计算机科学家(Erich Gamma、Richard Helm、Ralph Johnson和John Vlissides)合著的一本经典著作。

该书详细介绍了23种常见的设计模式,包括工厂模式、单例模式、观察者模式等。

通过学习和应用这些设计模式,软件工程师可以更好地设计和开发可重用、可扩展的软件系统。

4. 《敏捷软件开发:原则、模式与实践》(Robert C. Martin)《敏捷软件开发:原则、模式与实践》由著名软件工程师Robert C. Martin撰写。

本书介绍了敏捷开发的原则、实践和模式,深入讲解了敏捷软件开发的流程、工具和技术。

对于致力于提高软件交付效率和质量的软件工程师来说,该书是一部不可或缺的指南。

5. 《人月神话》(Frederick P. Brooks Jr.)《人月神话》是一本软件工程经典之作,由Frederick P. Brooks Jr.撰写。

网络工程师5天修炼(第三版)

作者简介

朱小平:

资深软考培训师、网络规划设计师、高级工程师,主持或参与的网络工程与软件开发项目20余个,具有丰富 的网络工程理论与实践经验。拥有多年软考培训经验,并总结出一套独特而高效的学习方法,好评如潮,众多考 生从中受益;近3年从事软考网络工程师培训几十场,学生遍布石化业、运输业、IT业、教育业各条战线。

网络工程师5天修炼(第三版)2018年水利水电Fra bibliotek版社出版的图书

01 推荐

03 作者简介

目录

02 内容简介 04 目录

《网络工程师5天修炼(第三版)》是2018年水利水电出版社出版的图书,作者是朱小平、施游。

推荐

本书特色: ●方法独特,提炼精辟,已助数万考生轻松通过网络工程师考试 ●攻克要塞软考研究团队真情分享 ●5天精华,浓缩著名一线软考讲师10年黄金经验 ●基于历年考点频次大数据组织编写,内容科学,重点突出 ●精确匹配新考纲,“攻克要塞”APP提供全天侯学习支持

谢谢观看

内容简介

网络工程师考试是计算机技术与软件专业技术资格(水平)考试系列中的一个重要考试,是计算机专业技术 人员获得网络工程师职称的一个重要途径。但网络工程师考试涉及的知识点极广,几乎涵盖了本科计算机专业课 程的全部内容,并且有一定的难度。

本书以作者多年从事软考教育培训和试题研究的心得体会建立了一个5天的复习架构。本架构通过深度剖析考 试大纲并综合历年的考试情况,将网络工程师考试涉及的各知识点高度概括、整理,以知识图谱的形式将整个考 试分解为一个个相互联系的知识点逐一讲解,并附以典型的考试试题和详细的试题分析解答以确保做到触类旁通。 读者通过对本书中知识图谱的了解可以快速提高复习效率和准确度,做到复习有的放矢,考试便得心应手。*后还 给出了一套全真的模拟试题并详细作了点评。

软考网络工程师推荐书目

此处官方指定教材,后面是群友推荐 的资料!!

价格

46元 83元 79元 40元 30元 62元 60元 50元 63元 60元 33元 49元

数据库系统工程师考试科目 1:信息系统知识——考点解 析及模拟训练 数据库系统工程师考试科目 2:数据库系统设计与管理— —考点解析及模拟训练 网络管理员考前辅导 跨越程序员必备训练 程序员考试复习与提高 程序员考试科目1: 计算机硬软件基础知识--考 点解析及模拟训练(2005 版) 程序员考试科目2: 程序设计--考点解析及模拟 训练(2005版) 程序员考试辅导(2005版) 程序员备考训练(2006版) 跨越软件设计师必备训练 软件设计师全真模拟试题及 解析(2006版) 软件设计师考试科目 计算机与软件工程知识--考 点解析及模拟训练(2005 版) 软件设计师考试科目2: 软件设计—考点解析与模拟 训练(2006版) 软件设计师考试辅导(2005 版) 网络管理员备考训练(2006 版) 系统分析师技术指南(2007 版) 系统分析师考试辅导(2007 版) 系统分析师常用工具(2004 版) 系统分析与设计技术(2005 版) 信息处理技术与工具(信 息处理技术员)(2005版) 跨越信息系统监理师必备训 练(2006版) 数据库系统工程师考试全程 指导(2006年) 电子商务设计师系统分析与 设计师应用技术(2007版) 电子商务技术员基础与应用 技术 多媒体应用设计师考试辅导

书号

978-7-302-21974-3 978-7-302-20584-5 978-7-302-20645-3 978-7-302-20585-2 978-7-302-20646-0 978-7-302-19708-9 978-7-302-19932-8 978-7-302-19558-0 7-302-12895-2 978-7-302-12958-5 7-302-12957-6 7-302-13006-X 7-302-09096-3 7-302-06464-4 7-302-10520-0 7-302-10436-0 7-302-10536-7 978-7-302-15766-3 7-302-11309-2 7-302-11308-4

[大家网]网络工程师教程(第三版

![[大家网]网络工程师教程(第三版](https://img.taocdn.com/s3/m/aaa3d901bed5b9f3f90f1cbf.png)

.Net技术精品资3;编程语言学习资料尽收眼底 电子书+视频教程

Visual C++(VC/MFC)学习电子书及开发工具下载

Perl/CGI脚本语言编程学习资源下载地址大全

Python语言编程学习资料(电子书+视频教程)下载汇总

2006 年下半年试题分析与解答 软考指定用书 清华出版(含各科)

2006 年上半年试题分析与解答 软考指定用书 清华出版(含各科)

2009 年计算机技术与软件水平考试各科目考试大纲汇总

全国计算机技术与软件专业资格(水平)考试真题及答案汇总

全国计算机技术与软件专业资格(水平)考试真题及答案

2008 年下半年试题分析与解答 软考指定用书 清华出版(含各科)

2008 年上半年试题分析与解答 软考指定用书 清华出版(含各科)

2007 年下半年试题分析与解答 软考指定用书 清华出版(含各科)

2007 年上半年试题分析与解答 软考指定用书 清华出版(含各科)

软件设计师考试同步辅导(上午科目) 高清PDF版

软件设计师考试考点分析与真题详解(软件设计技术篇)

软件设计师考试辅导:考点精讲、例题分析、强化训练 冶金工业出版

数据库系统工程师教程 软考指定用书 高清PDF版

软件评测师教程 软考指定教材 高清PDF版

网络工程师教程(第 3 版) 软考指定用书 高清PDF版

网络工程师考试同步辅导:计算机与网络知识篇 软考指定用书

网络工程师考试同步辅导(网络系统设计与管理篇) 软考指定辅导用书

软件设计师教程(第 3 版) 软考指定用书 高清PDF版

软件设计师考试同步辅导(下午科目) 高清PDF版

2024年计算机软考网络工程师考纲

一、考试范围

计算机网络工程师考试范围主要包括以下几个方面:

1、网络理论:包括OSI/TM参考模型、TCP/IP协议、网络编程、网

络设备(如路由器、交换机)以及网络安全相关知识。

2、宽带技术:包括宽带安装实施配置、宽带网络规划、虚拟专网(VPN)技术实施及安全配置等常见宽带技术相关知识。

3、数据网络技术:包括电路、节点、链路访问(X25/ISDN/FR)及数

据网络环境下的TCP/IP实施及应用。

4、网络服务管理:包括服务质量(QoS)技术、计算机网络环境下的系

统管理、安全、性能管理以及计算机网络上的服务管理。

5、网络设备及交换机:包括网络设备运行原理(BGP、RIP、OSPF)、路由器和交换机实施、网络安全及性能优化等网络设备及交换机相关知识。

6、网络安全:包括木马、病毒与防病毒、防火墙及入侵检测(IDS)、

网络安全实施、网络安全标准及策略、安全管理等网络安全相关知识。

7、网络管理:包括计算机网络管理理论,网络管理规划,网络性能

管理,网络安全管理,网络监控及网络运行管理等网络管理相关知识。

8、其他:包括网络质量,网络通信安全技术。

软件工程师复习资料推荐

软件工程师复习资料推荐在成为一名合格的软件工程师的道路上,学习和复习是非常重要的环节。

而选用适合的复习资料,可以帮助我们更加高效地掌握知识点,提升自己的技能。

本文将推荐一些优质的复习资料,供软件工程师们参考。

一、编程语言学习资料1.《Java核心技术》:由SUN公司的两位工程师编写,系统全面地介绍了Java语言的基础知识和进阶技巧,是Java程序员的必备参考书。

2.《Python编程:从入门到实践》:一本适合初学者的Python编程入门书籍,通过实际案例的演示和习题的训练,帮助读者快速入门Python编程。

3.《C++ Primer》:这是一本C++领域的经典教材,可以帮助读者全面掌握C++语言的基本概念和高级特性。

二、系统设计和架构学习资料1.《大型网站技术架构》:由阿里巴巴集团首席架构师李智慧所著,内容详尽介绍了大型网站的设计原理和重要技术,对于理解和掌握系统设计和架构非常有帮助。

2.《设计模式:可复用面向对象软件的基础》:这本书介绍了23种常用的设计模式,对于应用程序的设计和可维护性有着重要的指导作用。

三、数据库学习资料1.《SQL必知必会》:适合初学者的SQL学习资料,通过简单明了的语言和大量实例,帮助读者快速掌握SQL的基本知识和操作技巧。

2.《MongoDB权威指南》:对于学习和使用MongoDB的人来说,这本书是一本非常有价值的参考书,它详细介绍了MongoDB的各种特性和使用方法。

四、软件开发工具学习资料1.《Git权威指南》:介绍了Git版本控制工具的基本概念和使用方法,对于团队协作开发和代码管理非常有帮助。

2.《Maven实战》:Maven是Java项目构建和管理的重要工具,这本书详细介绍了Maven的使用和配置,对于软件工程师来说是一本不可或缺的参考资料。

以上是我为软件工程师们推荐的一些复习资料,希望能够对大家的学习有所帮助。

当然,选择适合自己的学习资料也需要根据自身的实际情况和学习需求来确定。

信息安全工程师软考书籍

信息安全工程师软考书籍

作为一位信息安全工程师,你需要掌握的知识和技能较为广泛。

以下是一些常见的软考书籍,涵盖了信息安全工程师考试的相关内容:

1. 《信息系统安全工程师教程》,该书是信息安全工程师考试

的权威教材,内容包括信息安全基础理论、安全技术与方法、安全

管理与实践等方面的知识。

2. 《信息安全技术基础》,这本书详细介绍了信息安全的基本

概念、密码学、网络安全、操作系统安全等内容,对于初学者来说

是一个很好的入门教材。

3. 《网络安全技术与实践》,该书主要介绍了网络安全的基本

原理、攻击与防御技术、入侵检测与防范等内容,对于理解网络安

全的基本概念和技术有很大帮助。

4. 《信息安全管理与评估》,这本书重点介绍了信息安全管理

的理论框架、安全策略与规划、风险评估与管理等内容,对于信息

安全工程师在实践中的管理工作非常有指导意义。

5. 《计算机网络安全技术与实践》,该书主要介绍了计算机网络安全的基本原理、攻击与防御技术、安全策略与管理等内容,对于理解网络安全的技术和实践有很大帮助。

除了上述书籍,还可以参考一些相关的教材、参考书和学术论文,如《信息安全技术导论》、《网络安全与管理》、《信息安全技术原理与应用》等。

此外,还建议参加一些培训班、考试辅导班,结合实际工作经验和实践,更好地掌握信息安全工程师的知识和技能。

希望以上信息对你有所帮助,祝你在信息安全工程师考试中取得好成绩!。

网络工程师职称考试材料

1.网络工程师教程(第3版)(全国计算机技术与软件专业技术资格(水平)考试指定用书)》清华大学出版社雷震甲主编2. 网络工程师考试冲刺指南(新修订版)》——希赛IT教育研发中心组编,施游、胡钊源主编,电子工业出版社3. 网络工程师考试考点分析与真题详解(最新版)》——希赛IT教育研发中心组编,施游、桂阳主编,电子工业出版社第一章《计算机基础知识》中介绍了计算机的基础知识(全部在上午题出),这个部分的内容现在一般有8分左右,有一定难度,而且知识的覆盖面很广但目前考察的难度有所降低,大部分的题目都是以前考过的真题(尤其是这个部分的计算机).. 第二章《计算机网络概论》主要讲述了网络的七层模型,建议大家简单地了解一下,书的后面有详细的讲解。

第三章《数据通信基础》,这一章的考题主要集中在上午的考试,一般2分左右,本部分内容有难度,但从考试方面来看不必研究太深,本章的考点有: (1)熟练信道带宽、误码率的公式(计算题); (2)了解数据的编码格式; (3)熟悉数据交换的三种不同的方式; (4)了解多路复用技术的概念以及原理; (5)熟悉差错控制的概念,特别需要掌握的是海明码以及循环冗余效验码。

第四章《广域通信网》的重点有: (1)HDLC协议的特点、帧结构、三种的基本配置方式以及三种帧的类型; (2)帧中继协议的特点、帧结构、关于拥塞控制的办法; (3)ISDN的特点、A TM层的特点,其中A TM高层的特点是比较重要的,同时A TM适配层也需要很好地掌握。

第五章《局域网和城域网》的重点有: (本部分内容有一定难度,大家不必在上面花太多时间) (1)了解802.1到802.11各个标准的特点; (2)对于CSMA/CD协议,了解它的工作原理; (3)了解令牌环总线、令牌环网的概念以及工作原理; (4)熟悉A TM局域网的工作原理,对于A TM局域网仿真要熟悉并掌握,这部分是比较重要的内容; (5)在无线局域网这部分,因为技术比较新,也是以后网络分支发展的一个方向,大家要重点看,有可能在下午题出现第六章《网络互连和互联网》的重点在于: (有可能出现在下午题,这章一定要重点看,对后面学习很有帮助) (1)了解中继器、网桥、路由器、网关的工作原理; (2)了解生成树网桥(本人觉得这部分也是个重点,但考试很少考这部分内容); (3)熟悉IP编址的方法、IP的分段和重装配以及差错控制和流控; (4)对于ICMP协议,熟悉ICMP各报文的含义; (5)了解ARP、RARP的帧格式、工作原理; (6)了解外部网关协议的概念以及各个协议的区别; (7)掌握NA T技术的概念以及实现原理(比较重要的知识点); (8)了解三层交换技术的概念以及实现原理; (9)了解FTP的命令。

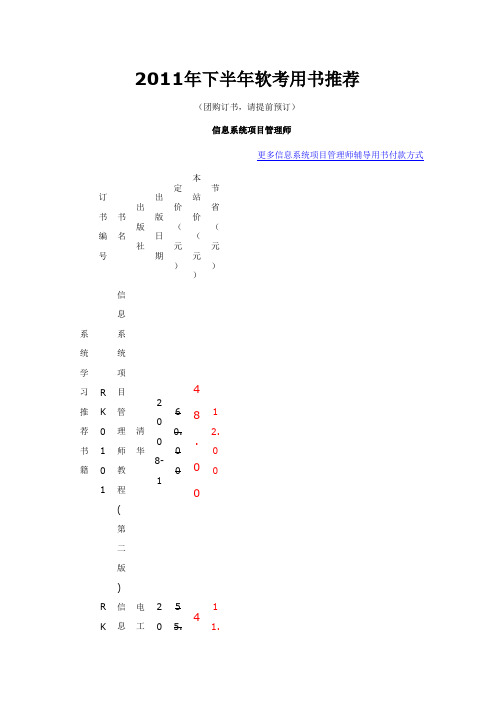

软考用书

2011年下半年软考用书推荐(团购订书,请提前预订)信息系统项目管理师更多信息系统项目管理师辅导用书付款方式系统学习推荐书籍订书编号书名出版社出版日期定价(元)本站价(元)节省(元)RK0101信息系统项目管理师教程(第二版) 清华2008-1 60.0048.012.RK0114信息系统项目管理师考试案例梳理、真题透解与强化训练电工2011-4 55.0044.011.RK0132信息系统项目管理师案例分析指南清华2009-9 30.0024.06.RK0186信息系统项目管理师考试试题分类精解(第4版)电工2011-4 55.0044.011.RK0 190 信息系统项目管理师历年试题分析与解答(2010最新版)清华2010-5 41.0032.88.2信息系统项目管理师系统学习推荐书籍合计241.0192.8048.2面授培训A班信息系统项目管理师冲刺串讲班2900元7月29日前报名优惠至2700元。

同单位报名5人可减免1人,并赠送网校名额。

包含教材、印刷品讲义、模拟测试等详情请点击B班信息系统项目管理师系统辅导班6500元7月15日前报名优惠至6300元。

同单位报名5人可减免1人。

包含教材、印刷品讲义、模拟测试等详情请点击系统集成项目管理工程师更多系统集成项目管理工程师辅导用书付款方式系统学习推荐书订书编号书名出版社出版日期定价(元)本站价(元)节省(元)RK4301系统集成项目管理工程师教程清华2009-355.00 44.0011籍.RK43 13 系统集成项目管理工程师考试考前冲刺预测卷及考点解析(最新版)电工2010-239.80 31.808.RK43 14 系统集成项目管理工程师考试案例梳理、真题透解与强化训练电工2011-448.00 38.409.6RK43 32 系统集成项目管理工程师备考指南与习题详解清华2010-246.00 36.809.2RK43 90 系统集成项目管理工程师历年试题分析与解答,2010版清华2010-513.00 10.402.6系统集成项目管理工程师系统学习推荐书籍合计201.8161.44.4面授培训A班系统集成项目管理工程师冲刺串讲班2350元7月29日前报名优惠至2150元。

全国计算机技术与软件专业技术资格(水平)考试用书网络工程师考

全国计算机技术与软件专业技术资 格(水平)考试用书网络工程师考

2014年电子工业出版社出版的图书

01 内容简介

03 目录

目录

02 内容提要 04 前言

《全国计算机技术与软件专业技术资格(水平)考试用书网络工程师考试试题分类精解(第5版)》是2014 年10月电子工业出版社出版的图书,作者是希赛教育软考学院。

内容简介

《网络工程师考试试题分类精解(第5版)》由希赛教育软考学院组织编写,可以作为计算机技术与软件专业 技术资格(水平)考试中的网络工程师级别考试的辅导与培训教材。本书根据最新的网络工程师考试大纲,对历 年(2008—2013年)考试试题进行了分析和总结,对考试大纲规定的内容有重点地进行了细化和深化。

《网络工程师考试试题分类精解(第5版)》适合参加计算机技术与软件专业技术资格(水平)考试中的网络 工程师级别考试的考生阅读,也可作为相关培训班的辅导书。

目录பைடு நூலகம்

第1章编码和传输 1 数据通信基础知识是网络工程师考试的必考内容,且考核分值较高。主要集中在数据通信的基本原理、数据 编码、数字调制、传输与交换技术的考核上。 第2章网络体系结构 21 网络体系结构是网络工程师考试的热门考点,考核分值很高。其中尤为重要的是与IP子网计算相关的问题, 因此大家在学习过程中要对各种子网划分计算的题型进行重点复习。 第3章网络分类 78 重点掌握计算机网络4种分类方法:按地域范围分类(LAN、MAN、WAN)、按服务分类(因特网、企业内部 网)、按传输媒体分类(**、数据、视像)、按电信网分类(驻地、接入、骨干)。 第4章网络互连技术 103 本章涉及的知识是相对其他章节中比较重要的部分。根据考试大纲,要求考生在本章掌握如下知识点:网络 连接设备、网络互连协议、交换技术。

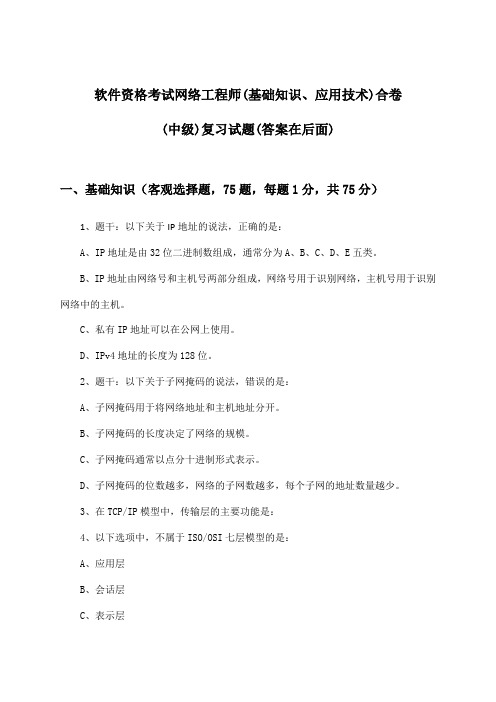

软件资格考试网络工程师(基础知识、应用技术)合卷(中级)试题及解答参考

软件资格考试网络工程师(基础知识、应用技术)合卷(中级)复习试题(答案在后面)一、基础知识(客观选择题,75题,每题1分,共75分)1、题干:以下关于IP地址的说法,正确的是:A、IP地址是由32位二进制数组成,通常分为A、B、C、D、E五类。

B、IP地址由网络号和主机号两部分组成,网络号用于识别网络,主机号用于识别网络中的主机。

C、私有IP地址可以在公网上使用。

D、IPv4地址的长度为128位。

2、题干:以下关于子网掩码的说法,错误的是:A、子网掩码用于将网络地址和主机地址分开。

B、子网掩码的长度决定了网络的规模。

C、子网掩码通常以点分十进制形式表示。

D、子网掩码的位数越多,网络的子网数越多,每个子网的地址数量越少。

3、在TCP/IP模型中,传输层的主要功能是:4、以下选项中,不属于ISO/OSI七层模型的是:A、应用层B、会话层C、表示层D、通信层5、什么是TCP/IP协议栈?6、以下哪个网络设备主要用于在一定范围内为其他设备提供无线接入点?7、在TCP/IP协议栈中,负责在网络层实现数据分片和重组的协议是:A. IP协议B. TCP协议C. UDP协议D. ARP协议8、以下关于OSI七层模型的描述,错误的是:A. 物理层负责在物理媒体上传输原始比特流B. 数据链路层负责在相邻节点之间可靠地传输数据C. 网络层负责实现网络中不同节点之间的通信D. 应用层负责为用户提供网络服务9、在IP地址分类中,128.11.3.31属于哪一类地址?A. A类B. B类C. C类D. D类 10、下列哪一项不属于TCP/IP模型的应用层?A. HTTPB. FTPC. SMTPD. IP11、在TCP/IP模型中,用于在网络层中提供可靠的数据传输、拥塞控制和流量调节功能的协议是:A. IP协议B. TCP协议C. UDP协议D. HTTP协议12、在OSI七层模型中,哪一层负责提供数据封装、地址分配和路由选择等功能?A. 表示层B. 传输层C. 网络层D. 应用层13、以下关于OSI七层模型中传输层的描述,错误的是:A. 传输层负责提供端到端的通信服务B. 传输层协议如TCP和UDP均工作在OSI模型的第四层C. 传输层可以保证数据的可靠传输D. 传输层的数据单元被称为报文14、以下关于IP地址的描述,错误的是:A. IP地址是一个32位的二进制数B. IP地址通常以点分十进制形式表示C. IP地址分为A、B、C、D、E五类D. A类IP地址的第一个字节范围为0~12715、IP地址192.168.10.110/29 的广播地址是()。

2024年软件资格考试网络工程师(中级)(基础知识、应用技术)合卷试题与参考答案

2024年软件资格考试网络工程师(基础知识、应用技术)合卷(中级)模拟试题(答案在后面)一、基础知识(客观选择题,75题,每题1分,共75分)1、以下关于TCP/IP协议栈四层模型的描述,正确的是()。

A、物理层、数据链路层、网络层、传输层B、应用层、表示层、会话层、传输层C、网络层、传输层、会话层、应用层D、传输层、网络层、数据链路层、物理层2、以下关于IP地址的说法,错误的是()。

A、IP地址由32位二进制数组成,分为A、B、C、D、E五类B、A类IP地址的前8位为网络地址,后24位为主机地址C、B类IP地址的前16位为网络地址,后16位为主机地址D、C类IP地址的前24位为网络地址,后8位为主机地址3、在OSI模型中,负责处理数据完整性、顺序性和流量控制的层是:A. 物理层B. 数据链路层C. 网络层D. 传输层4、IP地址192.168.1.10属于以下哪个分类?A. A类地址B. B类地址C. C类地址D. D类地址5、在OSI七层模型中,负责处理端到端的数据流并提供可靠传输服务的是哪一层?A. 物理层B. 数据链路层C. 网络层D. 传输层6、在TCP/IP协议族中,下列哪个协议用于自动分配IP地址给主机?A. ARP(地址解析协议)B. ICMP(互联网控制消息协议)C. DHCP(动态主机配置协议)D. DNS(域名系统)7、以下关于TCP协议的描述,错误的是:A. TCP协议是一种面向连接的、可靠的、基于字节流的传输层通信协议。

B. TCP协议通过三次握手建立连接,通过四次挥手终止连接。

C. TCP协议使用校验和字段来检测数据传输过程中的错误。

D. TCP协议的端口号范围从0到65535。

8、以下关于IP地址的说法,不正确的是:A. IP地址是全球互联网中设备的唯一标识。

B. IP地址分为A、B、C、D、E五类。

C. IPv4地址长度为32位,由4个字节组成。

D. IP地址的子网掩码用于将网络地址和主机地址分离。

网络工程师全部课程

Linux操作系统安装与配置方法

2024/1/25

安装Linux操作系统

掌握安装步骤和注意事项,如选择安装方式、设置安装选项、进 行系统分区等。

配置Linux操作系统

包括网络配置、用户管理、文件权限管理、软件包管理等常用功能 的配置方法。

Linux常用命令

了解并掌握Linux常用命令,如ls、cd、mkdir、rm、ps等,以便 进行故障排除和系统管理。

31

常见服务器软件安装与配置方法

Web服务器软件

如Apache、Nginx等,掌握安 装和配置方法,以及虚拟主机 、SSL证书等高级功能的配置。

文件服务器软件

如Samba、FTP等,掌握安装 和配置方法,以及文件共享权 限设置等常用操作。

2024/1/25

数据库服务器软件

如MySQL、Oracle等,掌握安 装和配置方法,以及数据库创 建、备份恢复等常用操作。

EIGRP协议原理及配置

深入解析OSPF协议的工作原理及配置方法 ,包括OSPF区域划分、LSA类型、 DR/BDR选举等。

全面介绍EIGRP协议的工作原理及配置方法 Байду номын сангаас包括EIGRP度量值计算、邻居发现机制、 DUAL算法等。

2024/1/25

22

05

网络安全技术

BIG DATA EMPOWERS TO CREATE A NEW

11

局域网故障排除与维护

1 2

局域网故障类型

物理层故障、数据链路层故障、网络层故障等。

局域网故障排除方法

观察法、测试法、替换法、配置检查法等。

3

局域网维护措施

定期备份数据、更新防病毒软件、监控网络性能 、及时处理故障等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件知识

计

计

运算器

算术逻辑单元(ALU)、累加器、状态寄存器、通用寄存器组等组成。算术逻辑运算单元(ALU)的基本功能为加、减、乘、除四则运算,与、或、非、异或等逻辑操作,以及移位、求补等操作。计算机运行时,运算器的操作和操作种类由控制器决定。运算器处理的数据来自存储器;处理后的结果数据通常送回存储器,或暂时寄存在运算器中。与Control Unit共同组成了CPU的核心部分。

C.高速缓存(Cache)D.随机访问存储器

试题解析:

相联存储器(associative memory)也称为按内容访问存储器(content addressed

memory),是一种不根据地址而是根据存储内容来进行存取的存储器。

参考答案:B

●处理机主要由处理器、存储器和总线组成。总线包括(2)。

(2)A.数据总线、地址总线、控制总线B.并行总线、串行总线、逻辑总线

试题解析:

CISC的特点是多采用变长指令,而RISC刚好相反。

答案:C

●若内存按字节编址,用存储容量为32K X 8比特的存储器芯片构成地址编号

A0000H至DFFFFH的内存空间,则至少需要(1)片。

(1)A.4 B.6 C.8 D.10

试题解析:

DFFFFH-A0000H=3FFFFH <218,32K=215,则至少需要芯片为218 /215=8。

问速度是在CPU和内存之间,可以提高CPU对内存的访问效率。

答案:B

●计算机在进行浮点数的相加(减)运算之前先进行对阶操作,若x的阶码大于y的

阶码,则应将(2)。

(2)A.x的阶码缩小至与y的阶码相同,且使x的尾数部分进行算术左移。

B.x的阶码缩小至与y的阶码相同,且使x的尾数部分进行算术右移。

C.y的阶码扩大至与x的阶码相同,且使y的尾数部分进行算术左移。

原码、补码、反码

计算机储存有符号的整数时,是用该整数的补码进行储存的,0的原码、补码都是0,正数的原码、补码可以特殊理解为相同,负数的补码是它的反码加1。

【考试要点】:计算,例如给予一个数值算补码和反码

【参考文档】:/forum.php?mod=viewthread&tid=86&page=1&extra=#pid166

地址寄存器:可作为存储器指针。

答案:B

●关于在I/O设备与主机间交换数据的叙述,(4)是错误的。

(4)A.中断方式下,CPU需要执行程序来实现数据传送任务。

B.中断方式和DMA方式下,CPU与I/O设备都可同步工作。

C.中断方式和DMA方式中,快速I/O设备更适合采用中断方式传递数据。

D.若同时接到DMA请求和中断请求,CPU优先响应DMA请求。

参考答案:B

●现有四级指令流水线,分别完成取指、取作的时间依次为数、运算、传送结果四步

操作。若完成上述操9ns、10ns、6ns、8ns。则流水线的操作周期应设计为(2)ns。

(2)A.6 B.8 C.9 D.10

试题解析:

取最大的那个微指令时间作为流水线操作周期。

答案:D

●若每一条指令都可以分解为取指、分析和执行三步。已知取指时间t取指=4△t,分析

[考试要点]:前些年经常考,主要是寄存器寻址

[参考文档]:无

CISC复杂指令集和RISC精简指令集

RISC具有简单高效的特色。对不常用的功能,常通过组合指令来完成。RISC机器更适合于专用机;而CISC机器则更适合于通用机。

[考试要点]:考察CSIC和RISC的差异

[参考文档]:/view/65652.htm

[考试要点]:指令周期运算时常考的重点

[参考文档]:无

寻址方式

寻址方式就是寻找操作数或操作数地址的方式。8086提供了与操作数有关和与I/O端口地址有关的两类寻址方式。与操作数有关的寻址方式有七种,分别是立即寻址,寄存器寻址,直接寻址,寄存器间接寻址,寄存器相对寻址,基址加变址寻址,相对基址加变址寻址;与I/0端口有关的寻址方式有直接端口寻址和间接端口寻址方式。

名称简称用途特点

高速缓冲存储器Cac行期间的大量程序和数据存取速度较快,存储容量不大

外存储器外存存放系统程序和大型数据文件及数据库存储容量大,位成本低

高速缓存是为了解决高速设备和低速设备相连,提高访问速度

【考试要点】:高速缓存存在的意义,内存存储机制

将自动修改PC的内容,即每执行一条指令PC增加一个量,这个量等于指令所含的字节数,

以便使其保持的总是将要执行的下一条指令的地址。

状态寄存器:用来标识协处理器中指令执行情况的,它相当于CPU中的标志位寄存器。

累加寄存器:主要用来保存操作数和运算结果等信息,从而节省读取操作数所需占用总

线和访问存储器的时间。

常识。

参考答案:C

指令系

指令

告诉计算机从事某一特殊运算的代码数据传送指令、算术运算指令、位运算指令、程序流程控制指令、串操作指令、处理器控制指令。

指令周期是执行一条指令所需要的时间,一般由若干个机器周期组成,是从取指令、分析指令到执行完所需的全部时间。

CPU从内存取出一条指令并执行这条指令的时间总和。指令不同,所需的机器周期数也不同。对于一些简单的的单字节指令,在取指令周期中,指令取出到指令寄存器后,立即译码执行,不再需要其它的机器周期。对于一些比较复杂的指令,例如转移指令、乘法指令,则需要两个或者两个以上的机器周期。从指令的执行速度看,单字节和双字节指令一般为单机器周期和双机器周期,三字节指令都是双机器周期,只有乘、除指令占用4个机器周期。在编程时要注意选用具有同样功能而机器指令步骤的并行。

试题解析:

串行执行时,总执行时间=100×(t取指+ t分析+ t执行)=100×12△t=1200△t。

流水执行的情况可以参看下图:

连续两条指令的执行时间差为t执行= 5△t,

因此100条指令的总执行时间=(t取指+ t分析+ t执行)+99×t执行= 507△t。

答案:(2)C(3)B

●若内存地址区间为4000H~43FFH,每个存储单位可存储16位二进制数,该内存区

指令流水线:将指令流的处理过程划分为取指、译码、计算操作数地址、取操作数、执行指令、写操作数等几个并行处理的过程段。这就是指令6级流水时序。在这个流水线中,处理器有六个操作部件,同时对这六条指令进行加工,加快了程序的执行速度。目前,几乎所有的高性能计算机都采用了指令流水线。周期数少的指令。

例如:一个指令分为三个步骤,取指4T,分析3T,执行5T。则指令周期为5T【取时间值最长的】,串行运行100条指令的时间是100*(4+3+5)T=1200T,并行执行100条指令的时间是99*5T+(4+3+5)T=507T

C.单工总线、双工总线、外部总线D.逻辑总线、物理总线、内部总线

试题解析:

全国计算机技术与软件专业技术资格(水平)考试历年试题

276

常识。

参考答案:A

●计算机中常采用原码、反码、补码和移码表示数据,其中,±0编码相同的是(3)。

(3)A.原码和补码B.反码和补码C.补码和移码D.原码和移码

试题解析:

域由4片存储器芯片构成,则构成该内存所用的存储器芯片的容量是(4)。

(4)A.512×16bit B.256×8bit C.256×16bit D.1024×8bit

试题解析:

总存储单位=(43FFH - 4000H + 1H)= 400H = 1024(H代表16进制)

每个存储器芯片的容量为:1024 × 16 / 4 = 4096。

试题解析:

ALU属于运算器,不属于控制器。

答案:C

●在CPU与主存之间设置高速缓冲存储器Cache,其目的是为了(2)。

(2)A.扩大主存的存储容量B.提高CPU对主存的访问效率

C.既扩大主存容量又提高存取速度D.提高外存储器的速度

试题解析:

Cache是不具有扩大主存容量功能的,更不可能提高外存的访问速度。但Cache的访

试题解析:

快速I/O设备处理的数据量比较大,更适合采用DMA方式传递数据。

答案:C

● Cache用于存放主存数据的部分拷贝,主存单元地址与Cache单元地址之间的转换

方式由(5)完成。

(5)A.硬件B.软件C.用户D.程序员

试题解析:

当然是硬件啦。

答案:A

●(1)是指按内容访问的存储器。

(1)A.虚拟存储器B.相联存储器

【考试要点】:运算器组成

【参考文档】:/view/147768.htm

控制器

是整个CPU的指挥控制中心,由指令寄存器IR(InstructionRegister)、程序计数器PC(ProgramCounter)和操作控制器0C(OperationController)三个部件组成,对协调整个电脑有序工作极为重要。

历年考题及解析

●在计算机中,最适合进行数字加减运算的数字编码是(1),最适合表示浮点数阶码的数字编码是(2)

(1)A.原码B.反码C补码D.移码

(2)A.原码B.反码C补码D.移码

●(1)不属于计算机控制器中的部件。

(1)A.指令寄存器IR B.程序计数器PC

C.算术逻辑单元ALU D.程序状态字寄存器PSW

答案:C

●高速缓存Cache与主存间采用全相联的地址影像方式,高速缓存的容量为4MB,

分为4块,每块1MB,主存容量为256MB,若主存读写时间为30ns,高速缓存的读写时

间为3ns,平均读写时间为3.27ns,则该高速缓存的命中率为(1)%。若地址更换表如

历年试题及分析

●某指令流水线由5段组成,第1、3、5段所需时间为Δt,第2、4段所需时间分别为3