行业词汇英文缩写

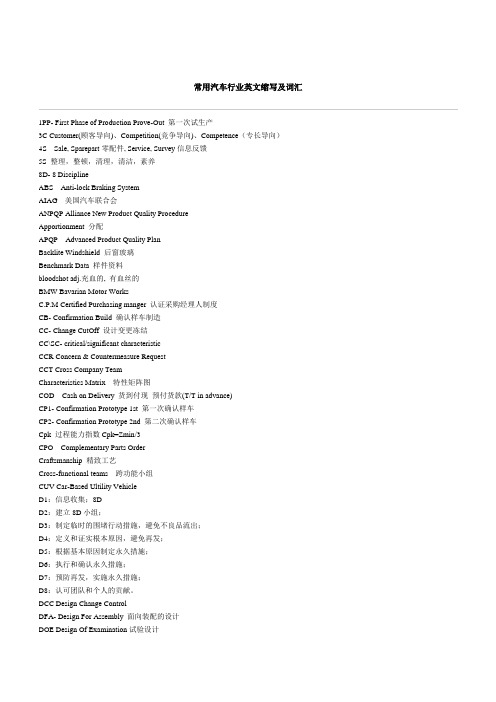

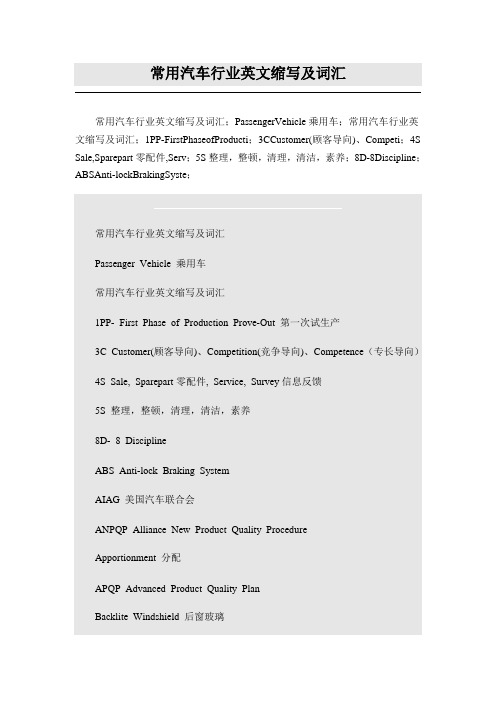

常用汽车行业英文缩写及词汇

常用汽车行业英文缩写及词汇常用汽车行业英文缩写及词汇;PassengerVehicle乘用车;常用汽车行业英文缩写及词汇;1PP-FirstPhaseofProducti;3CCustomer(顾客导向)、Competi;4S Sale,Sparepart零配件,Serv;5S整理,整顿,清理,清洁,素养;8D-8Discipline;ABSAnti-lockBrakingSyste;常用汽车行业英文缩写及词汇Passenger Vehicle 乘用车常用汽车行业英文缩写及词汇1PP- First Phase of Production Prove-Out 第一次试生产3C Customer(顾客导向)、Competition(竞争导向)、Competence(专长导向)4S Sale, Sparepart零配件, Service, Survey信息反馈5S 整理,整顿,清理,清洁,素养8D- 8 DisciplineABS Anti-lock Braking SystemAIAG 美国汽车联合会ANPQP Alliance New Product Quality ProcedureApportionment 分配APQP Advanced Product Quality PlanBacklite Windshield 后窗玻璃Benchmark Data 样件资料bloodshot adj.充血的, 有血丝的BMW Bavarian Motor WorksC.P.M Certified Purchasing manger 认证采购经理人制度CB- Confirmation Build 确认样车制造CC- Change CutOff 设计变更冻结CC\SC- critical/significant characteristicCCR Concern & Countermeasure RequestCCT Cross Company TeamCharacteristics Matrix 特性矩阵图COD Cash on Delivery 货到付现预付货款(T/T in advance) CP1- Confirmation Prototype 1st 第一次确认样车CP2- Confirmation Prototype 2nd 第二次确认样车Cpk 过程能力指数Cpk=Zmin/3CPO Complementary Parts OrderCraftsmanship 精致工艺Cross-functional teams 跨功能小组CUV Car-Based Ultility VehicleD1:信息收集;8DD2:建立8D小组;D3:制定临时的围堵行动措施,避免不良品流出;D4:定义和证实根本原因,避免再发;D5:根据基本原因制定永久措施;D6:执行和确认永久措施;D7:预防再发,实施永久措施;D8:认可团队和个人的贡献。

医院常用缩写

医院常用缩写医院常用缩写是指在医疗行业中常见的缩写词汇,它们通常用于医学文献、医疗记录、医院管理等方面。

这些缩写词汇的使用可以提高工作效率,减少文字冗长,使医疗专业人员更便于理解和交流。

以下是一些常见的医院常用缩写及其解释:1. ICU:重症监护室 (Intensive Care Unit)ICU是专门用于治疗危重病患者的特殊病房,提供高度监护和治疗设备,包括呼吸机、心电监护仪等。

2. ER:急诊室 (Emergency Room)ER是医院内专门用于紧急情况的诊疗区域,提供急救、初步治疗和紧急手术等服务。

3. OPD:门诊部 (Outpatient Department)OPD是医院内提供门诊服务的部门,包括普通门诊、专科门诊等。

4. OR:手术室 (Operating Room)OR是医院内进行手术的专用房间,提供手术所需的设备、器械和无菌环境。

5. MRI:磁共振成像 (Magnetic Resonance Imaging)MRI是一种利用磁场和无线电波来生成人体内部图像的医学检查技术,常用于诊断疾病和评估损伤。

6. CT:计算机断层扫描 (Computed Tomography)CT是一种通过多个X射线图像来重建人体内部结构的医学影像技术,广泛应用于诊断和评估疾病。

7. ECG:心电图 (Electrocardiogram)ECG是一种记录心脏电活动的检查方法,通过测量心脏电信号的变化来评估心脏功能。

8. OT:手术台 (Operation Theater)OT是进行手术的特殊房间,包括手术室、洗手间、换药间等。

9. NICU:新生儿重症监护室 (Neonatal Intensive Care Unit)NICU是专门用于治疗新生儿危重病患者的特殊病房,提供专业的护理和监护。

10. CCU:冠心病监护室 (Coronary Care Unit)CCU是专门用于治疗冠心病患者的病房,提供密切监护和心脏护理。

英语缩写大全

1. AAA :1). American Accounting Association 美国会计协会2). American Advertising Association 美国广告协会3). American Arbitration Association 美国商务仲裁协会2. AAL:American Airlines 美国航空公司3. A.B.C.C.:Association of British Chambers of Commerce 英国商会联合会4. ABS:American Bureau of Shipping 美国船运局5. AC:Air Canada 加拿大航空公司6. ACC:American Chamber of Commerce 美国商会(又简称Amcham)7. A.E.A:American Economic Association 美国经济协会8. AF:Air France 法国航空公司9. AFEB:authorized foreign exchange bank 指定外汇银行10. AFRASEC:Afro-Asian Organization for Economic Cooperation 亚非经济合作组织11. AGM:annual general meeting(公司股东)年度大会12. AID:Agency for International Development(美国)国际开发署13. AMA:American Management Association 美国管理协会14. ASA:American Standards Association 美国标准协会15. Amex:American Stock Exchange 美国证券交易所16. ADB:Asian Development Bank 亚洲开发银行17. APEC: Asia Pacific Economic Cooperation 亚太经济合作组织(2001年10月将在中国上海召开部长级会议和非正式首脑CEO(Chief Executive Officer),即首席执行官,源自美国20世纪60年代进行公司治理结构改革创新时IT是指信息技术,即英文Information Technology 的缩写.BT是一种P2P共享软件,全名叫"BitTorrent",中文全称:"比特流"又名"变态下载"OEM是英文Original Equipment Manufacturer的缩写,意思是原设备制造商。

外贸用语缩写

今天跟大家分享一些外贸行业中常用到的英文此缩略词:1 C&F (cost&freight)成本加运费价2 T/T (telegraphic transfer)电汇3 D/P (document against payment)付款交单4 D/A (document against acceptance)承兑交单5 C.O (certificate of origin)一般原产地证6 G.S.P. (generalized system of preferences)普惠制7 CTN/CTNS (carton/cartons)纸箱8 PCE/PCS (piece/pieces)只、的个、的支等9 DL/DLS (dollar/dollars)美元10 DOZ/DZ (dozen)一打11 PKG (package)一包,一捆,一扎,一件等12 WT (weight)重量13 G.W. (gross weight)毛重14 N.W. (net weight)净重15 C/D (customs declaration)报关单16 EA (each)每个,各17 W (with)具有18 w/o (without)没有19 FAC (facsimile)传真20 IMP (import)进口21 EXP (export)出口22 MAX (maximum)最大的、的最大限度的23 MIN (minimum)最小的,最低限度24 M 或MED (medium)中等,中级的25 M/V (merchant vessel)商船26 S.S (steamship)船运27 MT或M/T (metric ton)公吨28 DOC (document)文件、的单据29 INT (international)国际的30 P/L (packing list)装箱单、的明细表31 INV (invoice)发票32 PCT (percent)百分比33 REF (reference)参考、的查价34 EMS (express mail special)特快传递35 STL. (style)式样、的款式、的类型36 T或LTX或TX(telex)电传37 RMB (renminbi)人民币38 S/M (shipping marks)装船标记39 PR或PRC (price) 价格40 PUR (purchase)购买、的购货41 S/C (sales contract)销售确认书42 L/C (letter of credit)信用证43 B/L (bill of lading)提单44 FOB (free on board)离岸价45 CIF (cost,insurance&freight)成本、的保险加运费价补充:CR=credit贷方,债主DR=debt借贷方(注意:国外常说的debt card,就是银行卡,credit card就是信誉卡。

常用英文缩写

AA.A.R = against all risks 担保全险,一切险A.B.No. = Accepted Bill Number 进口到单编号A/C = Account 账号AC. = Acceptance 承兑acc = acceptance,accepted 承兑,承诺a/c.A/C = account 帐,帐户ackmt = acknowledgement 承认,收条a/d = after date 出票后限期付款(票据)ad.advt. = advertisement 广告adv. = advice 通知(书)ad val. = Ad valorem(according to value) 从价税A.F.B. = Air Freight Bill 航空提单Agt. = Agent 代理商AI = first class 一级AM = Amendment 修改书A.M.T. = Air Mail Transfer 信汇Amt. = Amount 额,金额A.N. = arrival notice 到货通知A.P. = account payable 应付账款A/P = Authority to Purchase 委托购买a.p. = additional premiun 附加保险费A.R. = Account Receivable 应收款Art. = Article 条款,项A/S = account sales 销货清单a/s = after sight 见票后限期付款asstd. = Assorted 各色俱备的att,.attn. = attention 注意av.,a/v = average 平均,海损a/v = a vista (at sight) 见票即付BB/-,b/- = bale,bag 包,装bal.,balce. = balance 余额bbl. = barrel 桶,樽B/C = bill for collection 托收票据B.D. = Bills discounted 贴现票据B/D = bank draft 银行汇票b/d = brought down 承前页B’dle,bdl = bundle 束,把B/E = bill of exchange 汇票B/F = brought forward 承前页bg = bag 袋BIS = Bank for International Settlement 国际清算银行BK = Bank 银行Bkg. = Banking 银行业务B/L = Bill of Lading 提单B/N = bank note 银行纸币B.O. = Branch Office 分支行b/o = brought over 承前bot. = bottle 瓶B/P = bill purchased 买入票据,出口押汇B/P = bills payable 应付票据B/R = bills receivable 应收票据Brl.,barl. = barrel 桶,樽bx = box 箱,盒CC/- = case,currency,coupon 箱,通货,息票c. =cent,centimes,centigrade 分(美),分(法),百分度(寒暑表)C.A. = Credit Advice 收款报单C.A.D. = cash against documents on arrival of good货到后凭单付款c.a.d. = cash against documents 凭单证付现金c.a.f.= cost and freight 成本加运费cat. = catalogue 货品目录C.B. = clean bill 光票C/B = Clean Bill 光票C.B.D. = Cash before delivery 付现金后交货c.c. = carbon copy,cubic centimeter 副本,立方公分C/C,C.C = Chamber of Commerce 商会pC/D = cash against document 凭单据付款C.D. = Collection and Delivery 托交Cert.= Certificate 证明书c/f = carried forward 过次页C&F = cost and freight 运费在内价C.F.S. = container freight station 集装箱集散场c.f.& i. = Cost freight and insurance 运费保险费在内价C.H. = Clearing House 票据交换所C.I. = Certificate of Insurance 保险单C&I = Cost and Insurance 货价及保险c.i.a. = cash in advance 预付现金cif,c.i.f. = cost,insurance and freight 运费保险费在内价c.i.f.&c.= cost,insurance,freight and commission 运费,保险费,利息在内价C.I.F.E. = Cost,Insurance,Freight and Exchange 运费,保险费,汇票在内价C.I.F.I. = Cost,Insurance,Freight and Interest 运费,保险费,利息在内价C.I.F.C.I.= Cost,Insurance,Freight,Commission and Interest 运费,保险费,佣金,利息在内价CK = Check 支票CL = collection 托收CM = Commission 佣金C/N.C.N. = credit note,covering note,consignment note 货方通知,保险承保单,发货通知书C.O. = certificate of origin 产地证明书c/o = care of carried over 烦转,过次页Co. = company 公司c.o.d.= cash on delivery 货到付款Con.Inv. = Concular Invoice 领事发票corp. = corporation 法人,公司C/P = charter party 租船契约cr. = credit 货方,债权人cs = case 箱csk.,ck = cask 樽C.W.O.= cash with order 现金订货,下定付款cwt. = hundred weight 衡量名C.Y. = container yard 集装箱集散场DD/A =documents against acceptance, 承兑后交付单= documents for acceptance,= documents attached, 备承兑单据= deposit account 存款账号d/a = days after acceptance 承兑后……日付款D.A. = Debit advice 付款报单D/D,D. = Demand draft,documentary draft 即期汇票,跟单汇票d/d = day’s date (days after date) 出票后……日付款d.f.,d.fet. = dead freight 空载运费(船)Disc. = Discount 贴现;折扣DLT = Day Letter Telegram 书信电D/N = debit note 借方通知D/O = delivery order 卸货通知书D/P = documents against payment 付款后交付单据Dr. = debit debter 借方,债务人d/s. = days’ sight 见票后……日付款DV = Dividends 股利Eea. = each 每,各e.e.E.E. = error excepted 错误除外E/B = Export-Import Bank 进出口银行(美国)enc.,encl.= enclosure 附件E.& O.E. = errors and omissions excepted 错误或遗漏不在此限ETA = estimated time of arrival 预定到达日期ex. = example,executive,exchange,extract 例子,执行官,外汇交换,摘要Exp. = Export 出口Ff.a.q.=fair average quality 良好平均品质f.a.s.=free alongside ship 船边交货价F.B.E.=foreign bill of exchange 国外汇票f.c.l.=full container load 整个集装箱装满f.d.free discharge 卸货船方不负责F.& D.=Freight and Demurrage 运费及延装费f.i.=free in 装货船方步负责f.i.o.=free in and out 装卸货船方均不负责f.i.o.=free in out stowed and trimming 装卸堆储平仓船方均不负责f.o.=free out 卸货船方不负责f.o.,f/o=firm offer 规定时限的报价f.o.b.=free on board 船上交货价f.o.c.=free of charge免费F.O.I.=free of Interest 免息f.o.r.=free on rail,free on road 火车上交货价f.o.s.=free on steamer 轮船上交货价f.o.t.=free on truck 卡车上交货价f.p.a.=free of particular average 单独海损不保fr.f=franc,from,free 法郎,从,自由FX=Foreign Exchange 外汇Gg=good,goods,gramme 佳,货物,一克G/A=general average 共同海损GATT=General Agreement on Tariffs and Trade 关税贸易总协定gm.=gramme 一克g.m.b.=good merchantable brand品质良好适合买卖之货品g.m.q.=good merchantable quality良好可售品质G/N=Guarantee of Notes 承诺保证g.s.w.=gross shipping weight 运输总重量gr.wt.=gross weight 毛重Hh.=hour,harbour,height 时,港,高度H.O.=Head Office 总公司h.p.=horse power 马力hr.=hour 时IIATA=International Air Transport Association 国际航空运输协会IBRD=International Bank Reconstruction and Development 国际复兴开发银行I/C=Inward Collection 进口托收ICC=International Chamber of Commerce 国际商会IMO=International Money Orders 国际汇票Imp=Import 进口IN=Interest 利息IMF=International Monetary Fund 国际货币基金inst.=instant(this month) 本月int.=interest 利息Inv.=Invoice 发票IOU=I owe you 借据I/P=Insurance Policy 保险单I/R=Inward Remittance 汇入汇款ISIC=International Standard Industrial Classification 国际行业标准分类it.=item 项目Kk.=karat(carat) 卡拉(纯金含有度)kg.=keg,kilogramme笑,公斤K.W.=Kilo Watt 千瓦LL/A=Letter of Authorization 授权书lbs.=pounds 磅L/C=Letter of Credit 信用证L/H=General Letter of Hypothecation 质押权利总股定书L/I=Letter of Indemnity赔偿保证书L/G=Letter of Guarantee 保证函l.t.=long ton 长吨(2,240磅)L/T=Letter Telegram 书信电报Ltd.=Limited 有限责任L/U=Letter of Undertaking 承诺书Mm.=mile,metre,mark,month,minute,meridian(noon)哩,公尺,记号,月,分,中午m/d=month after date 出票后……月付款memo.=memorandum 备忘录M.I.P.=marine insurance policy 海上保险单misc.=miscellaneous杂项M/L=more or less增或减M/N=Minimum最低额MO=Money Order拨款单,汇款单,汇票m/s=months after sight见票后……月付款m.s.=mail steamer,mail transfer油船,轮船M.T.=metric ton,mail transfer公吨,信汇M/T=Mail Transfer信汇m.v.=motor vessel轮船MNC=multi-national corporation跨国公司NN.B.=Nota Bene(take notice)注意NO.=number号码n/p=non-payment拒付Nt.Wt=Net Weight净重OO.=Order定单,定货O.B/L=Order bill of lading指示式提单O.C.P.=Overland Common Point通常陆上运输可到达地点O/C=Outward Collection出口托收OD.=Overdraft透支O/d=overdraft,on demand透支,要求即付款(票据)O/No.=order number定单编号o.p.=open policy预约保单O/R=Outward Remittance汇出汇款ORT=ordinary telegram寻常电报o/s=on sale,out of stock廉售,无存货O/S=old style老式o.t.=old term旧条件oz=ounce盎斯PP/A,p/a=particular average单独海损pa=power of attorney委任状=private account私人账户p.a.=per annum(by the year)每年p.c.=per cent,petty cash百分比,零用金p.l.=partial loss分损P.&I.=Protection and Indemnity意外险P.&L.=profit and loss益损P.M.O.=postal money order邮政汇票P/N=promissory note本票P.O.B.=postal office box邮政信箱p.o.d.=payment on delivery交货时付款P.O.D.=Pay on Delivery发货付款P/O=Payment Order支付命令P/R=parcel receipt邮包收据prox.=proximo(next month)下月PS.=postscript再启pt.=pint品脱P.T.O.=please turn over请看里面PTL=private tieline service电报专线业务Qqlty=quality品质qr=quarter四分之一qty=quantity数量quotn=quotation报价单qy=quay码头Rrecd=received收讫recpt=receipt收据ref.=reference参考,关于RFWD=rain,fresh water damage雨水及淡水险remit.=remittance汇款r.m.=ready money,readymade备用金,现成的RM=Remittance汇款R.O.=remittance Order汇款委托书R.P.=reply paid,returnof post邮下或电费预付,请即会示rt.=rate率SS.A.=-Statement of Account账单s.a.=subject to approval以承认(赞成,批准)为条件S/C=sale contract售货合同S/D=sight draft即期汇票S/D=sea damage海水损害SD.=Sundries杂项SE.=Securities抵押品S/N=shipping note装运通知S.O.s.o.=shipping order,seller’s option装船通知书,卖方有权选择S/S,s/s,ss,s.s=steamship轮船s.t.=short ton短吨TT/A=telegraphic address电报挂号tgm=telegram电报T.L.O.=total loss only只担保全损(分损不赔)T.M.O.=telegraphic money order电报汇款T.R.=trust receipt信托收据T.T.=telegraphic transfer电汇TPND=theft,pilferage and nondelivery盗窃遗失条款Uult.=ultimo(last month)上月u/w=underwriter保险业者Vvoy.=voyage航次V.V.=Vice Versa反之亦然Ww.a.=with average水渍险(单独海损赔偿)war=with risk担保一切险W/B=way bill warehouse book货运单,仓库簿wgt=weight重量whf=wharf码头W/M=weight or measurement重量或容量w.p.a.=with particular average单独海损赔偿W.R.=War Risk战争险W.R.=warehouse receipt仓单wt=weight重量Xx.d.=ex dividend除息XX=good quality良好品质XXX=very good quality甚佳品质XXXX=best quality最佳品质Yyd.=yard码yr.=your,year你的,年Z词汇Z=Zone地区,地带ZCL=Zone di Commercia自由贸易区。

制造业工厂常用英文与缩写词汇大全

制造业工厂常用英文与缩写词汇大全在制造业工厂中,常常会遇到各种各样的英文词汇和缩写词汇。

这些词汇和缩写词汇涉及到不同的工艺、设备、材料和管理等方面。

本文将为大家提供一个制造业工厂常用英文与缩写词汇大全,帮助大家更好地理解和运用这些术语。

一、工艺(Processes)1. Casting: 铸造2. Forging: 锻造3. Machining: 机械加工4. Welding: 焊接5. Stamping: 冲压6. Extrusion: 挤出7. Injection Molding: 注塑8. Polishing: 抛光9. Assembly: 装配10. Coating: 涂层二、设备(Equipment)1. CNC Machine: 数控机床2. Lathe: 车床3. Milling Machine: 铣床4. Grinding Machine: 磨床5. Welding Machine: 焊机6. Injection Molding Machine: 注塑机7. Press Machine: 压机8. Oven: 烤箱9. Conveyor: 输送机10. Crane: 起重机三、材料(Materials)1. Steel: 钢2. Aluminum: 铝3. Copper: 铜4. Plastic: 塑料5. Rubber: 橡胶6. Ceramic: 陶瓷7. Glass: 玻璃8. Wood: 木材9. Stainless Steel: 不锈钢10. Titanium: 钛四、质量与检测(Quality and Inspection)1. Quality Control: 质量控制2. Inspection: 检验3. Defect: 缺陷4. Nonconformance: 不合格5. Tolerance: 公差6. Gauge: 测量工具7. Calibration: 校准8. Sampling: 抽样9. Pass/Fail: 合格/不合格10. Root Cause Analysis: 根本原因分析五、管理与生产(Management and Production)1. Lean Manufacturing: 精益生产2. Six Sigma: 六西格玛3. Kanban: 看板4. Kaizen: 改善5. ISO: 国际标准化组织6. OEE (Overall Equipment Effectiveness): 设备综合效率7. JIT (Just-in-Time): 准时生产8. TPM (Total Productive Maintenance): 全面生产维护9. ERP (Enterprise Resource Planning): 企业资源计划10. MRP (Material Requirements Planning): 物料需求计划六、安全与环保(Safety and Environmental)1. PPE (Personal Protective Equipment): 个人防护装备2. MSDS (Material Safety Data Sheet): 材料安全数据表3. Hazardous Waste: 危险废物4. Pollution Control: 污染控制5. Emergency Evacuation: 紧急疏散6. Fire Suppression: 消防7. Risk Assessment: 风险评估8. Environmental Impact Assessment: 环境影响评估9. Occupational Health and Safety: 职业健康与安全10. Lockout-Tagout (LOTO): 断电锁定标识以上是制造业工厂常用英文与缩写词汇大全,涵盖了工艺、设备、材料、质量与检测、管理与生产以及安全与环保等多个方面。

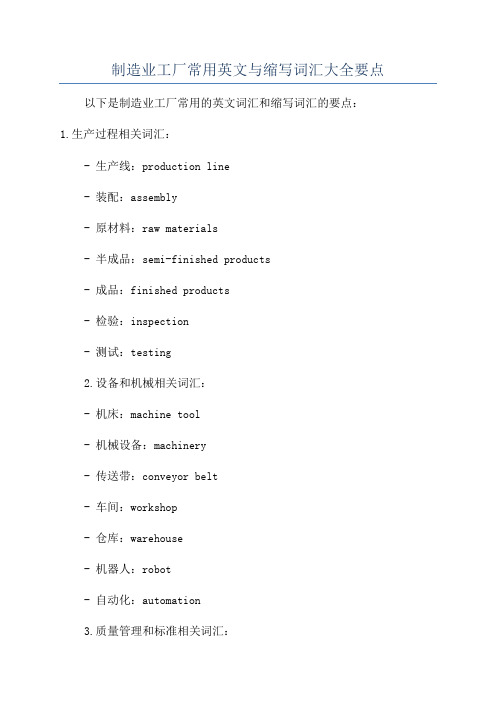

制造业工厂常用英文与缩写词汇大全要点

制造业工厂常用英文与缩写词汇大全要点以下是制造业工厂常用的英文词汇和缩写词汇的要点:1.生产过程相关词汇:- 生产线:production line- 装配:assembly- 原材料:raw materials- 半成品:semi-finished products- 成品:finished products- 检验:inspection- 测试:testing2.设备和机械相关词汇:- 机床:machine tool- 机械设备:machinery- 传送带:conveyor belt- 车间:workshop- 仓库:warehouse- 机器人:robot- 自动化:automation3.质量管理和标准相关词汇:- 质量控制:quality control- 标准化:standardization- 认证:certification- ISO认证:ISO certification- 故障分析:failure analysis4.生产计划和调度相关词汇:- 生产计划:production plan- 生产调度:production scheduling - 生产进度:production progress - 订单:order- 交货期:delivery date- 制定计划:make a plan- 制定预算:make a budget- 任务分配:task assignment5.安全和环保相关词汇:- 安全生产:safe production- 环保:environmental protection - 废物处理:waste disposal- 污染控制:pollution control- 安全防护:safety protection- 事故预防:accident prevention常用缩写词汇示例:- IOT (Internet of Things): 物联网- ERP (Enterprise Resource Planning): 企业资源计划- CRM (Customer Relationship Management): 客户关系管理- QMS (Quality Management System): 质量管理体系- OEE (Overall Equipment Efficiency): 设备综合效率- JIT (Just-in-Time): 精确制时- AM (Additive Manufacturing): 添加制造- LCA (Life Cycle Assessment): 生命周期评估这些只是制造业工厂常用的一些英文词汇和缩写词汇,还有更多的词汇和缩写词汇可以根据具体领域和行业进一步添加。

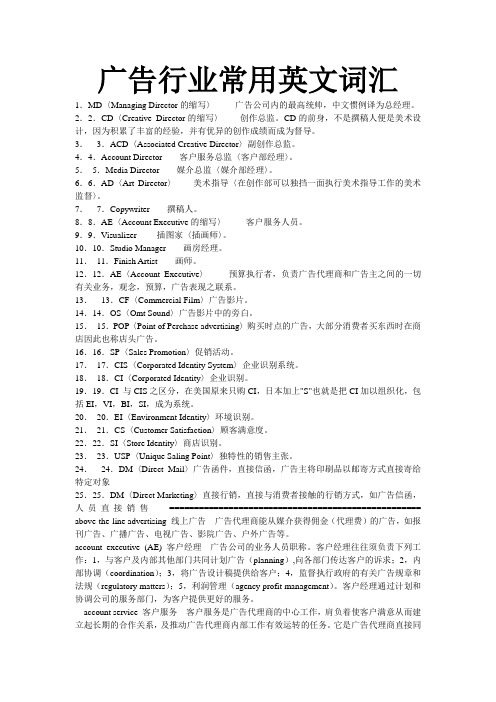

广告行业常用英文词汇

广告行业常用英文词汇1.MD〈Managing Director的缩写〉-------广告公司内的最高统帅,中文惯例译为总经理。

2.2.CD〈Creative Director的缩写〉------创作总监。

CD的前身,不是撰稿人便是美术设计,因为积累了丰富的经验,并有优异的创作成绩而成为督导。

3.3.ACD〈Associated Creative Director〉副创作总监。

4.4.Account Director------客户服务总监〈客户部经理〉。

5.5.Media Director------媒介总监〈媒介部经理〉。

6.6.AD〈Art Director〉------美术指导〈在创作部可以独挡一面执行美术指导工作的美术监督〉。

7.7.Copywriter------撰稿人。

8.8.AE〈Account Executive的缩写〉-------客户服务人员。

9.9.Visualizer-------插图家〈插画师〉。

10.10.Studio Manager------画房经理。

11.11.Finish Artist------画师。

12.12.AE〈Account Executive〉-------预算执行者,负责广告代理商和广告主之间的一切有关业务,观念,预算,广告表现之联系。

13.13.CF〈Commercial Film〉广告影片。

14.14.OS〈Omt Sound〉广告影片中的旁白。

15.15.POP〈Point of Perchase advertising〉购买时点的广告,大部分消费者买东西时在商店因此也称店头广告。

16.16.SP〈Sales Promotion〉促销活动。

17.17.CIS〈Corporated Identity System〉企业识别系统。

18.18.CI〈Corporated Identity〉企业识别。

19.19.CI 与CIS之区分,在美国原来只购CI,日本加上"S"也就是把CI加以组织化,包括EI,VI,BI,SI,成为系统。

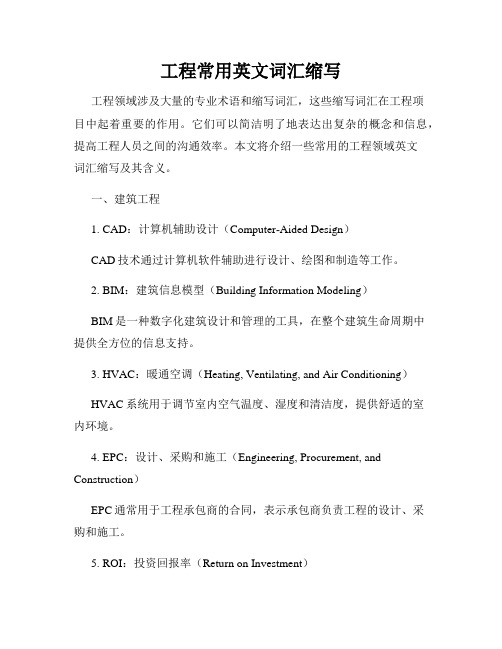

工程常用英文词汇缩写

工程常用英文词汇缩写工程领域涉及大量的专业术语和缩写词汇,这些缩写词汇在工程项目中起着重要的作用。

它们可以简洁明了地表达出复杂的概念和信息,提高工程人员之间的沟通效率。

本文将介绍一些常用的工程领域英文词汇缩写及其含义。

一、建筑工程1. CAD:计算机辅助设计(Computer-Aided Design)CAD技术通过计算机软件辅助进行设计、绘图和制造等工作。

2. BIM:建筑信息模型(Building Information Modeling)BIM是一种数字化建筑设计和管理的工具,在整个建筑生命周期中提供全方位的信息支持。

3. HVAC:暖通空调(Heating, Ventilating, and Air Conditioning)HVAC系统用于调节室内空气温度、湿度和清洁度,提供舒适的室内环境。

4. EPC:设计、采购和施工(Engineering, Procurement, and Construction)EPC通常用于工程承包商的合同,表示承包商负责工程的设计、采购和施工。

5. ROI:投资回报率(Return on Investment)ROI是用来衡量一项投资所带来的经济效益的指标,对于工程项目的投资决策具有重要意义。

二、电气工程1. PLC:可编程逻辑控制器(Programmable Logic Controller)PLC是一种工业自动化控制设备,可对电气系统进行编程控制,实现自动化生产过程。

2. DCS:分散控制系统(Distributed Control System)DCS由多个分散的控制器组成,用于实时监控和控制生产过程中的各个单元设备。

3. UPS:不间断电源(Uninterruptible Power Supply)UPS用于提供电力供应的备份,以防止电力中断对设备和系统造成影响。

4. MCC:电机控制中心(Motor Control Center)MCC用于集中控制和保护设备和系统中的电动机,提高电气系统的效率和可靠性。

汽车行业常见英文缩写及词汇

常用汽车行业英文缩写及词汇1PP- First Phase of Production Prove-Out 第一次试生产3C Customer(顾客导向)、Competition(竞争导向)、Competence(专长导向)4S Sale, Sparepart零配件, Service, Survey信息反馈5S 整理,整顿,清理,清洁,素养8D- 8 DisciplineABS Anti-lock Braking SystemAIAG 美国汽车联合会ANPQP Alliance New Product Quality ProcedureApportionment 分配APQP Advanced Product Quality PlanBacklite Windshield 后窗玻璃Benchmark Data 样件资料bloodshot adj.充血的, 有血丝的BMW Bavarian Motor WorksC.P.M Certified Purchasing manger 认证采购经理人制度CB- Confirmation Build 确认样车制造CC- Change CutOff 设计变更冻结CC\SC- critical/significant characteristicCCR Concern & Countermeasure RequestCCT Cross Company TeamCharacteristics Matrix 特性矩阵图COD Cash on Delivery 货到付现预付货款(T/T in advance)CP1- Confirmation Prototype 1st 第一次确认样车CP2- Confirmation Prototype 2nd 第二次确认样车Cpk 过程能力指数Cpk=Zmin/3CPO Complementary Parts OrderCraftsmanship 精致工艺Cross-functional teams跨功能小组CUV Car-Based Ultility VehicleD1:信息收集;8DD2:建立8D小组;D3:制定临时的围堵行动措施,避免不良品流出;D4:定义和证实根本原因,避免再发;D5:根据基本原因制定永久措施;D6:执行和确认永久措施;D7:预防再发,实施永久措施;D8:认可团队和个人的贡献。

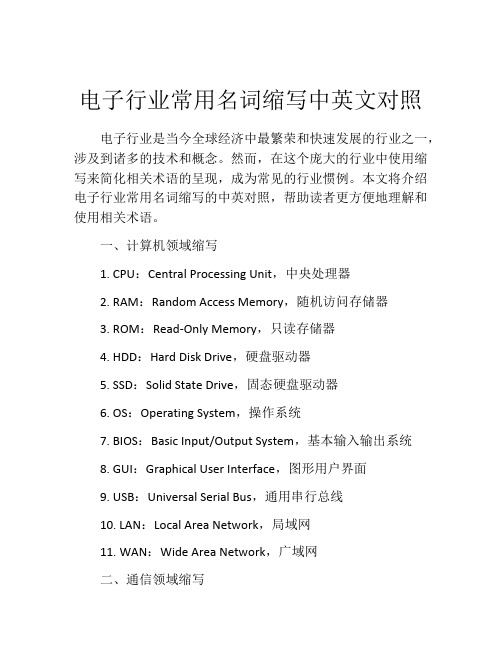

电子行业常用名词缩写中英文对照

电子行业常用名词缩写中英文对照电子行业是当今全球经济中最繁荣和快速发展的行业之一,涉及到诸多的技术和概念。

然而,在这个庞大的行业中使用缩写来简化相关术语的呈现,成为常见的行业惯例。

本文将介绍电子行业常用名词缩写的中英对照,帮助读者更方便地理解和使用相关术语。

一、计算机领域缩写1. CPU:Central Processing Unit,中央处理器2. RAM:Random Access Memory,随机访问存储器3. ROM:Read-Only Memory,只读存储器4. HDD:Hard Disk Drive,硬盘驱动器5. SSD:Solid State Drive,固态硬盘驱动器6. OS:Operating System,操作系统7. BIOS:Basic Input/Output System,基本输入输出系统8. GUI:Graphical User Interface,图形用户界面9. USB:Universal Serial Bus,通用串行总线10. LAN:Local Area Network,局域网11. WAN:Wide Area Network,广域网二、通信领域缩写1. ISP:Internet Service Provider,互联网服务提供商2. VPN:Virtual Private Network,虚拟专用网络3. DNS:Domain Name System,域名系统4. IP:Internet Protocol,互联网协议5. TCP:Transmission Control Protocol,传输控制协议6. UDP:User Datagram Protocol,用户数据报协议7. VoIP:Voice over Internet Protocol,互联网语音传输协议8. LTE:Long-Term Evolution,长期演进技术9. 5G:Fifth Generation,第五代移动通信技术三、显示器领域缩写1. LCD:Liquid Crystal Display,液晶显示器2. LED:Light Emitting Diode,发光二极管3. OLED:Organic Light Emitting Diode,有机发光二极管4. QLED:Quantum Light Emitting Diode,量子点发光二极管5. PPI:Pixels per Inch,每英寸像素密度6. HDR:High Dynamic Range,高动态范围7. SDR:Standard Dynamic Range,标准动态范围8. FHD:Full High Definition,全高清9. UHD:Ultra High Definition,超高清10. DPI:Dots per Inch,每英寸点密度四、存储器领域缩写1. GB:Gigabytes,千兆字节2. MB:Megabytes,兆字节3. TB:Terabytes,万亿字节4. RAID:Redundant Array of Independent Disks,独立磁盘冗余阵列5. NAS:Network Attached Storage,网络附加存储6. SAN:Storage Area Network,存储区域网络五、其他领域缩写1. IoT:Internet of Things,物联网2. AR:Augmented Reality,增强现实3. VR:Virtual Reality,虚拟现实4. AI:Artificial Intelligence,人工智能5. ML:Machine Learning,机器学习6. UI:User Interface,用户界面7. UX:User Experience,用户体验8. CAD:Computer-Aided Design,计算机辅助设计9. CAM:Computer-Aided Manufacturing,计算机辅助制造总体来看,电子行业的常用名词缩写对于提高工作效率和简化沟通起到了重要的作用。

工厂常用英语缩写

BYD公司英语一:常用部门术语Document center (database center) 料中心Design Center 设计中心Shang Hai Test & measurement laboratory 上海检测实验室Molding plant 成型车间Painting plant 烤漆车间Assembly plant 组装车间Stamping plant 冲压车间Business center 商务中心Quality Assurance Department 品保部Project Department 项目部Manufacture Department 制造部Tooling center 模具中心Plan Department 计划部Education and Training 教育训练Training room 教育训练室QCC Quality Control Circle 品质圈PDCA Plan Do Check Action 计划执行检查总结3CComputer 计算机类产品Consumer electronics 消费性电子产品Communication 通讯类产品7SClassification整理(sorting, organization)-seiriRegulation整顿(arrangement, tidiness)-seitonCleanliness清扫(sweeping, purity)-seisoConservation清洁(cleaning, cleanliness)-seiktsuCulture教养(discipline)-shitsukeSave 节约Safety安全二:英文缩写品质人员名称类QC quality control 品质管理人员FQC final quality control 终点质量管理人员IPQC in process quality control 制程中的质量管理人员OQC output quality control 最终出货质量管理人员IQC incoming quality control 进料质量管理人员TQM total quality management 全面质量管理QA quality assurance 质量保证人员QE quality engineering 品质工程人员品质保证类FAI first article inspection 新品首件检查FAA first article assurance 首件确认CP capability index 能力指数CPK capability process index 模具制程能力参数SSQA standardized supplier quality audit 合格供货商品质评估FMEA failure model effectiveness analysis 失效模式分析FQC运作类AQL Acceptable Quality Level 允收品质水准S/S Sample size 抽样检验样本大小ACC Accept 允收REJ Reject 拒收CRI Critical 极严重的MAJ Major 主要的MIN Minor 轻微的Q/R/S Quality/Reliability/Service 品质/可靠度/服务P/N Part Number 料号L/N Lot Number 批号AOD Accept On Deviation 特采UAI Use As It 特采FPIR First Piece Inspection Report 首件检查报告PPM Percent Per Million 百万分之一制程统计品管专类SPC Statistical Process Control 统计制程管制SQC Statistical Quality Control 统计质量管理GRR Gauge Reproductiveness & Repeatability 量具之再制性及重测性判断量可靠与否DIM Dimension 尺寸DIA Diameter 直径N Number 样品数其它品质术语类QIT Quality Improvement Team 品质改善小组ZD Zero Defect 零缺点QI Quality Improvement 品质改善QP Quality Policy 目标方针TQM Total Quality Management 全面品质管理RMA Return Material Audit 退料认可7QCTools 7 Quality Control Tools 品管七大手法通用之件类ECN Engineering Change Notice 工程变更通知(供货商) PMP Product Management Plan 生产管制计划SIP Standard Inspection Procedure 制程检验标准程序SOP Standard Operation Procedure 制造作业规范IS Inspection Specification 成品检验规范BOM Bill Of Material 物料清单PS Package Specification 包装规范SPEC Specification 规格DWG Drawing 图面系统文件类IWS International Workman Standard 工艺标准ISO International Standard Organization 国际标准化组织GS General Specification 一般规格部类PMC Production & Material Control 生产和物料控制PCC Product control center 生产管制中心PPC Production Plan Control 生产计划控制MC Material Control 物料控制DC Document Center 资料中心QE Quality Engineering 品质工程QA Quality Assurance 品质保证QC Quality Control 质量管理PD Product Department 生产部LAB Laboratory 实验室IE Industrial Engineering 工业工程R&D Research & Design 设计开发部生产类PCs Pieces 个(根,块等)PRS Pairs 双(对等)CTN Carton 卡通箱PAL Pallet/skid 栈板PO Purchasing Order 采购订单MO Manufacture Order 生产单D/C Date Code 生产日期码ID/C Identification Code (供货商)识别码SWR Special Work Request 特殊工作需求L/N Lot Number 批号P/N Part Number 料号OEM Original Equipment Manufacture 原设备制造PC Personal Computer 个人计算机CPU Central Processing Unit 中央处理器A.S.A.P As Soon As Possible 尽可能快的E-MAIL Electrical-Mail 电子邮件N/A Not Applicable 不适用QTY Quantity 数量I/O input/output 输入/输出NG Not Good 不行,不合格C=0 Critical=0 极严重不允许APP Approve 核准,认可,承认CHK Check 确认ASS'Y Assembly 装配,组装T/P True Position 真位度5WIH When, Where, Who, What, Why, How to6M Man, Machine, Material, Method, Measurement, Message4MTH Man, Material, Money, Method, Time, How 人力,物力,财务,技术,时间(资源)DQA Design Quality Assurance 设计品质保证MQA Manufacture Quality Assurance 制造品质保证SSQA Sales and service Quality Assurance 销售及服务品质保证LRR Lot Reject Rate 批退率SPS Switching power supply 电源箱DVD Digital Video DiskVCD Video Compact DiskLCD Liquid Crystal DisplayCAD Computer Aided DesignCAM Computer Aided ManufacturingCAE Computer Aided EngineeringPCB Printed Circuit Board 印刷电路板CAR Correction Action Report 改善报告PPM Percent Per Million 百万分之一TPM Total Production Maintenance 全面生产保养MRP Material Requirement Planning 物料需计划OS Operation System 操作系统TBA To Be Assured 待定,定缺D/C Drawing ChangeP/P Plans & ProcedureEMI Electrical-Music Industry 电子音乐工业 Electrical Magnetic Interference 电子干扰RFI Read Frequency Input 读频输入AVL Approved vendor listPOP Procedure of packagingEOL End of lifeVDCS Vender defect correcting sheetPDCS Process defect correcting sheetGRN Goods receiving noteA/R Accounting receivableA/P Accounting payable三:专业词汇通用类responsible department负责单位Human Resources Department 人力资源部Head count 人头数production department生产部门planning department企划部stamping factory冲压厂painting factory烤漆厂molding factory成型厂production unit生产单位meeting minutes会议记录distribution department分发单位subject主题conclusion结论decision items决议事项pre-fixed finishing date预定完成日Color management 颜色管理Visual management 目视管理production capacity生产力first count初盘first check初盘复棹second count 复盘second check复盘复核quantity of physicalinventory second count 复盘点数量physical inventory盘点数量physical count quantity账面数量difference quantity差异量spare parts physicalinventory list备品盘点清单cause analysis原因分析waste materials废料description品名specification 规格model机种work order工令revision版次remark备注registration登记registration card登记卡to control管制application form for purchase请购单consume, consumption消耗to notify通知to fill in填写to collect, to gather收集statistics统计cosmetic inspection standard 外观检验规范computer case 计算机外壳(组件)personal computer enclosure 计算机机箱产品front plate前板rear plate后板chassis |'∫æsi| 基座bezel panel面板Hood 上盖base pan 基座bezel 面板riser card 扩充卡flat cable 排线TOP driver cage 上磁架bottom driver cage 下磁架resin film 树脂膜raw materials原料materials物料steel plate钢板roll/coil material卷料spare parts =buffer备品plastic parts塑料件sheet metal parts/stamping parts 冲件material check list物料检查表finished product成品semi-finished product半成品good product/acceptedgoods/ accepted parts/goodparts良品defective product/non-goodparts不良品disposed goods处理品warehouse/hub仓库packing material包材plastic basket胶筐flow chart流程窗体production tempo生产进度现状lots of production生产批量manufacture procedure制程to revise, modify修订to switch over to, switch—to, switching over切换engineering bottleneck,project difficulty工程瓶颈glove(s)手套glove(s) with exposed fingers割手套Band-Aid创可贴Industrial alcohol工业酒精broom扫把mop拖把vacuum cleaner吸尘器rag 抹布garbage container灰箕garbage can垃圾箱garbage bag垃圾袋liaison联络单rags抹布lamp holder灯架to mop the floor拖地to clean a table擦桌子air pipe 气管delivery deadline交货期die worker模工production, to produce生产equipment设备resistance电阻beacon警示灯coolant冷却液crusher破碎机club car高尔夫球车plate电镀power button电源按键reset button重置键forklift叉车Workshop traveler 天车trailer =long vehicle拖板车Hydraulic trolley手压车hydraulic hand jack油压板车casing = containerization装箱velocity速度patent专利coordinate坐标supply and demand供求career card履历卡barricade隔板carton box纸箱to pull and stretch拉深work cell/work shop工作间sub-line支线bottleneck 瓶颈模具工程类plain die简易模pierce die冲孔模forming die成型模progressive die连续模stage die工程模compound die复合模shearing die剪边模riveting die铆合模feature die公母模male die公模female die母模cavity型控母模core模心公模die change 换模to fix a die装模to repair a die修模punch set上模座punch pad上垫板punch holder上夹板stripper pad脱料背板up stripper上脱料板upper plate上模板lower plate下模板die pad下垫板die holder下夹板die set下模座bottom block下垫脚bottom plate下托板(底板) upper supporting blank上承板upper padding plate blank 上垫板top plate上托板(顶板)top block上垫脚stripping plate内外打(脱料板)outer stripper外脱料板inner stripper内脱料板lower stripper下脱料板punch冲头insert入块(嵌入件) deburring punch压毛边冲子groove punch压线冲子stamped punch字模冲子round punch圆冲子special shape punch异形冲子bending block折刀roller滚轴baffle plate挡块located block定位块supporting block forlocation定位支承块air cushion plate气垫板air-cushion eject-rod气垫顶杆trimming punch切边冲子stiffening rib punch =stinger 加强筋冲子ribbon punch压筋冲子reel-stretch punch卷圆压平冲子guide plate定位板sliding block滑块sliding dowel block滑块固定块die locker锁模器pressure plate =plate pinch压板thickness gauge厚薄规cutting die, blanking die冲裁模die block模块folded block折弯块sliding block滑块location pin定位销lifting pin顶料销die plate, front board模板padding block垫块stepping bar垫条panel board镶块to load a die装上模具to unload a die 御模具active plate活动板lower sliding plate下滑块板upper holder block上压块upper mid plate上中间板spring box弹簧箱spring-box eject-rod弹簧箱顶杆spring-box eject-plate弹簧箱顶板bushing block衬套cover plate盖板guide pad导料块pilot导正筒trim剪外边pierce剪内边pocket for the punch head挂钩槽slug hole废料孔radius半径shim/wedge/heel/pad/spacer/gasket楔子torch-flame cut火焰切割set screw止付螺丝form block折刀round pierce punch =diebutton圆冲子shape punch =die insert异形子stock located block定位块metal plate钣金miller铣床grinder磨床tolerance公差score =groove压线sliding block滑块lathe车active plate活动板baffle plate挡块cover plate盖板groove punch压线冲子air-cushion eject-rod气垫顶杆spring-box eject-plate弹簧箱顶板capability能力parameter参数factor系数driller钻床set up die架模height of die setting up架模高度analog-mode device类模器inner guiding post内导柱inner hexagon screw内六角螺钉dowel pin固定销coil spring弹簧lifter pin顶料销eq-height sleeves =spool等高套筒pin销lifter guide pin浮升导料销guide pin导正销wire spring圆线弹簧outer guiding post外导柱stop screw止付螺丝located pin定位销outer bush外导套press specification冲床规格die height闭模高度flow mark流痕welding mark溶合痕post screw insert螺纹套筒埋值self tapping screw自攻螺丝stripper plate脱料板piston活塞handle mold手持式模具flash mold溢流式模具positive mold挤压式模具split mold分割式模具die lifter举模器top stop上死点bottom stop下死点one stroke一行程to continue, cont.连动to grip(material)吸料location lump, locatingpiece, location block定位块reset复位to file burr 锉毛刺embedded lump |in'bed||l mp|镶块stamping-missing漏冲to tight a bolt拧紧螺栓to loosen a bolt拧松螺栓punched hole冲孔to cut edge =side cut =sidescrap 切边to bending折弯to pull, to stretch拉伸engraving, to engrave刻印stamping 油印to stake铆合designing, to design设计design modification设计修改成gauge(or jig)治具pedal踩踏板stopper阻挡器flow board流水板torque扭矩spline =the multiple keys花键quenching淬火tempering回火annealing退火carbonization碳化alloy合金tungsten high speed steel钨高速的moly high speed steel钼高速的forming成型(抽凸,冲凸)draw hole抽孔bending折弯emboss凸点dome凸圆semi-shearing半剪stamp mark冲记号deburr or coin压毛边punch riveting冲压铆合side stretch侧冲压平reel stretch卷圆压平groove压线stamp letter冲字(料号)tick-mark nearside正面压印tick-mark farside反面压印extension DWG展开图procedure DWG工程图die structure DWG模具结构图冲压类punch, press冲punching machine 冲床hydraulic machine油压机jack升降机decoiler整平机manufacture management制造管理stamping, press冲压feeder送料机rack, shelf, stack料架taker取料机to reverse material 翻料to load material上料to unload material卸料to return material/stock to退料scraped |'skræpid|报废scrape ..v.刮;削robot机械手production line流水线packaging tool打包机packaging打包成型类well type蓄料井insulated runner绝缘浇道方式hot runner热浇道runner plat浇道模块valve gate阀门浇口band heater环带状的电热器spindle阀针spear head刨尖头slag well冷料井cold slag冷料渣air vent排气道welding line熔合痕eject pin顶出针knock pin顶出销return pin回位销反顶针sleeve套筒stripper plate脱料板insert core放置入子runner stripper plate浇道脱料板guide pin导销eject rod (bar)(成型机)顶业捧subzero深冷处理three plate三极式模具runner system浇道系统stress crack应力电裂orientation定向sprue gate射料浇口,直浇口nozzle射嘴sprue lock pin料头钩销(拉料杆)slag well冷料井side gate侧浇口edge gate侧缘浇口tab gate搭接浇口film gate薄膜浇口flash gate闸门浇口slit gate缝隙浇口fan gate扇形浇口dish gate因盘形浇口diaphragm gate隔膜浇口ring gate环形浇口submarine gate潜入式浇口tunnel gate隧道式浇口pin gate针点浇口runner less无浇道sprue less 无射料管方式long nozzle延长喷嘴方式spur浇口;溶waste废料board看板sliding rack滑料架to impose lines压线to compress, compressing压缩character die字模to feed, feeding送料material change, stockchange材料变更feature change 特性变更prepare for, make preparationsfor 准备rotating speed, revolution转速abnormal handling异常处理engineering plastics 工程塑胶 epoxy resin 环氧树脂EPethyl cellulose 乙基纤维素ethylene vinylacetatecopolymer 乙烯-醋酸乙烯EVAethylene-vinlacetatecopolyme 醋酸乙烯共聚物EVAexpanded polystyrene?泡聚苯乙烯EPSfiber reinforcement 纤维强化热固性/纤维强化复合材料high density polyethylene高密度聚乙烯HDPEhigh impact polystyrene 高冲击聚苯乙烯HIPShigh impact polystyrenerigidity 高冲击性聚苯乙烯low density polyethylene 低密度聚乙烯LDPE melamineresin 三聚氰胺酚醛树脂MFnitrocellulose 硝酸纤维素phenolic resin 酚醛树脂plastic 塑胶 polyacrylicacid 聚丙烯酸PAPpolyamide 耐龙PApolybutyleneterephthalate聚对苯二甲酸丁酯PBTpolycarbonate 聚碳酸酯PCpolyethyleneglycol 聚乙二醇PFGpolyethyleneoxide 聚氧化乙烯PEO polyethyleneterephthalate聚乙醇对苯PETP polymetylmethacrylate 聚甲基丙烯酸甲酯PMMA polyoxymethylene 聚缩醛POM polyphenylene oxide 聚硫化亚苯 polyphenyleneoxide 聚苯醚PPOpolypropylene 聚丙烯PP polystyrene 聚苯乙烯PS polytetrafluoroethylene 聚四氟乙烯PTFE polytetrafluoroethylene 聚四氟乙烯polythene 聚乙烯PE polyurethane 聚氨基甲酸酯PUpolyvinylacetate 聚醋酸乙烯PVAC polyvinylalcohol 聚乙烯醇PVApolyvinylbutyral 聚乙烯醇缩丁醛PVBpolyvinylchloride 聚氯乙烯PVCpolyvinylfuoride 聚氟乙烯PVF polyvinylidenechloride 聚偏二氯乙烯PVDC prepolymer 预聚物 silicone resin 矽树脂thermoplastic 热塑性thermosetting 热固性thermosetting plastic 塑胶unsaturated polyester 不饱和聚酯树脂acrylic 压克力 casein 酪素cellulose acetate 醋酸纤维素CA cellulose acetatebutyrate 醋酸丁酸纤维素CABcomposite material 复合材料cresol resin 甲酚树脂CFdially phthalate 苯二甲酸二烯丙酯disperse reinforcement 分散性强化复合材料breathing 排气caulking compound 填隙料cell 气孔cold slug 半凝式射出colorant 著色剂color matching 调色 colormasterbatch 色母料compound 混合料 copolymer共聚合体cull 残料废品 cure 凝固化cryptometer 不透明度仪daylight 开隙dry cycle time 空料试车周期时间 ductility 延性elastomer 弹性体 extrudedbead sealing 压出粒涂层法feed 供料 filler 充填剂film blowing 薄膜吹制法floating platen 活动模板foaming agent 发泡剂 gloss光泽granule 颗粒料 gunk 料斗hot mark 热斑 hot stamping烫印injection nozzle 射出喷嘴injection plunger 射出柱塞injection ram 射出冲柱isomer 同分异构物kneader 混合机 levelingagent 匀涂剂lubricant 润滑剂 matcheddie method 配合成形法mould clamping force 锁模力mould release agent 脱模剂nozzle 喷嘴 oriented film取向薄膜parison 吹气成形坏料pellet 粒料plasticizer 可塑剂 plunger压料柱塞porosity 孔隙率 post cure後固化premix 预混料 purging 清除reciprocating screw 往复螺杆 resilience 回弹性resin injection 树脂射出法rheology 流变学sheet 塑胶片 shot 注射shot cycle 射出循环 slipagent 光滑剂take out device 取料装置tie bar 拉杆toggle type mould clampingsystem 肘杆式锁模装置torpedo spreader 鱼雷形分流板 transparency 透明性void content 空洞率工程试验与试验用语air permeability test 透气性试验 austenitic steel 沃斯田铁钢brinell hardness 布耐内尔硬度 brinell hardness test 布氏硬度试验charpy impact test 夏比冲击试验 conical cup test 圆锥杯突试验cup flow test 杯模式流动度试验 dart drop impact test 落锤冲击试验Elmendorf test 埃罗门多撕裂强度试验 environmental stress cracking test 环境应力龟裂试验ericessen test 埃留伸薄板拉伸试验 falling ball impact test 落球冲击试验fatigue test 疲劳试验 ferrite 纯铁体gantt chart 甘特图 heat cycle test 热循环试验histogram 柱状图 hot bend test 热弯试验izod impact test 埃左德冲击试验 loop tenacity 环结强度martens heat distortion temperature test 马顿斯耐热试验martensite 马氏体 mullen bursting strength tester 密廉式破裂强度试验机nol ring test 诺尔环试验 normal distribution 常态分配ozone resistance test 抗臭氧试验 pareto diagram 柏拉图peeling test 剥离试验 pinhole test 针孔试验机rattler test 磨耗试验 rockweel hardness test 洛氏硬度试验rockweel hardness 洛氏威尔硬度 rolinx process 罗林克斯射出压缩成形法rossi-peakes flow test 罗西皮克斯流动试验 sampling inspection 抽样检查scratch hardness 抗刮硬度 shore hardness 萧氏硬度spiral flow test 螺旋流动试验 surface abrasion test 表面磨耗试验taber abraser 泰伯磨耗试验机 tensile impact test 拉伸冲击试验tensile strength 抗拉强度 tension test 张力试验thermal shock test 冷热剧变试验 torsion test 扭曲试验ubbelohde viscometer 乌别洛德黏度计 vicat indentation test 维卡针压陷试验Vickers hardness test 维氏硬度试验 warpage test 翘曲试验weatherometer 人工老化试验机 weissenberg effect 威森伯格回转效应组装类Assembly line组装线Layout布置图Conveyer流水线运输带Rivet machine拉钉机Rivet gun拉钉枪Screw driver起子Electric screw driver电动起子Hydraulic machine 液压机Pneumatic screw driver气动起子automation自动化to stake, staking, riveting 铆合add lubricant oil加润滑油argon welding氩焊cylinder油缸robot机械手conveying belt输送带transmission rack输送架to draw holes抽孔bolt螺栓nut 螺母screw 螺丝identification tag标示单screwdriver plug起子插座automatic screwdriver电动启子to move, to carry, to handle搬运be put in storage入库packing包装staker = riveting machine铆合机fit together组装在一起fasten锁紧(螺丝)fixture 夹具(治具)pallet/skid栈板barcode条形码barcode scanner条形码扫描仪fuse together熔合fuse machine/heat stake热熔机processing, to process加工delivery, to deliver 交货to return delivery to. to senddelivery back to return ofgoods退货easily damaged parts易损件standard parts标准件to lubricate润滑spring 弹簧spare tools location/buffer手工备品仓spare molds location模具备品仓tox machine自铆机烤漆类phosphate皮膜化成viscosity涂料粘度alkalidipping脱脂main manifold主集流脉organic solvent有机溶剂demagnetization去磁;消磁high-speed transmission高速传递heat dissipation热传rack上料volatile挥发性degrease脱脂rinse水洗alkaline etch龄咬desmot剥黑膜D.I. rinse纯水次Chromate铬酸处理Anodize阳性处理seal封孔scraped products报放品disposed products处理品dismantle the die折模auxiliary function辅助功能heater band 加热片thermocouple热电偶derusting machine除锈机degate打浇口dryer烘干机induction感应induction light感应光response =reaction=interaction感应ram连杆edge finder巡边器concave凸convex凹cold slug冷块blush 导色gouge沟槽;凿槽satin texture段面咬花witness line证示线grit沙砾granule =pellet =grain细粒sand blasting喷沙grit maker抽粒机cushion缓冲fillet镶;嵌边roller pin formality滚针形式cam driver铡楔shank摸柄crank shaft曲柄轴品质类qualified products,up-to-grade products良品defective products, not up-to-grade products不良品defective product box不良品箱poor processing 制程不良poor incoming part来件不良exposed metal/bare metal金属裸露excessive defect过多的缺陷critical defect极严重缺陷major defect主要缺陷minor defect次要缺陷not up to standard不合规格cosmetic defect外观不良lack of painting烤漆不到位slipped screw head/slipperyslipped thread滑丝missing part漏件wrong part错件oxidation氧化defective threading抽芽不良poor staking铆合不良deficient purchase来料不良deficient manufacturingprocedure制程不良cosmetic inspection外观检查inner parts inspection内部检查blister 气泡angular offset 角度偏差dent 压痕scratch 刮伤deformation 变形filings 铁削defective label 不良标签abrasion 磨损Breaking.(be)broken,(be)cracked断裂short射料不足nick缺口speck瑕疪shine亮班splay 银纹gas mark焦痕delaminating起鳞speckle斑点mildewed =moldy = mouldy发霉deformation变形burr(金属)flash(塑件)毛边poor staking铆合不良excessive gap间隙过大grease/oil stains油污inclusion杂质shrinking/shrinkage缩水mixed color杂色fold of packaging belt打包带折皱painting make-up补漆discoloration羿色water spots水渍impurity 杂质Mismatch 错位failure, trouble 故障deformation 变形rust 生锈peel 脱漆Shrink 缩水Contamination 脏污water spots 水渍Gap 间隙label error 标签错误Missing label 漏贴rejection criteria 拒收标准Suspected rejects 可疑庇abrasion 损伤、磨损Texture surface 印花纹表面Streak 条纹stains 污点Blotch 斑点discoloration 脱色Inclusion 杂质slug mark 压痕dirt grime 灰尘blush 毛边薄膜sink 下凹Hickey 漏漆labels and logos 贴纸与商标Configuration labels 组合贴纸corrugated container 瓦摆纸箱Delaminating 脱层splattering 散点Gouge 锉孔puckering 折痕。

汽车行业术语英文缩写

汽车行业术语英文缩写# 汽车行业术语英文缩写## 引言在汽车行业中,使用英文缩写可以简化专业术语的表达,提高沟通的效率。

本文将介绍一些常用的汽车行业术语的英文缩写,以帮助读者更好地理解和应用这些术语。

## 主体以下是一些常见的汽车行业术语及其英文缩写:1. Vehicle Identification Number(VIN):车辆识别码2. Original Equipment Manufacturer(OEM):原始设备制造商3. Electronic Control Unit(ECU):电子控制单元4. Anti-lock Braking System(ABS):防抱死制动系统5. Central Processing Unit(CPU):中央处理器6. On-Board Diagnostics(OBD):车载诊断系统7. Electronic Stability Control(ESC):电子稳定控制系统8. Tire Pressure Monitoring System(TPMS):胎压监测系统9. Powertrain Control Module(PCM):动力总成控制模块10. Continuously Variable Transmission(CVT):无级变速器11. Anti-Theft System(ATS):防盗系统12. Engine Control Unit(ECU):发动机控制单元13. Adaptive Cruise Control(ACC):自适应巡航控制14. Auxiliary Power Unit(APU):辅助动力装置15. Fuel Injection System(FIS):燃油喷射系统除了上述术语外,汽车行业还有许多其他缩写词,它们代表着不同的汽车部件、系统和功能。

通过掌握这些缩写词,读者可以更好地交流和理解汽车行业的相关信息。

## 结论本文介绍了一些常见的汽车行业术语的英文缩写,包括车辆识别码、原始设备制造商、电子控制单元等。

制药行业常用英语词汇(缩写、中英文对照)

tuber

序号 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71

12

组织能力

13

技术人员

14

实施

15

药品生产

16

质量管理

17

质量检验

18

专业技术培训

19

基础理论知识

20

实际操作技能

21

高生物活性

22

高毒性

23

污染

organizational skill technical staff implementation

pharmaceutical manufacturing quality management quality inspection

professional and technicaltraining basic theoreticalknowledge practical operationskills highly potent high toxicity contamination

序号 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47

lighting illumination emergency purification, clean micro-organism, microbiology,microbiologic monitoring

汽车行业专用英语词汇及常用缩写

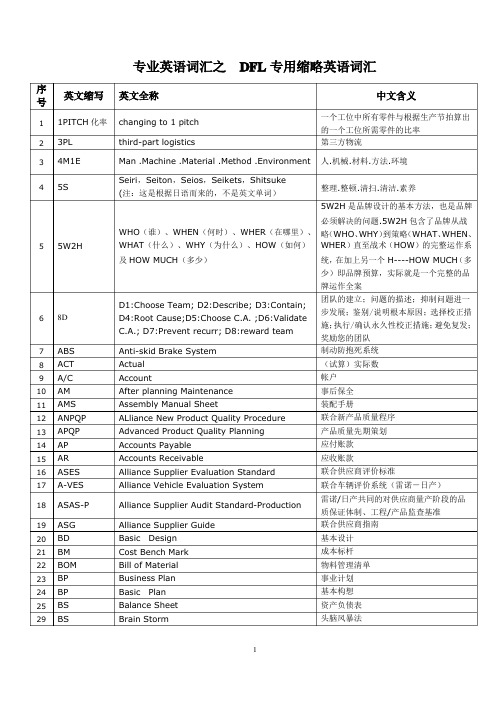

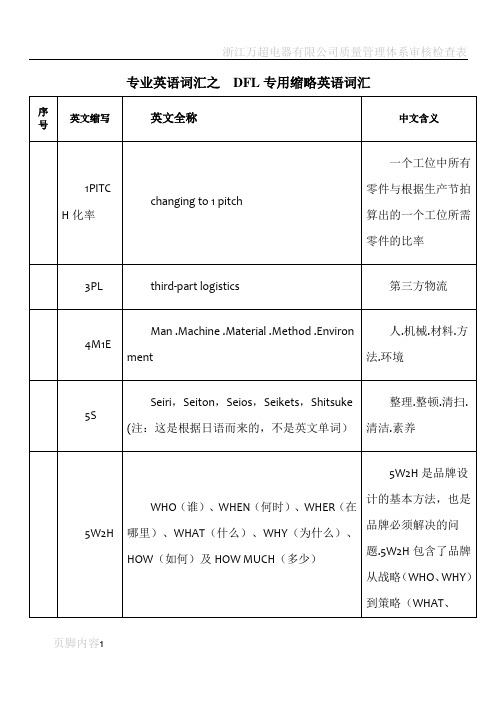

专业英语词汇之DFL专用缩略英语词汇序号12 3 4英文缩写英文全称1PITCH化率3PL4M1E5Schanging to 1 pitchthird-part logistics中文含义一个工位中所有零件与根据生产节拍算出的一个工位所需零件的比率第三方物流Man .Machine .Material .Method .Environment人.机械.材料.方法.环境Seiri,Seiton,Seios,Seikets,Shitsuke整理.整顿.清扫.清洁.素养(注:这是根据日语而来的,不是英文单词)5W2H是品牌设计的基本方法,也是品牌必须解决的问题.5W2H包含了品牌从战WHO(谁)、WHEN(何时)、WHER(在哪里)、略(WHO、WHY)到策略(WHAT、WHEN、55W2H WHAT(什么)、WHY(为什么)、HOW(如何)及HOW MUCH(多少)WHER)直至战术(HOW)的完整运作系统,在加上另一个H----HOW MUCH(多少)即品牌预算,实际就是一个完整的品牌运作全案团队的建立;问题的描述;抑制问题进一步发展;鉴别/说明根本原因;选择校正措施;执行/确认永久性校正措施;避免复发;奖励您的团队制动防抱死系统(试算)实际数帐户事后保全装配手册联合新产品质量程序产品质量先期策划应付账款应收账款联合供应商评价标准联合车辆评价系统(雷诺-日产)雷诺/日产共同的对供应商量产阶段的品质保证体制、工程/产品监查基准联合供应商指南基本设计成本标杆物料管理清单事业计划基本构想资产负债表头脑风暴法D1:Choose Team; D2:Describe; D3:Contain; 68D D4:Root Cause;D5:Choose C.A. ;D6:ValidateC.A.; D7:Prevent recurr; D8:reward team7 8 9 10 11 12 13 14 15 16 171819 20 21 22 23 24 25 29ABSACTA/CAMAMSANPQPAPQPAPARASESA-VESASAS-PASGBDBMBOMBPBPBSBSAnti-skid Brake SystemActualAccountAfter planning MaintenanceAssembly Manual SheetALliance New Product Quality ProcedureAdvanced Product Quality PlanningAccounts PayableAccounts ReceivableAlliance Supplier Evaluation StandardAlliance Vehicle Evaluation SystemAlliance Supplier Audit Standard-ProductionAlliance Supplier GuideBasic DesignCost Bench MarkBill of MaterialBusiness PlanBasic PlanBalance SheetBrain Storm号26 27 28 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49BTBTBUS A-VESCADCAECAPPCAPEXCARCBMCBUCCCCC(3C)CCRCCRCDCEMTCEOCFOCFSCFTCKDCMCMSBusiness TripBusiness TrialBus Alliance-Vehicle Evaluation SystemComputer Aided DesignComputer Aided EngineeringComputer Aided Process PlanningCaptal ExpenditureCountermeasure RequestCondition Based MaintenanceCompletely Build-upCareer CoachChina Compulsory CentificationClose Cycle ReductionConcern & Countermeasure RecurrenceCalendar DayCapital Expenditure Management TeamChief Executive OfficerChief Finance OfficerCash Flow StatementCross-Functional TeamCompleted Knocked DownCommunication ManagementCash Management System短期出差人员业务测试客车联合车辆评价系统计算机辅助设计计算机辅助工程计算机辅助工艺设计资本性支出对策要求状态基准保全完整整车进口职业指导员中国强制认证缩短关账周期防止再发生对策报告书日历日投资管理跨职能小组首席执行官首席财务官现金流量表跨职能工作小组进口件组装通讯管理现金管理系统组件标记,包括在产品上作出的任何标记,用于帮助识别产品。

常用汽车行业英文缩写及词汇

常用汽车行业英文缩写及词汇Passenger Vehicle 乘用车常用汽车行业英文缩写及词汇1PP- First Phase of Production Prove-Out 第一次试生产3C Customer(顾客导向)、Competition(竞争导向)、Competence(专长导向)4S Sale, Sparepart零配件, Service, Survey信息反馈5S 整理,整顿,清理,清洁,素养8D- 8 DisciplineABS Anti-lock Braking SystemAIAG 美国汽车联合会ANPQP Alliance New Product Quality ProcedureApportionment 分配APQP Advanced Product Quality PlanBacklite Windshield 后窗玻璃Benchmark Data 样件资料bloodshot adj.充血的, 有血丝的BMW Bavarian Motor WorksC.P.M Certified Purchasing manger 认证采购经理人制度CB- Confirmation Build 确认样车制造CC- Change CutOff 设计变更冻结CC\SC- critical/significant characteristicCCR Concern & Countermeasure RequestCCT Cross Company TeamCharacteristics Matrix 特性矩阵图COD Cash on Delivery 货到付现预付货款(T/T in advance)CP1- Confirmation Prototype 1st 第一次确认样车CP2- Confirmation Prototype 2nd 第二次确认样车Cpk 过程能力指数Cpk=Zmin/3CPO Complementary Parts OrderCraftsmanship 精致工艺Cross-functional teams 跨功能小组CUV Car-Based Ultility VehicleD1:信息收集;8DD2:建立8D小组;D3:制定临时的围堵行动措施,避免不良品流出;D4:定义和证实根本原因,避免再发;D5:根据基本原因制定永久措施;D6:执行和确认永久措施;D7:预防再发,实施永久措施;D8:认可团队和个人的贡献。

汽车行业专用英语词汇及常用缩写

Critical to Quality

质量关键点

70

CV

Commercial Vehicle

商用车

71

D

Dynamics

动态性能(动力学)

72

DC

Data center

数据中心

73

DCC

Design Change Control

设计更改控制

74

DCPW

Dongfeng Commercialvehicle Production Way

专业英语词汇之DFL专用缩略英语词汇

序号

英文缩写

英文全称

中文含义

1

1PITCH化率

changing to 1 pitch

一个工位中所有零件与根据生产节拍算出的一个工位所需零件的比率

2

3PL

third-part logistics

第三方物流

3

4M1E

Man .Machine .Material .Method .Environment

43

CEO

Chief Executive Officer

首席执行官

44

CFO

Chief Finance Officer

首席财务官

45

CFS

Cash Flow Statement

现金流量表

46

CFT

Cross-Functional Team

跨职能工作小组

47

CKD

Completed Knocked Down

人.机械.材料.方法.环境

4

5S

Seiri,Seiton,Seios,Seikets,Shitsuke (注:这是根据日语而来的,不是英文单词)

常用汽车行业英文缩写及词汇汇总

常用汽车行业英文缩写及词汇常用汽车行业英文缩写及词汇;PassengerVehicle乘用车;常用汽车行业英文缩写及词汇;1PP-FirstPhaseofProducti;3CCustomer(顾客导向)、Competi;4S Sale,Sparepart零配件,Serv;5S整理,整顿,清理,清洁,素养;8D-8Discipline;ABSAnti-lockBrakingSyste;常用汽车行业英文缩写及词汇Passenger Vehicle 乘用车常用汽车行业英文缩写及词汇1PP- First Phase of Production Prove-Out 第一次试生产3C Customer(顾客导向)、Competition(竞争导向)、Competence(专长导向)4S Sale, Sparepart零配件, Service, Survey信息反馈5S 整理,整顿,清理,清洁,素养8D- 8 DisciplineABS Anti-lock Braking SystemAIAG 美国汽车联合会ANPQP Alliance New Product Quality ProcedureApportionment 分配APQP Advanced Product Quality PlanBacklite Windshield 后窗玻璃Benchmark Data 样件资料bloodshot adj.充血的, 有血丝的BMW Bavarian Motor WorksC.P.M Certified Purchasing manger 认证采购经理人制度CB- Confirmation Build 确认样车制造CC- Change CutOff 设计变更冻结CC\SC- critical/significant characteristicCCR Concern & Countermeasure RequestCCT Cross Company TeamCharacteristics Matrix 特性矩阵图COD Cash on Delivery 货到付现预付货款(T/T in advance) CP1- Confirmation Prototype 1st 第一次确认样车CP2- Confirmation Prototype 2nd 第二次确认样车Cpk 过程能力指数Cpk=Zmin/3CPO Complementary Parts OrderCraftsmanship 精致工艺Cross-functional teams 跨功能小组CUV Car-Based Ultility VehicleD1:信息收集;8DD2:建立8D小组;D3:制定临时的围堵行动措施,避免不良品流出;D4:定义和证实根本原因,避免再发;D5:根据基本原因制定永久措施;D6:执行和确认永久措施;D7:预防再发,实施永久措施;D8:认可团队和个人的贡献。

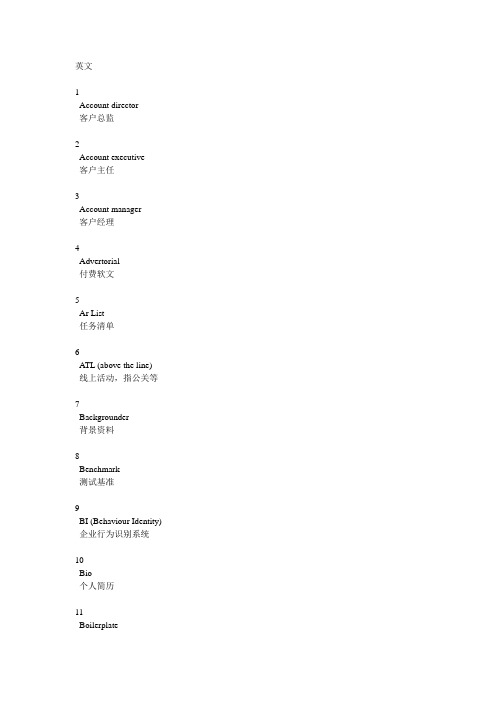

常见的公关行业词汇及缩写

英文1Account director客户总监2Account executive客户主任3Account manager客户经理4Advertorial付费软文5Ar List任务清单6ATL (above the line) 线上活动,指公关等7Backgrounder背景资料8Benchmark测试基准9BI (Behaviour Identity) 企业行为识别系统10Bio个人简历11Boilerplate简介(附在新闻稿后面的关于该公司的简短介绍)12Brand management品牌管理13Briefing简介、情况介绍14Briefing kit情况介绍文件15BTL (below the line)线下活动,指促销活动等16Case study案例研究17CI (Corporate Identity)企业形象18Clipping剪报19Clipping report剪报报告20Competitor竞争对手21Consecutive interpretation交互式翻译22Core media核心媒体23Corporate affairs企业事务24Corporate image企业形象25Corporate profile公司简介26Credential公司或个人简介27Crisis Management 危机管理、危机公关28Customer testimonial 客户证言29Datasheet宣传页30DM (Direct Mailing) 邮寄广告31Editorial Calendar媒体刊登计划32Event活动33Execution34Fact sheet资料(数字或其他材料)35FAQ常见问题问答36Feature文章类型中的通讯37Feature article深度文章38Follow-up跟进39Government Affairs政府事务40Graphics图形文件IMC (integrated marketing communications) 整合营销Interactive PR网上公关41Internal PR内部公关42Interpreter43Interview专访44Journalist记者45Key media核心媒体46Keynote speaker主题演讲人47Keynote speech主题演讲48Logo标志、公司标志49Marcomm (Marketing communications)市场营销50Market analysis report市场分析报告51Mass media大众媒体52MC (Master of Ceremony)主持人53Media54Media inquiry媒体垂询55Media kit通常是提供给媒体的整套资料56Media list媒体名单57Media relations媒体关系58Media tour媒体拜访或媒体外出巡游59Meeting agenda会议议程60Meeting minutes会议记录61Merchandise促销使用的传单、宣传板、礼品等物品的总称MI (Mind Identity)企业理念识别系统62Miscellaneous杂费63Monthly report月工作报告64Negative report负面报道65Newsletter通讯66On-line media网络媒体67oop (out-of-pocket)杂费、日常工作发生的成本68POP (Point Of Purchase Advertising) 导购点广告69Positioning(corporate, product)定位(企业、产品)70postmortem会后书面的简短总结报告71PR guideline公关方针72PR procedures公关流程73Press conference新闻发布会74Press kit提供给媒体的整套材料75Press release新闻稿76Print media平面媒体77Product test产品评测78Professional fee服务费79Project公关项目80Project owner活动负责人81Proposal公关建议书82Public affairs公共事务83Public relations公共关系84Publicity宣传85Q&A86Quotation报价87Rehearsal预演88Report报告89Retainer长期客户90Review回顾、总结91Roadshow巡展、路演92Rude question不友好的问题93Seminar研讨会94Simultaneous interpretation 同声传译95Source materials客户提供的辅助资料96Spokesperson97Success story成功故事98Survey调查99SWOT analysis优势、劣势、机遇、威胁分析100Synopsis概要总结101Vertical media行业媒体102VI (Visual Identity)视觉识别系统103Vision愿景104Whitepaper白皮书Academic community 学术团体Advertising 广告Announcement 公告Article reprints 文章翻印Audiovisual communications 视听沟通Banks,insurers 银行,保险公司Belief 意见、信仰Biography 传记/简历Board of directors 董事会Brand-building 品牌打造Budgeting 预算Bulletin boards 公告牌Business objective 经营目标Byliner 署名作者Case history 个案记录Cause-related marketing 事件营销Change 变革Clerical employees 办公人员Client 客户Communication audits 沟通审查Communication vehicles 沟通工具Community neighbors 社区同胞Community publics 社区公众Community relations 社区关系Competitors 竞争对手Conflict 冲突Confrontation 对峙Conscience 良心Consumer movement 消费者运动Consumer 消费者Consumerism 消费者权益保护Contributions 捐赠Corporate codes of conduct 企业行为准则Corporate image 企业形象Corporate social responsibility 企业的社会责任Corporation 企业Counseling 顾问Cover-up 掩盖(手段)Credibility 可信性Crisis management 危机管理Customers 消费者Database marketing 网络营销Deals/distributors 交易商/分销商Desktop publishing 电脑排版Direct mail 直邮Distortion 歪曲Education 教育Electronic media 电子媒体E-lobbying 电子游说E-mail memorandum 电子邮件备忘录E-mail 电子邮件Employee communication strategies 员工沟通战略Employee communication tactics 员工沟通策略Employee communication 员工沟通Employee families 员工家庭Environment 环境Environmentalism 环境保护Ethics 道德(准则)Evaluation 评价Face-to-face 面谈Federal,state,local legislators联邦,州,当地立法者Financial relations 金融公关Goodwill 商誉Government relations 政府关系Government 政府Grapevine rumor 小道消息。

外贸词汇及英文缩写

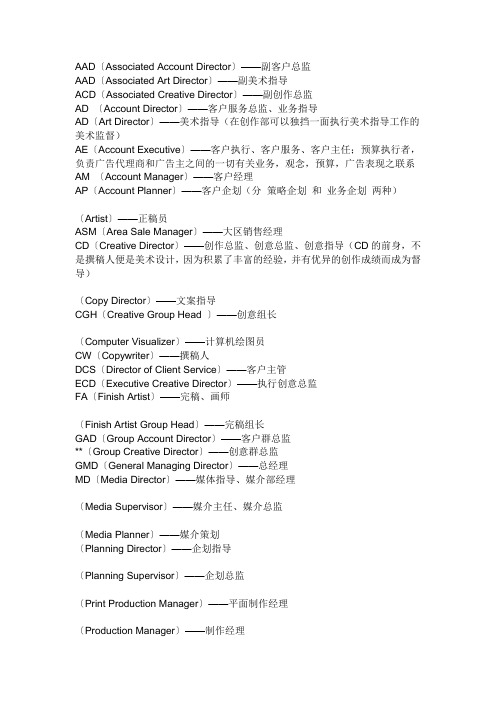

AAD〔Associated Account Director〕——副客户总监AAD〔Associated Art Director〕——副美术指导ACD〔Associated Creative Director〕——副创作总监AD 〔Account Director〕——客户服务总监、业务指导AD〔Art Director〕——美术指导(在创作部可以独挡一面执行美术指导工作的美术监督)AE〔Account Executive〕——客户执行、客户服务、客户主任;预算执行者,负责广告代理商和广告主之间的一切有关业务,观念,预算,广告表现之联系AM 〔Account Manager〕——客户经理AP〔Account Planner〕——客户企划(分策略企划和业务企划两种)〔Artist〕——正稿员ASM〔Area Sale Manager〕——大区销售经理CD〔Creative Director〕——创作总监、创意总监、创意指导(CD的前身,不是撰稿人便是美术设计,因为积累了丰富的经验,并有优异的创作成绩而成为督导)〔Copy Director〕——文案指导CGH〔Creative Group Head 〕——创意组长〔Computer Visualizer〕——计算机绘图员CW〔Copywriter〕——撰稿人DCS〔Director of Client Service〕——客户主管ECD〔Executive Creative Director〕——执行创意总监FA〔Finish Artist〕——完稿、画师〔Finish Artist Group Head〕——完稿组长GAD〔Group Account Director〕——客户群总监**〔Group Creative Director〕——创意群总监GMD〔General Managing Director〕——总经理MD〔Media Director〕——媒体指导、媒介部经理〔Media Supervisor〕——媒介主任、媒介总监〔Media Planner〕——媒介策划〔Planning Director〕——企划指导〔Planning Supervisor〕——企划总监〔Print Production Manager〕——平面制作经理〔Production Manager〕——制作经理〔Research Supervisor〕——调查总监SAD〔Senior Art Director〕——高级美术指导SCW〔Senior Copywriter〕——高级文案〔Studio Manager〕——画房经理、作业室经理〔Traffic Control Specialist(简称Traffic)〕——制管人员〔Traffic Coordinator〕——平面制作统筹〔TV Producer〕——制片〔Visualizer〕——插图家、插画师、绘图员、视觉设计〔Visualizer Group Head〕——视觉设计组长再下这些是其他一些名词:CF〈Commercial Film的缩写〉------广告影片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Glossary of Acronyms Relevant to Electronics ManufacturingACI Automatic Component InsertionANSI American National Standards InstituteAOI Automated Optical Inspection. Test fixture method in which printed circuit boards are checked at bare-board, pre-or post-soldered stages of assembly by opticalmeans.ASIC Application Specific Integrated CircuitASM American Society of MetalsASTE American Society Test EngineersASTM American Society for Testing and MaterialsASQC American Society Quality ControlATE Automatic Test Equipment. Equipment designed to automatically analyze functional or static parameters in order to evaluate performance degradation. Itmay also be designed to perform fault isolation.ATG Automatic Test Generation. Computer generation of a test program based solely on the circuit technology, requiring little or no manual programming effort.BGA Ball Grid Array. A component whose terminations are on the bottom of the package, and are in the shape of solder balls and in a grid array pattern. Thisgenerally covers components that have them in a full array or in a partial arraywith “missing” balls in the center.CAD Computer Aided Design. A computer based system to assist designers in the design, topological layout and drawing of an electronic component, assembly, orsystem.CBGA/CCGA Ceramic Ball Grid Array/Ceramic Column Grid Array. A grid array packaged component that has ceramic as the substrate of the package, and may haveeither solder balls or solder columns for connections.CFC Chlorinated Fluorocarbon.CMA Circuit Mil Area. A unit of area equal to the area of a circle whose diameter is one mil (0.001”). Used chiefly in specifying cross-sectional areas of conductors. CMOS Complementary Metal Oxide SemiconductorCMT Chip Mount Technology. Any packaging or electronic assembly manufacturing technology, such as TOB, COB, or flip chip, that connects bare (unpackaged) ICchips to the substrate.COB Chip-on-Board. A situation where the silicon IC chip is mounted directly to the electronic assembly substrate or PWB without an intermediate packaging step.Connections between the chip and the board are generally made with bond wired(also sometime called chip and wire), but the terminology is occasionally used forany chip connection technique such as flip chip (solderable bumps or tapeautomated bonding.CSP Chip Scale Package. Active, multi-I/O package that is no larger than 125% of the size of the silicon IC.CTE Coefficient of Thermal Expansion. See TCEDFM Design for ManufacturabilityDFT Design for TestDIL Dual In-Line. Component shape with two parallel rows of connection leads.DIP Dual In-Line Package. A popular through hole package with leads in rows on opposite sides of the package.DRAM Dynamic RAM. Read-write memory that must be refreshed (read or written into) periodically to maintain the storage of information.DUT Device Under Test. Component, PCB, or assembly subjected to a test. Also known as unit under test (UUT) and loaded board.EIAJ Electronic Industries Association in JapanESD Electrostatic Discharge. A transfer of electrostatic charge between bodies at different electrostatic potentials caused by direct contact or induced by anelectrostatic field.ESS Environmental Stress Screening. Manufacturing stage in which all assemblies are subjected to abnormal stresses, with the aim of forcing all early failures tooccur. Also known as reliability testing.FCA Flip Chip Attach. The technique of attachment of an IC chip to a substrate using solderable bumps between the silicon chip and substrate.FPT Fine Pitch Technology. The portion of surface mount technology that included components that typically have lead pitch, or center-to-center spacing, between0.4mm and 0.8mm.FP Flat Pack. A low profile IC package, which typically has gull wing type of leads on two or four sides.FR-4The most commonly used epoxy-fiberglass material standard for printed circuit boards. The “FR” refers to flame retardant.HASL Hot Air Soldered Leveled. Hot air is used to blow off the excess after the PWB is dipped in solder. Typically used with the SMOBC process.IC Integrated Circuit. A small, complete circuit made by vacuum deposition and other techniques, usually on a silicon chip, and mounted in a package.IEEE Institute of Electrical and Electronics EngineersILB Inner Lead Bonding. Process of bonding termination, which leads to a tape automated bond integrated circuit’s bumps.IMAPS International Microelectronics and Packaging Society.IMC Intermetallic Compound. Metallic compounds that form at the interfaces between different metals, such as copper-tin compounds that form at the interface of asolder joint and a copper lead. IMCs typically have significantly differentproperties, such as tensile strength.IPC Institute for Interconnecting and Packaging Electronic CircuitsIR Infrared. Soldering process that uses infrared energy as the primary method of heating.ISO International Standards Organization.JEDEC Joint Electronic Devices Engineering Council, a part of the Electronic Industries Association (EIA) that publishes specifications and standards for electroniccomponents.KGB Known Good Board. A correctly operating PCB. It is used in learning ordebugging a test program in development and for comparison testers where itserves as the standard unit by which other PCBs are compared.KGD Known Good DieLCCC Leadless Ceramic Chip Carrier (or CLCC for Ceramic Leadless Chip Carrier). A hermetically sealed ceramic package that has pads (castellations) around itssides for solder connection in a surface mounting application.LDCC Leaded Ceramic Chip Carrier. A hermetically sealed ceramic package that has leads around its sided for solder connection in a surface mounting application.Typically, thee packages have over 28 leads.LSI Large Scale Integration. Arrays of ICs on a single substrate that comprise 100 or more individual active circuit functions or gates.MCM Multichip Module. A circuit comprised of two or more silicon devices bonded directly to a substrate by wire bond, TAB, of flip chip.MELF Metal Electrode Face Bonding. A cylindrical leadless component with a round body and metals terminals on the ends.MLB Mutli Layer Board. A PWB that has more than two conductor layers. The layers are interconnected by the plated-through holes.MSD Moisture Sensitive Device.MTBF Mean Time Between Failures. The arithmetic or statistical mean average time interval, usually in hours, that may be expected between failures of an operatingunit. Results should be designated actual, predicted, or calculated.MTTF Mean Time To Failure. Average time between failures.MTTR Mean Time to Repair. A measure of how long it takes to access a failed system and identify, locate, and repair the fault.OSP Organic Solder Preservative. Layers of organic coatings applied to entire boar surfaces to prevent oxidation and to retain solderability.PBGA Plastic Ball Grid Array. A ball grid array component whose package substrate is made of plastic, most likely an FR-4 equivalent of epoxy-fiberglass, polyimide-arramid, or similar resin-fiber combinations.PCA Printed Circuit Assembly. The generic term for a PCB after all electricalcomponents have been attached. Also referred to as a printed wiring assembly(PWA).PCB Printed Circuit Board. A part manufactured from a rigid base material upon which a completely processed printed circuit has been formed.PGA Pad Grid Array. Similar to a pin grid array. An IC package that has solderable connections in a grid layout on the bottom of the package, and is soldered to thesurface of the substrate (PWB) with butt solder joints.PCMCIA Personal Computer Memory Card International Association. The organization that has developed the early standards for the various sizes of modules whichwere initially for memory expansion but are now used for many differentelectronic functions.PLCC Plastic Leaded Chip Carrier. A plastic IC package for surface mountingapplications that has leads, generally “J” leads, on all fours sides (sometimesgiven as PCC or PLDCC).PPM Parts Per MillionPQFP Plastic Quad Flat Pack. An FP with leads on fours sides. Generally refers to a plastic quad flat package that is built to JEDC standards.PTH Plated Through Hole. An interconnection from one side of a PWB (PCB) to another that is formed with the copper plating of the via (hole) sidewalls.PWA Printed Wiring Assembly. The generic term for a PWB after all electricalcomponents have been attached.PWB Printed Wiring Board. The substrate, generally epoxy glass, used to provide component attachment lands and interconnections to form a functioningelectronic circuit (also called a PCB or printed circuit board).QFP Quad Flat Pack. A FP with leads on four sides. Generally refers to a plastic quad flat package that is built to EIJ standards.QPL Qualified Products List. A listing of manufacturers qualified by test andperformance verification to produce items listed in the MIL specs.QSOP Quarter-Size Small Outline Package. An SO style IC package that has leads ona 25 mil pitch. The name derives from the fact that the package is approximately½ the length and ½ the width of a standard SOIC, and thus a package of thesame pin count occupies approximately ¼ the area on a PWB.RAM Random Access Memory. A type of memory that offers access to storage locations within it by means of X and Y coordinates.RCC Rectangular Chip Carrier. A chip carrier with unequal length and widthdimensions.ROM Read Only Memory. A random access storage in which the data pattern is unchangeable after manufacture.SCC A chip carrier with a square body.SIP Single-In-Line Package. An IC package or multi-component sub-assembly that has connections or leads in a single row on one side.SIR Surface Insulation ResistanceSMA Surface Mount Assembly. An electronic assembly or module that ismanufactured with surface mounted components and suing surface mounttechnology.SME Society of Manufacturing EngineersSMTA Surface Mount Technology AssociationSMC (SMD)Surface mount components. Any electrical or mechanical component that can be attached to the surface of a substrate with solder.SMOBC Solder Mask Over Bare Copper. A printed wiring board manufacturing technique whereby solder mask is applied over bare copper, exposed and developed, andthen the board is dipped in molten solder to coat the exposed copper.SMT Surface Mount Technology. The technology used to manufacture electronic assemblies using components that are soldered directly to the surface of thesubstrate or PWB.SO Small Outline. A package resembling a flat pack with leads on only two sides. SOIC Small Outline Integrated Circuit. A plastic IC package for surface mounting applications that has leads on two opposite sides.SOJ A plastic IC package with “J” leads on two sides. It resembles a plastic DIP or an SOIC except for lead spacing and forming.SOL/SOW Small Outline-Large/Small Outline Wide. SO generally refers to a package that is approximately 150 mils wide, while SOL/SOW refers to packages that areapproximately 300 mils wide.SOP VSOP/SSOP. Another designation for the small outline ICP packages, i.e. Small Outline Package (Very Small Outline Package, Shrink Small Outline Package) SOT Small Outline Transistor. A plastic leaded package for diodes and transistors used in surface mounting applications.SPC Statistical Process Control. The use of statistical techniques to analyze a process or its output to determine any variation from a benchmark and to takeappropriate action to restore statistical control, if required.SSOIC Shrink Small Outline IC. An SO style IC package that has leads on a 25 mil pitch.TAB Tape Automated Bonding. An IC interconnection process that uses organic tape to support pre-formed leads during bonding to the chip (inner lead bonding-ILB)and connection to the substrate (outer lead bonding-OLB). The IC chip is usuallybare during the interconnecting processes.TBGA Tape Ball Grid Array. A ball grid array component package that uses TAB techniques to make the connections between the IC chip and the solder balls.This results in a solder ball grid array that is only around the periphery, andleaves compliant connections between the IC and the solder balls for better TCEreliability.TCE (CTE)Thermal Coefficient of Expansion (Coefficient of Thermal Expansion). The rate of expansion (ppm/C) of a material when its temperature is increased.VFP Very Fine Pitch. The center-to-center lead distance of surface mount packages that are between 0.012 inch and 0.020 inch.VLSI Very Large Scale IntegrationVSP Vapor Phase Soldering. Soldering accomplished by using heat generated by the condensing of a vapor ion a cooler assembly. VSP is achieved with SMT byusing a high temperature, approximately 215 degrees C, special prefluorinatedfluid.VSOIC Very Small Outline IC. An SO style IC package that has leads with a pitch of 30 mils or less.Sources Used:“Understanding and Using Surface Mount and Fine Pitch Technology”, CharlesHutchins, 1995.“Surface Mount Technology: Principles and Practice”, Ray Prasad, 1997.“Surface Mount Technology Terms and Concepts”, Phil Zarrow and Debra Kopp,ITM, 1997.。