DSP完整课件第3章

合集下载

dsp第四讲第3章C C程序编写基础PPT课件

义和共同体定义。

20 盐城工学院 电气工程学院

DSP应用技2术0

1.定义寄存器文件结构

表3.2 SCI-A和SCI-B的公共寄存器文件

21 盐城工学院 电气工程学院

DSP应用技2术1

[例3.3] SCI寄存器文件结构定义

/******************************************************

第3章 C/C++程序编写基础

1 盐城工学院 电气工程学院

DSP应用技术1

整体概况

概况一

点击此处输入 相关文本内容

01

概况二

点击此处输入 相关文本内容

02

概况三

点击此处输入 相关文本内容

03

2 盐城工学院 电气工程学院

DSP应用技术2

3.1 C/C++编辑器概述

TMS320X28xx的C编译器是一个功能齐全的优化 编译器,可以利用该编译器将标准的ANSI C/C++程 序直接转换成TMS320X28xx处理器的汇编代码。

4 盐城工学院 电气工程学院

DSP应用技术4

3.1.2 输出文件

TMS320X28xx编译器输出下列代码:

(1) 汇编源代码输出

TMS320X28xx编译器可以产生汇编语言源码文件,

方便用户查看由C/C++产生的汇编源代码。

(2) COFF目标文件

通过目标文件格式(COFF)允许用户在连接时定义系

Union SCIFFRX_REG SCIFFRX; //FIFO接收寄存器

Union SCIFFCT_REG SCIFFCT; //FIFO控制寄存器

Uint16 rsvd2; //保留存储空间

20 盐城工学院 电气工程学院

DSP应用技2术0

1.定义寄存器文件结构

表3.2 SCI-A和SCI-B的公共寄存器文件

21 盐城工学院 电气工程学院

DSP应用技2术1

[例3.3] SCI寄存器文件结构定义

/******************************************************

第3章 C/C++程序编写基础

1 盐城工学院 电气工程学院

DSP应用技术1

整体概况

概况一

点击此处输入 相关文本内容

01

概况二

点击此处输入 相关文本内容

02

概况三

点击此处输入 相关文本内容

03

2 盐城工学院 电气工程学院

DSP应用技术2

3.1 C/C++编辑器概述

TMS320X28xx的C编译器是一个功能齐全的优化 编译器,可以利用该编译器将标准的ANSI C/C++程 序直接转换成TMS320X28xx处理器的汇编代码。

4 盐城工学院 电气工程学院

DSP应用技术4

3.1.2 输出文件

TMS320X28xx编译器输出下列代码:

(1) 汇编源代码输出

TMS320X28xx编译器可以产生汇编语言源码文件,

方便用户查看由C/C++产生的汇编源代码。

(2) COFF目标文件

通过目标文件格式(COFF)允许用户在连接时定义系

Union SCIFFRX_REG SCIFFRX; //FIFO接收寄存器

Union SCIFFCT_REG SCIFFCT; //FIFO控制寄存器

Uint16 rsvd2; //保留存储空间

DSP第三章.ppt

RPT后面的一条指令重复执行多次。

二、程序地址的产生

程序地址产生的情况

▲ 顺序操作:程序的地址来源于PC程序计数器(程序地址+1) ▲ 空(哑)周期:程序的地址来源于PAR (程序地址+1) ▲ 从子程序返回:程序的地址来源于栈顶(TOS) ▲ 从表传送或块传送返回:程序的地址来源于转移或调用指

PSC

TDDR

R-0

D15

PSCH

D8 D7

R/W-0

D0

TDDRH

R-0

R/W-0

一、时钟及系统控制

看门狗及其应用

F2812的看门狗与240x的基本相同,当8位的看门狗计数 器计数到最大值时,看门狗模块产生一个输出脉冲(512个振荡 器时钟宽度)。如果不希望产生脉冲信号,用户需要屏蔽计数 器,或用软件周期向看门狗复位控制寄存器写“0x55+0xAA", 该寄存器能够使看门狗计数器清零。

SUBC(条件减)

希望同学们坚信:

数据存储区中建立一个堆栈。

二、程序地址的产生

堆 栈 例 子

二、程序地址的产生

堆栈例子

二、程序地址的产生

微

堆 ▲ 一级深、16位宽,操作不可见,即无指令,只有程序

栈

地址产生逻辑才能够使用微堆栈。

▲ 程序地址产生逻辑在执行BLDD、BLPD、MAC、MACD、 TBLR 和TBLW 这些串(块)操作指令时利用微堆栈保 存返回地址。

WDCHK

R/W-0

R/W-0

D0

WDCNTR

R/W-0

D0

WDKEY

R/W-0

D8

D3 D2

D0

R/W-0WDPS

二、程序地址的产生

二、程序地址的产生

程序地址产生的情况

▲ 顺序操作:程序的地址来源于PC程序计数器(程序地址+1) ▲ 空(哑)周期:程序的地址来源于PAR (程序地址+1) ▲ 从子程序返回:程序的地址来源于栈顶(TOS) ▲ 从表传送或块传送返回:程序的地址来源于转移或调用指

PSC

TDDR

R-0

D15

PSCH

D8 D7

R/W-0

D0

TDDRH

R-0

R/W-0

一、时钟及系统控制

看门狗及其应用

F2812的看门狗与240x的基本相同,当8位的看门狗计数 器计数到最大值时,看门狗模块产生一个输出脉冲(512个振荡 器时钟宽度)。如果不希望产生脉冲信号,用户需要屏蔽计数 器,或用软件周期向看门狗复位控制寄存器写“0x55+0xAA", 该寄存器能够使看门狗计数器清零。

SUBC(条件减)

希望同学们坚信:

数据存储区中建立一个堆栈。

二、程序地址的产生

堆 栈 例 子

二、程序地址的产生

堆栈例子

二、程序地址的产生

微

堆 ▲ 一级深、16位宽,操作不可见,即无指令,只有程序

栈

地址产生逻辑才能够使用微堆栈。

▲ 程序地址产生逻辑在执行BLDD、BLPD、MAC、MACD、 TBLR 和TBLW 这些串(块)操作指令时利用微堆栈保 存返回地址。

WDCHK

R/W-0

R/W-0

D0

WDCNTR

R/W-0

D0

WDKEY

R/W-0

D8

D3 D2

D0

R/W-0WDPS

二、程序地址的产生

DSP原理与应用课件

Ⅱ、整数乘整数(数用Q0表示) Q0×Q0=Q0 举例:13×5 = 65 操作数用Q0表示为: 13 = 0000 0000 0000 1101B 5 = 0000 0000 0000 0101B 0000 0000 0000 1101 × 0000 0000 0000 0101 = 0000 0000 0000 0000 0000 0000 0100 0001 = 00000041H 表示的浮点数即为:65处理,如滤波、FFT、卷积等; ● 通信,如调制解调、纠错编码、传真、可 视电话等; ● 语音处理,如语音编码、语音合成、识别、 语音存储等; ●图形/图像处理,如模式识别、图像压缩与 传输、动画、机器人视觉等; ●仪器仪表,如数据采集、函数/波形产生等; ●军事,如保密通信、全球定位、雷达与声 纳信号处理、导航与制导等; ●医疗,如核磁共振、自动治疗仪等。

Ⅲ、混合表示法

在对精度和数据范围要求都比较高的情况下,两个 数可以采用介于Q15与Q0之间的不同的Q表示法。 举例: 设参与运算的两个数x和y的数值范围分别不超过± 1和± 4,两个数的Q值分别为Q15和Q13,为了保证数据 范围,应该采用Q13。例如: x = 0.4 y = 3.2 ,计算x + y 因为 xd = 3276, yd = 26214,则 xd + yd = 3276 + 26214 = 29490 转换为浮点数为:29490 × 2-13 ≈ 3.59985

●举例2:求3/40= ? step1:3 < 40 ,次数=0,余数=3 ; step2:3×10 = 30,30 <40,次数=0,余数=30; step3:30×10=300,300 > 40;300 - 40=260,执行第1次减 法;260 - 40=220,执行第2次减法; 220 - 40=180,执行第3次 减法;180 - 40=140,执行第4次减法;140 - 40=100,执行第5 次减法;100 - 40=60,执行第6次减法;60 - 40=20,执行第7 次减法;次数=7,余数=20; step4: 20×10=200,200 > 40; 200 - 40=160,执行第1次 减法;160 - 40=120,执行第2次减法;120 - 40=80,执行第3 次减法; 80 - 40=40,执行第4次减法; 40 - 40=0,执行第5次 减法;次数=5,余数=0; step5:结果=0 ×100 +0 ×10-1 + 7×10-2 +5 ×10-3 = 0.075

数字信号处理基础pptDSP第3章

(2) 补零到L点长 x(m)L、 h((m))LRL(m) (3) 将h((m))LRL(m)翻褶为h((−m))LRL(m) (4) h((−m))LRL(m)与x(m)对应位相乘相加得 yc(0)

(5) 循环右移到h((n−m))LRL(m),与x(m)相乘相加得 yc(n)

例3-6 x(n)= {1, 2, 3},0 n 2;h(n)= {1, 2, 2, 1},0n3。

翻褶 翻褶循环右移1位

§3.2.2 有限长复序列共轭的DFT

DFT[ x*( N n)]N X *(k), 0 k N 1

DFT[ x*(n)]N X *( N k), 0 k N 1

证明:

X*(N

k)

N 1

x(n)W

n0

(N N

k

)n

*

N 1

x(n)W

n0

N

kn

n 4 3 2 1 0 1 2 3 4 5

y(n4) 1 4 9 11 8 3

y(n)

1 4 9 11 8 3

yc1(n)

9 7 9 11

3. 循环卷积定理 x(n)长度M,h(n)长度N,L max(M, N) yc(n) = x(n) L h(n),Yc(k) = X(k)H(k) DFT[x1(n)x2(n)]L = X1(k) L X2(k)/L 0nL1,0kL1

N 4,

X (k)4

1 e j2k 1 e jk 2

4, 0,

k0 1k 3

4 (k),

0 k 3

N 8,

X (k)8

1 e jk 1 e jk 4

,

0

k

7

N 16,

X (k )16

1 e jk 1 e jk

(5) 循环右移到h((n−m))LRL(m),与x(m)相乘相加得 yc(n)

例3-6 x(n)= {1, 2, 3},0 n 2;h(n)= {1, 2, 2, 1},0n3。

翻褶 翻褶循环右移1位

§3.2.2 有限长复序列共轭的DFT

DFT[ x*( N n)]N X *(k), 0 k N 1

DFT[ x*(n)]N X *( N k), 0 k N 1

证明:

X*(N

k)

N 1

x(n)W

n0

(N N

k

)n

*

N 1

x(n)W

n0

N

kn

n 4 3 2 1 0 1 2 3 4 5

y(n4) 1 4 9 11 8 3

y(n)

1 4 9 11 8 3

yc1(n)

9 7 9 11

3. 循环卷积定理 x(n)长度M,h(n)长度N,L max(M, N) yc(n) = x(n) L h(n),Yc(k) = X(k)H(k) DFT[x1(n)x2(n)]L = X1(k) L X2(k)/L 0nL1,0kL1

N 4,

X (k)4

1 e j2k 1 e jk 2

4, 0,

k0 1k 3

4 (k),

0 k 3

N 8,

X (k)8

1 e jk 1 e jk 4

,

0

k

7

N 16,

X (k )16

1 e jk 1 e jk

DSP原理与应用-课件

多处理器结构

本书的 封面

走信息路 读北邮书

1.2.2 与CPU、MCU、FPGA/CPLD的比较

与CPU、MCU、FPGA/CPLD的比较

尽管微处理器集成度很高,但仍需要较多的外围电路, 使得其性价比、体积、功耗都都比DSP大的多。 但单片机的控制接口种类比DSP多,适用于以控制为主 的模数混合设计,同时在成本上单片机的价格也低的 多。

(4)图形/图像处理:如三维图像变换、模式识别、

图像增强、动画、电子地图等。

(5)自动控制:如机器人控制、自动驾驶、发动机控

制、磁盘控制等。

本书的

封面

走信息路 读北邮书

2.1 TMS320C54x的硬件结构特性

2.1.1 TMS320C54X的硬件结构 2.1.2 TMS320C54X的主要特性

走信息路 读北邮书

1.2.1 DSP芯片的特点 1.2.2 与CPU、MCU、FPGA/CPLD的比较 1.2.3 DSP产品简介

走信息路 读北邮书

本书的 封面

1.1

数字信号处理概述

数字信号处理概述

DSP可以代表数字信号处理技术(Digital Signal Processing),也 可以代表数字信号处理器(Digital Signal Processor

走信息路 读北邮书

本书的 封面

2.1.2 TMS320C54x的主要特性

1

CPU

2

存储器

3 片内外设

4 指令系统

走信息路 读北邮书

本书的 封面

2.1.2

CPU

CPU

(1) 先进的多总线结构(1条程序总线、3条数据总线和4

条地址总线)。

(2) 40位算术逻辑运算单元(ALU)。包括1个40位桶形移

本书的 封面

走信息路 读北邮书

1.2.2 与CPU、MCU、FPGA/CPLD的比较

与CPU、MCU、FPGA/CPLD的比较

尽管微处理器集成度很高,但仍需要较多的外围电路, 使得其性价比、体积、功耗都都比DSP大的多。 但单片机的控制接口种类比DSP多,适用于以控制为主 的模数混合设计,同时在成本上单片机的价格也低的 多。

(4)图形/图像处理:如三维图像变换、模式识别、

图像增强、动画、电子地图等。

(5)自动控制:如机器人控制、自动驾驶、发动机控

制、磁盘控制等。

本书的

封面

走信息路 读北邮书

2.1 TMS320C54x的硬件结构特性

2.1.1 TMS320C54X的硬件结构 2.1.2 TMS320C54X的主要特性

走信息路 读北邮书

1.2.1 DSP芯片的特点 1.2.2 与CPU、MCU、FPGA/CPLD的比较 1.2.3 DSP产品简介

走信息路 读北邮书

本书的 封面

1.1

数字信号处理概述

数字信号处理概述

DSP可以代表数字信号处理技术(Digital Signal Processing),也 可以代表数字信号处理器(Digital Signal Processor

走信息路 读北邮书

本书的 封面

2.1.2 TMS320C54x的主要特性

1

CPU

2

存储器

3 片内外设

4 指令系统

走信息路 读北邮书

本书的 封面

2.1.2

CPU

CPU

(1) 先进的多总线结构(1条程序总线、3条数据总线和4

条地址总线)。

(2) 40位算术逻辑运算单元(ALU)。包括1个40位桶形移

第三章DSP指令寻址方式

DP值 0000 0000 0

偏移量 000 0000

数据存储器 第0页:0000h~007Fh

0000 0000 0 0000 0000 1

0000 0000 1 0000 00010

0000 00010 1111 1111 1

1111 1

~ ~ ~ ~

111 1111 000 0000 第1页:0080h~00FFh

址,而是将此地址(或寄存器)内容再作为地址。间接

寻址通过8个16位的辅助寄存器访问数据存储器。

1.1 立即寻址方式 在立即寻址方式中,指令字中包含指令所需 的一个常数。两种立即寻址方式为: 短立即寻址。用短立即寻址的指令将一个8位、9 位或13位的常数作为操作数。短立即寻址指令为 一个单指令字,并且有一个常数嵌在该指令中。 长立即寻址。用常立即寻址的指令将一个16位常 数作为操作数,从而需要两个指令字。该常数作 为第二个指令字被发送。这个16位字值可以是绝 对常数或二进制补码。

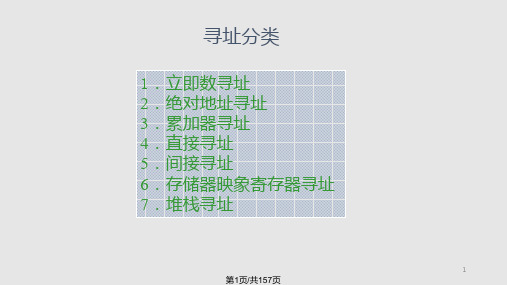

3.1 DSP指令寻址方式

也称为立即数寻址方式。

立即寻址:需要找的数据就在指令里,不需要存储器找, 直接寻址:即指令给出的是需要找的数的地址,按此地

址直接访问即可。直接寻址将指令字的7位与数据存储 器页指针(DP)的9位连接起来,形成一个16位数据存 储器地址。 间接寻址:即指令给出的既不是立即数,也不是直接地

下一个辅助寄存器 除了更新当前辅助寄存器的内容外,某些指令还可以指 明下一个辅助寄存器或下一个AR。当这条指令执行完 成后,这个寄存器就成为当前辅助寄存器。允许用于指 定下一个辅助寄存器的指令用新的值装载ARP。当ARP 用该值装载时,以前的ARP值被装入辅助寄存器指针缓 冲器(ARB)。 例1.6说明了下一个辅助寄存器的选择和其他间接寻址的 特点。 例1.6 选择新的当前辅助寄存器。 MAR *,AR1;向ARP装入1,指令执行后使得AR1成为 当前辅助寄存器 LT *+,AR2;AR2是下一个辅助寄存器。用AR1指定的 地址内容装载TREG,AR1内容加1,指令执行后使得 AR2成为当前辅助寄存器。 MPY *;TREG乘以AR2所指定的单元内容

哈工程DSP专业课课件第三章

总是来自16-bit的暂存寄存器(TREG)

另一个输入为下列数值之一:

在乘法之前,TREG 装载了一个数据读总线

(DRDB)的数值。

来自数据读总线(DRDB)的数据存储器的值。 来自程序读总线(PRDB)的程序存储器的值。

2020/4/20

输出

乘积寄存器(PREG)

用于存储两个16-bit 输入数据相乘之后产生

2020/4/20

3.1 概述

本章讲述中央处理单元(CPU)的主要组成

CPU 的 三 个 基 本 部 分 (3.2节~3.4节)

包括:输入定标部分、乘法 部分、中央算术逻辑部分

辅助寄存器算术单元 (ARAU)(3.5节)

状态寄存器ST0和ST1 (3.5节)

2020/4/20

ARAU实现对8个辅助寄存 器的算术运算。

2020/4/20

下面介绍输入移位器的输入、输出和移位位数。

输入

输入移位器的15位到0位接收程序存储器(PRDB)或数 据存储器(DRDB)的一个16-bit输入。

数据读总线(DRDB)

该输入为一个来自数据存储器的数据。

程序读总线(PRDB)

该输入为一个指令操作时给定的常数。

输出

接收了一个16-bit数据之后,输入移位器就将该16bit数据与CALU的32-bit总线对齐:

2020/4/20

输出

CALU的输入

移位器完成移位操作,所

有32位的数据被送入CALU, 而16位的数据则被存储在数 据存储器中。

移位方式

乘积定标移位器采用4种乘 积移位方式中的一种 (参见下表)。

暂存寄存器(TREG)的4个LSB位 基于TREG的移位操作允许动态地确定数据定 标因子,以便它能更好地适应系统性能。

DSP精品课件

DSP芯片的应用

第三章 5402存储器配置

目的:通过对5402的存储器配置与管理 的学习,掌握TMS320系列存储器配置与 管理的特点

DSP芯片的应用

本章主要内容

3-1 3-2 3-3 3-4 3-5 3-6 5402内部存储器配置 5402存储空间 5402存储器空间构成与管理(本章难点) 外部程序存储空间扩展 5402片内ROM组成 5402片内DARAM组成

XPC 为扩展程序指针寄存器,地址为 001EH。XPC 影响 ( A16---A19),为页指针, PC 影响( A15---A0)为页内 指针。复位时,XPC=0000H指向零页,复位后可用软件 修改XPC。 仅有8条指令可以直接影响XPC,直接访问1M程序空间, 分别说明如下:

DSP芯片的应用

DSP芯片的应用

3-1 5402内部存储器配置

5402内部配有: ROM: 4k×16bit

F000H

DARAM:16k×16bit 0000H

FFFFH

3FFFH

DSP芯片的应用

3-2 5402存储空间(包括内部和外部可扩展的) 5402有三个独立的存储空间:程序存储空间、数 据存储空间和I/O存储空间 1、程序存储空间,1M×16bit 00000H

DSP芯片的应用

作用:外部设备接口空间 受数据地址发生器DAGEN管理 受如下引脚控制(地址线、数据线除外) IS:I/O空间选择信号 IOSTRB:I/O空间选通信号 R/W:读写信号 此外,还受 READY:外设数据准备好与慢 速 I/O 设备匹配; BIO:跳转控制输入; XF: CPU输出引线等握手控制。

块重复开始地址

块重复结束地址 状态寄存器 PC扩展寄存器 保留

第三章 5402存储器配置

目的:通过对5402的存储器配置与管理 的学习,掌握TMS320系列存储器配置与 管理的特点

DSP芯片的应用

本章主要内容

3-1 3-2 3-3 3-4 3-5 3-6 5402内部存储器配置 5402存储空间 5402存储器空间构成与管理(本章难点) 外部程序存储空间扩展 5402片内ROM组成 5402片内DARAM组成

XPC 为扩展程序指针寄存器,地址为 001EH。XPC 影响 ( A16---A19),为页指针, PC 影响( A15---A0)为页内 指针。复位时,XPC=0000H指向零页,复位后可用软件 修改XPC。 仅有8条指令可以直接影响XPC,直接访问1M程序空间, 分别说明如下:

DSP芯片的应用

DSP芯片的应用

3-1 5402内部存储器配置

5402内部配有: ROM: 4k×16bit

F000H

DARAM:16k×16bit 0000H

FFFFH

3FFFH

DSP芯片的应用

3-2 5402存储空间(包括内部和外部可扩展的) 5402有三个独立的存储空间:程序存储空间、数 据存储空间和I/O存储空间 1、程序存储空间,1M×16bit 00000H

DSP芯片的应用

作用:外部设备接口空间 受数据地址发生器DAGEN管理 受如下引脚控制(地址线、数据线除外) IS:I/O空间选择信号 IOSTRB:I/O空间选通信号 R/W:读写信号 此外,还受 READY:外设数据准备好与慢 速 I/O 设备匹配; BIO:跳转控制输入; XF: CPU输出引线等握手控制。

块重复开始地址

块重复结束地址 状态寄存器 PC扩展寄存器 保留

DSP完整课件第3章 共29页

fin

CLKOUT

PLL选择 (SCSR1.11:9)

1500pF PLFF2

退出

2)外部滤波器电路回路

3.2.1 锁相环(PLL)

PLL有2个外接滤波输入引脚:PLLF,PLLF2 PLL模块使用外部滤波电路回路来抑制信号抖动和电磁干 扰,使信号抖动和干扰影响最小。

1 1Ω 0.68μ F

PLLF

(3)当未检测到累加器溢出时,其值为0;当溢出发生时, OV位被置1。

(4)根据被测试位的结果,测试控制标志位(TC)位被置1或0。

2019

退出

3.1.4 累加器(ACC)

存放CALU中的运算结果,其存放的数据可以执行单一的移位 或循环操作。其中的高位或低位字可以进入输出定标移位器进行 移位后再存放进数据存储器。与ACC有关的状态位有: 1)进位标志位C ① 当累加器中的数据相加时,结果有进位或减法无借位时C=1; 相减时,结果有借位或或加法无进位时,C=0 。 ② 当累加器中的数据被移动1位时,累加器中的最低位或最高位 进入C。

(2)外部时钟方式

最小和最大的CLKIN频率分别为4MHz和30MHz(2407A 为40MHz)。

2019

退出

3.2.2 看门狗定时器时钟

当CPU工作于低功耗模式下,看门狗能持续计数 WDCLK引脚为看门狗电路的时钟输入端。 WDCLK的时钟来自于时钟输出引脚CLKOUT。

WDCLK=CLKOUT/512 当CPU的挂起信号有效时,WDCLK将被停止。

2019

退出

3.1.6 状态寄存器ST0和ST1

1) 状态寄存器ST0

OV:溢出标志位。当中央算术逻辑单元发生溢出时,OV=1, 直到发生复位、执行以OV(溢出)或NOV(不溢出)为条件的转 移指令、或执行LST指令时被清0。

DSP原理及应用第三章PPT课件

以DP为基准的直接寻址是由DP值确定是512页中 的哪一页,由dmad确定是该页中的哪一个单元。

SP可以指向存储器中的任意一个地址。dmad可 以指向当前页中具体的单元,从而允许访问存储器 任意基地址中的连续的128个单元

15

第15页/共157页

特点

举例

用途

可以在不改 变DP或SP的 情况下,随 机地寻址128 个存储单元 中的任何一 个单元。

EFB:循环缓冲器的有效基地址(EFB)就是用户 选定的辅助寄存器(ARx)的低N位置 0后所得到 的值。

EOB:是通过用BK的低N位代替ARx的低N位得

到。

25

第25页/共157页

26

第26页/共157页

循环缓冲器的指示index就是ARx的低N位, 步长step就是加到辅助寄存器,或从辅助寄存 器中减去的值。循环寻址的算法如下:

特点:指令中包含一个固定的16位地址,能寻 址所有数据、程序和I/O存储空间,但 运行速度慢,需要较大的存储空间。

用途:用于对速度要求较低的场合。

9

第9页/共157页

3.累加器寻址

方法

举例

特点

用累加器 中的数值 作为地址 来读写程 序存储器。

READA Smem WRITA Smem

可用来完成 程序存储器 单元的数据 与数据存储 器单元的数 据进行交换

23

第23页/共157页

1) 循环寻址

许多算法,如卷积,相关和FIR滤波等, 都需要在存储器中实现一个循环缓冲器。在 这些算法中,一个循环缓冲器就是一个包含 了最近的数据的滑动窗口。当新的数据来到 时,缓冲器就会覆盖最早的数据。

循环缓冲器实现的关键是循环寻址的实 现。‘C54x间接寻址中提供了循环寻址的方 式,以%表示。

SP可以指向存储器中的任意一个地址。dmad可 以指向当前页中具体的单元,从而允许访问存储器 任意基地址中的连续的128个单元

15

第15页/共157页

特点

举例

用途

可以在不改 变DP或SP的 情况下,随 机地寻址128 个存储单元 中的任何一 个单元。

EFB:循环缓冲器的有效基地址(EFB)就是用户 选定的辅助寄存器(ARx)的低N位置 0后所得到 的值。

EOB:是通过用BK的低N位代替ARx的低N位得

到。

25

第25页/共157页

26

第26页/共157页

循环缓冲器的指示index就是ARx的低N位, 步长step就是加到辅助寄存器,或从辅助寄存 器中减去的值。循环寻址的算法如下:

特点:指令中包含一个固定的16位地址,能寻 址所有数据、程序和I/O存储空间,但 运行速度慢,需要较大的存储空间。

用途:用于对速度要求较低的场合。

9

第9页/共157页

3.累加器寻址

方法

举例

特点

用累加器 中的数值 作为地址 来读写程 序存储器。

READA Smem WRITA Smem

可用来完成 程序存储器 单元的数据 与数据存储 器单元的数 据进行交换

23

第23页/共157页

1) 循环寻址

许多算法,如卷积,相关和FIR滤波等, 都需要在存储器中实现一个循环缓冲器。在 这些算法中,一个循环缓冲器就是一个包含 了最近的数据的滑动窗口。当新的数据来到 时,缓冲器就会覆盖最早的数据。

循环缓冲器实现的关键是循环寻址的实 现。‘C54x间接寻址中提供了循环寻址的方 式,以%表示。

《DSP系统设计及应用》第三章

5

3.2.3

TMS320F206引脚 TMS320F206引脚

6

7

8

9

10

11

3.2.4

包括: 包括:

中央处理单元(CPU)

一个16位的比例转移器、 一个16位的比例转移器、 16位的比例转移器 一个16*16位并行乘法器 16*16位并行乘法器、 一个16*16位并行乘法器、 一个32 中央算术逻辑单元、 32位 一个32位中央算术逻辑单元、 一个32 累加器以及一个条件转移器。 32位 以及一个条件转移器 一个32位累加器以及一个条件转移器。 1.状态和控制寄存器 ST0和ST1两个状态寄存器保存各种各样的条件和模式的状态 两个状态寄存器保存各种各样的条件和模式的状态, ST0和ST1两个状态寄存器保存各种各样的条件和模式的状态, 包含状态位和控制位。 包含状态位和控制位。

12

13

2.输入比例转移器 (参看结构图)

DRDB它有一个 16 位的输入连到了数据总线DRDB DRDB 它有一个16 位的输入连到了数据总线 DRDB , 它有一个 16位的输入连到了数据总线 DRDB, 一个32位输出连到了CALU 32位输出连到 据空间来的数据得到CALU的路径, CALU的路径 据空间来的数据得到CALU的路径,这部分操作不需要 时钟周期,它用来把从内存来的16位数据与32 16位数据与32位 时钟周期,它用来把从内存来的16位数据与32位CALU 对齐。这对于位逻辑运算是很有用的。 对齐。这对于位逻辑运算是很有用的。 这个比例转移器在输入数据上产生一个0 16位 这个比例转移器在输入数据上产生一个0到16位 的左移,输出的LBS LBS用 填满;MSB可以被 可以被0 的左移,输出的LBS用0填满;MSB可以被0或有符号扩 展位填满,具体由状态寄存器的ST1的SXM位的值决定。 展位填满, 具体由状态寄存器的ST1 SXM位 的值决定。 ST 转移数据由一个存在于指令的常数或TREG TREG中的一 转移数据由一个存在于指令的常数或TREG中的一 个变量来确立。 个变量来确立。在指令中的转移数允许为特定的比例 或调整操作在代码中特定的点。TREG基本转移允许比 或调整操作在代码中特定的点。TREG基本转移允许比 例因素去适应系统。 例因素去适应系统。

3.2.3

TMS320F206引脚 TMS320F206引脚

6

7

8

9

10

11

3.2.4

包括: 包括:

中央处理单元(CPU)

一个16位的比例转移器、 一个16位的比例转移器、 16位的比例转移器 一个16*16位并行乘法器 16*16位并行乘法器、 一个16*16位并行乘法器、 一个32 中央算术逻辑单元、 32位 一个32位中央算术逻辑单元、 一个32 累加器以及一个条件转移器。 32位 以及一个条件转移器 一个32位累加器以及一个条件转移器。 1.状态和控制寄存器 ST0和ST1两个状态寄存器保存各种各样的条件和模式的状态 两个状态寄存器保存各种各样的条件和模式的状态, ST0和ST1两个状态寄存器保存各种各样的条件和模式的状态, 包含状态位和控制位。 包含状态位和控制位。

12

13

2.输入比例转移器 (参看结构图)

DRDB它有一个 16 位的输入连到了数据总线DRDB DRDB 它有一个16 位的输入连到了数据总线 DRDB , 它有一个 16位的输入连到了数据总线 DRDB, 一个32位输出连到了CALU 32位输出连到 据空间来的数据得到CALU的路径, CALU的路径 据空间来的数据得到CALU的路径,这部分操作不需要 时钟周期,它用来把从内存来的16位数据与32 16位数据与32位 时钟周期,它用来把从内存来的16位数据与32位CALU 对齐。这对于位逻辑运算是很有用的。 对齐。这对于位逻辑运算是很有用的。 这个比例转移器在输入数据上产生一个0 16位 这个比例转移器在输入数据上产生一个0到16位 的左移,输出的LBS LBS用 填满;MSB可以被 可以被0 的左移,输出的LBS用0填满;MSB可以被0或有符号扩 展位填满,具体由状态寄存器的ST1的SXM位的值决定。 展位填满, 具体由状态寄存器的ST1 SXM位 的值决定。 ST 转移数据由一个存在于指令的常数或TREG TREG中的一 转移数据由一个存在于指令的常数或TREG中的一 个变量来确立。 个变量来确立。在指令中的转移数允许为特定的比例 或调整操作在代码中特定的点。TREG基本转移允许比 或调整操作在代码中特定的点。TREG基本转移允许比 例因素去适应系统。 例因素去适应系统。

DSP完整课件第3章PPT文档30页

DSP完整课件第3章

26、机遇对于有准备的头脑有特别的 亲和力 。 27、自信是人格的核心。

28、目标的坚定是性格中最必要的力 量泉源 之一, 也是成 功的利 器之一 。没有 它,天 才也会 在矛盾 无定的 迷径中 ,徒劳 无功。- -查士 德斐尔 爵士。 29、困难就是机遇。--温斯顿.丘吉 尔。 30、我奋斗,所以我快乐。--格林斯 潘。

66、节制使快乐增加并使享受加强。 ——德 谟克利 特 67、今天应做的事没有做,明天再早也 是耽误 了。——裴斯 泰洛齐 68、决定一个人的一生,以及整个命运 的,只 是一瞬 之间。 ——歌 德பைடு நூலகம்69、懒人无法享受休息之乐。——拉布 克 70、浪费时间是一桩大罪过。——卢梭

dsp3_Q

3.2周期序列的离散傅里叶级数(DFS)及性质

1.周期序列的离散傅里叶级数

若离散时间序列x(n)为周期序列,则 x(n)=x(n+rN)

其中N(正整数)为信号的周期,该周期序列记作:

~

x

(

n

)

周期序列可以用傅里叶级数(DFS)来表示,其定义公式为:

x ~(n)1N 1X ~(k)ej2 N nkID F S[X ~(k)]n0,1,..N ..,1

2 n e v e n

n

例3-3 若序列h(n)是实因果序列,其傅里叶变换的实部为

HR(ej)1cos,求序列h(n)及其傅里叶变换 H ( e j )

解:由题意知:

比较两式得: 由于h(n)是实因果序列,根据共轭对称性得:

因此 H (ej)h e(n )ejn 1 ej2 ej 2co s n

第3章 离散时间系统的频域分析——傅里叶变换

3.1 非周期序列的傅里叶变换及性质 3.2 周期序列的离散傅里叶级数(DFS)及性质 3.3 有限长序列的离散傅里叶变换(DFT) 3.4 频率抽样理论 3.5 利用DFT对连续时间信号处理时应注意的问题

3.1 非周期序列的傅里叶变换及性质

3.1.1 非周期序列傅里叶变换

5.时间反转

设 D TFT[x(n)]X(ej)

则 D TF T[x(n)]X(ej)

6.尺度变换 DTFT[anx(n)]X(1ej) a

7.频域微分

DTFT[nx(n)]jdX(ej)

d

3.1.2 非周期序列傅里叶变换的性质

8.共轭性

设 D TFT[x(n)]X(ej) 则 D TF T[x*(n)]X*(ej)

5

DSP完整课件第3章

XF:XF引脚状态位。该位决定XF引脚的状态。SETC指令可对 该位进行置位,CLRC指令可对其进行清0。

15~13

ARB X

12

0

11

X

10

1

9

1

8

1 1

7

1 1

6

1 1

5

1 1

4

XF 1

3

1 1

2 1~0

1 1 PM 00

CNF TC SXM C

CNF:片内DARAM配置位。当CNF=0时,可配置的 DARAM映射到数据存储空间;当CNF=1时,可配置的 DARAM映射到程序存储空间。可通过SETC、CLRC指令对其 进行修改。 2010 退出

2010

退出

3.1 CPU功能模块

CPU是DSP 的核心部件, 主要进行取数、 运算(加、乘、 移位等)、送数 的操作。包括: 输入定标移位 器、中央算术 逻辑单元 (CALU)和乘法 单元等。

2010

退出

3.1.1 输入定标移位器

用于完成不同数据格式之间的转换。 因为240x芯片的数据总线是16位,而中央算术逻辑单元 (CALU)是32位,必须把16位数据转换为32位,实现数据格式转 换。因此,输入定标移位器的16位输入与数据总线相连,32位 输出与CALU单元相连。 输入定标移位器作为从数据总线到CALU之间的数据传输路 径的一部分,不会额外占用CPU的时钟开销。 定标移位器对输入数据进行0-15位左移。 左移时,输出数据的最低有效位(LSB)为0,最高有效位(MSB) 根据状态寄存器ST1的符号扩展控制位SXM的值来决定是否需要 进行符号扩展。 (1)当SXM=1时,高位进行符号扩展; (2)当SXM=0时,高位填0。 移位次数由包含在指令中的常量或临时寄存器(TREG)中的值 来指定。 2010 退出

15~13

ARB X

12

0

11

X

10

1

9

1

8

1 1

7

1 1

6

1 1

5

1 1

4

XF 1

3

1 1

2 1~0

1 1 PM 00

CNF TC SXM C

CNF:片内DARAM配置位。当CNF=0时,可配置的 DARAM映射到数据存储空间;当CNF=1时,可配置的 DARAM映射到程序存储空间。可通过SETC、CLRC指令对其 进行修改。 2010 退出

2010

退出

3.1 CPU功能模块

CPU是DSP 的核心部件, 主要进行取数、 运算(加、乘、 移位等)、送数 的操作。包括: 输入定标移位 器、中央算术 逻辑单元 (CALU)和乘法 单元等。

2010

退出

3.1.1 输入定标移位器

用于完成不同数据格式之间的转换。 因为240x芯片的数据总线是16位,而中央算术逻辑单元 (CALU)是32位,必须把16位数据转换为32位,实现数据格式转 换。因此,输入定标移位器的16位输入与数据总线相连,32位 输出与CALU单元相连。 输入定标移位器作为从数据总线到CALU之间的数据传输路 径的一部分,不会额外占用CPU的时钟开销。 定标移位器对输入数据进行0-15位左移。 左移时,输出数据的最低有效位(LSB)为0,最高有效位(MSB) 根据状态寄存器ST1的符号扩展控制位SXM的值来决定是否需要 进行符号扩展。 (1)当SXM=1时,高位进行符号扩展; (2)当SXM=0时,高位填0。 移位次数由包含在指令中的常量或临时寄存器(TREG)中的值 来指定。 2010 退出

精品课件-DSP处理器原理与应用(鲍安平)-第3章

10

(6) DSP开发系统。DSP开发系统是由厂家提供的一个包 含DSP、存储器、常用接口电路的通用电路板和相应软件的软 /硬件系统。通常有两种形式,一种是电路板卡的形式,插入 计算机中;另一种是通过计算机控制端口(如:串口、并口或 者USB接口)连接到计算机,通过计算机的控制端口来控制DSP 的运行。DSP厂家或者其他的第三方公司提供DSK(DSP starter Kit)入门套件和EVM(Evaluation Module)评估模块 等来帮助初学者熟悉DSP处理器的应用。同时,DSK和EVM也可 以作为程序的初步运行对象,以方便调试。

7

为了克服C编译器低效率,在提供标准C库函数的同时,开发 系统也提供了许多针对DSP运算的高效库函数,例如FFT、FIR 、IIR、相关、矩阵运算等,它们一般采用汇编语言来编写, 带有高级语言调用/返回接口。

为了得到高效编程,在系统软件开发中,关键的DSP运算 程序一般都是自行手工用汇编语言编写的,按照规定的接口 约定,由C程序进行调用,这样极大地提高了编程效率。

2

3.1 DSP处理器软、硬件开发工具简介

虽然不同DSP芯片厂家提供了多种不同的开发调试工具, 但它们的功能大体相似。图3-1为DSP处理器软件开发流程图 。

3

ห้องสมุดไป่ตู้

图3-1 DSP处理器软件开发流程图

4

从图3-1中可以看出,DSP软件开发可以分为5个步骤,首 先要根据所设计的硬件情况编写出结构文件;然后用C或者汇 编语言编写源程序,源程序经过C编译器和汇编器后与结构文 件以及库文件在链接器中链接成可执行代码,如果是汇编语 言编写的程序则可以跳过C编译器;可执行代码可以在软件模 拟器模拟运行或者通过硬件仿真器在标准的开发板或者评估 板上运行调试;当软件运行达到要求后,再在用户自己制作 的目标板上调试;调试成功后将可执行代码制作成EPROM码, 目标板脱机运行,完成系统的测试和调试。

(6) DSP开发系统。DSP开发系统是由厂家提供的一个包 含DSP、存储器、常用接口电路的通用电路板和相应软件的软 /硬件系统。通常有两种形式,一种是电路板卡的形式,插入 计算机中;另一种是通过计算机控制端口(如:串口、并口或 者USB接口)连接到计算机,通过计算机的控制端口来控制DSP 的运行。DSP厂家或者其他的第三方公司提供DSK(DSP starter Kit)入门套件和EVM(Evaluation Module)评估模块 等来帮助初学者熟悉DSP处理器的应用。同时,DSK和EVM也可 以作为程序的初步运行对象,以方便调试。

7

为了克服C编译器低效率,在提供标准C库函数的同时,开发 系统也提供了许多针对DSP运算的高效库函数,例如FFT、FIR 、IIR、相关、矩阵运算等,它们一般采用汇编语言来编写, 带有高级语言调用/返回接口。

为了得到高效编程,在系统软件开发中,关键的DSP运算 程序一般都是自行手工用汇编语言编写的,按照规定的接口 约定,由C程序进行调用,这样极大地提高了编程效率。

2

3.1 DSP处理器软、硬件开发工具简介

虽然不同DSP芯片厂家提供了多种不同的开发调试工具, 但它们的功能大体相似。图3-1为DSP处理器软件开发流程图 。

3

ห้องสมุดไป่ตู้

图3-1 DSP处理器软件开发流程图

4

从图3-1中可以看出,DSP软件开发可以分为5个步骤,首 先要根据所设计的硬件情况编写出结构文件;然后用C或者汇 编语言编写源程序,源程序经过C编译器和汇编器后与结构文 件以及库文件在链接器中链接成可执行代码,如果是汇编语 言编写的程序则可以跳过C编译器;可执行代码可以在软件模 拟器模拟运行或者通过硬件仿真器在标准的开发板或者评估 板上运行调试;当软件运行达到要求后,再在用户自己制作 的目标板上调试;调试成功后将可执行代码制作成EPROM码, 目标板脱机运行,完成系统的测试和调试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)当未检测到累加器溢出时,其值为0;当溢出发生时, OV位被置1。

(4)根据被测试位的结果,测试控制标志位(TC)位被置1或0。

2010

退出

3.1.4 累加器(ACC)

存放CALU中的运算结果,其存放的数据可以执行单一的移位 或循环操作。其中的高位或低位字可以进入输出定标移位器进行 移位后再存放进数据存储器。与ACC有关的状态位有: 1)进位标志位C ① 当累加器中的数据相加时,结果有进位或减法无借位时C=1; 相减时,结果有借位或或加法无进位时,C=0 。 ② 当累加器中的数据被移动1位时,累加器中的最低位或最高位 进入C。

TC:测试/控制标志位。在下列情况下TC位被置1:由BIT或

BITT测试的某位为1时;用NORM指令对累加器最高的两位进

行异或结果为真时;用CMPR指令对当前ARn与AR0比较条件

成立时。编程时,根据TC位的状态可进行程序的条件跳转、调

用和返回。

2010

退出

3.1.6 状态寄存器ST0和ST1

2) 状态寄存器ST1 C:进位位。加法结果产生进位时置1,减法结果产生借位时 被清0。执行带16位移位的ADD指令时,若产生进位时置1, 否则不影响该位;在执行16位移位的SUB指令,若产生借位 时置0,否则不影响该位。

2)溢出方式控制位OVM

OVM决定ACC运算结果发生溢出时,是否进行溢出处理。

① 若OVM=1,当运算结果发生溢出时,ACC结果被设定为确定

值:

若正向溢出,ACC=7FFF FFFFH(最大正数);

若负向溢出,ACC=8000 0000H(最小负数)。

② 若OVM=0,ACC溢出为0.

2010

退出

3.1.4 累加器(ACC)

8LSBs

主要功能:

在CALU操作的同 时执行8个辅助寄存 器(AR0~AR7)中的 算术运算。

提供了灵活而有 效的间接寻址功能,

使用任何一个辅助寄

存器提供的16位地

址,就可以访问64K

数据写总线

字的数据空间。

数据读地址总线

数据写地址总线

退出

3.1.7 辅助寄存器算术单元(ARAU)

辅助寄存器ARx通常用作地址间接指针,其中存放的数据即为 数据存储器地址。

注意:累加器中的数据不变

2010

退出

3.1.6 状态寄存器ST0和ST1

状态寄存器ST0和ST1,含有各种状态和控制位。状态寄存器 的内容可以被保存到数据寄存器,也可从数据寄存器中进行加 载。

1) 状态寄存器ST0

ARP:辅助寄存器指针。利用MAR、LST指令可以修改状态 寄存器ST0中的辅助寄存器指针(ARP)。在间接寻址时用于选 择当前辅助寄存器。在ARP被装载时,原先的ARP值被复制 到ARB中。

CNF:片内DARAM配置位。当CNF=0时,可配置的

DARAM映射到数据存储空间;当CNF=1时,可配置的

DARAM映射到程序存储空间。可通过SETC、CLRC指令对其

进行修改。

2010

退出

2) 状态寄存器ST1

3.1.6 状态寄存器ST0和ST1

SXM:符号扩展方式位。SXM决定是否进行符号扩展。当 SXM=0时,禁止符号扩展;当SXM=1时,数据被CALU使用 之前进行符号扩展。执行ADDS和SUBS指令时禁止符号扩展。 通过SETC、CLRC指令可对其置位或复位。

退出

退出

退出

退出

3.1.3 中央算术逻辑单元

由32位的中央算术逻辑单元(CALU)、32位的累加器(ACC) 以及32位的输出移位器组成。

2010

退出

注意几个问题:

3.1.3 中央算术逻辑单元

(1)当加到累加器或从累加器减或将累加器数值移1位或循环 移1位时将影响进位标志位C。

(2)溢出方式位(OVM)决定累加器如何处理算术运算的溢出, 当OVM=1且有溢出发生时,累加器自动填充最大值或最小 值;当OVM=0时,累加器中的结果正常溢出。

2010

退出

3.1.6 状态寄存器ST0和ST1

1) 状态寄存器ST0

OV:溢出标志位。当中央算术逻辑单元发生溢出时,OV=1, 直到发生复位、执行以OV(溢出)或NOV(不溢出)为条件的转 移指令、或执行LST指令时被清0。

OVM:溢出方式位。OVM决定CALU发生溢出时的处理方式。 当OVM=0时,累加器中结果正常溢出;当OVM=1时,根据 溢出的情况,累加器被设置成它的最大正值(7FFFFFFFh)或负 值(80000000h)。SETC、CLRC、LST指令均可修改OVM。

3)溢出标志位OV 当累加器发生溢出时,OV=1,反之为0。

4)测试/控制标志位TC 根据被测试位的值置1,或清0。 与累加器有关的转移指令主要取决于以上标志位状态,及累加

器的值。

3.1.5 输出数据定标移位器

根据相应的存储指令中指定的位数,将累加器输出的内容左移 0~7位,然后将移位器的高16位或低16位存储到数据RAM中。

2010

退出

2) 状态寄存器ST1

3.1.6 状态寄存器ST0和ST1

ARB:辅助寄存器的缓冲器指针。当ARP被装载时,ARP原 来的值就被复制到ARB中;当用LST指令装载ARB时,同样的 值也被复制到ARP中。

XF:XF引脚状态位。该位决定XF引脚的状态。SETC指令可对 该位进行置位,CLRC指令可对其进行清0。

2010

退出

1) 状态寄存器ST0

3.1.6 状态寄存器ST0和ST1

INTM:全局中断屏蔽控制位。全局屏蔽或使能所有的可屏蔽 中断。INTM=0时,使能所有可屏蔽的中断;INTM=1时, 禁止所有的可屏蔽中断。复位或可屏蔽中断发生时(TRAP指 令除外),INTM置1,禁止中断。

DP:数据存储器页指针。9位的DP指针和指令字中的低7位 连接在一起,形成直接寻址中的16位数据存储单元地址。可 通过LST、LDP指令对其修改。

8个辅助寄存器中,由状态寄存器ST0中的辅助寄存器指针 (ARP)指定的ARn为当前ARn。

PM:乘积移位方式位。SPM、LST指令可以修改1.7 辅助寄存器算术单元(ARAU)

16 AR7

16 AR6 16 AR5

16 AR4 16 AR3

16 AR2 16 AR1

16 AR0

16

MUX

ARUX

16

16

16

2010

ARB

数据读总线

3 ARP

3 MUX

3

3LSBs 指令寄存器