基于MicroBlaze的FPGA重配置系统设计

FPGA与mircobalze交互数据

六、添加网表文件

目录在软核所在目录的下implementation文件夹下。cpu.ngc(cpu是软核的名字,在新建时设定的)

七、添加BMM文件

目录在软核所在目录的下implementation文件夹下。cpu.bmm。

添加进来后入下图所示

注意:需要修改每一行的目录,如上图所示原来没有U3_CPU。C3_CPU是实例化软核的名称

还需要修改Implement Design目录,右键单击选择Process Propreties如下图所示

八、添加SDK生成的文件

右键点cpu添加,添加目录为SDK的目录。添加时按下图选择

九、添加ISE代码

源代码见附录1

十、软核C源代码

见附录2

十一、SDK端下载

第一个为bit流文件,第二个为EDK文件,第三个为软核代码文件

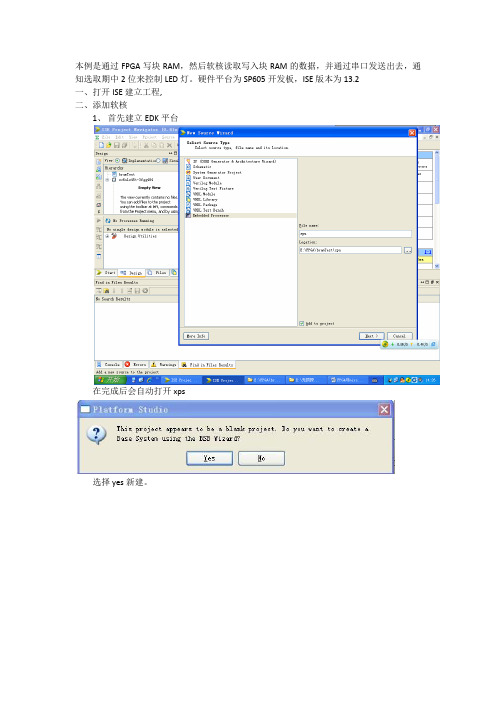

本例是通过FPGA写块RAM,然后软核读取写入块RAM的数据,并通过串口发送出去,通知选取期中2位来控制LED灯。硬件平台为SP605开发板,ISE版本为13.2

一、打开ISE建立工程,

二、添加软核

1、首先建立EDK平台

在完成后会自动打开xps

选择yes新建。

选择PLB(以PLB为例)总线,点OK。

//#include "xil_testcache.c"

XGpiomyled;

intmain()

{

intstatus=0;

Xuint32i=0;

Xuint16rst=0;

//print("Hello World\n\r");

//char x[]="Initial TheMicroblaze";

基于MicroBlaze处理器的BPIFlash操作_李斌

Electronic technology •电子技术Electronic Technology & Software Engineering 电子技术与软件工程• 115基于MicroBlaze 处理器的BPI Flash 操作文/李斌更新加载Flash 中的内容,并完成自身配置数据的重加载,该过程就是FPGA 的可重构能力。

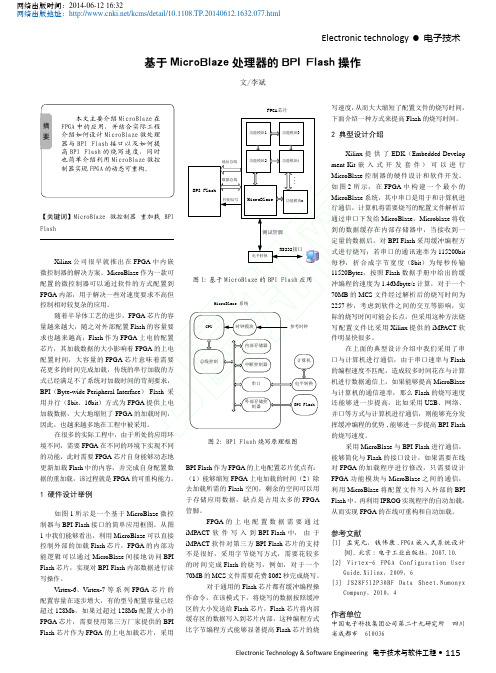

1 硬件设计举例如图1所示是一个基于MicroBlaze 微控制器与BPI Flash 接口的简单应用框图。

从图1中我们能够看出,利用MicroBlaze 可以直接控制外部的加载Flash 芯片,FPGA 的内部功能逻辑可以通过MicroBlaze 间接地访问BPI Flash 芯片,实现对BPI Flash 内部数据进行读写操作。

Virtex-6、Virtex-7等系列FPGA 芯片的配置容量在逐步增大,有的型号配置容量已经超过128Mb ,如果过超过128Mb 配置大小的FPGA 芯片,需要使用第三方厂家提供的BPI Flash 芯片作为FPGA 的上电加载芯片,采用BPI Flash 作为FPGA 的上电配置芯片优点有:(1)能够缩短FPGA 上电加载的时间(2)除去加载所需的Flash 空间,剩余的空间可以用于存储应用数据,缺点是占用太多的FPGA 管脚。

FPGA 的上电配置数据需要通过iMPACT 软件写入到BPI Flash 中,由于iMPACT 软件对第三方BPI Flash 芯片的支持不是很好,采用字节烧写方式,需要花较多的时间完成Flash 的烧写,例如,对于一个70MB 的MCS 文件需要花费8062秒完成烧写。

对于通用的Flash 芯片都有缓冲编程操作命令,在该模式下,将烧写的数据按照缓冲区的大小发送给Flash 芯片,Flash 芯片将内部缓存区的数据写入到芯片内部,这种编程方式比字节编程方式能够显著提高Flash 芯片的烧Flash 的烧写时间。

基于MicroBlaze的可重构嵌入式系统设计

基于MicroBlaze的可重构嵌入式系统设计摘要:基于MicroBlaze软核设计了一个可重构嵌入式系统,可完成基于嵌入式Web服务器的远程监控。

介绍了Xilinx微处理器软核MicroBlaze的定制、硬件平台的搭建及uCLinux操作系统的剪裁,最后给出了实现远程监控的程序流程图。

关键词:可重构MicroBlaze软核;嵌入式系统;XilinxFPGA中图分类号:TP39 文献标识码:A 文章编号:1007-9599 (2010) 05-0000-02Design of Embedded Refactoring System Based on MicroBlazeTang Pei,Huang Peng(Yangtze University,School of Computer Science,Jingzhou 434023,China) Abstract:A Refactoring embedded system based on the MicroBlaze soft-core can be used to complete the remote monitoring based on embedded Web server.In this thesis ,We'll introduce some information of Xilinx MicroBlaze soft-core microprocessor and the way of customizing the hardware platform and How to cut the operati ng system uCLinux.At last,We'll give the remote monitoring program flow chart.Keywords:Refactoring MicroBlaze soft-core;Embedded systems;XilinxFPGA可重构技术是目前计算机系统研究中的一个新热点,是指依靠软件编程来改变系统的硬件结构,以适应不同应用的一种技术,也称为自适应计算平台。

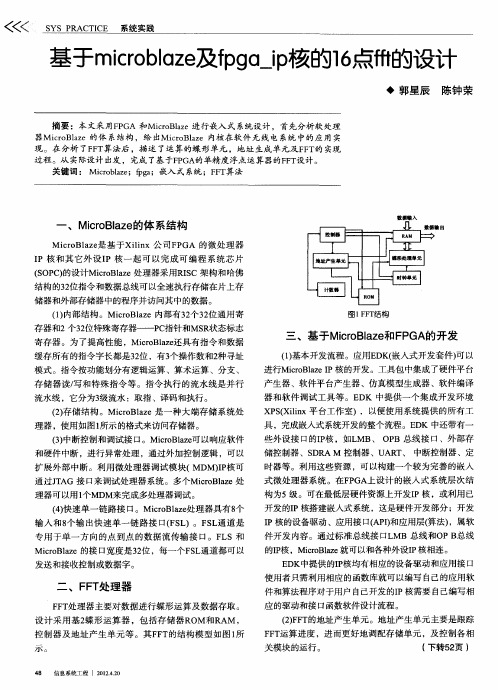

基于microblaze及fpga_ip核的16点fft的设计

模式 。指令按功能划分有逻辑运算 、算术运算 、分支 、

存储器读/ 写和特殊指令 等 。指令执行 的流水线是并行

流水线 ,它分为3 级流水 :取指 、译码和执行。

() 2存储结 构。Mi o lz 一种大端存储系统处 c B ae是 r 理器 ,使用如图l 所示 的格式来访问存储器 。

() 3 中断控制和调试接 口。Mi o l e 以响应软件 c Ba 可 r z

和硬件 中断 ,进行异常处理 ,通过外加控制逻辑 ,可以 扩展外部 中断。利 用微处理器调试模块f M) 核可 MD I P

通过JA 接 口来调试处理器 系统 。多个 Mi o l e TG c B a 处 r z 理器可以用 U ̄ M来完成多处理器调试 。 JMD

< - SS R CI 系 实 < . : Y A T E 统 践 < P C

基 于 mio l e p a i核的1点fB 设计 c b z 及fg p r a f ̄ 6 tJ

—

◆ 郭星辰

陈钟 荣

摘要 :本文采 用F G 和Mi o l e进行嵌入式 系统设计 ,首先分析软 处理 P A c Ba r z 器MirB ae的体 系结构 ,给 出Mi o l e内核在软件 无线 电系统 中的应 用实 co l z c Ba r z 现 。在分析 了F T F 算法后 ,描 述 了运算的蝶 形单元 ,地址 生成单元及F T 实现 F的 过程。从 实际设 计 出发 ,完成 了基 于F G P A的单精度浮点运算器的F T . F  ̄ 计。 关键词 :Mi o l e pa c ba ;fg;嵌入式 系统 ;F T r z F 算法

<< , <

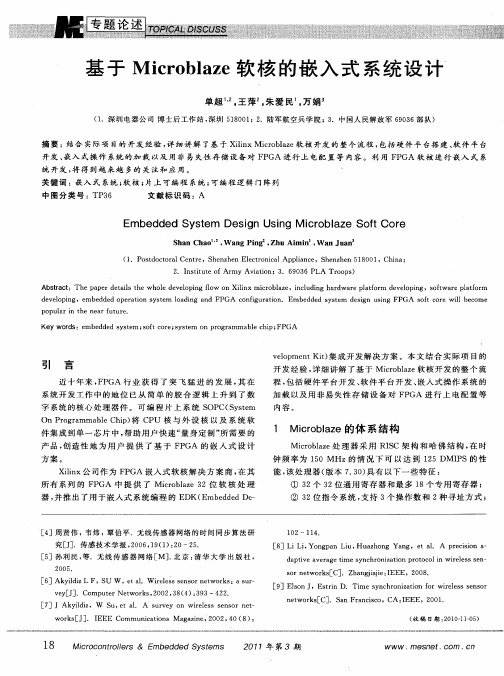

基于Microblaze软核的嵌入式系统设计

内容 。

On P o rmma l C i) C U 核 与 外 设 核 以及 系 统 软 rg a be hp 将 P 件 集 成 到 单 一 芯 片 中 , 助 用 户 快 速 “ 身 定 制 ” 需 要 的 帮 量 所 产 品 , 造 性 地 为 用 户 提 供 了 基 于 F GA 的 嵌 入 式 设 计 创 P 方案 。 Xin l x公 司作 为 F GA 嵌 入 式 软 核 解 决 方 案 商 , 其 i P 在

[ ]周 贤 伟 , 炜 , 伯 平 .无 线 传 感 器 网络 的时 间 同 步算 法 研 4 韦 覃

究 [] J.传 感 技 术学 报 ,0 6 1 () 2 2 . 2 0 ,9 1 :0— 5

[ ]孙 利 民 , .无 线 传 感 器 网 络 [ . 京 : 华 大 学 出 版 社 , 5 等 M] 北 清

所 有 系 列 的 F GA 中 提 供 了 Mi o lz 2位 软 核 处 理 P e bae 3 r

1 Mirba e的体 系结 构 co lz

Mir bae处 理 器 采 用 RI C架 构 和 哈 佛 结 构 , 时 co lz S 在 钟 频 率 为 1 0 MHz的 情 况 下 可 以 达 到 1 5 DMI S的 性 5 2 P

2 n t u e o my Av a in;3 9 3 LA o p ) .I s i t fAr ito t .6 0 6 P Tr o s

Ab ta t s r c :The pa e t i he who ede eop n lw l ir blz p rde al t s l v l i g fo on Xii m c o a e,i ldi r nx ncu ng ha dwa epltor e e o ng,s fw a e p a f m r a f m d v l pi o t r l tor d v l i g,e b dd d op r to s s e la ng an e eop n m e e e a in y t m o di d FPGA onfg a i c i ur ton. Em be de y t m sgn usng FPGA of o e wilbe o e d d s s e de i i s tc r l cm

MicroBlaze串口设计

MicroBlaze串口设计设计原理本系统中,Basys3的MicroBlaze模块调用基于AXI协议的(UART)IP核,通过AXI总线实现MicroBlaze-UART之间的(通信),完成串口打印。

操作步骤一、基于GUI界面创建工程1.创建新的工程项目1)双击桌面图标打开Viv(ad)o 2023.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2023.2>Vivado 2023.2;2)点击‘Create Project’,或者单击File>New Project创建工程文件;3)将新的工程项目命名为‘lab6’,选择工程保存路径,勾选‘Create project (sub)directory’,创建一个新的工程文件夹,点击Next继续;4)选择新建一个RTL工程,由于本工程无需创建源文件,故将Do not specify sources at this (ti)me(不指定添加源文件)勾选上。

点击Next继续;5)选择目标(FPGA)器件:xc7a35tcpg236-1或Basys3;6)最后在新工程总结中,检查工程创建是否有误。

没有问题,则点击Finish,完成新工程的创建。

2. 创建原理图,添加IP,进行原理图设计。

1)在Project Navigat(or)下,展开IP INTEGRATOR,选择‘Create Block Design’创建新的原理图设计;2)将新的设计命名为‘MB_UART’;3)添加一个clock IP,在原理图(Diag(ram))界面中鼠标右击,选择‘Add IP’。

在IP搜索框中输入‘clocking’,双击添加Clocking Wizard;4)双击Clocking Wizard模块进行自定义配置,选择Output Clocks 一栏,确定clk_out1频率为100(MHz),Reset Type为(Ac)tive High;5)鼠标右击‘clk_in1’,选择Make Ex(te)rnal添加引脚;6)完成后,如下图所示:7)同样的,在Diagram中添加MicroBlaze IP;8)添加完成后如下图所示,点击‘Run Block Automation’;9)在弹出窗口中,使用以下设置替换默认设置;Local Memory: 128KBLocal Memory ECC: NoneCache Configuration: NoneDebug Module: Debug OnlyPeripheral AXI Port:EnabledInterrupt Controller: 不勾选Clock Connection: /clk_wiz0/clk_out1(100 MHZ)10)完成之后,Vivado会基于之前的设置自动生成一些额外的IP,并且会自动连接完毕,此时不要点击‘Run Connection Automation’;11)在Diagram中添加AXI Uartlite IP,在搜索框输入‘uart’,选择相应的IP;12)鼠标右击Clocking Wizard的‘reset’,选择Make External添加引脚;13)使用连线工具将Processor System Reset的‘ext_reset_in’与‘reset’相连接。

MicroBlaze的那些事儿1:MicroBlaze的体系架构

MicroBlaze的那些事儿1:MicroBlaze的体系架构前言:Nios II很多人都知道,是Altera的32位软核,但MicroBlaze知道的人不多,是对头公司Xilinx与Nios II大擂台的产品。

“blaze”是火焰的意思,可惜MicroBlaze不如它的名字一样,引起太大的关注。

一方面是Xilinx的推广不力,另一方面是资料太少。

也看过MicroBlaze和Nios II比较的文章,最后总是说其实两者难分伯仲,其实主要还是看你FPGA用哪家公司的,唉,我算倒霉,自学的是用Xilinx的芯片,也只好投入MicroBlaze的怀抱,下面就讲讲MicroBlaze的那些事儿Xilinx公司其实有三个核:Picobalze 8位软核(真的很难用,没有C编译器,编程用汇编,资料超少,具体见之前我blog文章)MicroBlaze 32位软核(下面文章的主角)PowerPC 32位硬核,只存在于Xilinx高端系列芯片上(Virtex-4和Virtex-5)。

当你见到人家叫PPC时候,千万不要以为是智能手机,其实PowerPC也简称PPC。

MicroBlaze的体系结构MicroBlaze V7.0核心框图要注意MicroBlaze核心框图,MicroBlaze V7.0已经有MMU了,意味着MicroBlaze可以运行依赖MMU的操作系统,像Linux、WindowCE等。

EDK6.2的MicroBlaze核心框图MicroBlaze的版本号是同EDK的版本号相联系的,我用的EDK 9.2i MicroBlaze版本是v7.0。

而从上面框图可以看到EDK6.2的MicroBlaze是没有MMU的,因此也不能运行Linux,只能运行ucLinux。

目前最新版本是MicroBlaze v7.20。

要使用相关应用,先更新一下EDK的版本(软件安装文件越来越大 )。

不同版本MicroBlaze的性能还要注意MicroBlaze支持的器件系列,当然首先是Xilinx的FPGA器件(这不废话!其实我也不知道NIOS II 能不能移植到Xilinx FPGA上来)Spartan-3E / Spartan-II / Spartan-3 / Spartan-IIE / Virtex-4 FX /Virtex-4 LX / Virtex-4 SX / Virtex-5 FX / Virtex-5 LX / Virtex-5 SX /Virtex-E / Virtex-II / Virtex-II Pro如果你手上只是CoolRunner-II的CPLD,我建议你尝试一下用Picobalze作控制。

基于MicroBlaze的多FPGA及DSP远程更新系统设计

FLASH 中的程序,完成了 DSP 的远程更新。

为关闭状态,则继续向下读取数据,这样就把 golden

程更新主要是更新 golden bitstream area 中的配置文

件,步骤如下:

到 I/O 口 的 默 认 电 平 为 全 高 ,从 而 运 行 DSP 内 部

3 远程更新系统设计

1)擦除关键开关字的块或者扇区,使关键开关

Abstract: In the case of limited equipment environment and equipment status,it is risky and inflexible

to update FPGA and DSP programs by JTAG. The FPGA and DSP remote update system based on

件也包含有远程更新的功能,这样就保证了可以重

新 利 用 上 位 机 下 发 更 新 配 置 文 件 写 入 到 FLASH 的

2 远程更新方法

update bitstream area 区域,完成程序的更新,这样的

2.1

2.2

FPGA 远程更新方法

FPGA 的 远 程 更 新 功 能 采 用 了 QuickBoot 的 方

图 2 所示,FPGA 中使用了 MicroBlaze 软核,软核中用

4)验证写入的文件是否正确;

的 基 础 上 减 少 了 对 资 源 的 占 用 。 对 于 FPGA 的 更

area 区域中;

5)验证通过后,将关键开关字打开。

通过 Xilinx 提供的 TCL 指令和脚本文件,利用要

加载的含有远程更新功能的 bit 文件生成两个文件:

一种基于microblaze提高控制系统通信可靠性方法

Vol.28

第4期

No.4

2020 年 2 月

Feb. 2020

电子设计工程

Electronic Design Engineering

一种基于 Microblaze 提高控制系统通信可靠性方法

张柯

(中国西南电子技术研究所 四川 成都 610036)

摘要:基于旧有二次航管系统综合控制 DSP+FPGA 的硬件体系结构,为系统功能升级提出一种

system control method based on Micorblaze multi⁃core structure

ZHANG Ke

(Southwest China Institute of Electronic Technology,Chendu 610036,China)

Abstract: Based on the hardware architecture of the integrated control DSP&FPGA of the old

DSP+FPGA 软核的双核共同控制方法,利用本方法在不更改硬件设备的基础下,可以提高综合控制

设备通信可靠性,降低通信繁忙带来的通信异常,降低通信阻断率,减少系统虚警。通过对 FPGA

内建 Microblaze 软核,采用 DSP 和 FPGA 软核分责工作的设计,分别和不同的设备系统串口接口通

信,实现多串口互不干扰。使用该方法后,系统通信效果良好,通信干扰概率下降了约 7.3 倍。该

储在记录仪中。各设备之间的相互通信都遵循相同

设备的时间信息,并把时间信息和航管询问结果存

的命令、消息处理流程,具有握手、超时、重传机制,

储在存储记录设备内。每过 30 分钟,综合控制设备

基于MicroBlaze的可编程SOC硬件系统的构建

基于MicroBlaze的可编程SOC硬件系统的构建创建嵌入式处理器系统首先要创建一个硬件平台,这个平台包含一个或多个处理器、总线、以及外设。

下面的内容介绍如何以科大嵌联的数字刀剑系列之火龙刀Spartan3 开发板第三代为目标板,基于BSB(Base System Builder)模式建立一个以MicroBlaze处理器为核心的硬件系统。

整个内容我们以实验流程的形式给出,并包含如下三个部分:建立一个简单的硬件系统,向硬件系统添加IP,添加用户自定义IP。

整个实验所建立的硬件平台如图x.1所示。

图x.1其中,第一部分根据BSB模式建立了一个包含了UART IP的简单硬件系统,第二部分在第一部分的基础上添加了EDK自带的GPIO的IP CORE和定时计数器的IP。

第三部分在以上两部分的基础上利用Creat/Import custom IP工具创建并添加了七段数码管的控制IP。

一、创建一个简单的硬件系统在这部分内容中,我们使用XPS系统的BSB自动创建一个处理器系统,它由以下处理器IP 组成:∙MicroBlaze∙LMB BRAM controllers for BRAM∙BRAM∙OPB bus∙OPB MDM∙OPB UART包含以下步骤:1. 建立一个新的XPS工程3. 选择并配置处理器4. 配置接口5. 软件设置6. 察看硬件系统1. 建立一个新的XPS工程启动Xilinx Platform Studio (XPS) ,使用BSB建立一个工程文件,文件名和路径为d:\lab\lab1选择MicroBlaze 作为处理器,设置处理器时钟频率为50 MHz (Spartan-3板包含一个50 MHz的晶振),设置总线时钟频率为50 MHz,并且设置片上读/写调试模块(On-chip H/W debug module)为调试接口。

(1)选择Start → Programs → Xilinx Platform Studio 7.1i → Xilinx Platform Studio打开XPS (2)选择File → New Project → Base System Builder,如图1-2图1-2. 基于BSB模式这样将会打开使用BSB创建新工程的向导(Create New Project Using Base System Builder Wizard)对话框。

基于Virtex-6的microblaze开发实例流程

EDK实用实例目的:本实例是通过GPIO将8个LED等点亮。

实验环境:软件:Xilinx ISE Design Suit 13.3板卡: Virtex-6 开发板实验内容:在ISE工程中添加MircroBlaze软核,并在SDK中编写软件程序,驱动外部的8个LED灯。

实验步骤:第一步:ISE中创建工程。

1、打开ISE,点击New Project。

2、选择工程路径,为工程命名3、选择工程属性和器件参数此处注意,如果是使用其他的板卡,或者自己设计的板卡,需要选择相应的器件参数。

第二步:添加microblaze软核。

1、添加Embedded Processor。

2、添加完软核之后,双击生成的软核,系统会自动调用xps工具。

3、当xps打开的时候会弹出下面的界面,点击yes即可。

4、然后出现下面界面,按照图示进行选择。

5、点击OK,将出现下面的界面,此页面可以设置刷新时钟频率、复位时钟的边缘、以及选择单核处理器还是多核处理器。

设置好之后点击next。

的是LED实验,所以需要添加GPIO。

7、具体设置如下:点击ADD Device出现下面的界面,按照图示进行选择。

8、点击OK,生成的系统如下图示:9、因为系统默认的GPIO端口都为双向的端口,所以我们需要对端口做一些修改,选中Ports,点击Generic_GPIO中的Connected Port端口然后选择Disconnect from External Ports。

可以看到External Ports中的Generic_GPIO端口也已经没有了。

然后重新选择Generic_GPIO下面的GPIO_IO_O,选择External Ports。

可以看到在External Ports中的Generic_GPIO端口重新出现了,并且是GPIO_IO_O。

这样就将Generic_GPIO口从原来的双向端口更改成了输出端口。

注意:virtex-6的板子上面没有差分时钟,而我们生成的时钟是差分的,这里需要修改,修改方法跟上面修改GPIO的方式差不多。

基于MicroBlaze的FPGA重配置系统设计

第 7卷

第2 3期

20 0 7年 1 2月

科

学

技

术

与

工

程

V0 . No. 3 17 2

De c.20 7 0

1 71 1 1 2 0 2 — 9 — 3 6 — 8 9( 0 7) 3 610 0

S in e T c n l g n n i e r g c e c e h oo y a d E g n e i n

1 Xin P l xF GA配置方式及配置流程 i

实现 F G 的 数 据 配 置 方 式 比较 多 , X l x PA 以 in i 公 司的 Vr x ie - t 4系列 F G P A为 例 , 要 有 从 串模 式 、 主 主 串模 式 、 从 并 模 式 、2位 从并 模 式 、 并 模 式 8位 3 主 及 JA T G模 式 这 六 种 配 置 方 式 。这 些 模 式 是 通 过

第一作者简介: 李

炜 ( 9 3 ) 男 , 都 电 子 科 技 大 学 自动 化 I8 , 成

工 程 学 院研 究生 , 究 方 向 : 丁 F G 的 嵌 入 式 系 统 开 发 。E. 研 基 PA

⑥

20 Si eh E gg 0 7 c.T c . n n.

基 于 Mi o l e F G c Ba 的 P A重 配 置 系统 设 计 r z

李 炜 J l

( 电子 科 技 大学 自动 化 工程 学 院 , 都 6 0 5 成 104)

摘

要

介绍 了X l xF G in P A的配置模 式和配置 原理 , 出一种 基于 Mi o lz 核处 理器 的 F G 重配置 系统设 计 方案 i 提 c Bae软 r PA

基于MicroBlaze处理器的BPI Flash操作

Xi l i n x公 司 很 早 就 推 出 在 F P GA 中 内 嵌

每 秒 ,折 合 成 字 节 宽 度 ( 8 b i t )为 每 秒 传 输 图1 : 基 于 Mi c r o B l a z e的 B P I F l a s h应 用 1 1 5 2 0 B y t e s ,按照 F l a s h数据 手册 中给 出 的缓 冲编 程 的速度为 1 . 4 6 Mb y t e / s计算 ,对 于一 个 7 0 MB的 MC S文件经 过解 析后 的烧 写时 间为

2 2 5 7秒 ,考虑 到软件 之 间的 交互等 影响 ,实 际的烧 写时 间可能会长 点,但采用这种 方法烧 写 配置 文 件 比采 用 Xi l i n x提供 的 i MP AC T软

件明显快很多 。

量越 来越大 ,随之对 外部配置 F l a s h 的容量 要

求 也越 来越 高;F l a s h作 为 F P GA上 电的配 置 芯片 ,其加 载数据 的大小影响着 F P G A 的上电 配置 时 间 ,大 容量 的 F P G A 芯片 意 味着 需 要 花更 多的时间完 成加载 ,传统 的串行加载 的方 式 已经满足 不了系统对加载时 间的苛刻要求 ,

【 关键词 】M i c r o B l a z e 微控制器 重加载 B P I

F l as h

通过 串 口下 发给 Mi c r o B l a z e ,Mi c r o b l a z e将收 到 的数据 缓存 在 内部存储 器 中, 当接 收 到一 定量 的数 据后 ,对 BP I F l a s h采用 缓冲编 程方 式进 行烧 写;若 串 口的通讯 速率 为 1 1 5 2 0 0 b i t

基于MicroBlaze的可重构嵌入式系统设计

ir Ba e PA 可重构技 术是 目前计 算机 系统研 究 中的一个 新热 点 ,是 指依 外部 电路 ,因此利 用 M co lz 微处 理器作 为 F G 在线 重配置 靠软件 编程来 改变系 统的硬 件结 构, 以适应 不 同应用 的一种技 术 , 系统 的控制 器是较 好 的选择 。 也称 为 自适应 计算平 台。作为 一种新 的体 系结构 ,可重 构技 术可 麟 依据 不同 的应 用 ,将 同一 个器件 重新 定制 , 以完 成不 同的任 务 , 审 嵩 从 而达到 降低开 发成本 、加 快开发 进度 的 目的 。 文基于 x n 本 iix l 蒜 I. ..._j .. . . ... . ... 蘸

Absr c : Rea trnge t a tA fco i mbe e y tm a e I te Mi r Blz otc r a b s o c dd d s se b s O1 h c o a e s f— o ec n u e t omp eeter m o m o io ig d e d lt e m n trn h b s n e e d d W e ev r1 h ste i, e1 i to uc o n o m ai n o ln M ir Blz otc r ir r c so n a e o mb d e b sr e . ti ssW ’ nr d e s me if r to fXiix c o a e s f-o em cop o e s ra d d n h 1 h wa o u tmii g t e ad ae paf r n d w o utte o r tn yse uCLi u . a tW e lgie te r m0 e te y f c so zn h r w r lto m a h Ho t c peai g s tm h n xAt ls. q v h e t

MicroBlaze处理器的PetaLinux操作系

MicroBlaze 处理器的PetaLinux 操作系

本文针对Xilinx 公司的MicroBlaze 软核,介绍了PetaLinux 嵌入式操作系统及其移植方法,研究了PetaLinux 的相关配置和启动方案。

1 基于MicroBlaze 处理器的系统设计

1.1 MicroBlaze 处理器简介

MicroBlaze 软核处理器是一种针对Xilinx FPGA 器件而优化的功能强大的微处理器。

它内部采用RISC 架构的32 位指令和数据总线,支持CoreConnect 片上总线的标准外设计集合,具有兼容性和重复利用性,且可根据性能需求和逻辑区域成本任意裁减,极大地扩展了应用范围,其最精简的

核只需要将近400 个Slice。

MicroBlaze 的CoreConnect 总线、它能够将FPGA 内各种不同的IP。

ISE13.2 Microblaze工程配置流程

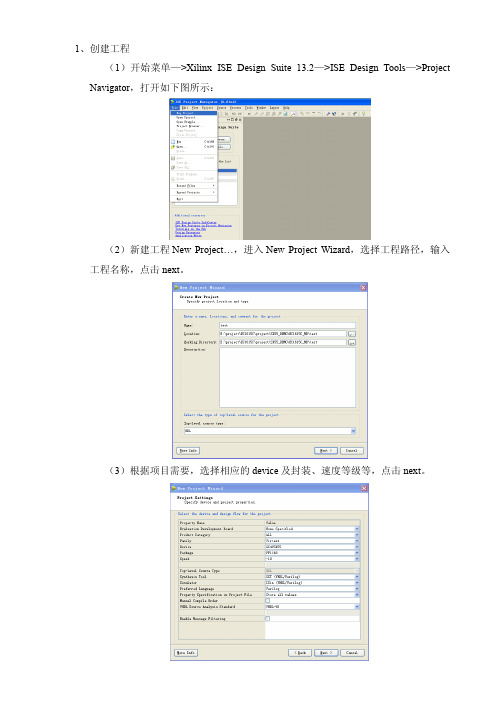

1、创建工程(1)开始菜单—>Xilinx ISE Design Suite 13.2—>ISE Design Tools—>Project Navigator,打开如下图所示:(2)新建工程New Project…,进入New Project Wizard,选择工程路径,输入工程名称,点击next。

(3)根据项目需要,选择相应的device及封装、速度等级等,点击next。

(4)显示新建工程信息,点击Finish,完成工程创建。

2、配置Microblaze软核(1)右键器件,这里是xc4vsx55-10ff1148,选择New Source,进入添加向导。

(2)选择Embedded Processor,输入文件名称和路径,点击next。

接着点击Finish 完成添加,系统会提示如下图所示,点击yes进入BSB Wizard。

(3)选择Create a new design,点击next。

(4)因为是自行设计的PCB板,所以选择create a system for a custom board,点击next。

(5)选择Single-Processor System,点击next。

(6)根据实际情况,选择参考时钟(PCB板上系统时钟频率)、工作频率(一般建议系统时钟不超过150MHz,这里选择100MHz),Local Memory选择64KB,点击next。

(7)添加外设。

这里可直接next,稍后在图形界面里可以进行添加配置。

(8)一直点击next,直到Finish,完成Microblaze软核的创建,如下图所示。

3、在Microblaze软核里添加外设(1)在上述界面即可添加外设。

这里以GPIO为例。

双击选择XPS General Purpose IO确定添加后,进入GPIO配置页面。

这里不添加中断,并选择位宽为8位。

设置完成后点击OK。

(2)添加后在如下图所示界面里,将GPIO挂到mb_plb总线上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第7卷第23期2007年12月1671—1819(2007)23—6190—03科学技术与工程ScienceTechnologyandEngineeringV01.7No.23Dec.2007⑥2007Sci.Tech.Engng.基于MicroBlaze的FPGA重配置系统设计李炜Jl’(电子科技大学自动化工程学院,成都610054)摘要介绍了XilinxFPGA的配置模式和配置原理,提出一种基于MicroBlaze软核处理器的FPGA重配置系统设计方案。

该方案灵活简便,具有很高的应用价值。

关键词XilinxFPGAMicroBlaze微处理器重配置中图法分类号TN919.3;文献标识码A基于SRAM工艺的FPGA集成度高,逻辑功能强,可无限次重复擦写,被广泛应用于现代数字系统的设计中。

基于SRAM工艺的FPGA在掉电后数据会丢失,当系统重新上电时,需要对其重新配置。

在系统重构或更换系统工作模式时,往往也需要对FPGA进行在线重配置,以获得更加灵活的设计和更加强大的功能。

在这些过程中,如何根据系统的需求,快速高效地将配置数据写入FPGA,对FPGA进行在线重配置,是整个系统重构的关键。

在FPGA的重配置系统设计中,通过外部控制器对FPGA进行在线重配置的方案是上佳选择。

在这种方案中,可以由外部控制器模拟FPGA的配置时序,并采用串行化,或者并行化的方式发送FPGA所需要的配置时钟和数据。

同时,在配置过程中控制器可以监控配置进程,很好地保证在线重配置的实时陛和高效性。

现基于MicroBlaze软核处理器,提出了一种灵活简便的FPGA在线重配置系统设计方案。

1XilinxFPGA配置方式及配置流程实现FPGA的数据配置方式比较多,以Xilinx公司的Virtex-4系列FPGA为例,主要有从串模式、主串模式、8位从并模式、32位从并模式、主并模式及JTAG模式这六种配置方式。

这些模式是通过2007年7月313收到第一作者简介:李炜(1983一),男,成都电子科技大学自动化工程学院研究生,研究方向:基于FPGA的嵌入式系统开发。

E—mail:kevinway@163.corn。

FPGA模式选择引脚M2、M1、M0上设定的电平组合来决定的。

Virtex-4的配置流程主要由四个阶段组成。

当系统复位或上电后,配置即开始,FPGA首先清除内部配置存储器,然后采样模式选择引脚M2、M1、M0以确定配置模式,之后下载配置数据并进行校验,最后由一个Start—up过程激活FPGA,进入用户状态。

在配置过程中,通过置低Virtex-4的PROG—B引脚可以重启配置过程。

在FPGA清除内部配置存储器完毕后,INIT—B引脚会由低电平变高,如果通过外部向INIT_B引脚置低电平,则可以暂停FPGA的配置过程,直到INIrll一B变为高电平。

在配置数据下载完毕且FPGA经过Start—up过程启动成功后,其DONE引脚将会由低电平变高。

2从串配置模式及时序在Virex-4的配置模式中,从串配置模式是最为简便和最容易控制的,本设计就采用从串模式对Virtex-4进行重配置。

在从串模式下需要使用到Virtex-4FPGA的几个相应配置管脚,其管脚功能和方向如表1所示。

在从串配置模式下,当MicroBlaze微处理器通过GPIO口输出将PROG_B引脚置为低电平后,Vir.tex-4FPGA将开始复位片内的配置逻辑,这一复位过程持续时间大约为330ns。

在PROG_B输入低电平的同时,FPGA将置低INIT_B和DONE信号,表明其正处于配置过程中。

片内配置逻辑复位完毕后,23期李炜:基于MicroBlaze的FPGA重配置系统设计6191FPGA会置高INIT—B引脚电平并采样模式选择引脚M[2:0]确定所采用的配置模式(在从串配置模式下,M0、M1、M2输人均为高电平)。

之后,FPGA进入配置数据装载阶段,MicroBlaze微处理器检测到INIT_B高电平信号后,便可通过GPIO通道向FPGA发送配置数据bit位,而FPGA将在每个外部CCLK时钟上升沿采样配置数据bit位。

所有配置数据发送完毕后FPGA便会进入Start—up启动过程,默认设置下经过4个内部时钟周期,FPGA便启动完毕并会置高DONE引脚电平,表明配置成功,已进入用户状态。

从串配置模式具体的配置时序如图1所示。

表1从串模式配置管脚PROGB]厂———————————一INIT旷——\/__——————————一八几厂、厂、…_、CCLKDIN—————矩匦蜒煎Ⅺ遁×甄…)—一厂一T)oNF图1从串模式配置时序图3重配置系统硬件电路设计设计选用了MicroBlaze微处理器作为Virtex-4FPGA在线重配置的外部主控制器。

MicroBlaze是Xilinx公司的微处理器IP软核,采用了RISC指令集和哈佛体系结构的32位指令和数据总线,可嵌入在Xilinx公司FPGA中,并和其他外设IP核及用户IP核一起,构成系统级集成电路(SystemOnChip,SOC)。

由于MicroBlaze处理器在FPGA中实现,并且可以灵活的选择其外设IP,对外部电路的控制非常方便,因此利用MicroBlaze微处理器作为’FPGA在线重配置系统的控制器是较好的选择。

Virtex-4FPGA的配置数据量较大,本设计选用了Flash存储器S29GL512N作为配置数据的外部存储器。

此外设计还选用了Xilinx公司的小规模FP.GAXC3S200作为MicroBlaze微处理器的实现平台,足以充分发挥MicroBlaze的强大功能。

图2所示为本设计方案的电路结构框图。

WE驻|HG唧DINoEG玛DlPRoGBCEGm2CCLK一FlashMicroBlazeⅥItex.4A[0:24】GPl03n盯TBGPl04DoNED[0:15]图2在线重配置系统电路结构系统设计中,MicroBlaze处理器通过挂接在其片内外设总线上的OPB—EMC(外部存储器控制器)IP核对Hash存储器进行读写操作。

当系统进行在线重配置操作时,由OPB—EMC模块从Flash存储器中读出FPGA的配置数据,并进行相应的地址递增操作和读写使能操作,然后通过片内外设总线将数据传送给MicroBlaze处理器。

MicroBlaze处理器则通过GPIO输出口与FPGA的各配置引脚相连,负责向FPGA发送配置数据和时钟信号,监控FPGA配置过程中的状态信号变化并做出相应处理,保证配置成功。

4重配置系统软件程序设计在配置过程中,时序配合要求十分严格,需要完全按照Virtex-4FPGA的配置时序进行,否则将导致配置过程失败。

重配置系统以Xilinx公司的嵌入式系统开发软件EDK作为平台,设计了FPGA在线重配置的软件程序,此程序运行在MicroBlaze处理器上,经实验证明效率较高。

按图1所示配置时序,程序首先通过GPIO口向FPGA的PROG_B引脚输出一个时间长度大于330ns的负脉冲并等待FPGA清除内部配置存储器。

延时一段时间后,若MicroBlaze检测到INIT—B电平为低,则表明清除配置存储器失败,需要重新向PROG—B发送负脉冲以重启配置过程。

当MicroBlaze检测到INIT_B引脚变为高电平后,程序便开始以bit为单位串行的向DIN引脚发送配置数据,同时向CCLK引脚发送配置时钟以保证Viaex-4FPGA在外部配置时钟6192科学技术与工程7卷的上升沿采样配置数据。

每次发送配置数据bit后,程序中的配置数据计数器也会递增以判断所有的配置数据是否发送完毕。

当所有的配置数据发送完毕之后,MicroBlaze处理器通过GPIO通道检测DONE引脚电平,若DONE信号变高,说明配置FPGA成功;若DONE信号为低,则说明配置失败,程序将重新进行配置。

软件程序流程图如图3所示。

图3在线重配置软件流程图5结束语本文提出了一种基于MicroBlaze软核微处理器的对Xilinx系列FPGA进行在线重配置的系统方案。

该方案适用于采用MicroBlaze处理器的FPGA嵌入式系统中,具有高效性和实时性。

经实验结果验证,在XC3¥200中实现的MicroBlaze处理器核心频率运行在50MHz,对一片Virtex-4LX60的高端大容量FPGA进行在线重配置,整个配置过程仅需要4—5秒时间,软件程序执行效率较高且配置数据的发送准确无误,能很好的保证在线重配置的实时性和可靠性要求。

同时由于MicroBlaze软核处理器能够在FPGA中实现,所以在使用FPGA设计的数字系统中,此方案能够省去额外的外部控制器芯片,减小PCB电路板面积,最大限度地精简系统结构,在智能化系统设计、信号测试系统设计等领域都具有良好的应用前景。

参考文献1MicroBlazeProcessorReferenceGuide.XiliaxCorporation,June14,20052Virtex-4ConfigurationGuide.XilinxCorporation,Jan24,20063徐志军,徐光辉.CPLD/FPGA的开发与应用.北京:电子工业出版社,2002DesignofFPGAReconfigurationSystemBasedonMicroBlazeLIWei(CollegeofAutomation,UniversityofElectronicScienceandTechnologyofChina,Chengdu610054,P.R.China)[Abstract]TheconfigurationmodesandconfigurationtheoryofXilinxFPGAisintroduced,thenasystemlevelsolutionusingMieroBlazeembeddedprocessortoreeonfigureFPGAispresented.Thisdesignisflexibleandcon-venient,alsohasgreatvalueintheapplicationfields.[KeyWords]XilinxFPGAMicroBlazeprocessorreconfiguration。