Virtuoso_Foundation_IP_Characterization

virtuoso schematic的基本组成

Virtuoso Schematic是Cadence公司的一款原理图设计工具,用于电路设计。

它的基本

组成包括以下几个方面:

1. 工作区(Workspace):用户可以在该区域内进行原理图设计和编辑。

2. 工具栏(Toolbars):包括常用的绘图工具、文本工具、组件工具等,方便用户进行

快速的原理图设计。

3. 组件库(Library Browser):包括了大量的电子元器件的符号和模型,用户可以从中选择需要的元件并将其拖拽到工作区中进行使用。

4. 属性窗口(Properties Window):主要用于设置当前选中元件或线段的属性,如名称、引脚数目、尺寸等。

5. 库管理器(Library Manager):用于管理所有的原理图库,并提供对库中元件的编辑、删除和添加等功能。

6. 原理图编辑器(Schematic Editor):包括了大量的原理图设计工具,如连线工具、

接地/电源符号、布局工具等,用户可以通过该编辑器创建和修改原理图。

7. 仿真环境(Simulation Environment):用户可以通过该环境对原理图进行仿真,比

如进行DC分析、交流分析、时域分析等。

总的来说,Virtuoso Schematic具备了丰富的功能和强大的仿真能力,可以帮助电路设

计人员进行高效的原理图设计和仿真。

Cadence芯片版图设计工具Virtuso

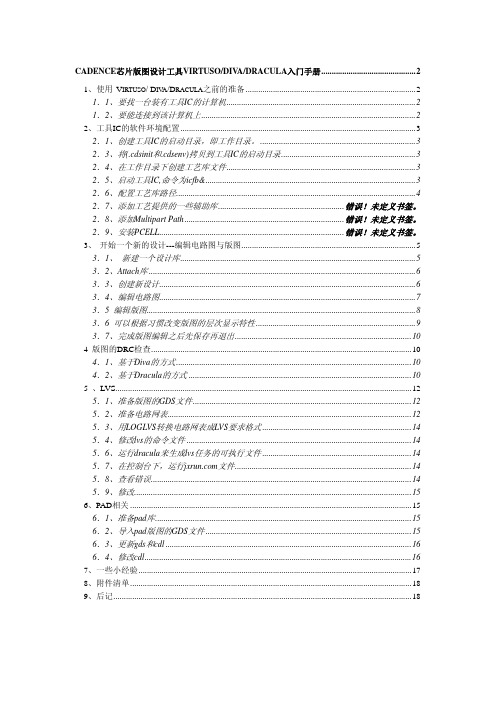

CADENCE芯片版图设计工具VIRTUSO/DIV A/DRACULA入门手册 (2)1、使用V IRTUSO/ D IV A/D RACULA之前的准备 (2)1.1、要找一台装有工具IC的计算机 (2)1.2、要能连接到该计算机上 (2)2、工具IC的软件环境配置 (3)2.1、创建工具IC的启动目录,即工作目录。

(3)2.3、将(.cdsinit和.cdsenv)拷贝到工具IC的启动目录 (3)2.4、在工作目录下创建工艺库文件 (3)2.5、启动工具IC,命令为icfb& (3)2.6、配置工艺库路径 (4)2.7、添加工艺提供的一些辅助库............................................................错误!未定义书签。

2.8、添加Multipart Path............................................................................错误!未定义书签。

2.9、安装PCELL........................................................................................错误!未定义书签。

3、开始一个新的设计---编辑电路图与版图 (5)3.1、新建一个设计库 (5)3.2、Attach库 (6)3.3、创建新设计 (6)3.4、编辑电路图 (7)3.5 编辑版图 (8)3.6 可以根据习惯改变版图的层次显示特性 (9)3.7、完成版图编辑之后先保存再退出 (10)4 版图的DRC检查 (10)4.1、基于Diva的方式 (10)4.2、基于Dracula的方式 (10)5 、LVS (12)5.1、准备版图的GDS文件 (12)5.2、准备电路网表 (12)5.3、用LOGLVS转换电路网表成LVS要求格式 (14)5.4、修改lvs的命令文件 (14)5.6、运行dracula来生成lvs任务的可执行文件 (14)5.7、在控制台下,运行文件 (14)5.8、查看错误 (14)5.9、修改 (15)6、PAD相关 (15)6.1、准备pad库 (15)6.2、导入pad版图的GDS文件 (15)6.3、更新gds和cdl (16)6.4、修改cdl (16)7、一些小经验 (17)8、附件清单 (18)9、后记 (18)Cadence芯片版图设计工具Virtuso/Diva/Dracula入门手册(以上华0.6um DPDM工艺设计库为例)Cadence 是一套功能强大的EDA软件,包含有诸如IC、SE等常用芯片设计工具。

Cadence IC版图工具Virtuso的使用简介

建立一个库(续)

3.在CIW窗口中点击file/ new/ library….. 给库任意取名字(如:lib_1),在右侧选 compile a new techfile. (如图) 点击OK,填入工艺文件的路径和名称。

DRC检查(续)

DRC检查(续)

• 在CIW窗口中查找错误

• 回到layout中改正错误,并重新做DRC。反复修改,直到所 有错误都被修改。

LVS检查

• DRC保证了版图能够在流片中没有违规 • LVS则保证了流片出来逻辑功能的正确性。 • LVS=layout versus schematic • 步骤:

建立一个库(续)

4.在CIW窗口中点击tools/ library manager 我们就看到了新建的库lib_1 在下拉菜单中选择new/ cell view,取一个cell name:INV。 在该窗口中点击tool选择Virtuoso。 OK!这样就建立了一个画版图的平台。

如何调入版图的层

• N-Well

N-Well的规则(续)

Island and Poly

Island and Poly(续)

Poly

PLUS

PLUS(续)

Contact and Metal-1

Contact

Metal-1

Via-1

Metal-2 and Via

Metal-3

Cadence 版图工具Virtuoso简介

作者:卢俊 2006-7-5

内容安排

• 本次上机实验的任务 • 使用Virtuoso设计版图的步骤简介 • 电子58所0.5um工艺设计规则介绍

关于Cadence virtuoso的一些实用技巧

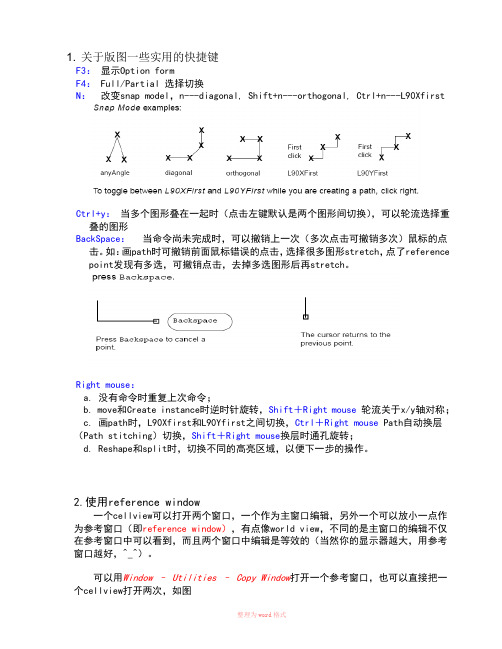

1. 关于版图一些实用的快捷键F3:显示Option formF4: Full/Partial 选择切换N:改变snap model,n---diagonal, Shift+n---orthogonal, Ctrl+n---L90XfirstCtrl+y:当多个图形叠在一起时(点击左键默认是两个图形间切换),可以轮流选择重叠的图形BackSpace:当命令尚未完成时,可以撤销上一次(多次点击可撤销多次)鼠标的点击。

如:画path时可撤销前面鼠标错误的点击,选择很多图形stretch,点了reference point发现有多选,可撤销点击,去掉多选图形后再stretch。

Right mouse:a. 没有命令时重复上次命令;b. move和Create instance时逆时针旋转,Shift+Right mouse轮流关于x/y轴对称;c. 画path时,L90Xfirst和L90Yfirst之间切换,Ctrl+Right mouse Path自动换层(Path stitching)切换,Shift+Right mouse换层时通孔旋转;d. Reshape和split时,切换不同的高亮区域,以便下一步的操作。

2.使用reference window一个cellview可以打开两个窗口,一个作为主窗口编辑,另外一个可以放小一点作为参考窗口(即reference window),有点像world view,不同的是主窗口的编辑不仅在参考窗口中可以看到,而且两个窗口中编辑是等效的(当然你的显示器越大,用参考窗口越好,^_^)。

可以用Window – Utilities – Copy Window打开一个参考窗口,也可以直接把一个cellview打开两次,如图可以同时在两个窗口中编辑3.关于Path stitching①画path时可以从一层切换到另一层,并且自动打上对应的接触孔,这个功能叫path stitching.②在Change To Layer 栏里选择你要换的layer,也可以通过Control+right mouse键来选择需要换的层。

Virtuoso软件的使用技巧

Tools →Library Manager

新建库: File→New →Library

File→New →Cell View

Tool:Composer-Schematic

主要内容

1、Virtuoso简介 2、如何正确进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

主要内容

1、Virtuoso简介 2、如何进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

Calibre →Run PEX

128

129 # add layout topcell name to replace xxx

130 setenv LAYOUT_PRIMARY "OP_CL_3p"

131 #setenv LAYOUT_PRIMARY "mpw_08"

132 #setenv LAYOUT_PRIMARY "HDPWM_top_with_buffer"

调用生成的模块

常用的快捷键

i (instance):插入元件 f (full screen):全屏幕 w (wire) :连线 p (pin):加管脚 q (quality):编辑属性

e:进入下一层模块 ctrl+e:返回上一层模

块

[ : 缩小两倍 ] :放大两倍

主要内容

1、Virtuoso简介 2、如何进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

Virtuoso cadence 教程轻松学

EDA概述

CADENCE

3、全定制IC设计工具

Virtuos Schematic Composer Analog Design Environment Virtuos Layout Editor Spectra Virtuoso Layout Synthesizer Assura dracula Diva

(3)定制设计

标准单元法 通用单元法

13

第二章 EDA概述

CADENCE

• 电子设计自动化(EDA:Electronic Design Automation)就是利用计算机作为工作平台进 行电子自动化设计的一项技术。

• 涵盖内容:系统设计与仿真,电路设计与 仿真,印制电路板设计与校正,集成电 路版图设计数模混合设计,嵌入式系统 设计,软硬件系统协同设计,系统芯片 设计,可编程逻辑器件和可编程系统芯 片设计,专用集成电路设计等

18

EDA概述

CADENCE

• EDA发展概况:

(1)20世纪60、70年代出现计算机辅助设计(CAD) (2)随后出现CAE、CAM、CAT、CAQ。 (3)20世纪80年代,初级的具有自动化功能的EDA出现。 (4)20世纪90年代,EDA技术渗透到电子设计和集成电

路设计各个领域,形成了区别于传统设计的整套设计思 想和方法。 (5)当前,深亚微米工艺和SoC设计对EDA技术提出更 高更苛刻的要求。

27

EDA概述

CADENCE

• EDA主要供应商:

VHDL仿真 行为综合 逻辑综合 可测性设计 低功耗设计 布局布线

后仿真

Cadence Vantage Synopsys Synopsys Alta Synopsys Compass Mentor Graphics Synopsys Sunrise Compass Synopsys Epic Cadence Avant! Mentor Graphics Synopsys Cadence Compass IKOS Vantage

virtools教程 虚拟角色的导入与运动制作PPT课件

3.依照第三章 第一单元的制作流程,将悟空的 动作与键盘对应调整好。

3.1分别拖动 到悟空身上,注意分别改名。

12

13

创建脚本 3.2加入

14

连接并修改参数 点击播放,发现悟空待机状态。

15

3.3拖放

16

连接

17

4.拖放

18

连接

19

ห้องสมุดไป่ตู้

5.测试,发现悟空飘浮在地板上面,下面增加 地板属性:

41

6.请将水桶3中的Send Message的Out连接到 Collision Detection的In以达成循环。

7.请将水桶2脚本中的Bezier Progression的 Out连接到Wait Message的In以达成循环。

8.测试, sample030204.cmo

42

虚拟角色定位移动的制作

20

双击 地板 可看到地板属性

21

7.测试,会发现人物可以走在地板上,但到地 板外则会掉下去。

8.修改参数

第一个参数保持在地板边界,第二个参数增加 人物的重量,让人物不再发飘。

9.测试,可参考sample030201.cmo

22

2-2基本碰撞处理

人物这个时候还是可以穿墙而过的,下面增加 碰撞功能

54

5-2平面影子的制作

1.打开sample0304.cmo,创建灯光

55

56

2.找到地板并创建脚本

57

3.加入

58

59

4.添加属性

60

61

5.测试一下,注意这个效果只适用于对象水平 面上,不适用于立体对象上, sample030502.cmo

62

5-3投射影子的制作

virtuoso高效率使用技巧

Virtuoso是一个用于模拟和设计集成电路的软件工具。

以下是一些高效率使用Virtuoso的技巧:

1. 熟悉命令行界面:Virtuoso提供了命令行界面,用户可以使用命令行工具执行各种操作。

通过熟悉命令行界面,可以更快地执行任务并减少错误。

2. 使用脚本文件:Virtuoso支持使用脚本文件来自动化任务。

通过编写脚本文件,可以自动执行一系列操作,从而节省时间并提高效率。

3. 优化设计流程:在设计集成电路时,应该优化设计流程,以减少不必要的步骤和等待时间。

例如,可以尝试并行处理多个任务,或者在等待仿真结果时进行其他工作。

4. 善于利用搜索功能:Virtuoso提供了强大的搜索功能,可以帮助用户快速找到所需的信息。

通过使用搜索功能,可以更快地找到库元件、命令、参数等。

5. 掌握常用快捷键:Virtuoso支持使用快捷键来执行常见操作。

通过掌握常用快捷键,可以更快地完成任务并减少鼠标点击次数。

6. 不断学习和实践:Virtuoso是一个不断发展和更新的工具,因此用户需要不断学习和实践以掌握新的功能和技巧。

可以通过阅读教程、参加培训课程、与其他用户交流等方式来提高自己的技能水平。

总之,高效率使用Virtuoso需要熟悉命令行界面、使用脚本文件、优化设计流程、善于利用搜索功能、掌握常用快捷键以及不断学习和实践。

最新实验一-Virtuoso原理图和图标编辑器的基本使用

最新实验一-Virtuoso原理图和图标编辑器的基本使用实验一Virtuoso原理图和图标编辑器的基本使用目录1.实验目的2.创建一个新的自定义单元库3.使用 Cadence Virtuoso 原理图编辑器构建一个反相器4.创建一个自定义元器件图标1.实验目的本实验采用AMI06工艺设计一个反相器,以此使学生达到熟悉Cadence Virtuoso 原理图和图标编辑器使用,记住常用热键组合以及掌握与特定工艺库关联之目的。

2.创建一个新的自定义单元库启动 Cadence,调用 CIW(Command Interpreter Window)首先启动计算机,在用户名处键入 cdsusr, 密码处键入123456,进入Linux操作系统桌面,在cdsusr’s Home文件夹中创建iclabs 子文件夹。

请记住一定要创建这个子文件夹,这样才不会影响到cdsusr根目录下的cds.lib文件。

操作如下:File --> Create Folder, 在新创建的文件夹名称处键入iclabs(可取不同名字,学号和本人名字拼音等)。

进入Linux桌面,单击鼠标右键打开终端。

见图1。

图1. Linux桌面操作在打开的终端中执行下列命令:见图2的红色框线内。

图2. Linux终端执行第二个命令后你就可看见Cadence软件的CIW窗口出现。

见图3所示。

图3. Cadence软件的CIW窗口在CIW窗口中点击Tools-->Library Manager..., 将打开库管理器(图4)。

图4. 库管理器你可看到NCSU提供的库已显示在Library栏目中,有NCSU_Analog_Parts,...等。

点击库管理器中的File-->New-->Library..., 将打开New Library 对话窗口, 现创建一个新库取名为IClab1。

见图5。

图5. 创建一个自定义元件库点击OK弹出关联工艺库对话框(图6),选择Attach to an existing techfile。

版图绘制及VIRTUOSO的使用

• Ctrl+F显示上层等级 • Shift+F显示所有等级 • F fit,显示你画的所有图形 • K 标尺工具 • Shift+K清除所有标尺。 • L 标签工具

• M 移动工具 • Shift+M 合并工具,Merge • N 斜45对角+正交。 • Shift+O 旋转工具。Rotate • O 插入接触孔。 • Ctrl+P 插入引脚。 Pin • Shift+P 多边形工具。Polygon • P 插入Path。路径。 • Q 图形对象属性。选中一个图形先 • R 矩形工具。绘制矩形图形。 • S 拉伸工具。可以拉伸一个边。也

• System default location ./.cdsenv

2019/5/19

共85页

24

• File

.cdsinit

• Purpose

A Cadence SKILL language file

executed when the Cadence design framework II (DFII)

ault.drf

• System default location ./display.drf

2019/5/19

共85页

27

Using the Display Options Form

2019/5/19

共85页

28

Using the Layout Editor Options Form

2019/5/19

2019/5/19

共85页

20

Layout Editor 菜单(1)

Abstract用于版图抽取,Dracula Interactive用于Dracula工具进行DRC等 Verify菜单下的DRC等是用于Diva工具的。

virtuoso基本指令

Virtuoso的基本指令包括一些常用的操作快捷键,例如:

- 常规操作:Ctrl + N用于新建设计,Ctrl + O用于打开设计,Ctrl + S用于保存设计。

如果需要撤销或重做操作,可以使用Ctrl + Z和Ctrl + Y。

此外,Ctrl + C可以复制选中的元件或文本,Ctrl + V用于粘贴元件或文本,Ctrl + X用于剪切选中的元件或文本。

若需全选元件或文本,则可以使用Ctrl + A。

在查找元件或文本时,可以使用Ctrl + F,而跳转到指定的元件或文本,则是通过Ctrl + G实现。

- 其他指令:编辑器的打开可以通过Ctrl + E完成,打印设计的指令是Ctrl + P。

此外,还有一些未提及但可能用到的操作快捷键,例如:

- Layout操作:按shift+z可以实现缩小,ctrl+z则可以放大。

F键可以使整图居中显示,u键可以撤销上一步操作。

virtuoso schematic的基本组成

virtuoso schematic的基本组成摘要:1.引言2.Virtuoso Schematic 的定义和作用3.Virtuoso Schematic 的基本组成部分3.1 数据平面3.2 控制平面3.3 物理平面4.结论正文:【引言】随着电子技术的快速发展,电路设计越来越复杂,对于电子设计自动化(EDA)工具的需求也日益增加。

Virtuoso Schematic 是一款广泛应用于电子设计领域的EDA 工具,它以其强大的功能和灵活性而受到广大工程师的青睐。

为了更好地理解和使用Virtuoso Schematic,我们需要了解其基本组成。

【Virtuoso Schematic 的定义和作用】Virtuoso Schematic 是一款用于电路设计和仿真的软件工具,它可以帮助工程师快速、准确地完成复杂的电路设计。

通过Virtuoso Schematic,工程师可以绘制和编辑电路图,进行电路仿真和分析,以及生成电路原理图和布局图等。

【Virtuoso Schematic 的基本组成部分】Virtuoso Schematic 主要由三个部分组成,分别是数据平面、控制平面和物理平面。

【3.1 数据平面】数据平面是Virtuoso Schematic 中最重要的部分,它包含了电路设计中所有的信息,如元器件、连线、电源、地等。

数据平面是电路设计的核心,所有的电路仿真和分析都是基于它进行的。

【3.2 控制平面】控制平面主要用于控制Virtuoso Schematic 的运行,包括电路仿真、分析和生成等操作。

通过控制平面,工程师可以方便地对电路进行各种操作,如添加元器件、修改连线、调整参数等。

【3.3 物理平面】物理平面是Virtuoso Schematic 中用于描述电路物理特性的部分,如元器件的尺寸、形状、材料等。

物理平面对于电路的性能和可靠性有着重要的影响,因此,工程师需要仔细地定义和管理物理平面。

【结论】总的来说,Virtuoso Schematic 的基本组成包括数据平面、控制平面和物理平面。

使用Virtuoso设计全定制版图

使用Virtuoso设计全定制版图本文介绍利用virtuoso layout editor(以后简称le)创建全定制版图,以及vituoso le 的一些使用说明。

全文将用一个贯穿始终的例子来说明如何绘制全定制版图,一个最简单的反相器的版图.设计过程采用chartered(csm25rf)库—标准CMOS工艺库。

具体内容包括:1)如何打开virtuoso le和le 的一些设置;2)使用LSW窗口;3)使用le 创建一个版图;4)使用快捷键—bindkey;5)使用diva验证版图;6)使用diva 进行LVS;登陆以后,首先要先创建自己的工作目录,比如Work, cd Work.从csm25rf库所在文件夹下拷贝文件到自己的工作目录下,你的工作目录下必须有文件,不然在LSW窗无法显示绘制版图需要的各个图层。

从/CDS_ROOT/tools/dfII/cdsuser目录下拷贝 .cdsinit文件到自己的目录下,该文件是Cadence 自带的软件相关设置的文件,里面有相关字体的设置,Bindkey设置等,这里主要考虑Bindkey的设置,也可以设置自己的Bindkey,不过 Cadence默认的设置是足够的。

当然也可以单单靠鼠标来进行操作,virtuoso le 窗口有常用命令的工具栏,不过就我自己的感觉,用快捷键比鼠标要快很多。

如果要运行Diva LVS 还得有.simrc文件。

(不过这里有一个问题,服务器上的.simrc文件的设置跟csm25rf库有不一致的地方,运行Diva LVS 会出现目录LVS非法的错误。

运行vituoso le要打开virtuoso le ,首先要打开CIW窗口。

在shell 命令行下输入:icfb& 进入CIW 窗口,字符&使得cadence 在后台工作(即可以在shell命令行执行其它命令),也可以在shell 提示符下输入其它的命令来打开CIW窗口,如下图:(在这里也可以输入layout& 或者 layoutPlus&)检查设计需要的相关库是否存在。

Virtools中文手册

Virtools技术介绍法国拥有许多技术上尖端的小型三维引擎或平台公司。

例如,Virtools所开发的三维引擎成为微软XBox认可系统。

其特点是方便易用,应用领域广(游戏机,互联网,工业合作等)。

全球交互三维开发解决方案公司VIRTOOLS日前推出了最新版本Virtools Dev 2.1实时三维互动媒介创建工具。

Virtools在其Dev接口上加入了许多新功能,改善了工作流程,让用户可以专注于创作出完美的交互三维画面。

Virtools Dev 2.1具备多项全新功能,其中包括20多种新增的“行为模块(Behavioural Module)”,以及全新的DirectX 8.1引擎。

在其行为引擎(Behavioural Engine)及各管理系统上添加了新功能,Virtools SDK及Virtools Web Player允许用户随意操控,享受全新的体验。

Dev 2.1无论在图形用户接口(GUI)、行为引擎、管理系统与渲染引擎方面均达到了前所未有的水平。

Virtools具有灵活、易操作的特点,其“行为模块”可以重复使用,因此,不但加速了生产过程,降低生产成本,并使投资回报更大。

开发人员可以使用“行为数据库”或在C++中,借助于Virtools的软件研发套件(SDK)进行创作。

使用者界面介绍场景编辑器(3D Layout)在3D Layout的区域内可以显示目前正在编辑的场景,使用者可以在这区域内即时检视编辑、修改的状况。

所有的对象包括3D的物体、灯光、摄影机、线段...等,都可以在这部分中做修改,如位置的移动、旋转、缩放等,并即时显示修改后的结果。

档案资源管理(Level Manager)在档案中的所有对象,都会依照分类(CK Class的分类),显示在这部分,如3D 物体就会在此分类显示(3D 物体泛指档案中的3D模型),灯光会显示在Light的分类中,摄影机会显示在Camera的分类中...等,方便使用者管理档案中的资源。

virtuoso schematic的基本组成

virtuoso schematic的基本组成

一个Virtuoso schematic的基本组成主要包括以下几个部分:

1. 元件库(Library):可包含各种元件的库,包括模拟元件(如电阻、电容、电感等)、数字元件和特殊元件(如运算放大器、晶体管等)。

元件库通常按照类型进行组织,方便在原理图中使用。

2. 元件(Component):原理图中使用的具体元件。

可以从元件库中选择并放置到原理图中。

每个元件在原理图中有唯一的名称和引脚标号。

3. 连接线(Net):用于连接元件之间的电气连接。

连接线可以通过直线或曲线的方式绘制,并被命名为一个电路网络。

4. 电源(Power Source):提供电路的电源信号。

电源通常包括正极和负极,并通过引脚与元件连接。

5. 地(Ground):连接所有地点的参考点,通常用于连接电路的共地引脚。

6. 标号(Label):用于标识和注释元件、连接线和电源等。

标号可以包含文本、数值和描述,以便更好地理解电路结构。

7. 注释(Comment):用于添加说明、分析或其他相关信息的文本框。

注释通常用于帮助设计者和读者更好地理解电路。

8. 网表(Netlist):记录了原理图中使用的元件、引脚、连接

线和电源等信息,用于后续的仿真、布局和电路板设计等环节。

这些基本组成部分可以根据具体需求进行组合和扩展,以满足不同的电路设计要求。

virtuosuo 用法

virtuosuo 用法

Virtuoso是一个电路模拟软件,用法如下:

1.打开Virtuoso软件,创建一个新的电路设计。

2.在电路设计界面中,添加所需的电子元件和连接线,以构建电路。

3.选择模拟算法,例如SPICE、IBIS等,以用于模拟电路的性能。

4.设置模拟参数,例如电压、频率等,以确定模拟的特定条件。

5.运行模拟,并分析结果。

Virtuoso会提供各种分析工具,例如波形图、眼图等,以帮助用户理解电路的性能。

6.根据需要调整电路设计,并重新进行模拟,以优化电路性能。

此外,Virtuoso还有一些常用功能,如复制/粘贴、查找/替换、批量修改等操作,可以大大提高电路设计效率。

同时,Virtuoso还支持多种脚本语言,例如Tcl/Tk、Perl、Python等,可以用于自动化处理和批处理操作。

需要注意的是,Virtuoso是一个比较复杂的软件,需要一定的学习和实践才能熟练使用。

建议在掌握基本的电子技术和模拟算法知识后再使用Virtuoso进行电路设计和模拟。

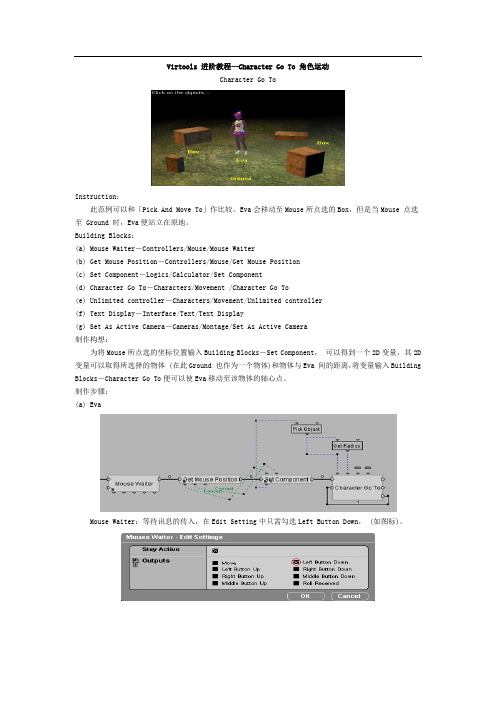

Virtools 进阶教程—Character Go To 角色运动

Virtools 进阶教程—Character Go To 角色运动Character Go ToInstruction:此范例可以和「Pick And Move To」作比较。

Eva会移动至Mouse所点选的Box,但是当Mouse 点选至 Ground 时,Eva便站立在原地。

Building Blocks:(a) Mouse Waiter-Controllers/Mouse/Mouse Waiter(b) Get Mouse Position-Controllers/Mouse/Get Mouse Position(c) Set Component-Logics/Calculator/Set Component(d) Character Go To-Characters/Movement /Character Go To(e) Unlimited controller-Characters/Movement/Unlimited controller(f) Text Display-Interface/Text/Text Display(g) Set As Active Camera-Cameras/Montage/Set As Active Camera制作构想:为将Mouse所点选的坐标位置输入Building Blocks-Set Component,可以得到一个2D变量,其2D 变量可以取得所选择的物体 (在此Ground 也作为一个物体)和物体与Eva 间的距离,将变量输入Building Blocks-Character Go To便可以使Eva移动至该物体的轴心点。

制作步骤:(a) EvaMouse Waiter:等待讯息的传入,在Edit Setting中只需勾选Left Button Down, (如图标)。

Get Mouse Position:当Left Button Down讯息传入后,即得到Mouse Cursor的坐标位置,该坐标位置X值与Y值再分别由pOut输出至Building Blocks-Set Component的pIn,其值为Component1和Component2。

关于cadence-virtuoso的一些实用技巧

关于cadence-virtuoso的一些实用技巧以下是一些关于Cadence Virtuoso的实用技巧:1. 利用工具栏和快捷键:Virtuoso具有丰富的工具栏和快捷键选项,可以帮助您快速访问常用功能。

了解并使用这些选项可以提高您的工作效率。

2. 使用布局编辑器:布局编辑器是一个强大的工具,可以用于设计芯片的物理布局。

学会使用布局编辑器的功能,例如图层放置、区域分配、设备放置等,可以将设计优化到最佳状态。

3. 路由设置:在进行布线时,可以设置不同的路由参数以满足设计的要求。

通过调整路由设置,如寻路方向、蔽隔层规则等,可以生成更好的布线结果。

4. 使用 DRC 和 LVS 检查:DRC (Design Rule Check) 和 LVS (Layout vs. Schematic) 是确保设计质量的重要工具。

在设计结束后,务必运行 DRC 和 LVS 检查来查找潜在的错误和不匹配。

5. 嵌入定制的脚本:Virtuoso支持脚本语言,如Skill和Tcl。

通过嵌入自己的脚本,可以自动执行一系列的操作,从而提高设计的自动化程度。

6. 使用层间生成器:层间生成器是一个实用的工具,可以自动生成多层布线。

通过使用层间生成器,可以大大简化布线流程,减少手动操作的时间和复杂性。

7. 查看设计历史:Virtuoso提供了设计历史的功能,可以查看和恢复之前的设计版本。

在设计过程中,定期保存和查看设计历史,可以避免不必要的错误和后悔。

8. 配置自定义快捷键:Virtuoso允许用户配置自定义快捷键。

根据个人喜好和使用习惯,将常用的功能和操作设置为自定义快捷键,可以提高工作效率。

希望这些技巧对您有帮助!请注意,Cadence Virtuoso是一款功能强大的工具,掌握它需要一定的时间和实践。

不断学习和探索,您将能够更加熟练地使用该软件进行芯片设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Virtuoso Foundation IP Characterization

MMSIM

Full Custom Routing Virt

Des ment

MMSIM IntegrationVirtuo

St d mory

rizationProcess Variation

ex I/Os Custom

form Precision Layout

• Advanced timing, power, and signal integrity DC current source models

Virtuoso Liberate MX

Virtuoso Liberate LV

Virtuoso Variety

Memory characterization

A Complete Solution

Virtuoso Foundation IP Characterization is a suite of highperformance tools for characterizing, validating, and generating libraries for standard cells, I/Os, and memories. The suite achieves both accuracy and high speed through the powerful combination of “Inside View”—patented technology for generating and optimizing characterization stimulus—coupled with a parallel processing capability that takes advantage of enterprise-wide compute resources. The solution includes Virtuoso Liberate, Virtuoso Liberate MX, Virtuoso Liberate LV, and Virtuoso Variety.

Virtuoso Liberate

Standard cell and complex I/O

characterization

• Ultra-fast library characterization

• Patented “inside view” technology for optimized runtime

MMSIM IntegrationVirtuo

St d mory

rizationProcess Variation

ex I/Os

Custom

so FouAnddvaantcieodnMIoPdeClihngaracte

Cells

Compl

Inside View

Blocks

Me

Library Validation

ify Manuf

uoso

Custom IC Design

Analog Prototyping源自PlatignVer

Correct by Construction

acture

Imple

Parasitic-Aware Design

Spectre

Spectre APS

Accurate, high-performance

• AOCV tables

Figure 3: The solution comprises four main product technologies

Virtuoso Liberate

Virtuoso Liberate is an ultra-fast standard cell and I/O library creator. As part of our complete Foundation IP Characterization solution, it generates electrical cell views for timing, power, and signal integrity including advanced current source models (CCS and ECSM).

Virtuoso Foundation IP Characterization

A complete solution for fast and accurate IP modeling and validation

Cadence® Virtuoso® Foundation IP Characterization delivers the industry’s most comprehensive and robust solution for the characterization and validation of your foundation IP—from standard cells and I/Os to complex I/Os and memory. Its patented “inside view” technology delivers better correlation to silicon by improving library throughput and ensuring timing, power, noise, and statistical coverage of your cells.

Virtuoso Foundation IP Characterization also integrates with Virtuoso Spectre® Circuit Simulator, the industry-standard SPICE simulator, delivering even greater throughput than when used with standalone thirdparty simulators.

Library validation

Process variation modeling

• Characterization of large embedded memories

• Unique “dynamic partitioning” technology for optimized runtime

Benefits

• Ultra-fast cell library characterization for standard cells and complex I/Os

• Automatic pre-characterization of each cell using the “inside view” transistor-level circuit analysis technology to learn all internal logic states and enable automatic vector generation.

• Ultra-fast throughput to complete library validation overnight on a small number of multi-core computers

• Variation-aware timing model creation accounting for process variations (systematic and random) for any set of correlated or uncorrelated process parameters.

Our patented “inside view” approach automatically pre-characterizes each cell using transistor-level circuit analysis, which yields all the necessary stimulus and internal logic states to ensure a complete, accurate, and highly efficient characterization of that cell.

Spectre Infrastructure Common infrastructure, advanced simulation database,

versatile front-end parser, robust device library

Spectre Applications Comprehensive coverage, integrated with Virtuoso, LEA, Liberate,

simulatioin

Spectre RF

Analog and RF-IC noise analysis

Spectre XPS

High-speed, high-capacity full-chip variation

analysis

AMS Designer

Mixed-signal verification at all abstraction levels

Allegro, and Encounter Timing System technologies

so FouAnddvaantcieodnMIoPdeClinhgaracte

Cells

Compl

Inside View

Blocks

Me

Library Validation

Figure 2:A complete solution for custom simulation and characterization, with Virtuoso Multi-Mode Simulation and integrated Spectre technology