Spartan-14.7平台与ISE软件的入门

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

ISE软件的基本操作

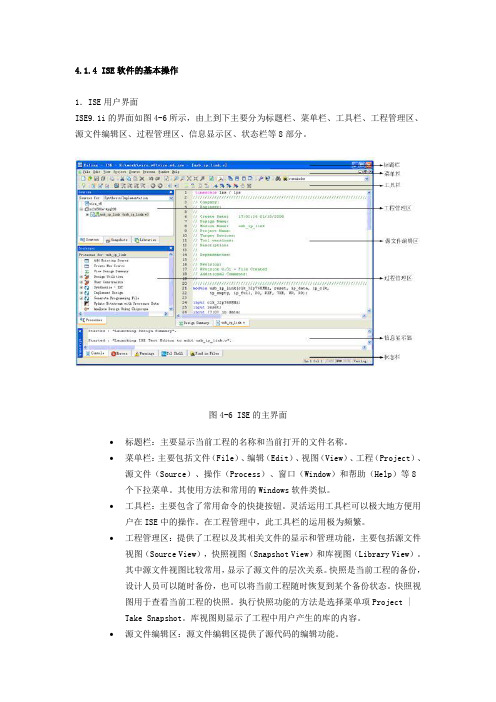

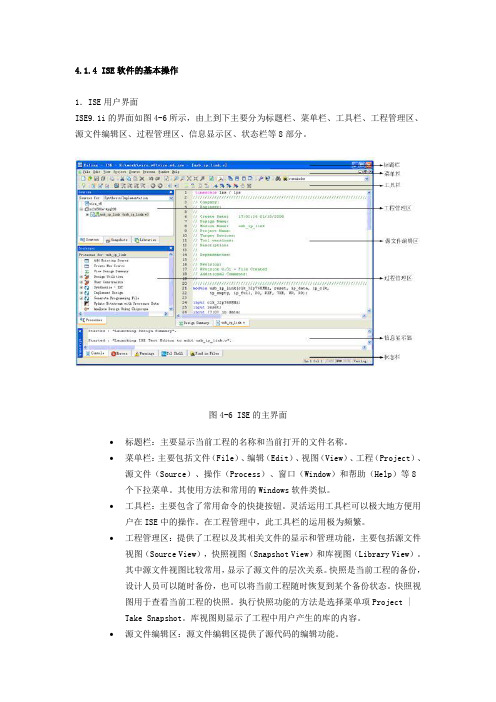

4.1.4 ISE软件的基本操作1.ISE用户界面ISE9.1i的界面如图4-6所示,由上到下主要分为标题栏、菜单栏、工具栏、工程管理区、源文件编辑区、过程管理区、信息显示区、状态栏等8部分。

图4-6 ISE的主界面∙标题栏:主要显示当前工程的名称和当前打开的文件名称。

∙菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、窗口(Window)和帮助(Help)等8个下拉菜单。

其使用方法和常用的Windows软件类似。

∙工具栏:主要包含了常用命令的快捷按钮。

灵活运用工具栏可以极大地方便用户在ISE中的操作。

在工程管理中,此工具栏的运用极为频繁。

∙工程管理区:提供了工程以及其相关文件的显示和管理功能,主要包括源文件视图(Source View),快照视图(Snapshot View)和库视图(Library View)。

其中源文件视图比较常用,显示了源文件的层次关系。

快照是当前工程的备份,设计人员可以随时备份,也可以将当前工程随时恢复到某个备份状态。

快照视图用于查看当前工程的快照。

执行快照功能的方法是选择菜单项Project |Take Snapshot。

库视图则显示了工程中用户产生的库的内容。

∙源文件编辑区:源文件编辑区提供了源代码的编辑功能。

∙过程管理区:本窗口显示的内容取决于工程管理区中所选定的文件。

相关操作和FPGA设计流程紧密相关,包括设计输入、综合、仿真、实现和生成配置文件等。

对某个文件进行了相应的处理后,在处理步骤的前面会出现一个图标来表示该步骤的状态。

∙信息显示区:显示ISE中的处理信息,如操作步骤信息、警告信息和错误信息等。

信息显示区的下脚有两个标签,分别对应控制台信息区(Console)和文件查找区(Find in Files)。

如果设计出现了警告和错误,双击信息显示区的警告和错误标志,就能自动切换到源代码出错的地方。

ISE14.7下创建一个Microblaze软核的流水灯和串口输出程序

ISE14.7下创建一个Microblaze软核的流水灯和串口输出程序使用硬件平台Xilinx Spartan6系列的FPGA,开发环境为ISE14.7。

废话少说,直接上图创建一个ISE工程,工程名字为UART_LED_TEST。

点击完成,完成工程的创建。

往工程中添加MICROBLAZE IP核

工程创建完成图。

点击完成后进入XPS,然后开始创建核

选择PLB system,我也不知道为什么?

按向导点击下一步。

给microblaze添加UART核

波特率可以根据自己情况修改,下面添加LED跑马灯

导出刚才创建的软核平台。

选择Export Only,仅仅只导出平台。

Console中显示Done!说明软核平台导出完成。

右键点击SYS_CPU,选择Add Copyof Source,添加约束文件。

选择SYS_CPU,双击GenerateTop HDL Source,创建顶层模块文件。

创建完成后,如下图。

双击Export Hardware Design To SDK With bitstream,编译刚才创建的软核平台。

此过程大约需要十几分钟。

编译完成后弹出如下对话框,选择SDK的工作目录。

创建一个SDK_Workspace文件夹,并选择该文件夹为SDK 的工作目录。

进入SDK主界面。

创建工程完成后的SDK界面图。

将FPGA上电,并接上USB下载线。

点击下图中标记的图标。

打完收功!。

ISE使用指南基础篇

ISE使⽤指南基础篇第4章ISE开发环境使⽤指南第1节ISE套件的介绍与安装4.1.1ISE简要介绍Xilinx是全球领先的可编程逻辑完整解决⽅案的供应商,研发、制造并销售应⽤范围⼴泛的⾼级集成电路、软件设计⼯具以及定义系统级功能的IP(Intellectual Property)核,长期以来⼀直推动着FPGA技术的发展。

Xilinx 的开发⼯具也在不断地升级,由早期的Foundation系列逐步发展到⽬前的ISE9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:包含了Xilinx新型SmartCompile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最⾼的性能,提供了⼀个功能强⼤的设计收敛环境;全⾯⽀持Virtex-5系列器件(业界⾸款65nm FPGA);集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;可以节省⼀个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界⾯友好、操作简单的特点,再加上Xilinx的FPGA芯⽚占有很⼤的市场,使其成为⾮常通⽤的FPGA⼯具软件。

ISE作为⾼效的EDA设计⼯具集合,与第三⽅软件扬长补短,使软件功能越来越强⼤,为⽤户提供了更加丰富的Xilinx平台。

4.1.2ISE功能简介ISE的主要功能包括设计输⼊、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其⼯作流程⽆需借助任何第三⽅EDA软件。

设计输⼊:ISE提供的设计输⼊⼯具包括⽤于HDL代码输⼊和查看报告的ISE⽂本编辑器(The ISE Text Editor),⽤于原理图编辑的⼯具ECS(The Engineering Capture System),⽤于⽣成IP Core的Core Generator,⽤于状态机设计的StateCAD以及⽤于约束⽂件编辑的Constraint Editor等。

综合:ISE的综合⼯具不但包含了Xilinx⾃⾝提供的综合⼯具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum 和Synplicity公司的Synplify,实现⽆缝链接。

熟悉ISE软件的使用方法

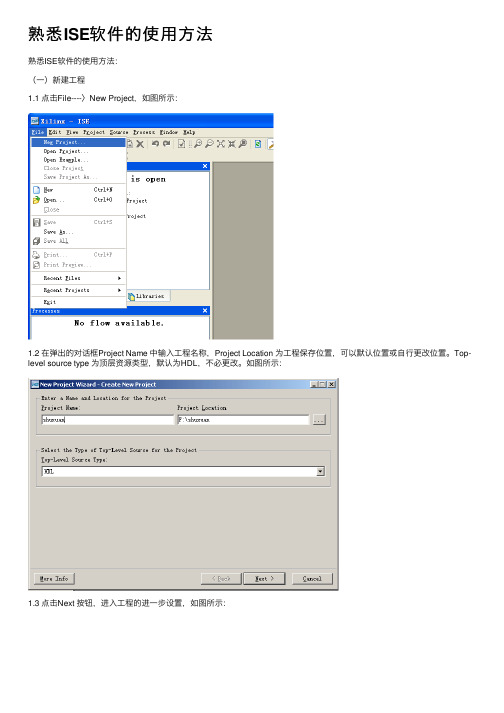

熟悉ISE软件的使⽤⽅法熟悉ISE软件的使⽤⽅法:(⼀)新建⼯程1.1 点击File----〉New Project,如图所⽰:1.2 在弹出的对话框Project Name 中输⼊⼯程名称,Project Location 为⼯程保存位置,可以默认位置或⾃⾏更改位置。

Top-level source type 为顶层资源类型,默认为HDL,不必更改。

如图所⽰:1.3 点击Next 按钮,进⼊⼯程的进⼀步设置,如图所⽰:选择器件家族(Family)、具体器件名称(Device)、封装形式(Package)、速度(Speed)、综合⼯具(默认就⾏)、仿真⼯具(Simulator)(默认使⽤ISE⾃带的仿真⼯具、也可以选择使⽤Modesim)。

1.4 设置完成点击Next,⼀路Next直到点击Finish。

(⼆)建⽴VHDL源程序2.1 新建⼯程后,在ISE软件左侧Source中的器件名上单击右键弹出对话框,如图所⽰:选择New Source。

2.2在弹出的对话框中选择VHDL Module,File Name中键⼊VHDL⽂件名称。

如图所⽰:Location 默认就⾏,⼀路点击Next完成新建VHDL模块。

2.3回到ISE环境,我们可以看到⼀个有待完成的VHDL程序,该程序已经包含了头⽂件,实体和结构体的定义,需要我们添加端⼝和结构体的具体实现。

也可以删除这些内容,拷贝已经写好的VHDL程序到其中,然后保存⽂件。

(⼆)VHDL程序的综合与仿真3.1 程序的综合双击ISE环境左侧Processes下的Implement design 中的Synthesize-XST,或右键点击再选择Run,如果程序没有错误则会综合通过,如果程序出错,可点击ISE环境左下的Errors进⾏查看。

如图所⽰:(三)引脚锁定与下载4.1 在ISE环境下,在左侧Source 下的Source for 中可以选择post-rout simulation 进⾏时序仿真,具体过程参考功能仿真。

ISE_Design_Flow_14.7

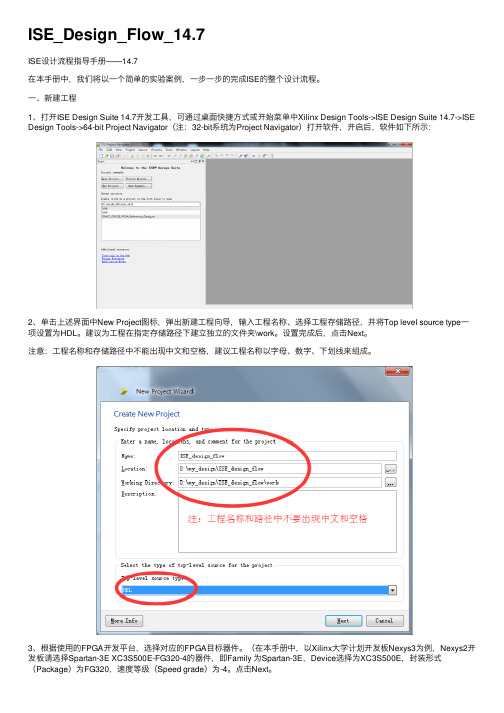

ISE_Design_Flow_14.7ISE设计流程指导⼿册——14.7在本⼿册中,我们将以⼀个简单的实验案例,⼀步⼀步的完成ISE的整个设计流程。

⼀、新建⼯程1、打开ISE Design Suite 14.7开发⼯具,可通过桌⾯快捷⽅式或开始菜单中Xilinx Design Tools->ISE Design Suite 14.7->ISE Design Tools->64-bit Project Navigator(注:32-bit系统为Project Navigator)打开软件,开启后,软件如下所⽰:2、单击上述界⾯中New Project图标,弹出新建⼯程向导,输⼊⼯程名称、选择⼯程存储路径,并将Top level source type⼀项设置为HDL。

建议为⼯程在指定存储路径下建⽴独⽴的⽂件夹\work。

设置完成后,点击Next。

注意:⼯程名称和存储路径中不能出现中⽂和空格,建议⼯程名称以字母、数字、下划线来组成。

3、根据使⽤的FPGA开发平台,选择对应的FPGA⽬标器件。

(在本⼿册中,以Xilinx⼤学计划开发板Nexys3为例,Nexys2开发板请选择Spartan-3E XC3S500E-FG320-4的器件,即Family 为Spartan-3E,Device选择为XC3S500E,封装形式(Package)为FG320,速度等级(Speed grade)为-4。

点击Next。

4、确认相关信息与设计所⽤的的FPGA器件信息是否⼀致,⼀致请点击Finish,不⼀致,请修改。

5、得到如下的空⽩ISE⼯程界⾯,完成空⽩⼯程新建。

⼆、设计⽂件输⼊1、如下图所⽰,点击New Source快捷图标,或在空⽩处右击选择New Source,或在File->NewSource选项,打开设计⽂件添加向导对话框。

2、选择Verilog Module,并输⼊设计⽂件名称如图所⽰,点击Next。

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

Xilinx ISE 使用入门手册

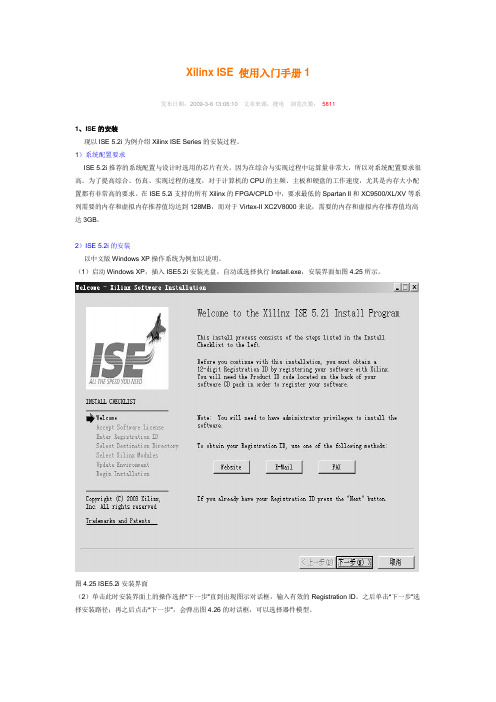

Xilinx ISE 使用入门手册1发布日期:2009-3-6 13:06:10文章来源:搜电浏览次数:58111、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

i se 14.7安装教程

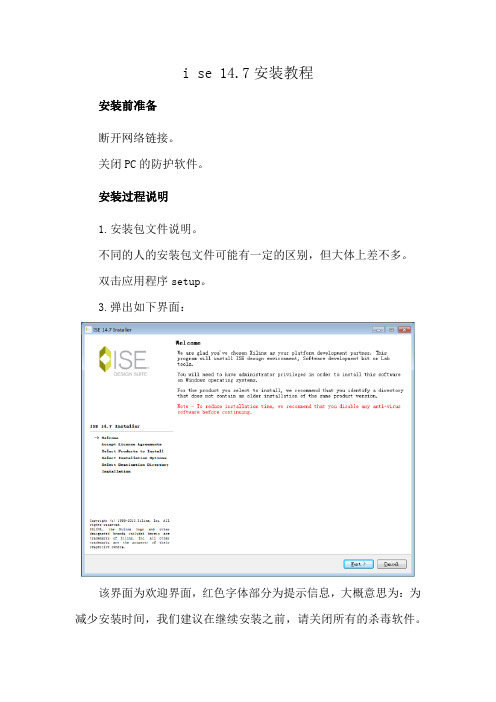

i se 14.7安装教程安装前准备断开网络链接。

关闭PC的防护软件。

安装过程说明1.安装包文件说明。

不同的人的安装包文件可能有一定的区别,但大体上差不多。

双击应用程序setup。

3.弹出如下界面:该界面为欢迎界面,红色字体部分为提示信息,大概意思为:为减少安装时间,我们建议在继续安装之前,请关闭所有的杀毒软件。

由于有些杀毒软件会误删系统文件,所以我们在安装时可以先把杀毒软件退出然后再安装,避免不必要的麻烦。

在一切准备就绪之后,点击下一步。

4.该界面显示的是软件的许可协议,总共两项,全部接受即可。

5.这个界面是选择需要安装的内容,大家安装时,选择自己需要的进行安装,这里勾选了ISE Design Suite System Edition。

在下面的详细介绍中,我们可以知道,这个选项中包含了ISE的逻辑编辑器,还有EDK和System Generator For DSP。

6.选择安装设置。

①第一个选项:使用多个CPU内核来加速安装速度②第二个选项:获取或管理许可证密钥。

③第三个选项:为以太网硬件协同仿真安装WinPCap。

④第四个选项:安装驱动。

⑤第五个选项:启用webtalk发软硬件的IP和设备使用情况,统计到XILINX。

这五项内容,大家根据自己需要进行勾选,这里我进行了全部选择。

7.选择安装路径。

在选择安装路径的时候,系统默认是安装在C 盘。

但是建议大家不要装在C盘,避免电脑卡顿。

如果大家要安装到其他盘。

只需要将C改为你想安装的盘即可,后面的路径不需要修改。

另外,安装时一定要确保安装路径里面没有中文。

8.这个界面显示了我们要安装的内容,直接点击INSTALL。

9.进入安装界面,等待安装即可。

10.点击NEXT。

11.继续点击Install。

12.界面提示,安装完成,点击Finish。

13.点击NEXT。

14.点击NEXT。

15.点击Finish。

16.安装WinPcap。

点击NEXT。

17.引导界面,点击NEXT。

ISE软件的基本操作

4.1.4 ISE软件的基本操作1.ISE用户界面ISE9.1i的界面如图4-6所示,由上到下主要分为标题栏、菜单栏、工具栏、工程管理区、源文件编辑区、过程管理区、信息显示区、状态栏等8部分。

图4-6 ISE的主界面∙标题栏:主要显示当前工程的名称和当前打开的文件名称。

∙菜单栏:主要包括文件(File)、编辑(Edit)、视图(View)、工程(Project)、源文件(Source)、操作(Process)、窗口(Window)和帮助(Help)等8个下拉菜单。

其使用方法和常用的Windows软件类似。

∙工具栏:主要包含了常用命令的快捷按钮。

灵活运用工具栏可以极大地方便用户在ISE中的操作。

在工程管理中,此工具栏的运用极为频繁。

∙工程管理区:提供了工程以及其相关文件的显示和管理功能,主要包括源文件视图(Source View),快照视图(Snapshot View)和库视图(Library View)。

其中源文件视图比较常用,显示了源文件的层次关系。

快照是当前工程的备份,设计人员可以随时备份,也可以将当前工程随时恢复到某个备份状态。

快照视图用于查看当前工程的快照。

执行快照功能的方法是选择菜单项Project |Take Snapshot。

库视图则显示了工程中用户产生的库的内容。

∙源文件编辑区:源文件编辑区提供了源代码的编辑功能。

∙过程管理区:本窗口显示的内容取决于工程管理区中所选定的文件。

相关操作和FPGA设计流程紧密相关,包括设计输入、综合、仿真、实现和生成配置文件等。

对某个文件进行了相应的处理后,在处理步骤的前面会出现一个图标来表示该步骤的状态。

∙信息显示区:显示ISE中的处理信息,如操作步骤信息、警告信息和错误信息等。

信息显示区的下脚有两个标签,分别对应控制台信息区(Console)和文件查找区(Find in Files)。

如果设计出现了警告和错误,双击信息显示区的警告和错误标志,就能自动切换到源代码出错的地方。

ISE14.7调试心得

ISE14.7调试心得第一次做软件一般都是从“hello world”开始的。

第一次做硬件一般都是从LED开始的。

先做个跑马灯,熟悉一下板子和xilinx芯片以及ISE软件的使用方法。

真是悲剧~写个跑马灯,我都感觉verilog HDL编程生疏了,出现了不少问题,在此记下,希望以后不要再范了。

不过,就拿如何写testbench来说,我是会了忘忘了学学了又不会了。

这次又复习了一遍。

真的希望以后可以将自己的知识和技能的基础打牢固。

不要再有那么多琐碎和烦心的事情。

第一个程序的错误:1、posedge clk and negedge rst_n应该写为posedge clk or negedge rst_n2、posedge clk or nedge rst_n应该写为posedge clk or negedge rst_n3、module LED8(input clk_100M;input rst_n;output [0:7] LED);应该定义为:module LED8(input clk_100M,input rst_n,output [0:7] LED);将端口定义包括类型定义一起放在module后的括号内的时候,之间用逗号隔开。

4、数组假设abc[0:7],单个元素写成abc[0]而不是abc(0)。

5、100MHz分频成1Hz。

计数为1042*1024*100(27'h640_0000)。

6、两种方式定义信号端口第一种:module LED8(clk_100M,rst_n,LED);input clk_100M;input rst_n;output [0:7] LED;reg [0:7] LED;reg [0:7] choose; //Choose the LED to highlightreg [0:26] count;没错误。

第二种:module LED8(input clk_100M,input rst_n,output [0:7] LED);reg [0:7] LED;reg [0:7] choose; //Choose the LED to highlightreg [0:26] count;提示错误:ISE软件是:ERROR:HDLCompilers:27 - "LED8.v" line 34 Illegal redeclaration of 'LED'Quartus软件是:Error (10759): Verilog HDL error at LED8.v(34): object LED declared in a list of port declarations cannot be redeclared within the module body。

ISE使用指南中

ISE使用指南中ISE(Intelligent Software Engineering)是一种经验丰富的工具,用于支持软件开发过程中的各个阶段。

本指南将介绍ISE的基本概念和使用方法,以帮助用户充分利用该工具。

1.ISE的概述2.安装与配置3.项目管理ISE提供了一个强大的项目管理功能,可以帮助用户组织和管理各个项目。

用户可以创建新项目、导入现有项目或从版本控制系统中检出项目。

在项目管理面板中,用户可以查看项目的文件结构和依赖关系,并进行文件的增删改查等操作。

5.调试器ISE的调试器功能可以帮助用户定位和修复代码中的错误。

用户可以设置断点、单步执行代码、观察变量值和查看函数调用栈等。

调试器还支持远程调试功能,可以在远程计算机上调试代码。

6.版本控制7.自动化构建ISE支持自动化构建功能,可以帮助用户自动执行一系列的构建步骤,如编译、打包、发布和部署等。

用户可以通过配置文件或命令行参数来定义构建步骤,并将其添加到项目的构建脚本中。

8.单元测试ISE支持单元测试框架,如JUnit和PyTest等。

用户可以编写和运行单元测试用例,并查看测试结果和覆盖率报告。

ISE还提供了代码覆盖率分析功能,可以帮助用户评估测试用例的覆盖率。

9.效能分析ISE提供了效能分析工具,可以帮助用户评估代码的效率和性能。

用户可以收集和分析代码的运行时间、内存占用和CPU使用情况等。

ISE还提供了图形化界面和报表,以便用户更好地理解和优化代码的性能。

10.文档生成ISE支持自动化文档生成功能,可以帮助用户生成代码的文档和注释。

用户可以使用特定的注释标记来标识代码的文档化部分,然后使用ISE提供的工具生成文档。

ISE支持多种文档格式,如HTML、Markdown和PDF等。

总之,ISE是一款功能强大的工具,可以帮助开发人员提高软件开发的效率和质量。

本指南提供了对ISE的基本介绍和使用方法,希望能对用户的工作有所帮助。

具体的使用细节和高级功能可以参考ISE的官方文档和用户手册。

xilinxise14.7破解版详细安装教程(含license许可文件)

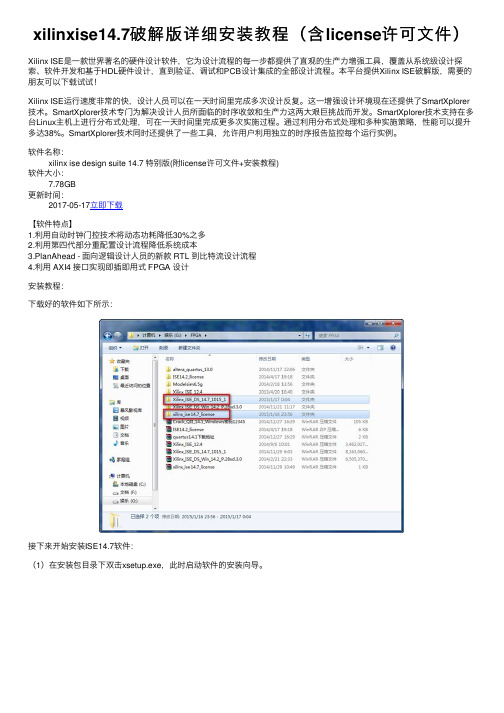

xilinxise14.7破解版详细安装教程(含license许可⽂件)Xilinx ISE是⼀款世界著名的硬件设计软件,它为设计流程的每⼀步都提供了直观的⽣产⼒增强⼯具,覆盖从系统级设计探索、软件开发和基于HDL硬件设计,直到验证、调试和PCB设计集成的全部设计流程。

本平台提供Xilinx ISE破解版,需要的朋友可以下载试试!Xilinx ISE运⾏速度⾮常的快,设计⼈员可以在⼀天时间⾥完成多次设计反复。

这⼀增强设计环境现在还提供了SmartXplorer 技术。

SmartXplorer技术专门为解决设计⼈员所⾯临的时序收敛和⽣产⼒这两⼤艰巨挑战⽽开发。

SmartXplorer技术⽀持在多台Linux主机上进⾏分布式处理,可在⼀天时间⾥完成更多次实施过程。

通过利⽤分布式处理和多种实施策略,性能可以提升多达38%。

SmartXplorer技术同时还提供了⼀些⼯具,允许⽤户利⽤独⽴的时序报告监控每个运⾏实例。

软件名称:xilinx ise design suite 14.7 特别版(附license许可⽂件+安装教程)软件⼤⼩:7.78GB更新时间:2017-05-17⽴即下载【软件特点】1.利⽤⾃动时钟门控技术将动态功耗降低30%之多2.利⽤第四代部分重配置设计流程降低系统成本3.PlanAhead - ⾯向逻辑设计⼈员的新款 RTL 到⽐特流设计流程4.利⽤ AXI4 接⼝实现即插即⽤式 FPGA 设计安装教程:下载好的软件如下所⽰:接下来开始安装ISE14.7软件:(1)在安装包⽬录下双击xsetup.exe,此时启动软件的安装向导。

这是安装欢迎界⾯,直接Next~~(2)选中复选框,表⽰接受条⽬(必选,否则⽆法进⾏下⼀步),Next~~(3)同样必须接受条⽬,Next~~(4)选择要安装的软件类型,根据⼤家需求进⾏选择,这⾥选“ISE Design Suite System Edition”,Next~~(5)什么都不做,直接Next~~(6)选择安装路径,根据⼤家磁盘情况进⾏设置,这⾥为C盘,Next~~(7)这是对前⾯的设置进⾏的总结页⾯,点“Install”进⾏安装。

ise的使用流程

ise的使用流程1. 简介ise是一款功能强大的集成电路设计软件,可以提供全面的工程设计解决方案。

以下是ise的使用流程。

2. 下载与安装•访问ise官方网站。

•在网站上找到并点击下载按钮。

•根据操作系统选择合适的版本进行下载。

•下载完成后,双击安装程序进行安装。

•按照安装向导的提示进行安装。

3. 打开ise•双击ise的图标以打开软件。

•在启动界面选择新建项目。

•输入项目名称并选择适当的存储路径。

•点击确定以创建项目。

4. 添加设计文件•在项目导航栏中,右键单击Design Sources。

•选择Add Sources。

•在弹出的对话框中选择适当的文件类型。

•点击下一步并选择要添加的设计文件。

•点击完成以将文件添加到项目中。

5. 设计功能模块•在项目导航栏中,右键单击设计文件。

•选择New Source。

•在弹出的对话框中选择设计模块类型。

•点击下一步并输入模块的名称。

•点击完成以创建模块。

6. 添加约束文件•在项目导航栏中,右键单击设计文件。

•选择New Source。

•在弹出的对话框中选择约束文件类型。

•点击下一步并输入约束文件的名称。

•点击完成以创建约束文件。

7. 综合与优化•在项目导航栏中,右键单击设计文件。

•选择Synthesize - XST。

•等待综合过程完成。

8. 实现与布局•在项目导航栏中,右键单击设计文件。

•选择Implement Design。

•等待实现与布局过程完成。

9. 模拟与仿真•在项目导航栏中,右键单击设计文件。

•选择Simulate - ModelSim。

•编写仿真脚本文件并保存。

•运行仿真脚本以进行模拟与仿真。

10. 下载与验证•连接目标板与计算机。

•在ise软件中,点击Generate Programming File。

•将生成的Bitstream文件下载到目标板中。

•验证设计功能正常运行。

11. 导出项目•在ise软件中,选择Export - Export Project。

ISE基本操作

1 在服务器linux下建立新用户,包括口令和密码。

2 安装exceed网络访问软件,按照提示进行安装。

设置服务器ip地址,192.168.1.883 通过进入进入,输入用户名和密码进入linux操作系统。

Terminal中输入/ISE/bin/GENESISe。

进入/ISE/bin/custom4 将师兄的文件考入自己建的目录下面(否则不能保存,软件问题),打开目录下面所需要的,进入。

点击右键,出现,选择Boundary。

进入mdraw 界面,绘制器件结构。

5首先选择绘制器件结构,选中是“坑”。

在中选择SiC材料,用画矩形,选中,再点击矩形的各个端点,输入坐标位置。

其中,坐标单位默认为um。

依次画出器件的其他部分结构,宽度对器件的性能的影响不大,不需要精确定位。

和调解大小。

使用中的zoom reset也可以达到效果。

(Mdraw中默认的是um 微米)6在中添加新的电极名(cathode,anode),框中存在的电极表示要添加的。

再点击按钮,在图中相应的位置点击下,添加接触。

删除不需要的部分。

Preferences调节相应的参数。

7选择掺杂。

点击(均匀掺杂),在窗口的区域里面划动鼠标,选取掺杂区域,在窗口里面,确定掺杂区域对角线端点坐标,掺杂种类和掺杂浓度。

依次对各个区域进行掺杂。

8划分网格。

点击,在窗口的某个区域里面划动鼠标,出现窗口。

由此,确定划分网格区域的对角坐标,网格划分的最大值和最小值,网格大小的划分直接影响结果的收敛性,所以要不断调整,(一般原则,网格的划分最大值一般取作全长的1/10,最小值取作最大值的一半)。

还要在中添加掺杂种类。

其中还有一点要注意,对于不规则图形,默认区域的网格划分也要设定。

默认区域是指最大的矩形。

在菜单里面选择选择默认区域,设置它的对角线坐标值应该是最大的区域,同时划分网格大小,在中添加掺杂种类点击ok。

点击键,可以查看网格划分和掺杂信息(掺杂点端点,网格点区域)。

FPGA and ISE14.7基础教程

IDE A COMPLETED PROJECT

PROJECT FILES—— (*.V)

模块开始和结束(figure 1) 变量声明(figure 2) 数据流语句 低层模块实例(figure3) 行为描述块 任务和函数

Figure 1

Figure 2

Figure 3

VERILOG STANDARD——PURPOSE

SIMULATION TOOL:ISIM

Graphite:PID_LED_CONTROL simulation

REFERENCE DOCUMENTS

Figure: LED control, from Graphite schematic

Figure: led behavior description, from Graphite FPGA spec.

Behavioral simulation Post-place & route static timing analysis Download and verify in circuit

Post-synthesis gate-level simulation and post-place & route timing simulations can be done for production sign off

SIMULATION TOOL:ISIM

Graphite:reset timing simulation

PROGRAM AND DEBUG —— COMPILE

Failed

successful

PROGRAM AND DEGUB —— START IMPACT

IMPACT——SELECT/ADD STORAGE DEVICE

Spartan-14.7平台与ISE软件的入门资料

Spartan-3平台与ISE软件的入门一、快速浏览Spartan-3E Starter Kit的用户指南,便于以后进行内容查找。

中文用户指南:Spartan-3E Starter Kit Board User Guide.mht英文用户指南:Spartan-3E Starter Kit Board User Guide.pdf二、ISE软件安装。

根据资料自学完成安装(在个人电脑上),ISE推荐版本:14.7。

注意需要破解(即提供license)。

三、ISE软件的初次使用。

在Spartan-3E开发板上,使用ISE软件,完成一个最基本工程的建立、编程、仿真、下载实现。

3.11)运行ISE Design Suite软件,界面如下2)新建工程(可参考图书:Xilinx FPGA开发实用教程)File New Projecta)设置顶层文件类型Top-level source type为Schematic(原理图)b)选择工程的保存位置Location和工作目录Working Directory为fpgaxunlianc)为工程取名,如:xunlian1点击Next进行下述设置根据观察我们使用的Spartan 3E开发板上的FPGA芯片上的字,可知目标FPGA芯片的属性如下芯片系列(Family):Spartan3E芯片型号(Device):XC3S500E芯片封装(Package):FG320速度等级(Speed):-4(注:XILINX的FPGA,值越大,速度等级越高)综合工具(Systhesis Tool)选择ISE自带的XST仿真工具(Simulator)选择ISE自带的Isim编程语言(Preferred Language)选择Verilog然后,点击Next观察,然后,点击Finish 3)在工程中加入文件右键点击“xc3s500e-4fg320”,执行“New Source”如上图,先建立一个原理的源文件,取名为Topsch,注意“Add to project”复选框需选中,然后点击Next观察,然后点击Finish,到此建立一张空白原理图。

ISE的使用说明

ISE的使用说明ISE是集成电路设计中常用的一种工具,是一种综合软件环境,它用于设计目的,例如创建和测试电路设计的逻辑模型。

本文将详细介绍ISE 的使用说明,包括安装步骤、主要功能、常用操作和调试技巧。

一、安装步骤2.运行安装程序:双击安装程序启动安装流程,按照提示完成安装向导。

3.设置安装选项:在安装向导中,您可以选择安装目录、添加快捷方式和其他个性化设置。

4.完成安装:等待安装程序完成所有必要文件的复制和配置,安装完成后重启计算机。

二、主要功能1.逻辑设计:ISE提供了丰富的逻辑设计工具,包括原理图设计、硬件描述语言编写和逻辑优化等功能。

用户可以通过拖放元件、连接线和逻辑门,创建电路的逻辑模型。

2.约束设置:ISE允许用户定义各种约束条件,如时钟频率、延迟限制和电气规范等。

这些约束条件对于确保设计的正确性和性能至关重要。

3.仿真和验证:ISE提供了强大的仿真和验证工具,以验证设计的功能和时序正确性。

用户可以模拟不同输入情况下的电路行为,并通过波形查看器等工具进行调试和分析。

4.综合和布局布线:ISE可以将逻辑设计综合为电路网表,并根据指定的目标器件和约束条件进行布局布线。

综合和布局布线的结果直接影响电路的性能和可靠性。

6.文档生成:ISE可以根据设计规范和用户的需求,自动生成各种设计文档,如用户手册、接口定义和设计报告等。

这些文档对于设计团队的交流和项目管理非常重要。

三、常用操作2.添加文件:在工程中,用户可以添加设计文件、约束文件和仿真文件等。

这些文件描述了电路的结构、约束条件和仿真模型,是设计的基础。

3.进行综合和优化:在添加文件后,用户需要对设计进行综合和优化,以便生成电路网表。

综合和优化的操作可以通过综合工具和约束文件完成。

4.进行布局布线:综合完成后,用户需要对设计进行布局布线,以生成具体的物理布局。

布局布线的操作可以通过布局布线工具和约束文件完成。

5.进行仿真和验证:在布局布线完成后,用户可以使用ISE提供的仿真和验证工具,对设计进行功能和时序验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Spartan-3平台与ISE软件的入门

一、快速浏览Spartan-3E Starter Kit的用户指南,便于以后进行内容查找。

中文用户指南:Spartan-3E Starter Kit Board User Guide.mht

英文用户指南:Spartan-3E Starter Kit Board User Guide.pdf

二、ISE软件安装。

根据资料自学完成安装(在个人电脑上),ISE推荐版本:14.7。

注意需要破解(即提供license)。

三、ISE软件的初次使用。

在Spartan-3E开发板上,使用ISE软件,完成一个最基本工程的建立、编程、仿真、下载实现。

3.1

1)运行ISE Design Suite软件,界面如下

2)新建工程(可参考图书:Xilinx FPGA开发实用教程)File New Project

a)设置顶层文件类型Top-level source type为Schematic(原理图)

b)选择工程的保存位置Location和工作目录Working Directory

为fpgaxunlian

c)为工程取名,如:xunlian1

点击Next

进行下述设置

根据观察我们使用的Spartan 3E开发板上的FPGA芯片上的字,可知目标FPGA芯片的属性如下

芯片系列(Family):Spartan3E

芯片型号(Device):XC3S500E

芯片封装(Package):FG320

速度等级(Speed):-4(注:XILINX的FPGA,值越大,速度等级越高)

综合工具(Systhesis Tool)选择ISE自带的XST

仿真工具(Simulator)选择ISE自带的Isim

编程语言(Preferred Language)选择Verilog

然后,点击Next

观察,然后,点击Finish 3)在工程中加入文件

右键点击“xc3s500e-4fg320”,执行“New Source”

如上图,先建立一个原理的源文件,取名为Topsch,注意“Add to project”复选框需选中,然后点击Next

观察,然后点击Finish,到此建立一张空白原理图。

4)使用原理图方式,实现简单功能如下:

a)LD7灯点亮

b)通过拨码开关控制LD6灯的亮或灭

c)将板上的50Mhz的时钟,二分频后输出到LD5

a)

在symbols子栏目下,在类型(Categories)中,选择General;然后从元件Symbols中,选择元件gnd,放置在原理图中

然后,点击Add→Wire,从gnd元件上引出一根导线

然后,点击Add→I/O Marker,在红色小方块处(电气连接点)点一下

双击XLXN_1,将网络名改成LD7,点击OK

双击LD7,在Nets中,点击New,新增属性,如下

点击OK,在点击OK

即,将LD7的输出端口的引脚锁定到芯片引脚F8上。

至此,完成将gnd信号输出到F8引脚的功能,即将LD7灯点亮(低电平点灯)。

b)

选择元件ibuf(位置为IO类别中),放置到原理图中

点击Add I/O Marker,分别在上图的两个电气连接出点击

更改输入端口的网络名称为SW3,更改输出端口的网络名称为LD6 双击SW3,

在Nets中,增加引脚锁定的设置。

即点击New

然后,输入上述信息,将SW3端口锁定到FPGA的引脚N17

点击OK,在点击OK

同样,双击LD6,增加引脚锁定设置,LOC=E9

至此,完成拨码开关控制LD6灯的功能。

c)

放入元件fd(位置在Flip_Flop类中),即一个D触发器

放入元件inv(位置在Logic类中),即一个反相器

对两个元件的位置进行适当调整

选中INV,执行Edit Mirror,将元件INV的放置方向调整一下,便于连线

进行连线,如下图

加上IO端口,如下图

更改端口名称,并锁定引脚

输入:XLXN_4,改为CLK50,LOC=C9

输出:XLXN_5,改为CLKOUT,LOC=D11 注:引脚D11对应LD5灯

原理图画完,注意保存。

5)执行综合,仿真,下载。

在Design子栏目下,选中Topsch

然后双击Systhesize-XST,进行综合。

Console窗口显示“Process "Synthesize - XST" completed successfully”,

即成功。

然后双击Implement Design,即执行

成功后。

然后进行仿真。

(仿真部分可以跳过不做,直接下载执行)首先需要增加一个用于仿真的test文件

与需要仿真验证的文件Topsch关联

生成初始的top_bench_v.v文件

// Verilog test fixture created from schematic D:\fpgaxunlian\xunlian1\Topsch.sch - Tue Jan 12 17:36:23 2016

`timescale 1ns / 1ps

module Topsch_Topsch_sch_tb();

// Inputs

reg SW3;

reg CLK50;

// Output

wire LD7;

wire LD6;

wire CLKOUT;

// Bidirs

// Instantiate the UUT

Topsch UUT (

.LD7(LD7),

.SW3(SW3),

.LD6(LD6),

.CLKOUT(CLKOUT),

.CLK50(CLK50)

修改top_bench_v.v的内容(增加蓝色的代码,实现输入信号控制)

#150;

SW3 = 0;

#200;

SW3 = 1;

end

always

begin

#10 CLK50 = ~CLK50;

end

endmodule

在Implementation和Simulation的选择框中,从当前的选中Implementation改为选中Simulation

选择后仿真Post-Route

右键点击Simulate Post-Place & Route Model,选择Run

点击按钮“Zoom to Full View”,观察仿真结果

下载

在Implementation和Simulation的选择框中,选中Implementatio 右键点击Generate Programming File,执行Run

右键点击Configure Target Device,执行Run

选中Boundary Scan,然后点击按钮“Initialize Chain”

选择Yes,执行FPGA芯片的下载文件的选择

选择到我们工程下对应的bit文件

接下来,提示选择开发板上PROM存储器的下载文件和CPLD的下载文件,均点击No

然后右键点击xc3s500e芯片,执行Program

显示编程成功,观察开发板效果

LD7等常亮,LD6灯可通过SW3开关,LD5等弱亮,示波器测试为25Mhz的信号。