频率计和占空比测量电路的设计

频率计与占空比

频率计和占空比测量电路的设计引言:随着科技的进步和发展,微处理器的性能逐渐提高,因此现在的频率计设计大部分是采用单片机来实现。

因为处理器的工作频率很高,所以测量精度很高,误差比较小。

但是由于采用单片机来实现的话还要软件的结合,因此对于编程能力较差的我采用纯硬件电路来实现。

占空比是脉冲信号的一个基本参数,不论在脉冲信号设计中,还是在脉冲信号的应用中,都需要知道脉冲的占空比,不同的应用情况对占空比的要求也不相同,因此准确快速地测量出脉冲占空比也就十分必要。

测量占空比的方法主要有示波器比较法,单片机计算法,平均值转换法等,示波器比较法简单易行,但不能直接准确快速的飞鼠读数,单片机法虽然直接准确的显示出数值,但需要软件硬件配合,设计比较麻烦;平均值转换法电路简单,但需要将脉冲信号转换成平均值电压再进行A/D转换,而其他的一些测量方法虽然能克服上述方法的缺点,但是具体测量应用时却受到一些限制,于是,本文提出了一种全数字式的调频计数测量法。

一.频率计设计思路:众所周知,频率就是周期的倒数,因此就是信号在单位时间内的脉冲数。

所以要测脉冲数必然要用到计数芯片,要显示脉冲数就要用到数码管,还有锁存和译码器。

又因为计数时间是一秒,所以555芯片来实现单稳态触发时间为一秒的触发信号。

二.芯片介绍:1.4518计数芯片-----------------功能图:2. 4511译码器功能图:三.功能模块1.触发信号模块2.4518计数模块3.4511锁存模块4.数码管显示模块5.信号控制输入模块补充:以上的电路是正对时钟信号的频率测量,对于正弦信号和三角波信号的测量,都可以把其转化为时钟信号后在测量即可。

四.整体模块图五.占空比测量电路设计对于占空比的测量,我想大家最先想到测量方式就是用示波器,这很简单但是不方便,比较流行的是用单片机的中断功能。

后通过软件编程即可实现,对于单片机外围电路设计比较简单,所以受到很多人都很青睐,但是还是那句老话对于编程能力较差的我只能通过纯硬件来实现。

基于FPGA数字频率计 (可测占空比)

VHDL 课程设计报告——基于FPGA的数字频率计姓名:学号:班级:目录1 设计原理 (1)2功能设计 (1)3系统总体框图 (1)4各功能块设计说明 (2)5实验结果 (14)6结论分析 (15)一、设计原理频计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。

通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1 s。

闸门时间可以根据需要取值,大于或小于1 s都可以。

闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长。

闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响。

一般取1 s作为闸门时间,此测量方法称为直接测频法。

由于闸门时间通常不是待测信号的整数倍,这种方法的计数值也会产生最大为±1个脉冲误差。

进一步分析测量准确度:设待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量相对误差为Tx/T=Tx=1/Fx。

由此可知直接测频法的测量准确度与信号的频率有关:当待测信号频率较高时,测量准确度也较高,反之测量准确度也较低。

二、功能设计1、测量范围:1HZ--------99MHZ,测量精度±1HZ。

2、测量结果高4位与低4位进行分页显示。

当超过9999HZ时,系统亮灯提示超出低4位显示范围,可通过按键进行高低4位结果的显示切换。

高4位显示时,伴有小数点位的点亮,提示已成功切换到高4位。

3、测量所测信号的占空比。

能够快速测出输入待测信号的占空比,并且通过按键,切换到占空比显示状态。

4、内置自测信号由内部时钟产生三个特定时钟,以供自身测试功能是否正常。

三、系统总体框图系统总框图四、各功能块设计说明1、时钟发生器通过对50MHZ的晶振时钟进行50M的分频,等到一个1HZ信号。

再通过此信号,通过2分频,得到一个0.5HZ的信号,从而得到高电平为1秒的闸门控制信号en来控制计数器的计数时间.再通过对en求反,等到锁存信号load.而清零信号clr则通过en与1HZ信号共同产生.同时对50MHZ信号进行500分频,一个两位的std_logic_vector(1 downto 0)信号在分频信号的驱动下不断加‘1’,等到“00”、“01”、“10”、“11”四种片选信号,对应4个数码管,从而驱动数码管的动态扫描显示。

有效值、频率、占空比测量电路

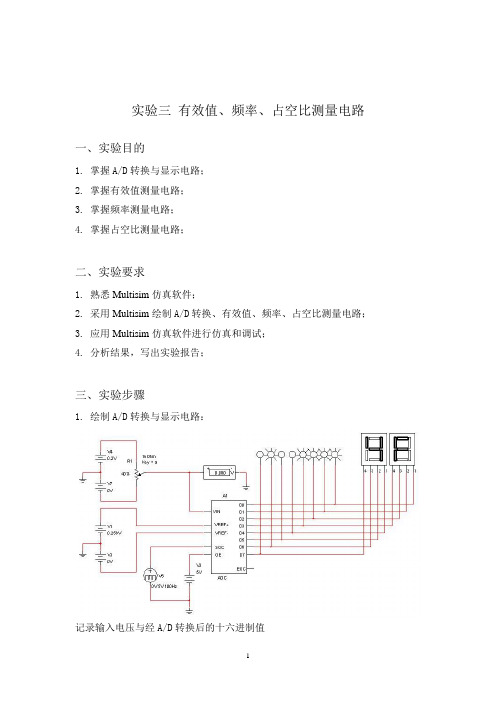

实验三有效值、频率、占空比测量电路一、实验目的1.掌握A/D转换与显示电路;2.掌握有效值测量电路;3.掌握频率测量电路;4.掌握占空比测量电路;二、实验要求1.熟悉Multisim仿真软件;2.采用Multisim绘制A/D转换、有效值、频率、占空比测量电路;3.应用Multisim仿真软件进行仿真和调试;4.分析结果,写出实验报告;三、实验步骤1.绘制A/D转换与显示电路:记录输入电压与经A/D转换后的十六进制值显示值(V) 0 0.05 0.1 0.15 0.2十六进制值00H 31H 63H 95H C7H2.有效值测量电路:设置输入正弦波频率为100Hz,幅值为141mV,调节Rp使输出电压直流为100mV,记录该Rp值。

频率(Hz) 50 100 200 400峰值(mV) 141 141 141 141直流显示(mV) 106.5 100 99.6 98.0误差% 23.9% 29.3% 29.5% 30.5%3.频率测量电路:采用“a” 减小可调电阻;“A”增加可调电阻,调整Rp使得f=20kHz时输出直流电压为200mV。

为缩短调试时间,可将R10电阻值降低,只要确保输出电压的直流平均值为200mV即可。

正弦波输入测试数据记录:输入频率50Hz 500 Hz 5kHz 20kHz输出直流电压0mv 5.9mv 49.3mv 198.7mv三角波输入测试数据记录:输入频率50Hz 500 Hz 5kHz 20kHz输出直流电压0mv 5.9mv 49.3mv 198.7mv矩形波输入测试数据记录:输入频率50Hz 500 Hz 5kHz 20kHz输出直流电压0mv 5.9mv 49.3mv 198.7mv4.占空比测量电路调整Rp使得输入频率为1kHz,幅度为4V,D=50%时输出直流电压为50mV。

输入频率(Hz)被测占空比D(%)10 20 40 50 60 80 9020 15mv 24mv 42mv 50mv 59mv 75mv 83mv 200 15mv 24mv 42mv 50mv 59mv 75mv 82mv 2k 15mv 24mv 42mv 50mv 59mv 75mv 83mv 20k 15mv 23mv 42mv 50mv 59mv 75mv 83mv200k 14mv 23mv 40mv 48mv 57mv 73mv 82mv 1M 13mv 15mv 33mv 41mv 50mv 66mv 76mv四、思考题:1. 分析A/D转换器电路工作原理。

FPGA频率计设计毕业设计(论文)

一、课程设计原理1、测频原理及误差分析本次课程设计采用直接测频法。

直接测频法就是在确定的闸门时间内,记录被测信号的脉冲个数。

这种方法的计数值也会产生最大为±1个脉冲误差。

进一步分析测量准确度。

设待测信号脉冲周期为T1,频率为F1,当闸门时间为T=1s 时,测量准确度为&=T1/T=1/F1。

由此可知直接测频法的测量准确度与信号的频率有关。

当待测信号频率较高时,测量准确度也较高,反之测量准确度也较低。

2、占空比测量原理占空比:占空比是指高电平在一个周期之内所占的时间比率。

方波的占空比为50%,占空比为0.5,说明正电平所占时间为0.5个周期。

在1S的闸门时间之内,只要我们利用50Mhz的时钟脉冲,对待测信号的高电平时间进行计数,得到一个num值。

最后num*20ns就是所求信号的占空比了。

二、系统的设计1、分频模块分频模块我们采用50Mhz的时钟频率产生待测的信号,和三个控制信号。

此程序要求将50Mhz分出1Mhz的频率,再产生1hz作为控制信号的标准输入时钟。

该模块产生的3个控制信号,分别为EN,LOAD,CLR。

CLR信号用于在每次测量开始时,对计数器进行复位,以清除上次测量的结果,该复位信号高电平有效。

EN为计数允许信号,在EN信号的上升沿时刻计数模块开始对输入信号的频率进行测量,在此1S时间里被测信号的脉冲数进行计数,即为信号的频率。

然后将值锁存,并送到数码管显示出来。

设置锁存器的好处是使显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

在每一次测量开始时,都必须重新对计数器清0。

另外,也设计出另外一个进程process,产生同样地三个控制信号给占空比测量时提供使能,锁存和清零的能力。

部分程序如下:process(clk)beginif clk'event and clk = '1' thentemp1<=temp1+1;end if;end process;freq<=temp1(16); --381Hz=50Mhz/2^172、计数模块计数模块分为2个子模块。

基于FPGA的数字频率计实验报告(能测占空比)

基于FPGA的数字频率计设计学院:专业:班级:姓名:学号:审阅老师:评分:目录一、课程设计目的 (3)二、设计任务 (3)三、功能要求与技术指标 (3)四、数字频率计工作原理概述 (3)五.数字频率计实现方法 (4)六.结论与误差分析 (11)七.VHDL程序: (12)一、课程设计目的熟悉EDA工具,掌握用VHDL语言进行数字系统设计的基本方法和流程,提高工程实践能力。

二、设计任务设计一数字频率计,用VHDL语言描述,用QuartusII工具编译和综合,并在实验板上实现。

三、功能要求与技术指标1.基本功能要求(1)能够测量出方波的频率,其范围50Hz~50KHz。

(2)要求测量的频率绝对误差±5Hz。

(3)将测量出的频率以十进制格式在实验板上的4个数码管上显示。

(4)测量响应时间小于等于10秒。

以上(1)~(4)基本功能要求均需实现。

2.发挥部分(1)提高测量频率范围,如10Hz~100KHz或更高、更低频率,提高频率的测量绝对值误差,如达到±1Hz。

(2)可以设置量程分档显示,如X1档(显示范围1Hz~9999Hz),X10档(显示范围0.001KHz~9.999KHz),X100档(显示范围0.100KHz~999.9KHz)...可以自定义各档位的范围。

量程选择可以通过按键选择,也可以通过程序自动选择量程。

(3)若是方波能够测量方波的占空比,并通过数码管显示。

以上(1)~(3)发挥功能可选择实现其中的若干项。

四、数字频率计工作原理概述1.数字频率计简介在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

而数字频率计是采用数字电路制成的实现对周期性变化信号的频率的测量。

2.常用频率测量方法:方案一采用周期法。

通过测量待测信号的周期并求其倒数,需要有标准倍的频率,在待测信号的一个周期内,记录标准频率的周期数,这种方法的计数值会产生最大为±1个脉冲误差,并且测试精度与计数器中记录的数值有关,为了保证测试精度,测周期法仅适用于低频信号的测量。

电子技术课程设计(数字频率计的设计)

一课程设计题目:数字频率计的设计二、功能要求(1)主要用于测量正弦波、矩形波、三角波和尖脉冲等周期信号的频率值。

(2)率范围:分四1Hz~999Hz、01kHz~9.99kHz、1kHz~99.9kHz、10~999KHZ(3)周期范围:1ms~1s。

(4)用3个发光二极管表示单位,分别对应3个高档位。

三频率计设计原理框图正弦波数字频率计原理框图1测试电路原理:在测试电路中设置一个闸门产生电路,用于产生脉冲宽度为1s 的闸门信号。

改闸门信号控制闸门电路的导通与开断。

让被测信号送入闸门电路,当1s闸门脉冲到来时闸门导通,被测信号通过闸门并到达后面的计数电路(计数电路用以计算被测输入信号的周期数),当1s闸门结束时,闸门再次关闭,此时计数器记录的周期个数为1s内被测信号的周期个数,即为被测信号的频率。

测量频率的误差与闸门信号的精度直接相关。

被测信号频率测量算法对应的方框图四、各部分电路及仿真1 整形电路部分整形电路的目的是将三角波、正弦波变成方便计数的脉冲信号。

整形电路可以直接用555定时器构成施密特触发。

本次设计采用555定时器,适当连接若干个电阻就可以构成触发器图1-1 整形电路将555定时器的THR和TR1两个输入端连在一起作为信号输入端,则可得到显示电路闸门产生输入电路闸门计数电路施密特触发器,为了提高其稳定性通常要在要在CON端口接入一个0.01uf左右的滤波电容。

但使用555定时器的时候输入的电压应该要大于5V,本次设计直接用信号源来做输入信号,并且信号源的振幅为10V,没有用放大电路将信号放大。

2 时基电路时基电路时用来控制闸门信号选通的时间,由于本次设计的频率计测试范围是0到999KHz,故时基信号要有1ms 10ms 100ms 1s,基于上述,还需要一个分频器分出不同的频率。

设计过程如下:可用一个多谐振电路产生频率为1KHz的脉冲信号(即T=1ms),然后使用分频器产生10ms 100ms 1s。

脉冲占空比测试仪制作_设计报告 精品

设计报告课题:脉冲占空比测试仪制作设计者:指导老师:日期:目录1.系统设计 (3)1.1设计要求 (3)1.1.1基本要求 (3)1.1.2发挥部分 (3)2.总体设计方案 (4)2.1设计思路 (4)2.2方案论证比较 (5)2.2.1锁相倍频产生的设计方案论证与选择 (5)2.2.2触发定时器设计方案论证与选择 (5)3.单元电路设计 (6)3.1.锁相倍频器 (6)3.1.1工作原理分析 (6)3.1.2电路参数计算 (7)3.2触发定时电路 (7)3.2.1工作原理分析 (7)3.2.2参数器件选取 (8)3.3计数储存电路 (8)3.3.1工作原理分析 (8)3.4译码驱动显示电路 (9)3.4.1工作原理分析 (9)3.4.2参数器件选取 (9)4.测试方法与数据 (10)4.1调试方法与问题 (10)4.1.1调试方法 (10)4.1.2调试的问题与解决方案 (10)4.2数据处理 (11)4.3数据测量图片记录 (11)4.3.1占空比测量 (12)4. 3.2 HCF4046相关波形记录 (14)4.3.3. 555定时器相关波形记录 (15)4.4 数据分析结果 (16)5.参考文献 (16)6.附录 (17)6.1芯片介绍 (17)6.1.1锁相环4046 (17)6.1.2计数器-74LS90 (18)6.2电路工作原理6.3电路PCB图 (20)6.4实物图正反面 (20)脉冲占空比测试仪摘要:介绍一种测量占空比方法,该电路主要由锁相环、100进制加法器、触发定时、锁存译码驱动和数码显示等组成。

由锁相环和100进制加法器组成倍频器,将倍频的脉冲经过另外一个100进制加法器统计正脉冲的频率个数储存在寄存器。

用触发定时器控制寄存器输出到译码器,再由译码器驱动数码管显示,显示的数据即为占空比。

该方法直接在电路上可以读出占空比,不必用专门仪器去测量。

关键词: 锁相环锁相倍频脉冲占空比1.系统设计1.1设计要求1.1.1基本要求(1)量程:0—99%,显示器最大显示数为 99(即99%),误差绝对值均小于1%;(2)分频率:1%;(3)被测信号频率范围:2Hz—5KHz;电源电压:+5V;(5)触发-定时电路的暂态时间由电阻R和电容C决定,其选值应保证数码管显示的读数不出现闪烁现象。

MHz等精度频率计设计基于VerilogHDL

姓名:郑中权班级:电子1班 数电课设报告江苏科技大学2017/10/12100MHz等精度频率计设计(基于Verilog HDL)一、设计要求:提供一个幅值为10mV ~ 1 V,频率为 1 ~ 100MHz的正弦信号,需测试以下指标:1.频率:测频范围 1Hz ~ 100MHz,测频精度为测频全域内相对误差恒为百万分之一。

2.占空比:测试精度 1% ~ 99%3.相位差:测试两个同频率的信号之间的相位差,测试范围 0 ~ 360二、设计分析使用FPGA数字信号处理方法,首先需要将正弦信号转换成可读取的数字方波信号,再经过FPGA设计计算得出所需测量值。

三、模电部分首先选择比较器,对于 100 MHz 信号,比较器灵敏度需要达到5ns内,TI公司的LTV3501灵敏度为4.5ns,符合要求由TLV3501数据手册得知:当频率低于 50MHz 的时候,正弦波的峰峰值需大于20mV,频率高于50MHz时,峰峰值需大于 1V。

然后需要选择放大器,当正弦波幅值为 10mV时,放大倍数需大于35。

方法通过二级放大,一级用OPA847放大20倍,二级用OPA675放大8倍,得到总放大倍数160的正弦波。

经转换后的输出电压符合TTL电平要求,可以被识别出0和1。

四、数电部分开发板:Cyclone IV E: EP4CE6E22C8板载时钟为 50MHz,带4个按键和一个复位键(按键按下为0,抬起为1),四个七段数码管(共阳),FPGA的引脚可由杜邦线引出。

设计思路:测量频率:输入一个100MHz的基准频率,由计数器CNT1来计算基准频率的上升沿个数,即周期数。

输入一个被测信号,它由计数器CNT2来测量周期数。

两个信号在同一个使能信号EN(使能信号时间为1~2s)下开始计数,计数完后,存储计数结果,由(CNT1 * 10)可以算出具体的计数时间(单位ns),再由((CNT1 * 10ns)/CNT2 )*10^9可算得被测信号频率,单位Hz。

基于51单片机的频率计的设计

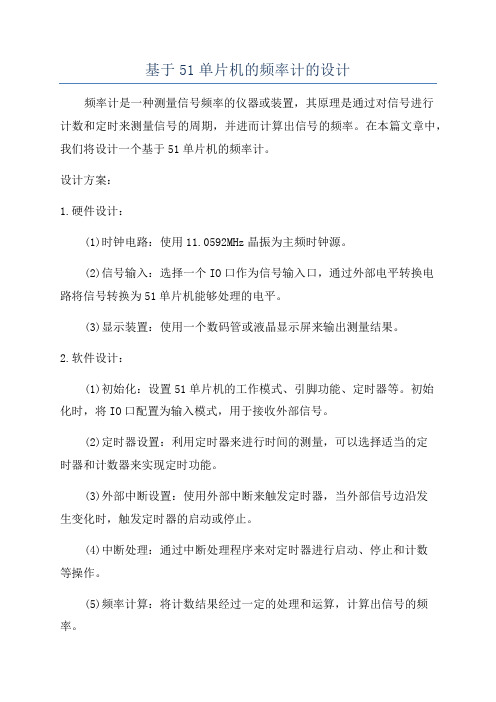

基于51单片机的频率计的设计频率计是一种测量信号频率的仪器或装置,其原理是通过对信号进行计数和定时来测量信号的周期,并进而计算出信号的频率。

在本篇文章中,我们将设计一个基于51单片机的频率计。

设计方案:1.硬件设计:(1)时钟电路:使用11.0592MHz晶振为主频时钟源。

(2)信号输入:选择一个IO口作为信号输入口,通过外部电平转换电路将信号转换为51单片机能够处理的电平。

(3)显示装置:使用一个数码管或液晶显示屏来输出测量结果。

2.软件设计:(1)初始化:设置51单片机的工作模式、引脚功能、定时器等。

初始化时,将IO口配置为输入模式,用于接收外部信号。

(2)定时器设置:利用定时器来进行时间的测量,可以选择适当的定时器和计数器来实现定时功能。

(3)外部中断设置:使用外部中断来触发定时器,当外部信号边沿发生变化时,触发定时器的启动或停止。

(4)中断处理:通过中断处理程序来对定时器进行启动、停止和计数等操作。

(5)频率计算:将计数结果经过一定的处理和运算,计算出信号的频率。

(6)结果显示:将计算得到的频率结果通过数码管或液晶显示屏输出。

3.工作流程:(1)初始化设置:对51单片机进行初始化设置,包括端口、定时器、中断等的配置。

(2)外部信号输入:通过外部电平转换电路将要测量的信号输入至51单片机的IO口。

(3)定时测量:当外部信号发生边沿变化时,触发外部中断,启动定时器进行定时测量。

(4)停止计时:当下一个信号边沿出现时,中断处理程序停止定时器,并将计数结果保存。

(5)频率计算:根据定时器的设置和计数结果,计算出信号的周期和频率。

(6)结果显示:将计算得到的频率结果通过数码管或液晶显示屏进行显示。

4.注意事项:(1)确保信号输入的稳定性:外部信号输入前需要经过滤波处理,保证稳定且无杂波的输入信号。

(2)测量精度的提高:如有必要,可以通过增加定时器的位数或扩大计数范围来提高测量精度。

(3)显示结果的优化:可以根据需要,通过增加缓冲区、优化数码管显示等方式来改善结果的可读性。

电子系统课程设计——简易频率计

河南科技大学课程设计说明书课程名称_现代电子系统课程设计__题目_简易数字频率计设计_学院__电子信息工程学院____班级__学生姓名_______指导教师______日期___2011年12月16日__课程设计任务书(指导教师填写)课程设计名称现代电子系统课程设计学生姓名专业班级设计题目简易数字频率计设计一、课程设计目的掌握高速AD的使用方法;掌握频率计的工作原理;掌握GW48_SOPC实验箱的使用方法;了解基于FPGA的电子系统的设计方法。

二、设计内容、技术条件和要求设计一个具有如下功能的简易频率计。

(1)基本要求:a.被测信号的频率范围为1~20kHz,用4位数码管显示数据。

b.测量结果直接用十进制数值显示。

c.被测信号可以是正弦波、三角波、方波,幅值1~3V不等。

d.具有超量程警告(可以用LED灯显示,也可以用蜂鸣器报警)。

e.当测量脉冲信号时,能显示其占空比(精度误差不大于1%)。

(2)发挥部分a.修改设计,实现自动切换量程。

b.构思方案,使整形时,以实现扩宽被测信号的幅值范围。

三、时间进度安排布置课题和讲解:1天查阅资料、设计:4天实验:3天撰写报告:2天四、主要参考文献何小艇《电子系统设计》浙江大学出版社2008.1潘松黄继业《EDA技术实用教程》科学出版社2006.10指导教师签字:2011年11月28日摘要频率计是数字电路中的一个典型应用,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,频率测量在科技研究和实际应用中的作用日益重要。

数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着复杂可编程逻辑器件(CPLD)的广泛应用,以EDA工具作为开发手段,运用VHDL语言。

将使整个系统大大简化。

提高整体的性能和可靠性。

在本文中,我们设计了一个简易数字频率计。

主要分为如下几个部分:●A/D模块:用VHDL语言写一个状态机,控制ADC0809芯片正常工作,使输入的被测模拟信号经过ADC0809芯片处理,转化为数字信号。

电路CAD课程设计之频率计

摘要在电子技术中,频率是最基本的参数,并且与许多电参量的测量方案,测量结果都有十分密切的关系,因此频率测量就显得更加重要。

测量频率的方法有很多种,其中数字计数器测量频率具有精度高、使用方便,测量迅速,以便于是先测量过程自动化等优点,是频率测量的重要手段之一。

数字计数器测频有两种方式:意识直接测频法,即在一定的闸门时间内测量被测信号的脉冲个数;而是间接测频法,如周期测频法。

直接测频法适用于高频信号的测量,简介测频法适用于低频信号的测量,本文叙述了间接测频即周期测频法测量频率的过程。

关键字:74ls160,555定时器,矩形波发生器。

Abstract: In electronic technology, frequency is the most basic parameters, and with many electric parameter measurement, measurement results are very close relationship, so frequency measurement is more important. Method of measuring frequency there are a lot of kinds, including electronic technology companies measure frequency has high precision, easy to use, measurement quickly, so that the first measurement process automation, etc, is one of the important means of frequency measurement. Consciousness of electronic counter measure frequency has two ways: direct frequency measuring method, namely, in a certain gate time measurement of the measured signal pulse number; But indirect frequency measurement method, such as the cycle frequency measuring method. Direct frequency measurement method is suitable for high frequency signal measurement, the introduction of frequency measurement method is suitable for low frequency signal measurement, this paper describes the indirect frequency measuring the cycle frequency measuring method to measure the frequency of process.一、设计任务和要求 (4)二、方案选择与论证 (4)2.1 系统原理框图[1]: (4)2.2 图1中各电路工作原理: (4)三、单元电路设计与计算说明 (4)3.1 25ms闸门时间控制电路 (4)(1)方案论证 (4)(2)闸门控制电路 (6)3.2 555定时器构成的施密特触发器电路 (7)(1)555定时器电路组成及引脚图 (7)(2)555的工作原理 (8)(3)555构成施密特触发器的主要原理 (8)3.3 计数显示电路 (9)3.4:电路,元件,芯片选择 (10)四、元器件选择及参数说明、总原理图 (10)4.1.电路工作说明及元件清单 (10)4.3总原理图 (11)五、总原理框图 (12)5.1 总PCB图 (12)5.2:新建元器件封装 (13)六、结论与心得 (14)七:参考文献 (14)一、设计任务和要求设计一个简易频率计,该频率计测量频率小于40kHz,要求测量数据显示3秒以上,被测信号为幅值小于10V的正弦波,输入信号可以为锯齿波,尖脉冲,三角波。

2015全国大学生电子设计大赛F题一等奖--数字频率计

2015 年全国大学生电子设计竞赛全国一等奖作品设计报告部分错误未修正,软件部分未添加竞赛选题:数字频率计(F 题)摘要本设计选用FPGA 作为数据处理与系统控制的核心,制作了一款超高精度的数字频率计,其优点在于采用了自动增益控制电路(AGC)和等精度测量法,全部电路使用P CB 制版,进一步减小误差。

AGC 电路可将不同频率、不同幅度的待测信号,放大至基本相同的幅度,且高于后级滞回比较器的窗口电压,有效解决了待测信号输入电压变化大、频率范围广的问题。

频率等参数的测量采用闸门时间为1s 的等精度测量法。

闸门时间与待测信号同步,避免了对被测信号计数所产生±1 个字的误差,有效提高了系统精度。

经过实测,本设计达到了赛题基本部分和发挥部分的全部指标,并在部分指标上远超赛题发挥部分要求。

关键词:FPGA 自动增益控制等精度测量法目录摘要 (1)目录 (2)1. 系统方案 (3)1.1. 方案比较与选择 (3)宽带通道放大器 (3)正弦波整形电路 (3)主控电路 (3)参数测量方案 (4)1.2. 方案描述 (4)2. 电路设计 (4)2.1. 宽带通道放大器分析 (4)2.2. 正弦波整形电路 (5)3. 软件设计 (6)4. 测试方案与测试结果 (6)4.1. 测试仪器 (6)4.2. 测试方案及数据 (7)频率测试 (7)时间间隔测量 (7)占空比测量 (8)4.3. 测试结论 (9)参考文献 (9)1. 系统方案1.1. 方案比较与选择宽带通道放大器方案一:OPA690 固定增益直接放大。

由于待测信号频率范围广,电压范围大,所以选用宽带运算放大器 OPA690,5V 双电源供电,对所有待测信号进行较大倍数的固定增益。

对于输入的正弦波信号,经过 OPA690 的固定增益,小信号得到放大,大信号削顶失真,所以均可达到后级滞回比较器电路的窗口电压。

方案二:基于 VCA810 的自动增益控制(AGC)。

毕业设计:基于单片机的频率计设计

毕业设计〔论文〕题目:基于单片机的频率计设计学生姓名:廖承润学号:学部〔系〕:信息学部专业年级:光信1班指导教师:赵真职称或学位:副教授2015年5 月20 日目录目录 (I)摘要....................................................... I II ABSTRACT....................................................... I V 第一章绪论. (1)1.1频率计概述 (1)1.2频率计发展现状及研究概况 (1)1.3本课题研究背景及主要研究意义 (2)数字频率计的种类 (2)第二章数字频率计的结构设计 (4)控制电路 (4)2.2单片机部分 (5)2.3数据显示电路 (6)2.4软件设计流程图 (9)第三章频率测量原理 (10)3.1测量频率的原理 (10)3.2直接测频法 (10)第四章系统设计 (11)4.1功能实现 (11)4.2硬件部分设计 (11)4.2.1 信号放大电路 (11)4.2.2 单片机AT89C52 (12)4.2.3 测量数据显示电路 (13)4.3硬件电路工作过程 (14)4.3.1 直接测频法的工作流程 (15)第五章数字频率计的设计与仿真 (17)电路的设计 (17)电路设计的内容和方法 (17)电路设计的步骤 (18)5.2数字频率计的仿真 (19)第六章减小误差措施及扩展方面 (23)减小误差措施 (23)扩展方面 (23)6.3功能上的完善 (24)6.3.1 增加键盘控制 (24)6.3.2 实现自动量程转换 (24)6.3.3 液晶显示器〔LCD〕进行数据的显示 (24)结论 (25)参考文献 (26)致谢 (27)附录 (28)1硬件设计原理图: (28)2数字频率计测量频率程序: (29)基于单片机的频率计设计摘要本文提出设计数字频率计的方案,重点介绍以单片机AT89C52为控制核心,实现频率测量的数字频率设计。

如何设计一个简单的频率计

如何设计一个简单的频率计频率计是一种用于测量信号频率的设备,广泛应用于电子、通信、自动化等领域。

本文将介绍如何设计一个简单的频率计,并提供相关原理和步骤。

一、简介频率计是一种测量频率的仪器。

它可以通过测量信号周期的时间来计算频率。

频率计可以根据测量的频率范围和精度要求,选择不同的设计方案。

下面将介绍一种简单的频率计设计。

二、设计原理该频率计设计基于计数器原理。

其思想是通过计数已知时间内信号周期的脉冲数来确定频率。

三、所需元器件1. 计数器芯片:选择适合频率范围的计数器芯片。

2. 晶振:提供稳定的时钟信号作为计数器的时基。

3. 预处理电路:用于处理输入信号,确保其满足计数器的输入要求。

四、设计步骤1. 确定测量范围和精度要求:根据应用需求确定频率计所需要测量的频率范围和精度要求,选择合适的计数器芯片。

2. 选择计数器芯片和晶振:根据测量范围和精度要求,选择适合的计数器芯片和晶振。

计数器芯片的型号选择要能满足测量范围,并具有足够的计数位数。

晶振的频率要足够稳定。

3. 设计输入信号预处理电路:根据计数器芯片的输入要求,设计合适的输入信号预处理电路。

例如,如果输入信号幅值过大或过小,需要进行合适的电平转换或调整。

五、连接设计1. 将输入信号接入预处理电路,确保信号满足计数器芯片的输入要求。

2. 将预处理后的信号接入计数器芯片的计数端。

3. 将晶振连接至计数器芯片的时钟输入端。

4. 连接供电电源,确保设计正常工作。

六、测试与调试1. 给设计供电,确保所有连接正确。

2. 输入已知频率的信号,观察频率计是否能准确测量。

3. 如果测量结果不准确,检查元器件连接是否正确、晶振频率是否稳定等。

4. 根据实际情况调整设计参数,直至测量结果满足要求。

七、注意事项1. 设计中要注意信号的幅值范围和频率范围。

2. 选择合适的计数器芯片和晶振,以保证测量精度和稳定性。

3. 调试时要注意设计的连通性和元器件的正确连接。

八、总结设计一个简单的频率计需要确定测量范围和精度要求,选择适合的计数器芯片和晶振,并设计合适的输入信号预处理电路。

课程设计 频率计的设计

学生姓名(学号) )课程名称数字电子技术设计题目数字频率计设计完成期限自 2009 年 6 月 24至 2009 年 6月 30 共 1 周设计依据已学过电路分析、模拟电子技术、数字电子技术,按照教学计划要求进行《数字电子技术课程设计》。

设计要求及主要内容1、设计一个3位十进制频率计,其测量范围为1MHz。

量程分为10KHz、100KHz、1MHz三档(最大读数分别为9.99KHz、99.9KHz、999KHz),量程转换规则如下:(1)当读数大于999时,频率计处于超量程状态,此时显示器发出溢出指示。

下一次测量时,量程自动增大一档。

(2)当读数小于099时,频率计处于欠量程状态,下一次测量时,量程自动减小一档。

2、显示方式如下:(1) 采用记忆显示方式。

即计数过程中不显示数据,等到计数过程结束以后,显示计数结果,并将此计数结果保持到下一次计数结束。

显示时间不小于1s。

(2) 小数点位置随量程变换自动移位。

3、对电路进行仿真。

参考资料[1]MAXPLUSII 及 VHDL 使用教程.东南大学[2]康华光.电子技术基础数字部分.高等教育出版社.指导教师签字日期目录一、设计任务 (4)二、设计条件 (4)三、设计要求 (4)四、总体概要设计 (4)五、各单元模块设计和分析 (5)六、元器件清单 (7)七、设计总结 (7)八、参考文献 (7)九、附数字钟课程设计仿真图 (8)十、实验心得 (9)引言:数字频率计是用数字显示被测信号频率的仪器,被测信号可以是正弦波、方波或其它周期性变化的信号。

如配以适当的传感器,可以对多种物理量进行测试,比如机械振动的频率、转速、声音的频率以及产品的计件等等。

因此,数字频率计是一种应用很广泛的仪器。

一、设计任务:频率计设计二、设计条件:本设计基于Multisim仿真软件的调试三、设计要求:1、设计一个3位十进制频率计,其测量范围为1MHz。

量程分为10KHz、100KHz、1MHz三档(最大读数分别为9.99KHz、99.9KHz、999KHz),量程转换规则如下:(1)当读数大于999时,频率计处于超量程状态,此时显示器发出溢出指示。

CCP模块设计频率计C语言 详解

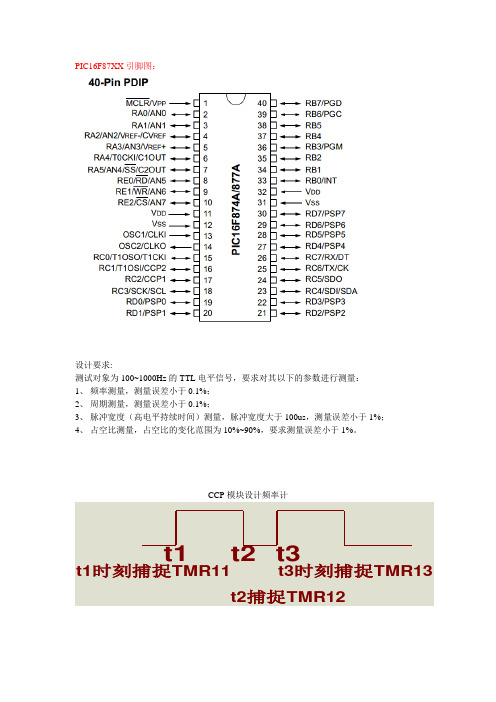

PIC16F87XX引脚图:设计要求:测试对象为100~1000Hz的TTL电平信号,要求对其以下的参数进行测量:1、频率测量,测量误差小于0.1%;2、周期测量,测量误差小于0.1%;3、脉冲宽度(高电平持续时间)测量,脉冲宽度大于100us,测量误差小于1%;4、占空比测量,占空比的变化范围为10%~90%,要求测量误差小于1%。

t1t2t3t3时刻捕捉TMR13 t1时刻捕捉TMR11t2捕捉TMR12t1时刻以前,把CCP1设置成捕捉上升沿;当上升沿到来时,CCP中断,捕捉此时TMR1寄存器中16位的值TMR11,把CCP1再设置成捕捉下降沿,当t2下降沿到来时,CCP中断,捕捉此时TMR1寄存器中16位的值TMR12,把CCP1再设置成捕捉上升沿,当t3时刻下降沿到来时,CCP中断,捕捉此时TMR1寄存器中16位的值TMR13。

则:信号的周期T=TMR13—TMR11 us脉冲宽度Tp=TMR12—TMR11 us信号的频率f= 1/T占空比D=Tp/T *100%如何提高测量频率•特别注意:•2次中断的时间间隔必须大于一次中断服务的执行时间;•如需要测量的最高频率为1000HZ,周期时1000us,且占空比的变化范围是10%--90%,则高电平持续的最短时间是:100us。

可以由充分的中断服务时间。

•如果实际应用中发现两次捕捉中断的时间间隔小于中断服务时间,则可以设置CCP1CON的值,时CCP模块每4个脉冲上升沿捕捉1次,或16个脉冲捕捉一次•要么把被测信号进行分频。

本例要求测试4种参数,并且可以利用按键选择显示其中任何1种,设定S9为加1键、S11为减1键、S10为确定键、S12为功能键。

按下S9键时,程序中得一个寄存器COUNTER 可以从1连续或点动步进的加到4;同理按下减1键时,COUNTER从4减到1,并把COUNTER值显示在LED上。

不同的COUNTER值对应不同的测试参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

频率计和占空比测量

引言:

随着科技的进步和发展,微处理器的性能逐渐提高,因此现在的频率计设计大部分是采用单片机来实现。

因为处理器的工作频率很高,所以测量精度很高,误差比较小。

但是由于采用单片机来实现的话还要软件的结合,因此对于编程能力较差的我采用纯硬件电路来实现。

占空比是脉冲信号的一个基本参数,不论在脉冲信号设计中,还是在脉冲信号的应用中,都需要知道脉冲的占空比,不同的应用情况对占空比的要求也不相同,因此准确快速地测量出脉冲占空比也就十分必要。

测量占空比的方法主要有示波器比较法,单片机计算法,平均值转换法等,示波器比较法简单易行,但不能直接准确快速的飞鼠读数,单片机法虽然直接准确的显示出数值,但需要软件硬件配合,设计比较麻烦;平均值转换法电路简单,但需要将脉冲信号转换成平均值电压再进行A/D转换,而其他的一些测量方法虽然能克服上述方法的缺点,但是具体测量应用时却受到一些限制,于是,本文提出了一种全数字式的调频计数测量法。

一.频率计设计思路:

众所周知,频率就是周期的倒数,因此就是信号在单位时间内的脉冲数。

所以要测脉冲数必然要用到计数芯片,要显示脉冲数就要用到数码管,还有锁存和译码器。

又因为计数时间是一秒,所以555芯片来实现单稳态触发时间为一秒的触发信号。

二.芯片介绍:

1.4518计数芯片-----------------功能图:

2. 4511译码器

功能图:

三.功能模块

1.触发信号模块

2.4518计数模块

3.4511锁存模块

4.数码管显示模块

5.信号控制输入模块

补充:

以上的电路是正对时钟信号的频率测量,对于正弦信号和三角波信号的测量,都可以把其转化为时钟信号后在测量即可。

四.整体模块图

五.占空比测量电路设计

对于占空比的测量,我想大家最先想到测量方式就是用示波器,这很简单但是不方便,比较流行的是用单片机的中断功能。

后通过软件编程即可实现,对于单片机外围电路设计比较简单,所以受到很多人都很青睐,但是还是那句老话对于编程能力较差的我只能通过纯硬件来实现。

六.设计思路

我们知道占空比就是信号正脉宽除以周期即:

D=T1/T (其中T1为正脉宽的时间,T为信号周期) 因此只要信号通过相应的处理即可变成正脉宽为T的信号,后利用一个基准信号使得其在正脉宽为T的时间下产生脉冲数100,在正脉宽为T1的时间产生脉宽数为M,此时M即为D。

七.芯片介绍:

双JK触发器 74109

芯片图:

功能图:

(其他用到的芯片上面都有叙述)

八.功能模块

1.信号处理模块

2.信号控制模块

(计数模块和数码管显示模块和上面一样)九.整体模块图

十.实验数据

1).频率计测量结果分析

根据以上测量原理和设计方案,在电路仿真proteus中进行电路搭建,经过过仿真验证测量电路能够按照预先设计的方案进行对信号的频率测量,在0~99999的频率信号作用下,其数码管上显示出的计数值分别为如下表所示:

2).占空比测量

对于信号占空比的测量,也是在proteus仿真中进行,经过仿真验证测量电路能够按照预先设定的方案对脉冲信号占空比进行测量,油信号源在1Hz~10kHz,幅度为5v,脉冲上升时间和脉冲下降时间均为1ns,占空比为1%~99%进行抽样测量,调节频率可调振荡测量数据如

下表所示:

3)误差分析:

1.给定的待测信号其占空比本身就存在一定误差

2.仿真是得到计数脉冲信号是由待测信号与测量高频脉冲信号通过

与门进行相与操作得到,有时会在计数脉冲序列两端形成1个或者2个附加信号的尖脉冲信号,使计数值稍微变大。

3.门电路的传输延时等所带来的测量电路的固有误差。

十一.总结

对于频率计的设计我个人认为准确度比较高,一般误差不会超过0.005,唯一的缺点就是倘若要测高频的话要等到时间比较长,不会像理想效果就是直接显示,没有计数过程。

而占空比电路的设计我觉得精度也是可以保证就是测量不方便,首先视觉效果不好,低频还好,如果是高频的话基准信号的频率比较难调,不知道计数何时能达到100,所以不太可行。

还有就是操作比较麻烦,你还要去调才能测,这样给使用者带来很大不便。