ARM汇编指令机器码举例详解

3.Arm机器码

3.Arm机器码3.Arm机器码⾸先汇编程序转化为机器码,才能在机器内运⾏。

⾸先我们对上⾯的裸机的代码中⽣的.elf⽂件进⾏反汇编:start.elf: file format elf32-littlearmDisassembly of section .text:50008000 <_start>:.text.global _start_start:@ldr和str的操作mov r0,#0xff50008000: e3a000ff mov r0, #255 ; 0xffstr r0,[r1]50008004: e5810000 str r0, [r1]ldr r2,[r1]50008008: e5912000 ldr r2, [r1]@程序状态字寄存器访问mrs r0,cpsr5000800c: e10f0000 mrs r0, CPSRorr r0,#0b10050008010: e3800004 orr r0, r0, #4 ; 0x4msr cpsr,r050008014: e129f000 msr CPSR_fc, r0@ror:循环右移mov r1,#0b1150008018: e3a01003 mov r1, #3 ; 0x3mov r1,r1,ror#15000801c: e1a010e1 ror r1, r1, #1@lsl:左移mov r1,#0b1150008020: e3a01003 mov r1, #3 ; 0x3mov r1,r1,lsl#250008024: e1a01101 lsl r1, r1, #2@bl指令:带链接跳转bl func150008028: eb000005 bl 50008044 <func1>@b指令:mov r1,#65000802c: e3a01006 mov r1, #6 ; 0x6mov r2,#750008030: e3a02007 mov r2, #7 ; 0x7cmp r1,r250008034: e1510002 cmp r1, r2bgt branch1@gt表⽰⼤于的时候跳转50008038: ca000003 bgt 5000804c <branch1> add r3,r1,r25000803c: e0813002 add r3, r1, r2b end50008040: ea000002 b 50008050 <end>50008044 <func1>:func1:mov r1,#2350008044: e3a01017 mov r1, #23 ; 0x17mov pc,lr@函数的返回,固定格式。

ARM指令机器码学习

ARM指令机器码学习以前,死活看不懂这个DLL 文件的16 进制(其实是二进制,为了好看,以16 进制ASCII 码显示),对一些高手使用IDA 反汇编流口水,今天终于轮到俺上场了。

现在来看看这个指令通常的编码格式这个貌似和英文原版不一样,现在来看看ARM Architecture Reference Manual 里面的格式还是以这个为准安全点。

现在看看这个最高四位的con 到底是怎么决定的。

上面这些条件都是可选的,ARM 都有固定的指令。

下面看看无条件指令。

在ARMv4 架构中任何带条件域0b1111 的都是不可预测的。

看了那么多,现在来举个例子吧。

以branch 指令为例子引用驱动调试助手作者的成果,并解释验证Foxit Reader V1.1 for WinCE6.0 今天终于整理清了PXA270 上的WinCE6.0,为了方便给客户演示WinCE6.0 的强大,定制了一个增强型的操作系统。

但WinCE6.0 中已经不支持PDF 等阅读器了。

于是从网站上找了一个PPC 版的Foxit Reader,把它放到WinCE6.0 的设备上面运行,竟然提示OS 不支持,只能在PPC 上面跑。

看到这个提示有些失望,但也有一丝希望。

这个提示似乎是Foxit Reader 运行时的提示框,与一般的不是有效的Windows CE 应用程序是不一样的。

既然这样,那说明程序还是运行起来了,只是检测OS 时出错,所以才会出现如下图所示的提示。

想一想,如果让程序跳过检测OS,是不是就可以正常运行呢。

满怀着希望,用IDA 反汇编了这个程序,并找到了对应的函数调用。

显而易见,0x000182b4 处是有条件的调用,如果改成绝对调用loc_0_182D0,按理就不会出现那个提示框了,修改方法就是将BEQ 改为B。

用UltraEdit 将上面的0A 改为EA,即将BEQ 改成B,再拷贝到设备上面去,果然可以运行现在我们解释这个B 和BEQ 机器码指令这个本来这BEQ,这个con 由EQ 决定,按照上面的知识,应该是0b0000,所以高八位为0x0A,现在改成B 绝对跳转,这样con。

ARM的汇编指令讲解

汇编知识点的要求:1、能看的懂2、可以做修改3、不需要用汇编直接编写程序汇编代码的应用场合:1、ARM的启动代码必须要汇编,如:uboot最开始初始化硬件的代码2、内核在最开始初始化的位置。

一、ARM汇编指令的编码格式1、编码格式ARM汇编指令编译成机器码以后,机器码的长度是32bits,这32bits的编码有一个固定的格式。

不同ARM 汇编指令,编码格式不同。

2、举例C:if(a==10)a++;elsea--;汇编1:CMP R0, #10;ADDEQ R0,R0,#1SUBNE R0,R0,#1汇编2SUBS R1, R0, #10; //S ---运算的结果会影响条件码标志位:CPSR:NZCVADDEQ R0,R0,#1SUBNE R0,R0,#1提示:空指令NOP,实际上是占用CPU的时间,但是执行后,没有什么意义。

NOP ---- MOV R0,R03、条件码标识10 -10Z = 1C = 0N = 0V = 0=================================================================================二、ARM的寻址方式1、立即数寻址操作数,有立即数。

ADD R0,R0,#1MOV R1,#10ORR R1,R1,#0xf @ R1=R1 | 0xfBIC R1,R1,#0xf @R1 = R1&(~(0xf))错误:ADD R1,#1,#2注意:立即数合法的条件在ARM汇编指令中,并不是所有的立即数,立即数是有一定的限制的。

什么样的立即数是合法的???1、如果一个立即数是小于256的(即该立即数是8bits以内的,0~255),该立即数是合法的。

2、如果一个立即数是大于等于256,该立即数经过循环左移偶数位,可以得到一个小于256的数,则该立即数合法。

256 = 0x100 ------→左移20位0x10000000----→左移4 0x1 合法0x111 非法0x102 非法0x104 合法0xfff0xff000x120000x4500000xab原因:在数据处理指令编码的时候,立即数用12bits来表示:高4bits:循环左移左移偶数位除以2低8bits:循环左移后的结果。

arm汇编逻辑指令 -回复

arm汇编逻辑指令-回复ARM汇编逻辑指令ARM汇编逻辑指令是一种基于RISC(Reduced Instruction Set Computing)的指令集架构,在数字电子设备中被广泛使用。

逻辑指令主要用于实现基本的逻辑操作,例如布尔运算、比较和分支跳转等。

本文将深入探讨ARM汇编逻辑指令的各个方面,包括指令格式、操作数和指令示例等。

一、指令格式ARM汇编逻辑指令的指令格式通常包括操作码、目标寄存器和操作数等字段。

下面是一个典型的ARM汇编逻辑指令的格式:<操作码>{xx}{cond} <目标寄存器>, <操作数1>, <操作数2>其中,操作码用于指定具体的逻辑操作,xx字段用于指定操作的类型(例如AND、OR或XOR等),cond字段用于指定条件执行的条件码,目标寄存器用于存储运算结果,操作数1和操作数2分别是参与运算的操作数。

二、操作数ARM汇编逻辑指令的操作数可以是寄存器或立即数。

寄存器是存储在CPU内部的高速存储器单元,用于存储临时数据。

ARM架构通常提供了16个通用寄存器(R0-R15),其中R0-R7用于存储一般性目的数据,R8-R15用于存储特殊用途数据。

立即数是直接写在指令中的常数值,通常用于表示较小的数据。

立即数的宽度取决于具体的指令和操作码。

例如,对于AND指令,立即数可以是8位或32位的。

三、指令示例以下是一些常见的ARM汇编逻辑指令示例:1. AND指令AND指令用于将两个操作数逐位进行与运算,并将结果存储在目标寄存器中。

例如,下面的指令将执行R1 = R2 AND 3:AND R1, R2, 32. OR指令OR指令用于将两个操作数逐位进行或运算,并将结果存储在目标寄存器中。

例如,下面的指令将执行R1 = R2 OR R3:ORR R1, R2, R33. XOR指令XOR指令用于将两个操作数逐位进行异或运算,并将结果存储在目标寄存器中。

第8章 ARM汇编指令

23/95

算术运算指令

指令格式

ADD{cond}{S} Rd,Rn,operand2 SUB{cond}{S} Rd,Rn,operand2 RSB{cond}{S} Rd,Rn,operand2

说明 加法 减法 逆向减法 带进位加法 带进位减法

201611293095加载存储指令指令格式说明操作ldrcondrdaddressing加载字数据rdaddressing注意addressing的寻址方式及索引方式ldrcondtrdaddressing以用户模式加载字数据ldrcondbtrdaddressing以用户模式加载无符号字节ldrcondbrdaddressing加载无符号字节数据ldrcondhrdaddressing加载无符号半字数据ldrcondsbrdaddressing加载有符号字节数据ldrcondshrdaddressing加载有符号半字数据ldrconddrdaddressing加载双字数据strcondrdaddressing存储字数据addressingrd注意addressing的寻址方式及索引方式strcondtrdaddressing以用户模式存储字数据strcondbrdaddressing存储字节数据strcondbtrdaddressing以用户模式存储字节数据strcondhrdaddressing存储半字数据strconddrdaddressing存储双字数据符号数加载时用符号扩展到32位否则用零扩展到32位

14/95

1. 操作数存放在内存单元中; 2.指令地址码字段给出 {寄存器编号(名)列表}; 3.编号高的寄存器总是对应内存中的高地址单元; 4. 可完成存储块和16个寄存器或其子集之间的数据传送。 LDMIA

(Increase After)

ARM中常用的汇编指令

ARM 中常⽤的汇编指令1 处理器内部数据传输指令MSR & MRS⽤于在状态寄存器和通⽤寄存器之间传送数据MRS: 状态寄存器到通⽤寄存器的传送指令。

({R0-R12} <== CPSR,SPSR)MSR: 通⽤寄存器到状态寄存器的传送指令。

MRS:(CPSR,SPSR==>{R0-R12})MOVMOV 指令⽤于将数据从⼀个寄存器拷贝到另外⼀个寄存器,或者将⼀个⽴即数传递到寄存器⾥⾯,使⽤⽰例如下:2 存储器访问指令ARM 不能直接访问存储器,⽐如 RAM 中的数据,⼀般先将要配置的值写⼊到 Rx(x=0~12)寄存器中,然后借助存储器访问指令将 Rx 中的数据写⼊到寄存器中。

指令描述LDR Rd, [Rn , #offset]从存储器 Rn+offset 的位置读取数据存放到 Rd 中STR Rd, [Rn, #offset]将 Rd 中的数据写⼊到存储器中的 Rn+offset 位置LDR 指令LDR 主要⽤于从存储加载数据到寄存器 Rx 中, LDR 也可以将⼀个⽴即数加载到寄存器 Rx中, LDR 加载⽴即数的时候要使⽤“=”,⽽不是“#”。

在嵌⼊式开发中, LDR 最常⽤的就是读取 CPU 的寄存器值。

上述代码就是读取寄存器中的值,读取到的寄存器值保存在 R1 寄存器中,上⾯代码中 offset 是 0,也就是没有⽤到 offset。

STR 指令LDR 是从存储器读取数据, STR 就是将数据写⼊到存储器中LDR 和 STR 都是按照字进⾏读取和写⼊的,也就是操作的 32 位数据,如果要按照字节、半字进⾏操作的话可以在指令“LDR”后⾯加上B 或 H,⽐如按字节操作的指令就是 LDRB 和STRB,按半字操作的指令就是 LDRH 和 STRH。

MRS R0, CPSR @ 将特殊寄存器 CPSR ⾥⾯的数据传递给 R0,即R0=CPSR1MSR CPSR , R0 @ 将 R0 中的数据复制到 CPSR 中,即 CPSR =R01MOV R0, R1 @ 将寄存器 R1 中的数据传递给 R0,即 R0=R1MOV R0, #0X12 @ 将⽴即数 0X12 传递给 R0 寄存器,即 R0=0X1212LDR R0, =0X0209C004 @ 将寄存器地址 0X0209C004 加载到 R0 中,即 R0=0X0209C004LDR R1, [R0] @ 读取地址 0X0209C004 中的数据到 R1 寄存器中12LDR R0, =0X0209C004 @ 将寄存器地址 0X0209C004 加载到 R0 中,即 R0=0X0209C004LDR R1, =0X20000002 @ R1 保存要写⼊到寄存器的值,即R1=0X20000002STR R1, [R0] @ 将 R1 中的值写⼊到 R0 中所保存的地址中1233 压栈和出栈指令我们通常会在 A 函数中调⽤ B 函数,当 B 函数执⾏完以后再回到 A 函数继续执⾏。

ARM汇编指令集

ARM汇编指令集1 跳转指令1.1 跳转指令B:B LABLE ;跳转到标号LABEL处B 0X1111 ;跳转到绝对地址0X1111处1.2 带连接的跳转指令BL:START …BL NEXT ;跳转到标号NEXT处,同时保存当前PC到R14中…;返回地址…NEXT…;子程序入口MOV PC,R14 ;返回1.3 带状态切换的跳转指令BX:MOV R0, #0X0201BX R0 ;程序跳转到0x0200处,微处理器切换到Thumb状态(地址必须是4的倍数,否则产生不可预知的后果)2算术运算指令2.1不带进位加法指令ADDADD R0, R1, R2 ;R0←(R1)+(R2)ADD R0, R1, #112 ;R0←(R1)+ 112ADD R0, R1, R2, LSL #1 ;R0←(R1)+(R2<<1) ;将R2中的值左移1位,再与R1值相加,结果送R02.2带进位加法指令ADCADDS R0, R3, R6 ;加最低位字节,不带进位ADCS R1, R4, R7 ;加第二个字,带进位ADCS R2, R5,R8 ;加第三个字,带进位;三句话实现了96bit加法运算,由于ARM寄存器宽度只有32bit所以分三次相加2.3 不带进位减法指令SUB ;S—进位标志SUB R0, R1, R2 ;R0←(R1)- (R2)SUB R0, R1, #112 ;R0←(R1)- 112SUB R0, R1 ,R2 LSL#1 ;R0←(R1)- (R2<<1)2.4 带进位减法指令SBCSUBS R0, R3, R6 ;减最低位字节,不带进位SBCS R1, R4, R7 ;减第二个字,带进位SBCS R2, R5, R8 ;减第三个字,带进位;三句话实现了96bit减法运算,由于ARM寄存器宽度只有32bit所以分三次相减2.5 不带进位逆向减法指令RSBRSB R0, R1, R2 ;R0←(R2)- (R1)RSB R0, R1, #112 ;R0←112- (R1)RSB R0, R1, R2, LSL#1 ;R0←(R2<<1)-R12.6 带进位逆向减法指令RSCRSBS R0, R6, R3 ;减最低字节的字,不带进位RSCS R1, R7, R4 ;减第二个字,带进位RSCS R2, R8, R5 ;减第三个字,带进位;三句话实现了96bit减法运算,由于ARM寄存器宽度只有32bit所以分三次相减2.732位乘法指令MULMUL R0, R1, R2 ;R0←(R1) X(R2)MULS R0, R1, R2 ;R0←(R1) X(R2) ;更新CPSR标志位2.8乘-累加指令MLAMLA R0, R1, R2, R3 ;R0←(R1) X(R2)+(R3)MLAS R0, R1, R2, R3 ;R0←(R1) X(R2)+(R3) ;更新CPSR标志位2.9 无符号数长乘指令UMULLMOV R5, #0X01MOV R8, #0X02UMULL R0, R1, R5, R8 ;(R1) (R0)←(R5)X(R8);UMULL指令实现64bit无符号数乘法2.10无符号长乘-累加指令 UMLALMOV R0, #0X01MOV R1, #0X02MOV R5, #0X01MOV R8, #0X02UMLAL R0, R1, R5, R8 ;R0←(R0) +(R5)X(R8)低字节;R1←(R1) +(R5) X(R8)高字节;UMLAL 指令为64位无符号乘-累加指令2.11有符号长乘指令SMULLMOV R5, #0X01MOV R8, #0X02SMULL R0, R1, R5, R8 ;(R1) (R0)←(R5)X(R8);SMULL指令实现64bit有符号数乘法2.12 有符号长乘-累加指令 SMLALMOV R0, #0X01MOV R1, #0X02MOV R5, #0X01MOV R8, #0X02SMLAL R0, R1, R5, R8 ;R0←(R0) +(R5)X(R8)低字节;R1←(R1) +(R5) X(R8)高字节; SMLAL 指令为64位有符号乘-累加指令2.13 比较指令 CMPCMP R1, #0X10 ;比较BGT TAG ;R1> #0X10转到TAG标号处……2.14负数比较指令 CMNCMN R0, #1 ;判断R0中的值是否为1的补码,是则置标志位Z为13逻辑运算指令3.1“与”指令 ANDMOV R0, 0XFFAND R0, R0, #3 ;取出R0的最低2bit3.2“或”指令 ORRMOV R0, 0XFFORR R0, R0, #33.3“异或”指令 EORMOV R0, 0XFFEOR R0, R0, #3 ;R0←(R0)^(0X03)3.4位清除指令 BICMOV R0, 0XFFBIC R0, R0, #B11 ;寄存器R0的低2bit被清零3.5测试比较指令 TSTTST R1, #b11 ;测试寄存器R1中的第0位和第1位,更新CPSR中标志位,应用中会在TST指令后加一条跳转指令。

ARM汇编指令机器码举例详解

ARM汇编指令机器码举例详解

ARM7内核采用的是RISC精简指令集,所有的ARM指令都是32bits的,在这32bits里既包含了指令的指令码,也包含了指令需要运算的数据,以MOV 指令为例,通过MOV指令的32bits可以识别出这是一个MOV指令,又可以在这32bits里找到源寄存器和目的寄存器。

我们来看一下MOV指令的机器

码格式:

28~31bits(cond)是条件码,就是表明这条语句里是否有大于、等于、非零等的条件判断,这4bits共有16种状态,分别为:

表 1 汇编语言条件码

指令与条件码可以有多种组合,比如MOV指令可以有MOV、MOVEQ、MOVLT等多种形式。

前面我们说过状态寄存器里有NZCV的状态标志,

当执行一条指令时,芯片就会将这条指令的条件码与状态寄存器中的状态标志做比较,如果状态寄存器中的状态标志满足这条指令的条件码时,则执行这条语句,如果不满足则不执行这条指令。

状态寄存器中的状态标志是受某些指令影响的,因此在使用有条件码的

指令进行判断前,必然会有其它指令配合使用,先修改状态寄存器中的状态标志。

汇编语言转换成机器码

汇编语言转换成机器码

将汇编语言转换成机器码的过程称为汇编。

在汇编过程中,汇编器(assembler)将汇编语言代码转换成机器语言代码,也就是二进制代码。

这个过程通常涉及到指令集架构(ISA),它是计算机硬件和软件之间的接口。

汇编语言通常用助记符(mnemonics)表示指令,而不是直接使用二进制代码。

例如,助记符"ADD" 代表加法操作,"MOV" 代表数据移动等。

汇编器将这些助记符转换成对应的二进制机器码。

以下是一个简单的例子,展示了如何将汇编代码转换成机器码:

假设我们有一个简单的汇编指令"MOV R1, #10"。

这条指令表示将数字10加载到寄存器R1中。

如果我们使用ARM架构的汇编器和指令集,这个指令可以被转换为以下的二进制机器码:

```assembly

MOV R1, #10

```

对应的二进制机器码为:

```bash

32'h0A908F66

```

这是两条ARM指令的组合:

`32'h0A` 是"MOV" 指令的机器码,表示数据移动操作。

`32'h90` 是立即数(#10)的机器码表示。

在ARM架构中,立即数被加载到寄存器中。

`32'h8F` 是目标寄存器R1的机器码表示。

`32'h66` 是指令后缀,表示这是一个条件执行指令。

请注意,实际的二进制机器码可能会根据具体的汇编器、目标架构和指令集有所不同。

ARM指令集详解--汇编

ARM指令集详解--汇编1. 汇编1.1. 通⽤通⽤寄存器37个寄存器,31个通⽤寄存器,6个状态寄存器,R13指针sp,R14返回指针,R15为PC指针, cpsr_c代表的是这32位中的低8位,也就是控制位CPSR有4个8位区域:标志域(F)、状态域(S)、扩展域(X)、控制域(C)MSR - Load specified fields of the CPSR or SPSR with an immediate constant, orfrom the contents of a general-purpose register. Syntax: MSR{cond} _, #immed_8rMSR{cond} _, Rm where: cond is an optional condition code. is either CPSR orSPSR. specifies the field or fields to be moved. can be one or more of: ccontrol field mask byte (PSR[7:0]) x extension field mask byte (PSR[15:8]) sstatus field mask byte (PSR[23:16) f flags field mask byte (PSR[31:24]).immed_8r is an expression evaluating to a numeric constant. The constant mustcorrespond to an 8-bit pattern rotated by an even number of bits within a32-bit word. Rm is the source register.C 控制域屏蔽字节(psr[7:0])X 扩展域屏蔽字节(psr[15:8])S 状态域屏蔽字节(psr[23:16])F 标志域屏蔽字节(psr[31:24])CPSR寄存器FIQ和IRQ的区别?MODE(以下为⼆进制)10000⽤户模式PC,CPSR,R0~R1410001FIQ PC,CPSR,SPSR_fiq,R14_fiq~R8_fiq,R7~R010010IRQ PC,CPSR,SPSR_irq,R14_irq~R13_irq,R12~R010011管理模式(svc)PC,CPSR,SPSR_svc,R14_svc~R13_svc,R12~R010111终⽌模式PC,CPSR,SPSR_abt,R14_abt~R13_abt,R12~R011011未定义PC,CPSR,SPSR_und,R14_und~R13_und,R2~R011111系统模式(sys)PC,CPSR,R14 ~R01.2. 指令格式1) 基本格式<opcode>{<cond>}{S} <Rd>,<Rn>{,<opcode2>}其中,<>内的项是必须的,{}内的项是可选的,如<opcode>是指令助记符,是必须的,⽽{<cond>}为指令执⾏条件,是可选的,如果不写则使⽤默认条件AL(⽆条件执⾏)。

arm跳转指令机器码

arm跳转指令机器码ARM是一种广泛应用于嵌入式系统的指令集架构,其跳转指令用于实现程序的跳转和分支控制。

本文将详细介绍ARM跳转指令的机器码表示及其功能。

ARM跳转指令一般由条件码(Condition Code)和目标地址(Target Address)组成。

条件码用于指定跳转的条件,目标地址则指明了跳转的目的地。

不同的条件码可以根据特定的条件来判断是否进行跳转,从而实现程序的流程控制。

ARM跳转指令的机器码由32位二进制数表示,其中前4位用于表示条件码,后28位用于表示目标地址。

条件码共有16种,分别对应不同的条件判断方式,例如等于、不等于、大于、小于等。

下面以一条典型的ARM跳转指令机器码为例进行分析,假设该指令的机器码为0xEA000001。

解析该机器码,前4位0xEA表示跳转指令,而剩下的28位00000001则表示跳转的目标地址。

在ARM汇编语言中,0xEA对应的是B指令,用于实现无条件跳转。

跳转的目标地址是相对于当前指令的偏移量,即跳转到当前指令地址加上目标地址所表示的偏移量的位置。

因此,0xEA000001表示跳转到当前指令地址加上1个字节的位置。

除了无条件跳转外,ARM还提供了其他各种条件码,用于实现有条件的跳转。

例如,条件码0x0A表示等于时跳转,0x1A表示不等于时跳转,0x4A表示大于时跳转等。

这样,我们可以根据特定的条件来决定是否进行跳转,从而实现程序的分支控制。

在实际应用中,ARM跳转指令经常与其他指令结合使用,实现复杂的控制流程。

例如,可以使用B指令进行条件判断,若满足条件则跳转到目标地址,否则继续执行下一条指令。

这样可以灵活地控制程序的执行流程,实现各种功能。

总结一下,ARM跳转指令的机器码由条件码和目标地址组成,用于实现程序的跳转和分支控制。

条件码用于判断是否进行跳转,目标地址指明了跳转的目的地。

通过灵活使用跳转指令,可以实现复杂的控制流程,提高程序的灵活性和可扩展性。

ARM指令集详解(超详细!带实例!)

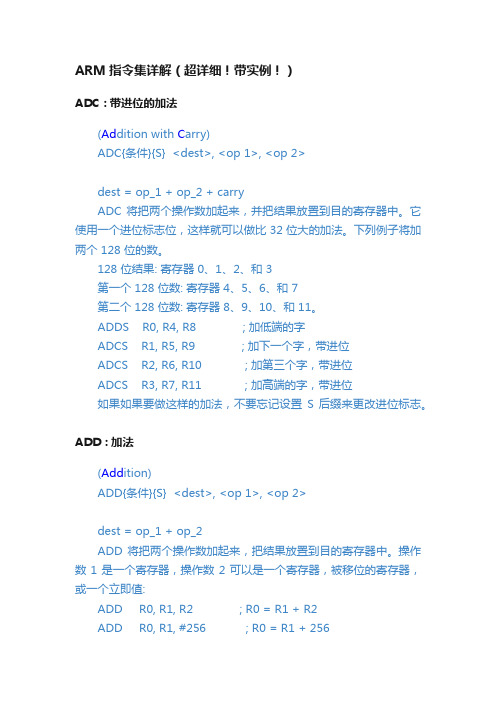

ARM指令集详解(超详细!带实例!)ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到目的寄存器中。

它使用一个进位标志位,这样就可以做比 32 位大的加法。

下列例子将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第一个 128 位数: 寄存器 4、5、6、和 7第二个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下一个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加高端的字,带进位如果如果要做这样的加法,不要忘记设置S 后缀来更改进位标志。

ADD : 加法(Add ition)ADD{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2ADD 将把两个操作数加起来,把结果放置到目的寄存器中。

操作数 1 是一个寄存器,操作数 2 可以是一个寄存器,被移位的寄存器,或一个立即值:ADD R0, R1, R2 ; R0 = R1 + R2ADD R0, R1, #256 ; R0 = R1 + 256ADD R0, R2, R3,LSL#1 ; R0 = R2 + (R3 << 1)加法可以在有符号和无符号数上进行。

AND : 逻辑与(logical AND)AND{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 AND op_2AND 将在两个操作数上进行逻辑与,把结果放置到目的寄存器中;对屏蔽你要在上面工作的位很有用。

arm 32 常见汇编指令 对应的机器码

arm 32 常见汇编指令对应的机器码

ARM 32位汇编指令是一种用于ARM架构的低级编程语言,它将人类可读的汇编指令转换为机器码,从而实现对计算机硬件的直接控制。

以下是几个常见的ARM 32位汇编指令及其对应的机器码:

1. MOV指令:将一个数据从一个位置复制到另一个位置。

机器码:0xMOV Rd, Rn

2. ADD指令:将两个数据相加并将结果存储在目标寄存器中。

机器码:0xADD Rd, Rn, Rm

3. SUB指令:将两个数据相减并将结果存储在目标寄存器中。

机器码:0xSUB Rd, Rn, Rm

4. CMP指令:比较两个数据的大小,并根据比较结果设置条件代码。

机器码:0xCMP Rn, Rm

5. LDR指令:从内存中加载数据到寄存器中。

机器码:0xLDR Rd, [Rn, #offset]

6. STR指令:将寄存器中的数据存储到内存中。

机器码:0xSTR Rd, [Rn, #offset]

7. B指令:无条件跳转到指定的地址。

机器码:0xB label

8. BEQ指令:如果上一次比较结果为相等,则跳转到指定的地址。

机器码:0xBEQ label

以上是ARM 32位汇编指令的一些常见例子,每个指令都有对应的机器码。

通过编写汇编程序,程序员可以直接对计算机硬件进行控制,实现各种功能。

虽然汇编语言比高级语言更难以理解和编写,但它提供了更高的灵活性和效率,特别适合对性能要求较高的应用。

ARM指令集详解(超详细!带实例!)

ARM指令集详解(超详细!带实例!)算术和逻辑指令ADC : 带进位的加法(Ad dition with C arry)ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carryADC 将把两个操作数加起来,并把结果放置到⽬的寄存器中。

它使⽤⼀个进位标志位,这样就可以做⽐ 32 位⼤的加法。

下列例⼦将加两个 128 位的数。

128 位结果: 寄存器 0、1、2、和 3第⼀个 128 位数: 寄存器 4、5、6、和 7第⼆个 128 位数: 寄存器 8、9、10、和 11。

ADDS R0, R4, R8 ; 加低端的字ADCS R1, R5, R9 ; 加下⼀个字,带进位ADCS R2, R6, R10 ; 加第三个字,带进位ADCS R3, R7, R11 ; 加⾼端的字,带进位如果如果要做这样的加法,不要忘记设置 S 后缀来更改进位标志。

这两个指令与普通指令在对操作数的限制上有所不同:1. 给出的所有操作数、和⽬的寄存器必须为简单的寄存器。

2. 你不能对操作数 2 使⽤⽴即值或被移位的寄存器。

3. ⽬的寄存器和操作数 1 必须是不同的寄存器。

4. 最后,你不能指定 R15 为⽬的寄存器。

译注:CMP 和 CMP 是算术指令,TEQ 和 TST 是逻辑指令。

把它们归⼊⼀类的原因是它们的 S 位总是设置的,就是说,它们总是影响标志位。

CMN : ⽐较取负的值(C o m pare N egative)CMN{条件}{P} <op 1>, <op 2>status = op_1 - (- op_2)CMN 同于 CMP,但它允许你与⼩负值(操作数 2 的取负的值)进⾏⽐较,⽐如难于⽤其他⽅法实现的⽤于结束列表的 -1。

这样与 -1 ⽐较将使⽤:CMN R0, #1 ; 把 R0 与 -1 进⾏⽐较详情参照 CMP 指令。

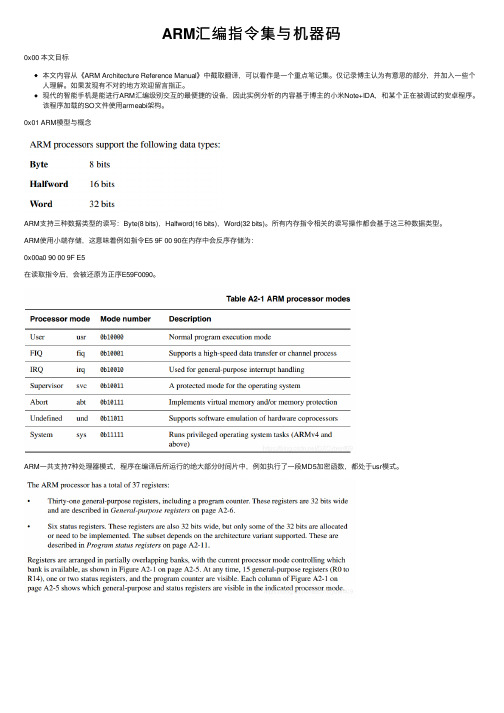

ARM汇编指令集与机器码

ARM汇编指令集与机器码0x00 本⽂⽬标本⽂内容从《ARM Architecture Reference Manual》中截取翻译,可以看作是⼀个重点笔记集。

仅记录博主认为有意思的部分,并加⼊⼀些个⼈理解。

如果发现有不对的地⽅欢迎留⾔指正。

现代的智能⼿机是能进⾏ARM汇编级别交互的最便捷的设备,因此实例分析的内容基于博主的⼩⽶Note+IDA,和某个正在被调试的安卓程序。

该程序加载的SO⽂件使⽤armeabi架构。

0x01 ARM模型与概念ARM⽀持三种数据类型的读写:Byte(8 bits),Halfword(16 bits),Word(32 bits)。

所有内存指令相关的读写操作都会基于这三种数据类型。

ARM使⽤⼩端存储,这意味着例如指令E5 9F 00 90在内存中会反序存储为:0x00a0 90 00 9F E5在读取指令后,会被还原为正序E59F0090。

ARM⼀共⽀持7种处理器模式,程序在编译后所运⾏的绝⼤部分时间⽚中,例如执⾏了⼀段MD5加密函数,都处于usr模式。

寄存器⽰例图,某个程序正在处于调试暂停中。

ARM处理器⼀共有37个之多的寄存器。

在所有的ARM状态模式中,有15个可见寄存器(R0~R14),和1~2个状态寄存器随时可编程交互。

其余没有提到的寄存器,⽤于处理异常、中断等核⼼指令,外部不可见也不能⾃主控制读写。

R0~R7作为不保留寄存器,可以⾃由编程指定其含义。

例如R0~R3最常⽤于参数传递,返回值等保存。

R8~R14是保留寄存器,有⾃⼰的特殊含义,在寄存器实例图中可以看到多半保存和地址相关的值,⼜或者指向了SP地址或LR地址。

通常R13就是SP(Stack Pointer)寄存器,该值指向当前汇编代码段可以使⽤的栈起始地址。

R14作为LR(Link Register)寄存器,保存当前汇编代码段执⾏完毕后,需要回溯到的汇编代码地址。

PC程序计数器是⼀个特殊的寄存器,指向当前正在执⾏的代码地址。

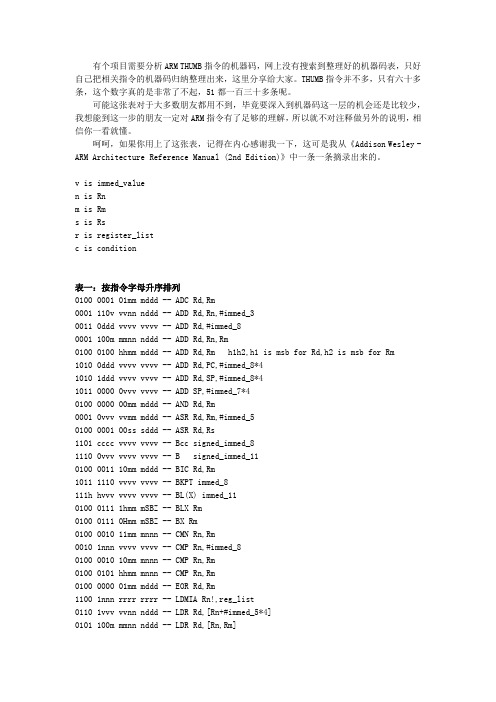

自己归纳整理的ARM THUMB指令机器码表

有个项目需要分析ARM THUMB指令的机器码,网上没有搜索到整理好的机器码表,只好自己把相关指令的机器码归纳整理出来,这里分享给大家。

THUMB指令并不多,只有六十多条,这个数字真的是非常了不起,51都一百三十多条呢。

可能这张表对于大多数朋友都用不到,毕竟要深入到机器码这一层的机会还是比较少,我想能到这一步的朋友一定对ARM指令有了足够的理解,所以就不对注释做另外的说明,相信你一看就懂。

呵呵,如果你用上了这张表,记得在内心感谢我一下,这可是我从《Addison Wesley - ARM Architecture Reference Manual (2nd Edition)》中一条一条摘录出来的。

v is immed_valuen is Rnm is Rms is Rsr is register_listc is condition表一:按指令字母升序排列0100 0001 01mm mddd -- ADC Rd,Rm0001 110v vvnn nddd -- ADD Rd,Rn,#immed_30011 0ddd vvvv vvvv -- ADD Rd,#immed_80001 100m mmnn nddd -- ADD Rd,Rn,Rm0100 0100 hhmm mddd -- ADD Rd,Rm h1h2,h1 is msb for Rd,h2 is msb for Rm1010 0ddd vvvv vvvv -- ADD Rd,PC,#immed_8*41010 1ddd vvvv vvvv -- ADD Rd,SP,#immed_8*41011 0000 0vvv vvvv -- ADD SP,#immed_7*40100 0000 00mm mddd -- AND Rd,Rm0001 0vvv vvmm mddd -- ASR Rd,Rm,#immed_50100 0001 00ss sddd -- ASR Rd,Rs1101 cccc vvvv vvvv -- Bcc signed_immed_81110 0vvv vvvv vvvv -- B signed_immed_110100 0011 10mm mddd -- BIC Rd,Rm1011 1110 vvvv vvvv -- BKPT immed_8111h hvvv vvvv vvvv -- BL(X) immed_110100 0111 1hmm mSBZ -- BLX Rm0100 0111 0Hmm mSBZ -- BX Rm0100 0010 11mm mnnn -- CMN Rn,Rm0010 1nnn vvvv vvvv -- CMP Rn,#immed_80100 0010 10mm mnnn -- CMP Rn,Rm0100 0101 hhmm mnnn -- CMP Rn,Rm0100 0000 01mm mddd -- EOR Rd,Rm1100 1nnn rrrr rrrr -- LDMIA Rn!,reg_list0110 1vvv vvnn nddd -- LDR Rd,[Rn+#immed_5*4]0101 100m mmnn nddd -- LDR Rd,[Rn,Rm]0100 1ddd vvvv vvvv -- LDR Rd,[PC+#immed_5*4] 1001 1ddd vvvv vvvv -- LDR Rd,[SP,#immed_8*4] 0111 1vvv vvnn nmmm -- LDRB Rd,[Rn,#immed_5*4] 0101 110m mmnn nddd -- LDRV Rd,[Rn,Rm]1000 1vvv vvnn nddd -- LDRH Rd,[Rn,#immed_5*2] 0101 101m mmnn nddd -- LDRH Rd,[Rn,Rm]0101 011m mmnn nddd -- LDRSB Rd,[Rn,Rm]0101 111m mmnn nddd -- LDRSH Rd,[Rn,Rm]0000 0vvv vvmm mnnn -- LSL Rd,Rm,#immed_5 0100 0000 10ss sddd -- LSL Rd,Rs0000 1vvv vvmm mddd -- LSR Rd,Rm,#immed_5 0100 0000 11ss sddd -- LSR Rd,Rs0010 0ddd vvvv vvvv -- MOV Rd,#immed_80001 1100 00nn nddd -- MOV Rd,Rn0100 0110 hhmm mddd -- MOV Rd,Rm0100 0011 01mm mddd -- MUL Rd,Rm0100 0011 11mm mddd -- MVN Rd,Rm0100 0010 01mm mddd -- NEG Rd,Rm0100 0011 00mm mddd -- ORR Rd,Rm1011 110R rrrr rrrr -- POP reg_list1011 010R rrrr rrrr -- PUSH reg_list0100 0001 11ss sddd -- ROR Rd,Rs0100 0001 10mm mddd -- SBC Rd,Rm1100 0nnn rrrr rrrr -- STMIA Rn!,reg_list 0110 0vvv vvnn nddd -- STR Rd,[Rn,#immed_5*4] 0101 000m mmnn nddd -- STR Rd,[Rn,Rm]1001 0ddd vvvv vvvv -- STR Rd,[SP,#immed_8*4] 0111 0vvv vvnn nddd -- STRB Rd,[Rn,#immed_5] 0101 010m mmnn nddd -- STRB Rd,[Rn,Rm]1000 0vvv vvnn nddd -- STRH Rd,[Rn,#immed_5*2] 0101 001m mmnn nddd -- STRH Rd,[Rn,Rm]0001 111v vvnn nddd -- SUB Rd,Rn,#immed_3 0011 1ddd vvvv vvvv -- SUB Rd,#immed_80001 101m mmnn nddd -- SUB Rd,Rn,Rm1011 0000 1vvv vvvv -- SUB Sp,#immed_7*41101 1111 vvvv vvvv -- SWI immed_80100 0010 00mm mnnn -- TST Rn,Rm表二:按指令机器码升序排列0000 0vvv vvmm mnnn -- LSL Rd,Rm,#immed_5 0000 1vvv vvmm mddd -- LSR Rd,Rm,#immed_5 0001 0vvv vvmm mddd -- ASR Rd,Rm,#immed_5 0001 100m mmnn nddd -- ADD Rd,Rn,Rm0001 101m mmnn nddd -- SUB Rd,Rn,Rm0001 110v vvnn nddd -- ADD Rd,Rn,#immed_30001 111v vvnn nddd -- SUB Rd,Rn,#immed_30001 1100 00nn nddd -- MOV Rd,Rn0010 0ddd vvvv vvvv -- MOV Rd,#immed_80010 1nnn vvvv vvvv -- CMP Rn,#immed_80011 0ddd vvvv vvvv -- ADD Rd,#immed_80011 1ddd vvvv vvvv -- SUB Rd,#immed_80100 0000 00mm mddd -- AND Rd,Rm0100 0000 01mm mddd -- EOR Rd,Rm0100 0000 10ss sddd -- LSL Rd,Rs0100 0000 11ss sddd -- LSR Rd,Rs0100 0001 00ss sddd -- ASR Rd,Rs0100 0001 01mm mddd -- ADC Rd,Rm0100 0001 10mm mddd -- SBC Rd,Rm0100 0001 11ss sddd -- ROR Rd,Rs0100 0010 00mm mnnn -- TST Rn,Rm0100 0010 01mm mddd -- NEG Rd,Rm0100 0011 00mm mddd -- ORR Rd,Rm0100 0010 10mm mnnn -- CMP Rn,Rm0100 0010 11mm mnnn -- CMN Rn,Rm0100 0011 01mm mddd -- MUL Rd,Rm0100 0011 10mm mddd -- BIC Rd,Rm0100 0011 11mm mddd -- MVN Rd,Rm0100 0100 hhmm mddd -- ADD Rd,Rm h1h2,h1 is msb for Rd,h2 is msb for Rm 0100 0101 hhmm mnnn -- CMP Rn,Rm0100 0110 hhmm mddd -- MOV Rd,Rm0100 0111 0Hmm mSBZ -- BX Rm0100 0111 1hmm mSBZ -- BLX Rm0100 1ddd vvvv vvvv -- LDR Rd,[PC+#immed_5*4]0101 000m mmnn nddd -- STR Rd,[Rn,Rm]0101 001m mmnn nddd -- STRH Rd,[Rn,Rm]0101 010m mmnn nddd -- STRB Rd,[Rn,Rm]0101 011m mmnn nddd -- LDRSB Rd,[Rn,Rm]0101 100m mmnn nddd -- LDR Rd,[Rn,Rm]0101 101m mmnn nddd -- LDRH Rd,[Rn,Rm]0101 110m mmnn nddd -- LDRV Rd,[Rn,Rm]0101 111m mmnn nddd -- LDRSH Rd,[Rn,Rm]0110 0vvv vvnn nddd -- STR Rd,[Rn,#immed_5*4]0110 1vvv vvnn nddd -- LDR Rd,[Rn+#immed_5*4]0111 1vvv vvnn nmmm -- LDRB Rd,[Rn,#immed_5*4]0111 0vvv vvnn nddd -- STRB Rd,[Rn,#immed_5]1000 0vvv vvnn nddd -- STRH Rd,[Rn,#immed_5*2]1000 1vvv vvnn nddd -- LDRH Rd,[Rn,#immed_5*2]1001 0ddd vvvv vvvv -- STR Rd,[SP,#immed_8*4]1001 1ddd vvvv vvvv -- LDR Rd,[SP,#immed_8*4]1010 0ddd vvvv vvvv -- ADD Rd,PC,#immed_8*41010 1ddd vvvv vvvv -- ADD Rd,SP,#immed_8*41011 0000 0vvv vvvv -- ADD SP,#immed_7*41011 0000 1vvv vvvv -- SUB Sp,#immed_7*41011 010R rrrr rrrr -- PUSH reg_list1011 110R rrrr rrrr -- POP reg_list1011 1110 vvvv vvvv -- BKPT immed_81100 0nnn rrrr rrrr -- STMIA Rn!,reg_list1100 1nnn rrrr rrrr -- LDMIA Rn!,reg_list1101 cccc vvvv vvvv -- Bcc signed_immed_81101 1111 vvvv vvvv -- SWI immed_81110 0vvv vvvv vvvv -- B signed_immed_11111h hvvv vvvv vvvv -- BL(X) immed_11附件:《Addison Wesley - ARM Architecture Reference Manual (2nd Edition)》。

ARM指令集讲解

ARM指令集讲解ARM指令和指令系统:指令是指示计算机某种操作的命令,指令的集合称为指令系统。

指令系统的功能强弱很大程度上决定了这类计算机智能的高低,它集中地反应了微处理器的硬件功能和属性。

ARM指令在机器中的表示格式是用32位的二进制数表示。

如ARM中有一条指令为ADDEQS R0,R1,#8;其二进制代码形式为:31~28 | 27~25 | 24~21 | 20 | 19~16 | 15~12 | 11~0 0000 | 001 | 0100 | 1 | 0001 | 0000 | 0000 0000 1000cond | opcode | Rn | Rd | Op2ARM指令格式一般如下:{}{s},{,}格式中< >的内容是必不可少的,{ }中的内容可忽略表示操作码。

如ADD表示算术加法{} 表示指令执行的条件域。

如EQ、NE等,缺省为AL。

{S} 决定指令的执行结果是否影响CPSR的值,使用该后缀则指令执行结果影响CPSR的值,否则不影响表示目的寄存器表示第一个操作数,为寄存器表示第二个操作数,可以是立即数。

寄存器和寄存器移位操作数ARM指令后缀:S、!S后缀:指令中使用S后缀时,指令执行后程序状态寄存器的条件标志位将被刷新,不使用S后缀时,指令执行后程序状态寄存器的条件标志将不会发生变化。

S后缀常用于对条件进行测试,如是否有溢出,是否进位等,根据这些变化,就可以进行一些判断,如是否大于,相等,从而影响指令执行的顺序。

!后缀:如果指令地址表达式中不含!后缀,则基址寄存器中的地址值不会发生变化。

加上此后缀后,基址寄存器中的值(指令执行后)= 指令执行前的值+ 地址偏移量(1)!后缀必须紧跟在地址表达式后面,而地址表达式要有明确的地址偏移量(2)!后缀不能用于R15(PC)的后面(3)当用在单个地址寄存器后面时,必须确信这个寄存器有隐性的偏移量,例如“STMDB R1!,{R3,R5,R7}”。

arm汇编指令总结(不断更新)

arm汇编指令总结(不断更新)/********************************************************************************* @author Maoxiao Hu* @version V1.0.1* @date Jan-2015******************************************************************************* < COPYRIGHT 2015 ISE of SHANDONG UNIVERSITY >********************************************************************************/本⽂会不时完善和纠正⼀些⼩错误,还请到参考最新版本。

ARM的指令集去哪⾥查才最权威最详细呢?⼀般ARM官⽅⽹站上会有针对你⼿上芯⽚对应指令集的《架构参考⼿册》,可以免费下载。

例如我⼿上的exynos4412是ARM v7-A指令集,那么对应的⼿册就是《arm_architecture_reference_manual ARMv7-A and ARMv7-R edition.pdf》。

在这个⼿册的第A8节:Instruction Details 按照字母顺序详细介绍了ARMv7-A的各种指令语法,700页之多,⽤到时详查即可。

下⾯说⼀下查阅⽂档需要注意的⼏个地⽅。

⼀、指令格式当我们查找⼀些指令⽐如ldrle movne,发现⽆法在⼿册中搜索到,其实并不是没有这些指令,⽽是这些指令是在原始指令ldr mov后⾯加上了条件码(Condition Code)le ne,然后被写到了⼀起。

举个例⼦:LDR的第⼀种指令格式如下,LDR后⾯的<c>就表⽰可以选择后接条件码,当然也可以不接。

ARM汇编指令学习:[0]编码格式与条件码域

![ARM汇编指令学习:[0]编码格式与条件码域](https://img.taocdn.com/s3/m/7e04cb998ad63186bceb19e8b8f67c1cfbd6ee4f.png)

ARM汇编指令学习:[0]编码格式与条件码域ARM 汇编指令学习:[0]编码格式与条件码域⼀、ARM指令的编码格式31 2827 212019 1615 1211 0cond opcode S Rn Rd shifter_operand其中:cond [31-28] 4-bit 指令执⾏的条件编码opcode [27-21] 4-bit 指令操作符编码S [20] 1-bit 决定指令的操作是否影响CPSR的值Rn [19-16] 4-bit 包含第1个操作数的寄存器编码Rd [15-12] 4-bit ⽬标寄存器编码shifter_operand [11-0] 12-bit 表⽰第2个操作数⼀条典型的ARM指令语法如下:<opcode>{<cond>}{S} <Rd>,<Rn>,<shifter_operand>其中:<opcode> 指令助记符{<cond>} 指令执⾏的条件{S} 决定指令的操作是否影响CPSR的值<Rd> 表⽰⽬标寄存器<Rn> 表⽰包含第1个操作数的寄存器<shifter_operand> 表⽰第2个操作数⼆、ARM指令的条件码域条件码<cond>条件码助记符含义CPSR中条件标志位值0000EQ相等Z=10001NE不相等Z=00010CS/HS⽆符号数⼤于/等于C=10011CC/LO⽆符号数⼩于C=00100MI负数N=10101PL⾮负数N=00110VS上溢出V=10110VS上溢出V=1条件码<cond>条件码助记符含义CPSR中条件标志位值0111VC没有上溢出V=01000HI⽆符号数⼤于C=1且Z=01001LS⽆符号数⼩于/等于C=0且Z=11010GE带符号数⼤于/等于N=1且V=1或N=0且V=01011LT带符号数⼩于N=1且V=0或N=0且V=11100GT带符号数⼤于Z=0且N=V1101LE带符号数⼩于/等于Z=1或N!=V1110AL⽆条件执⾏1111NV该指令从不执⾏我的个⼈主页:我的个⼈站点博客:我的CSDN博客:我的简书:我的GitHub:欢迎相互follow~。

ARM汇编指令

ARM指令格式

• ARM指令集——第2个操作数

<opcode> {<cond>} {S} <Rd> ,<Rn>{,<operand2>}

灵活的使用第2个操作数“operand2”能够提高代码效率。

它有如下的形式:

▪Rm——寄存器方式;

如:SUB R1,R1,R2

▪Rm,shift——寄存器移位方式;

ARM指令种类

存储器访问指令

➢ARM处理器是典型的RISC处理器,对存储器的访问 只能使用加载和存储指令实现。对外围IO、程序数据 的访问均要通过加载/存储指令进行。 ➢存储器访问指令分为单寄存器操作指令和多寄存器操 作指令。 ➢所有单寄存器加载/存储指令可分为“字和无符号字 节加载存储指令”和“半字和有符号字节加载存储指 令。 ➢一条指令处理多寄存器的的加载/存储。

个寄存器的任何子集或所有寄存器。多寄存器寻址指令举例如下:

LDMIA

R1!,{R2-R4,R6}

;将R1指向的单元中的数据读出到R2~R4,R6中

• 相对寻址

相对寻址是基址寻址的一种变通。由程序计数器

PC提供基准地址,指令中的地址码字段作为偏移量,两者

相加后得到的地址即为操作数的有效地址。

BL

SUBR1

四种类型的堆栈方式:满递增、空递增、满递减、空递减

ARM指令格式

ARM指令的基本格式如下:

<opcode> {<cond>} {S} <Rd> ,<Rn>{,<operand2>}

其中<>号内的项是必须的,{}号内的项是可选的。 各项的说明如下:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ARM汇编指令机器码举例详解

ARM7内核采用的是RISC精简指令集,所有的ARM指令都是32bits的,在这32bits里既包含了指令的指令码,也包含了指令需要运算的数据,以MOV 指令为例,通过MOV指令的32bits可以识别出这是一个MOV指令,又可以在这32bits里找到源寄存器和目的寄存器。

我们来看一下MOV指令的机器

码格式:

28~31bits(cond)是条件码,就是表明这条语句里是否有大于、等于、非零等的条件判断,这4bits共有16种状态,分别为:

表 1 汇编语言条件码

指令与条件码可以有多种组合,比如MOV指令可以有MOV、MOVEQ、MOVLT等多种形式。

前面我们说过状态寄存器里有NZCV的状态标志,

当执行一条指令时,芯片就会将这条指令的条件码与状态寄存器中的状态标志做比较,如果状态寄存器中的状态标志满足这条指令的条件码时,则执行这条语句,如果不满足则不执行这条指令。

状态寄存器中的状态标志是受某些指令影响的,因此在使用有条件码的

指令进行判断前,必然会有其它指令配合使用,先修改状态寄存器中的状态标志。