锁相环Simulink仿真模型

几个简单的simulink仿真模型

一频分复用和超外差接收机仿真目的1熟悉Simulink模型仿真设计方法2掌握频分复用技术在实际通信系统中的使用3理解超外差收音机的接收原理内容设计一个超外差收接收机系统,其中发送方的基带信号分别为1000Hz的正弦波和500Hz的方波,两路信号分别采用1000kHz和1200kHz的载波进行幅度调制,并在同一信道中进行传输。

要求采用超外差方式对这两路信号进行接收,并能够通过调整接收方的本振频率对解调信号进行选择。

原理超外差接收技术广泛用于无线通信系统中,基本的超外差收音机的原理框图如图所示:图1-1超外差收音机基本原理框图从图中可以看出,超外差接收机的工作过程一共分为混频、中频放大和解调三个步骤,现分别叙述如下:混频:由天线接收到的射频信号直接送入混频器进行混频,混频所使用的本机振荡信号由压控振荡器产生,并可根据调整控制电压随时调整振荡频率,使得器振荡频率始终比接收信号频率高一个中频频率,这样,接受信号和本机振荡在混频器中进行相乘运算后,其差频信号的频率成分就是中频频率。

其频谱搬移过程如下图所示:图1-2 超外差接收机混频器输入输出频谱中频放大:从混频模块输出的信号中包含了高频和中频两个频率成分,这样一来只要采用中频带通滤波器选出进行中频信号进行放大,得到中频放大信号。

解调:将中频放大后的信号送入包络检波器,进行包络检波,并解调出原始信号。

步骤1、设计两个信号源模块,其模块图如下所示,两个信号源模块的载波分别为1000kHz,和1200kHz,被调基带信号分别为1000Hz的正弦波和500Hz的三角波,并将其封装成两个子系统,如下图所示:图1-2 信源子系统模型图2、为了模拟接收机距离两发射机距离不同引起的传输衰减,分别以Gain1和Gain2模块分别对传输信号进行衰减,衰减参数分别为0.1和0.2。

最后在信道中加入均值为0,方差为0.01的随机白噪声,送入接收机。

3、接收机将收到的信号直接送入混频器进行混频,混频所使用的本机振荡信号由压控振荡器产生,其中压控振荡器由输入电压进行控制,设置Slider Gain模块,使输入参数在500至1605可调,从而实现本振的频率可控。

锁相环Simulink仿真模型

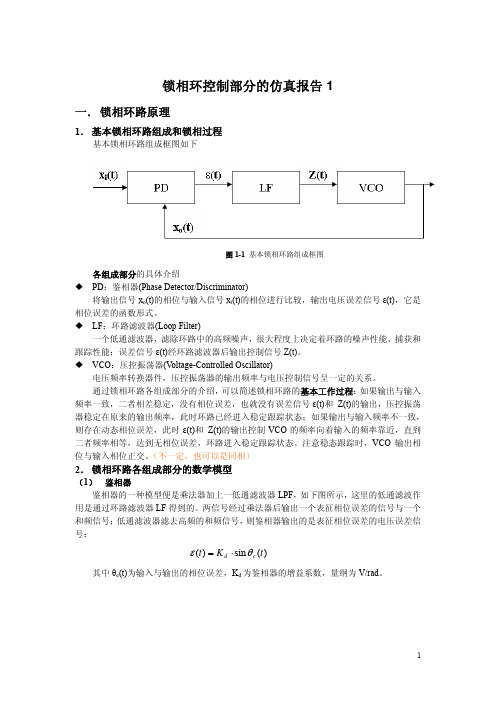

锁相环学习总结通过这段的学习,我对锁相环的一些基本概念、结构构成、工作原理、主要参数以及simulink 搭建仿真模型有了较清晰的把握与理解,同时,在仿真中也出现了一些实际问题,下面我将对这段学习中对锁相环的认识和理解、设计思路以及中间所遇到的问题作一下总结:1. 概述锁相环(PLL )是实现两个信号相位同步的自动控制系统,组成锁相环的基本部件有检相器(PD )、环路滤波器(LF )、压控振荡器(VCO ),其结构图如下所示:2.锁相是相位锁定的简称,表示两个信号之间相位同步。

若两正弦信号如下所示:相位同步是指两个信号频率相等,相差为一固定值。

当i ω=o ω,两个信号之间的相位差 为一固定值,不 随时间变化而变化,称两信号相位同步。

o i t t θθθθ-=-)()('当i ω≠o ω,两个信号的相位差 ,不论iθ 是否等于o θ,只要时间有变化,那么相位差就会随时间变化而变化,称此时两信号不同步。

若这两个信号分别为锁相环的输入和输出,则此时环路出于失锁状态。

当环路工作时,且输入与输出信号频差在捕获带范围之内,通过环路的反馈控制,输出信号的瞬时角频率)(t v ω便由o ω向i ω方向变化,总会有一个时刻使得i ω=o ω,相位差等于0或一个非常小的常数,那么此时称为相位锁定,环路处于锁定状态。

若达到锁定状态后,输入信号频率变化,通过环路控制,输出信号也继续变化 并向输入信号频率靠近,相位差保持在一个固定的常数之内,则称环路此时为跟踪状态。

锁定状态可以认为是静态的相位同步,而跟踪状态则为动态的相位同步。

环路从失锁进入到锁定状态称为捕获状态。

其他几个环路工作时的重要概念:快捕带:能使环路快捕入锁的最大频差称为环路的快捕带,记为L ω∆,两倍的快捕带为快捕范围。

捕获带:能使环路进入锁定的最大固有频差,用P ω∆表示,两倍的捕获带为捕获范围。

同步带:环路在所定条件下,可缓慢增加固有频差,直到环路失锁,把能够维持环路锁定的最大固有频差成为同步带,用H ω∆,2H ω∆为同步范围。

自适应锁相环的设计与仿真

理论算法2021.07自适应锁相环的设计与仿真何琦(安徽理工大学电气与信息工程学院,安徽淮南,232001)摘要:在三相电压不平衡时,负序分量会在Park变换后产生一个2倍基频的波动,进而影响对基频分量相位的提取。

针对一般的锁相环在电网三相不平衡时无法准确锁定电网的相位,本文提出一种基于陷波器的自适应锁相环,利用自适应陷波器(ANF)能够输出两个相互正交分量的特点,生成两个能抵消dq坐标系的负序分量,这样就实现了基波的正序负序分离。

在Matlab/Simulink中建立仿真模型进行验证,结果表明了文中所提的方法在电网不平衡时可以准确地锁定电网的相位。

关键词:三相电压不平衡;锁相环;自适应陷波器;正序负序分离Design and Simulation of Adaptive Phase-locked LoopHe Qi(School of Electrical and Information Engineering,Anhui University of Science and Technology,Huainan Anhui,232001)Abstract:When the fundamental frequency of the three-phase is not balanced,a negative componentof the volt a ge will be ext r ac ted.In view of the fac t that the general phase-locked loop(PLL)cannot accurately lock the phase of the power grid when the three-phase power grid is unbalanced,this paper proposes an adaptive phase-locked loop based on notch f订ter.The adaptive notch filter(ANF) can output two mutually orthogonal components to generate two negative sequence components which can offset the dq coordinate system.Thus,the separation of positive sequence and negative sequenceof fundamental wave is realized.The simulation model is established in Matlab/SIMULINK for verifica t ion.The resu Its show that the proposed met h od can accura t ely lock the phase of power grid when the power grid is unbalanced.Keywords:Three-phase voltage unbalance;PLL;Adaptive notch f订ter;Positive sequence negative sequence separation0引言随着新能源技术的快速发展,并网逆变器在分布式发电中得到广泛应用。

matlab锁相环仿真

锁相环

1.svpwm调制

(1)、simulink搭建的结构图为

(2)、三相正弦波经过alpha-beta 坐标变换的x-y坐标图形为

(2)、以上结果经过svpwm调制模块后输出的适量顶点轨迹xy图形为

2

2、三相锁相环的设计

(1)、三相锁相环的原理为

三相锁相环的基本原理是基于坐标变换,采用静止坐标变换和同步坐标变换完成鉴相功能(将输入的三相电压经过坐标变换输出输入电压(相位给定)与输出信号的相位差),然后经过滤波器将高频信号过滤,经过pi调节器锁定到输入信号的频率,然后经过积分器对频率w进行积分得到电角度。

最后将输出反馈到输入端,构成闭环系统。

(2)、结构框图为

Pll局部结构图为

(3)、仿真结果与分析1 三相电源中含有谐波电源波形含有五次谐波

电源波形

仿真结果为

当三相电源不平衡时

仿真结果图为

电源波形为

仿真结果图为

对以上仿真结果的具体分析为

如果电源中含有直流分量,在进行abc到dq变换过程中直流分量会自动消失掉,故输出波形中不会含有直流分量

当电源中含有谐波时变换以后会是一个正弦量这个时候在系统

中添加一个滤波器将高频信号过滤掉即可。

其实锁相环最终的输出量为与输入量同相位的基波分量。

3 单相锁相环的设计

结构图为

pll具体结构图为

该仿真电源含有三相谐波。

锁相环Simulink仿真模型

锁相环学习总结通过这段的学习,我对锁相环的一些基本概念、结构构成、工作 原理、主要参数以及 simulink 搭建仿真模型有了较清晰的把握与理 解,同时,在仿真中也出现了一些实际问题,下面我将对这段学习中 对锁相环的认识和理解、设计思路以及中间所遇到的问题作一下总 结:1. 概述锁相环(PLL )是实现两个信号相位同步的自动控制系统,组成 锁相环的基本部件有检相器(PD )、环路滤波器(LF )、压控振荡器 (VCO ),其结构图如下所示:2. 锁相环的基本概念和重要参数指标锁相是相位锁定的简称,表示两个信号之间相位同步。

若两正弦 信号如下所示:q(t) U j Sin( it i) U isin (t)u °(t) U o Sin( °t o ) U o Sin '(t)相位同步是指两个信号频率相等,相差为一固定值 当i = o ,两个信号之间的相位差(t) '(t) i o 为一固定值,不 随时间变化而变化,称两信号相位同步。

当i 「,两个信号的相位差(t) '(t) ( i o )t i o ,不论i是否等于 o ,只要时间有变化, 那么相位差就会随时间变化而 变化,称此时两信号不同步。

若这两个信号分别为锁相环的输入 和输出,则此时环路出于 失锁状态 。

当环路工作时,且输入与输出信号频差在捕获带范围之oi(t)ud(t) -- ue(t)PDLF ----------- ► VCO内,通过环路的反馈控制,输出信号的瞬时角频率v(t)便由。

向i方向变化,总会有一个时刻使得i= o,相位差等于0或一个非常小的常数,那么此时称为相位锁定,环路处于锁定状态。

若达到锁定状态后,输入信号频率变化,通过环路控制,输出信号也继续变化并向输入信号频率靠近,相位差保持在一个固定的常数之内,则称环路此时为跟踪状态。

锁定状态可以认为是静态的相位同步,而跟踪状态则为动态的相位同步。

基于simulink的用于载波提取的锁相环仿真

用于载波提取的锁相环仿真

一、仿真原理:利用平方环恢复载波

抑制载波的双边带(DSB-SC)信号为

其中,m(t)为基带信号,由于其直流分量为零,所以r(t)中没有载波分量。

为了得出载波,可对r(t)作平方运算,即

式中,的均值是基带信号的功率,是一个正的常数,因此在中

含有2fc频率分量的谐波,用中心频率为2fc}的带通滤波器将这一谐波分量选出后,再通过锁相环锁定之,最后对锁相环VCO输出信号进行2分频即可恢复载波。

由于2分频器的初始状态的任意性,其输出的恢复载波将存在相位模糊,即

恢复载波可能是,也可能是。

抑制载波的双边带调制解调系统,载波频率为10KHz,被调信号为1KHz正弦波。

二、Simulink仿真模型:

三、仿真结果:。

锁相环频率合成器设计与Simulink仿真

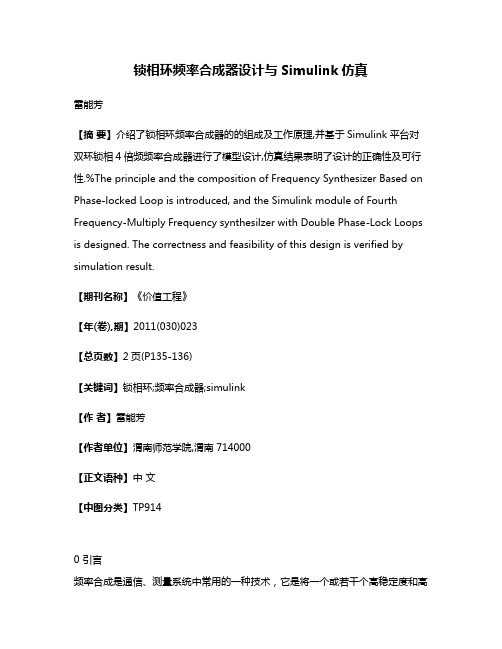

锁相环频率合成器设计与Simulink仿真雷能芳【摘要】介绍了锁相环频率合成器的的组成及工作原理,并基于Simulink平台对双环锁相4倍频频率合成器进行了模型设计,仿真结果表明了设计的正确性及可行性.%The principle and the composition of Frequency Synthesizer Based on Phase-locked Loop is introduced, and the Simulink module of Fourth Frequency-Multiply Frequency synthesilzer with Double Phase-Lock Loops is designed. The correctness and feasibility of this design is verified by simulation result.【期刊名称】《价值工程》【年(卷),期】2011(030)023【总页数】2页(P135-136)【关键词】锁相环;频率合成器;simulink【作者】雷能芳【作者单位】渭南师范学院,渭南714000【正文语种】中文【中图分类】TP9140 引言频率合成是通信、测量系统中常用的一种技术,它是将一个或若干个高稳定度和高准确度的参考频率经过各种处理技术生成具有同样稳定度和准确度的大量离散频率的技术。

频率合成器通常分为直接式频率合成器、间接式频率合成器、直接式数字频率合成器(DDS)。

间接式频率合成器也称锁相式频率合成器,它是利用锁相环路的窄带跟踪特性,在石英晶体振荡器提供的基准频率源作用下,产生出一系列离散的频率。

锁相式频率合成器的优点是可以实现任意频率和带宽的频率合成,具有极低的相位噪声和杂散[1]。

1 锁相环的工作原理锁相环是一种利用外部输入的参考信号控制环路内部振荡信号的反馈控制电路。

锁相环主要由鉴相器、压控振荡器(VCO)及环路滤波器组成[2],如图1所示。

基于SOGI—FLL+NF的复合锁相环

基于SOGI—FLL+NF的复合锁相环三相并网系统中,锁相环能检测出三相电网电压的相位和频率信息,它对整个逆变系统的安全稳定运行有重要作用。

三相电网发生波动时,同步旋转锁相环易受二倍频分量的影响导致锁相不准确。

文章采用SOGI-FLL+NF复合锁相结构,消除三相电网电压波动对锁相效果的影响,通过Matlab/Simulink仿真证明复合结构锁相环的可行性和准确性。

标签:锁相环;二阶广义积分器;陷波器引言對于分布式发电系统而言,为了保证并网逆变器能够向电网输送高质量的电能,这就要求并网电流必须与电压同步。

谐波会使电网电压波动,所以需要锁相环实时准确的获取电网电压的幅值和相位信息,获取信息准确与否直接决定了设备安全稳定运行。

在三相并网逆变器系统中常采用同步旋转坐标系锁相环(SRF-PLL),当三相电压平衡时,有较好的锁相效果,但是当电网电压不平衡时,SRF-PLL容易受二倍频分量影响使精度下降。

二阶广义积分(SOGI)型锁相技术能够抑制谐波分量,但是在精度上有待提高。

陷波器可以看作是一个带宽很小的带阻滤波器,把某一频率的信号滤除。

为了消除谐波对PLL的影响,本文采用SOGI-FLL+NF 复合结构仿真分析锁相效果。

1 三相电网电压不平衡时SRF-PLL性能分析SRF-PLL将输入abc坐标系下的三相电网电压经过Clark和park变换,得到dq系下的电压,调节q轴分量为0,使dq坐标系的旋转角θ与电网电压矢量的相位角相同,来实现锁相[1]。

当电网电压不平衡并采用三相三线的方式接入电网的时候,只考虑正序分量和负序分量。

此时电网电压可以表示为:式中:Vgp、Vgn是电网电压的正序与负序分量的幅值,Φp、Φn正序和负序分量的初始相位,ω代表电网电压角频率。

对式(1)进行Clark变换,再进行Park变换,电网电压矢量在两相旋转坐标系下的表达式为:可以看出,电网电压不平衡时,dq轴下电网电压正序分量变成了直流量,基波负序分量变成了二倍频交流量。

新型锁相环技术及仿真分析

新型锁相环技术及仿真分析

郭子雷;张海燕;徐强;秦臻

【期刊名称】《电测与仪表》

【年(卷),期】2015(000)009

【摘要】新型锁相环因其诸多优点成为了电力电子技术中的研究热点。

这里对三种新型的锁相环进行了原理分析及比较,通过搭建相应的数学模型从理论上解析了它们的区别和联系,并通过simulink仿真软件建立了对应的仿真模型并仿真得出实验结果并进行了性能对比,验证了新型锁相环的锁相效果及适用范围。

【总页数】5页(P82-86)

【作者】郭子雷;张海燕;徐强;秦臻

【作者单位】上海电机学院电气学院,上海200240;上海电机学院电气学院,上海200240;上海电机学院电气学院,上海200240;上海电机学院电气学院,上海200240

【正文语种】中文

【中图分类】TM464

【相关文献】

1.基于双派克变换的新型三相锁相环技术 [J], 李研达

2.分布式能源并网锁相环技术仿真分析 [J], 孙忠鸣;张海燕;郭建;宋飞宇;

3.应用于有源滤波器的新型软锁相环技术 [J], 马立新;徐聪;项庆

4.分布式能源并网锁相环技术仿真分析 [J], 孙忠鸣;张海燕;郭建;宋飞宇

5.一种适用于谐波电网环境的新型锁相环技术 [J], 张蕾

因版权原因,仅展示原文概要,查看原文内容请购买。

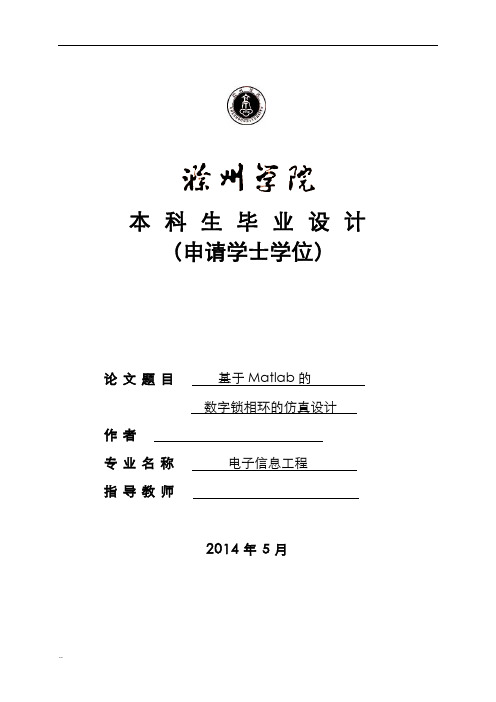

基于MATLAB数字锁相环仿真设计

本科生毕业设计(申请学士学位)论文题目基于Matlab的数字锁相环的仿真设计作者专业名称电子信息工程指导教师2014年5月学生:(签字)学号:答辩日期:2014 年 5 月24 日指导教师:(签字)目录摘要 (1)Abstract (1)1 绪论 (2)1.1 本文研究背景 (2)1.2 本文研究意义 (2)1.3 锁相环和仿真方式 (2)1.3.1 锁相环 (2) (2)3 2 模拟锁相环Matlab仿真 (3)2.1 模拟锁相环方案 (3)2.1.1 模拟鉴相器 (3)2.1.2 模拟低通滤波器 (6)2.1.3 模拟压控振荡器 (7)2.2 模拟锁相环仿真 (8)2.3 本章小结 (9)3 数字锁相环Matlab仿真 (10)3.1 数字锁相环方案 (10)3.1.1 数字鉴相器 (10)3.1.2 数字滤波器 (12)3.1.3 数字压控振荡器 (13)3.2 数字锁相环仿真 (14)3.3 本章小结 (15)4 总结与展望 (15)参考文献 (16)致 (18)基于Matlab的数字锁相环的仿真设计摘要:锁相环是一种能够自动跟踪信号相位并达到锁频目的的闭环负反馈系统。

数字锁相环在无线电领域得到较广泛的应用和发展。

而且已经成为雷达、通信、导航等各类电子信号产品不可替代的元器件之一。

锁相环的窄带跟踪性能使其得到较广泛应用。

因为锁相技术在实际应用中较为复杂,所以锁相环的设计通常采用仿真设计这种方式。

本次设计采用Matlab这一软件进行辅助仿真设计,完全能达到设计预期的目标。

Matlab中的Simulink仿真软件,具有很强的灵活性和直观性。

本次设计所采用的方法是在simulink中搭建模拟锁相的模型,并对模拟锁相环的组成、结构、设计进行不断的分析和改进。

然后根据模拟锁相环的原理进行改进,并搭建数字锁相环。

关键词:锁相环;自动跟踪;matlab;simulinkSimulative design of digital phase-locked loop based onMatlabAbstract:PLL is the automatic tracking system of close loop atracking signal phase. It is widely used in various fields of radio. It has become an irreplaceable part of radar, communication, navigation and all kinds of electronicsignal device. PLL is able to be widely used. Because, it has unique narrow-band tracking performance. However, because of the complexity of phase lock technique, for the design of PLL have brought great difficulty. This design uses Matlab, the simulative software for design assistance, can completely meet the design expectations. Simulink simulative software on Matlab, has strong flexibility and intuitive. Methods used by this project is to build the analog phase locked in the Simulink model, and the composition, structure, design of analog phase-locked loop of continuous improvement and analysis. It improved according to the principle of analog PLL, build digital phase-locked loop in Simulink, and then reach the simulation design of digitalphase-locked loop based on Matlab the design objective .Key words: PLL, Automatic tracking, Matlab, simulink1 绪论1.1 本文研究背景19世纪30年代法国H.de Bellescize首次提出同步检波这一概念,并且设计出锁相环电路这一划时代的研究成果[1]。

锁相环仿真报告

ωn =

2 BL ; 1 ζ+ 4ζ

τ1 =

Kd Kr

ω

2 n

;

τ2 =

2ζ

ωn

。

2. 仿真分析(使用 Matlab 中的 Simulink)

(1) 仿真参数 3 给定 ζ=0.707,Kd=4V/rad,Kr=24π×10 rad/(V·S),BL=10Hz,计算得 ωn=19rad/s, τ1=848s,τ2=0.075s,环路滤波器传递函数

0

0.1

0.2

0.3

1/ 2

τ ⎛ Kd Kr ⎞ ⎟ , ζ = ωn = 2 ⎜ ⎟ 2 2⎜ ⎝ τ1 ⎠ τ2

1/ 2

它是传递函数的幅频曲线的最高点对应的频率; ζ 为环路阻尼系数, ωn 为自然谐振频率, 它表示了传递函数幅频响应最大值的衰减程度,该值越大,传递函数幅频曲线最高点越小。 环路噪声带宽 BL 可用 ωn 和 ζ 来表示

BL =

ωn

2

(ζ +

1 ) 4ζ

环路噪声带宽是幅频响应下降到 3dB 时的频宽。

二. 锁相环的锁定过程分析

1. 环路捕获过程的几种情况

① 快捕过程

3

起始频差很小,即输入输出的相差 θe(t)动态变化频率很小,使得 Z(t)的变化不超过一个 周期时环路就进入锁定状态。此时 θe(t)的变化不超过 2π,这种捕获过程称为快捕过程。 快捕带:使得 θe(t)在 2π 之内环路就进入锁定的最大起始频差。 ② 频率牵引的捕捉过程 随着起始频差增大, 相位误差 θe(t)的频率增大, 则误差电压信号 ε(t)频率增大, 此时 ε(t) 通过环路滤波器(低通)有衰减。如果衰减后的误差信号不至于使 Z(t)接近于 0,而是对压控 振荡器(VCO)还是有一定的控制作用,则 VCO 输出频率会逐渐向着输入频率靠近,这就使 得误差信号 ε(t)的频率得到降低,通过环路滤波器的衰减变弱,Z(t)变大,对 VCO 的控制作 用逐渐变大,直到最后进入锁定过程。 捕捉带:可以通过频率牵引过程使环路进入锁定状态的最大起始频差。 ③ 环路无法锁定情况 当起始频差很大,使得误差信号 ε(t)不能通过环路滤波器,Z(t)接近于 0,不能对 VCO 进行电压控制,则 VCO 的输出频率和相位不发生变化,环路不能锁定。

simulink仿真锁相环工作原理

simulink仿真锁相环工作原理

Simulink仿真锁相环的工作原理如下:

1. 锁相环由相位比较器、低通滤波器、电压控制振荡器(VCO)以及除频

器组成。

2. 相位比较器接收输入信号和反馈信号,并输出相位误差,表示输入信号和反馈信号之间的相位差。

3. 低通滤波器对相位误差进行滤波处理,产生直流偏置电压,控制VCO的频率调节。

4. 电压控制振荡器根据LF输出的直流偏置电压调整自身的振荡频率,将VCO的输出信号作为反馈信号输入到PD中。

5. 除频器根据设定的除数将VCO输出的频率进行分频,输出给相位比较器,以提供稳定的参考信号。

以上是锁相环的工作原理,如需了解更多信息,建议查阅相关书籍或咨询专业人士。

锁相环应用电路仿真

高频电子线路实训报告锁相环路仿真设计专业学生姓名学号2015 年 6 月24日锁相环应用电路仿真锁相环是一种自动相位控制系统,广泛应用于通信、雷达、导航以及各种测量仪器中。

锁相环及其应用电路是“通信电子电路”课程教学中的重点容,但比较抽象,还涉及到新的概念和复杂的数学分析。

因此无论是教师授课还是学生理解都比较困难。

为此,我们将基于Multisim的锁相环应用仿真电路引入课堂教学和课后实验。

实践证明,这些仿真电路可以帮助学生对相关容的理解,并为进行系统设计工作打下良好的基础。

锁相环的应用电路很多,这里介绍锁相环调频、鉴频及锁相接收机的Multisim仿真电路。

1.锁相环的仿真模型首先在Multisim软件中构造锁相环的仿真模型(图1)。

基本的锁相环由鉴相器(PD)、环路滤波器(I P)和压控振荡器(VCO)三个部分组成。

图中,鉴相器由模拟乘法器A 实现,压控振荡器为V3,环路滤波器由R1、C1构成。

环路滤波器的输出通过R2、R3串联分压后加到压控振荡器的输入端,直流电源V2用来调整压控振荡器的中心频率。

仿真模型中,增加R2、R3及的目的就是为了便于调整压控振荡器的中心频率。

图1 锁相环的仿真模型2.锁相接收机的仿真电路直接调频电路的振荡器中心频率稳定度较低,而采用晶体振荡器的调频电路,其调频围又太窄。

采用锁相环的调频器可以解决这个矛盾。

其结构原理如图2所示。

图2 锁相环调频电路的原理框图实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外,也就是说,锁相环路只对慢变化的频率偏移有响应,使压控振荡器的中心频率锁定在稳定度很高的晶振频率上。

而随着输人调制信号的变化,振荡频率可以发生很大偏移。

图3 锁相环调频的仿真电路根据图2建立的仿真电路如图3所示。

图中,设置压控振荡器V1在控制电压为0时,输出频率为0;控制电压为5V时,输出频率为50kHz。

这样,实际上就选定了压控振荡器的中心频率为25kHz,为此设定直流电压V3为2.5V。

simulink锁相环pll用法

simulink锁相环pll用法

Simulink中的锁相环(Phase-Locked Loop,PLL)是一种常用的信号处理器件,用于频率和相位同步。

它可以用于许多应用中,例如通信系统、数据转换、时钟恢复和信号重构等。

在Simulink中使用PLL有几个关键的步骤:

1.模拟输入信号:首先需要生成或获取输入信号,这通常是

一个模拟信号或数字信号。

2.创建PLL模块:打开Simulink环境,创建一个新的模型,

在模型中添加PLL模块。

对于PLL模块的创建,可以在

Simulink库中搜索PLL模块并将其拖放到模型中。

3.设置参数:对于PLL模块,需要设置一些关键参数,例如

参考频率(Reference Frequency)、带宽(Loop Bandwidth)、初始相位(Initial Phase)等。

这些参数决定了PLL的性能

和工作方式。

4.连接信号和参考:将输入信号连接到PLL模块,并指定参

考信号。

参考信号可以是外部提供的,也可以是由PLL根

据输入信号生成的稳定参考。

5.仿真和分析:设置好参数并连接信号后,运行模型进行仿

真。

可以观察输出信号的频率和相位与参考信号的同步情

况,并进行性能分析和优化。

需要注意的是,PLL的具体用法和设置参数会因应用和设计需求而有所差异。

Simulink提供了丰富的库和模块,可以根据具体

应用需求选择和配置适当的PLL模块。

还可以通过自定义模块或编写MATLAB脚本来实现更高级的PLL功能。

锁相环设计及其MATLAB仿真

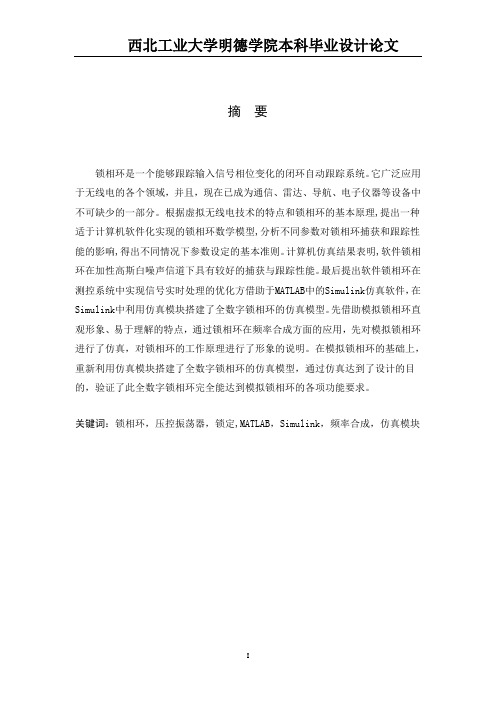

摘要锁相环是一个能够跟踪输入信号相位变化的闭环自动跟踪系统。

它广泛应用于无线电的各个领域,并且,现在已成为通信、雷达、导航、电子仪器等设备中不可缺少的一部分。

根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基本准则。

计算机仿真结果表明,软件锁相环在加性高斯白噪声信道下具有较好的捕获与跟踪性能。

最后提出软件锁相环在测控系统中实现信号实时处理的优化方借助于MATLAB中的Simulink仿真软件,在Simulink中利用仿真模块搭建了全数字锁相环的仿真模型。

先借助模拟锁相环直观形象、易于理解的特点,通过锁相环在频率合成方面的应用,先对模拟锁相环进行了仿真,对锁相环的工作原理进行了形象的说明。

在模拟锁相环的基础上,重新利用仿真模块搭建了全数字锁相环的仿真模型,通过仿真达到了设计的目的,验证了此全数字锁相环完全能达到模拟锁相环的各项功能要求。

关键词:锁相环,压控振荡器,锁定,MATLAB,Simulink,频率合成,仿真模块ABSTRACTPhase-locked loop is a closed loop frequency control system,which functioning is based on the phase sensitive detection of phase difference between the input and output signals of the controlled oscillator.It has been widely used in all aspects in radio field and ,has becomed a indispensable part in communication、radar、nevigation and electronic equipments.But with the disign complexity of phase-locked loop in works,there will meet a lot of datas and a long simulation time if simulating the PLL with SPICE ,what is worse, which need to simulate several times to extract the disign parameters,at that way,the disign term will be extended.With the help of flexibility and palpability of Matlab’s simulink,the behavioral model of DPLL is builded using the block in simulink based on the frequency systhesis.Through the DPLL applicating in frequency systhesis,the principle of phase-locked loop and the work process is simulated. According to the characteristics of the Virtual Radio technology and the basic theory of the Phase Look Loop ( PLL) ,this paper puts forward the mathematicalmodel of the PLL which is suitable for software realization by the computer. In this paper,the influences of the parameters to the cap ture performance and the tracking performance are analyzed, and the basic p rincip le of the parameter setting in different conditions is given. The results of the simulation p rove that the cap ture performance and the tracking performance of Software PLL in AdditiveWhite Gaussian Noise are good. At the last of the paper, the op timized method of the PLL signal realtime p rocessing in the Tracking, Telemetering and Control System is p resented.KEYWORDS: MATLAB, phase-lockedloop, V oltage-controlledoscillator ,locked,simulink, frequency systhesis, simulationmodel。

基于Simulink的取样锁相环非线性分析

其 中 0 为 输 入 的 相 位 信 号 , 为 输 出相 位 信 号 , 为 相

s mpig c ce .Atte s me t , te w y o d ce s te c pue t n i rv n nie r po e is o w - re P L wi a l y ls n h a i me h a s t era e h a tr i me a d mpo e o l a- rp r e ft o od r S L t n t h

Te hnq e a d M e h d c iu n to

基 于 Smuik的取样锁相 环非线性分析 i l n

李 欣

( 南 理 工 大 学 广 州 汽 车 学 院 电子 信 息 工 程 系 , 东 广 州 5 0 0 ) 华 广 18 0

摘 要 :提 出 了采 用 M t b中的仿 真 工 具 箱 S ui aa l i l k建 立二 阶 无 源 比例 积 分 取 样 锁相 环 的近 似 m n 相 位模 型 , 对该 模 型 在 不 同条 件 下进 行 仿 真 。分析 了 时 间常数 、 路 增 益 和 采样 周期 的 改 变对二 阶 并 环

无 源 比例 积 分 取 样 锁 相 环 非 线 性 捕 获 时 间 的 影 响 , 过 二 阶 取 样 锁 相 环 快 速 捕 获 的 方 法 , 出 了 改 善 通 提

二 阶 无 源 比例 积 分取 样 环 的 非 线性 性 能 的 途径 , 对取 样 锁 相环 的研 究与 设 计 有 着积 极 的 意 义 。 关 键 词 :取 样 锁 相 环 ; 线 性 ; i l k; 真 ; 获 时 间 非 Smui 仿 n 捕

锁相环的基本原理和模型

1.锁相环的基本原理和模型在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。

一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。

图1-1 基本锁相环结构鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。

PLL 的每个部分都是非线性的,但是这样不便于分析设计。

因此可以用近似的线性特性来表示PLL 的控制模型。

鉴相器传递函数为:)(Xo Xi Kd Vd -=压控振荡器可以等效为一个积分环节,因此其传递函数为:SKo 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。

综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下:S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,)()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。

2.鉴相器的实现方法鉴相器的目的是要尽可能的得到准确的相位误差信息。

可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。

一般也可以使用乘法鉴相器。

通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。

在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。

同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁相环学习总结通过这段的学习,我对锁相环的一些基本概念、结构构成、工作原理、主要参数以及simulink 搭建仿真模型有了较清晰的把握与理解,同时,在仿真中也出现了一些实际问题,下面我将对这段学习中对锁相环的认识和理解、设计思路以及中间所遇到的问题作一下总结:1. 概述锁相环(PLL )是实现两个信号相位同步的自动控制系统,组成锁相环的基本部件有检相器(PD )、环路滤波器(LF )、压控振荡器(VCO ),其结构图如下所示:2. 锁相环的基本概念和重要参数指标锁相是相位锁定的简称,表示两个信号之间相位同步。

若两正弦信号如下所示:相位同步是指两个信号频率相等,相差为一固定值。

)(sin )sin()()(sin )sin()('t U t U t u t U t U t u o o o o o i i i i i θθωθθω=+==+=当i ω=o ω,两个信号之间的相位差为一固定值,不随时间变化而变化,称两信号相位同步。

当i ω≠o ω,两个信号的相位差,不论i θ是否等于o θ,只要时间有变化,那么相位差就会随时间变化而变化,称此时两信号不同步。

若这两个信号分别为锁相环的输入和输出,则此时环路出于失锁状态。

当环路工作时,且输入与输出信号频差在捕获带范围之内,通过环路的反馈控制,输出信号的瞬时角频率)(t v ω便由o ω向i ω方向变化,总会有一个时刻使得i ω=o ω,相位差等于0或一个非常小的常数,那么此时称为相位锁定,环路处于锁定状态。

若达到锁定状态后,输入信号频率变化,通过环路控制,输出信号也继续变化 并向输入信号频率靠近,相位差保持在一个固定的常数之内,则称环路此时为跟踪状态。

锁定状态可以认为是静态的相位同步,而跟踪状态则为动态的相位同步。

环路从失锁进入到锁定状态称为捕获状态。

其他几个环路工作时的重要概念:快捕带:能使环路快捕入锁的最大频差称为环路的快捕带,记为L ω∆,两倍的快捕带为快捕范围。

捕获带:能使环路进入锁定的最大固有频差,用P ω∆表示,两倍的捕获带为捕获范围。

同步带:环路在所定条件下,可缓慢增加固有频差,直到环路失锁,把能够维持环路锁定的最大固有频差成为同步带,用H ω∆,2H ω∆为同步范围。

o i t t θθθθ-=-)()('oi o i t t t θθωωθθ-+-=-)()()('三者关系为:H P L ωωω∆<∆<∆在理想二阶环的情况下,在捕获状态下,评价捕获性能的主要指标为P ω∆、L ω∆和捕获时间P T 。

计算式如下:3202/2nP P n L T ξωωωξωω∆=∞=∆=∆其中,n ω为自然谐振角频率,后面将介绍n ω在设计环路滤波器时,将与ξ(阻尼系数,由于考虑到不同ξ对多种输入信号的误差响应和输出响应的影响,选取使响应曲线最平稳的最佳值0.707)决定滤波器两个参数的大小,仿真中可通过设定快捕带得到n ω。

从这可以看到,P T 不仅与环路参数有关,而且与初始频差有关,固有频差越大,则需捕获时间就越长。

在同步状态下,重要的指标有稳态相位误差)(∞e θ和H ω∆,环路锁定后,频差等于0,但稳态相差通常会存在,它反映了环路的跟踪精度,稳态相差越小,跟踪精度越高。

理想二阶环条件下,∞=∆H ω。

3. 锁相环的构成及工作原理从锁相环结构图看到,其包括鉴相器、环路滤波器和压控振荡器。

3.1. 鉴相器正弦型鉴相器即一乘法器(有些资料后接LPF ),用于检测环路输入信号相位与输出信号相位间的相位误差)(t e θ,设输入输出信号分别为:作如下变换:通过鉴相器后得到,m K 为相乘系数,这里为1/2。

3.2. 环路滤波器由通过检相器式子看出,检相器输出包含了和频分量和差频分量,通过环路滤波器,由于其具有低通特性,和频分量将被滤除,输出为振荡器的控制信号)(t u c 。

记F(p)为环路滤波器的传递函数,则)()()(t u p F t u d c =。

3.3. 压控振荡器压控振荡器为电压频率变换器,其瞬时频率为 当)(t u c =0时,)(t v ω=0ω。

瞬时相位可以表示为)(sin )sin()(t U t U t u i i i i i θθω=+=)(cos ))(cos()('t U t t U t u o o o o o θθω=+=)()()()()(;)()(2'11t t t t t t t t t t t t o o i o o i o i o i o i i θωθθωθθωθωωωθωωωθωθ+=+=+∆=-=∆+-+=+=)]()(2sin[)]()({sin[***)2/1()()(2121t t t t t U U K t u t u K o o i m o i m θθωθθ+++-=)()(t U t u e d d θ=)()]([)(t u K t u f t c o o c v +==ωω通过以上分析,得到模拟锁相环的相位模型为:相应的数字锁相环的模型为则PLL 的动态方程为4. 数字锁相环的设计及simulink 仿真数字锁相环的设计主要在于环路滤波器和NCO 的设计,而鉴相器则为一简单的数字乘法器。

下面将主要介绍数字环路滤波器和NCO 的设计。

4.1. 数字环路滤波器设计在清楚数字环路滤波器的结构后,数字环路滤波器的系数是设计的主要部分,其结构如下图所示(simulink 仿真图):)(*p /)(dt)(dt )()(2t0t0't u K t t u K t t c o c o o v )(=⎰+=⎰=θωωθ)(sin )p (KF )(p )(p 1t t t e e θθθ-=传输函数为:)1/()(/)()(121--+==z C C k u k u z F d c由PLL 的线性化数字模型得到的传递函数,将N(z)和F(z)代入得到12()121()121[()2](1)121K K C C z K K C z o d o d H z K K C C z K K C zo d o d --+-=--++-+-由PLL 的线性化模拟模型得到传递函数并代入N(s)及F(s),然后进行双线性变换()1/()1)(/2(11--+-=z z T s s )得到22122[4()]2()[()4]()2221[44()](1)[2()8]T T T z T T z n n n n n H z T T z T zn n n ξωωωωξωξωωω--+++-=--++++- 比较两式得到C1、C2,分别为))(44/()(4*)/1())(44/(8*)/1(22221T T T K K C T T T K K C n n n d o n n n d o ωξωωωξωξω++=++=通常d o K K K =取1,ξ取0.707,n ω可由自己设定的快捕带得到,T 为抽样间隔,经计算然后可以求得两参数。

4.2. NCO在介绍NCO 的设计之前先介绍一下DDS 算法。

4.2.1. DDS 算法NCO 一般采用数字相位综合技术(DDS ),该技术主要是由时钟驱动读取三角函数表,基于DDS 的NCO 结构如下图所示:一个N 位字长相位累加器的DDS 的基本结构图如下所示:以单频信号说明DDS 的工作原理,信号为)(cos )2cos()(t U t f U t s o o o θϕ=∆+∏=ϕ∆为初始相位(即前述信号的相位初始值t o ω)以采样频率s f 对信号进行采样,得到离散相位序列ss o s o f f T f kT f k /22k 2)(o ∏=∏=∆∆+∆=∆+∏=θϕθϕθθ∆即连续两次采样间的相位增量,控制θ∆可控制输出信号的频率。

现将正弦函数一周期的相位∏2进行等分,当用N 位字长的相位累加器时,最小等分量为N 2/2∏=δ,若每次相位增量取δ,得到的最低频率增量为N min 2/2/s s o f T f =∏=δ,若频率控制字为M ,则可得到输出信号频率增量为N 2/M 2/M s s f T =∏δ。

可以预见,若M 越大,则相位累加幅度就越大,输出频率也就向目标频率变化越快,落到锁相环范围内捕获时间也就越小。

4.2.2. 设计原理这样就可以清楚地得到NCO 的数学模型。

设NCO 的自由振荡频率为o f ,0)0(2=θ,在相位累加器的字长为N 、采样频率为s f 确定的情况下,可确定所用DDS 频率控制字的初始值和初始相位分别为s o f f M /2o ∏=和s o o f f M /22/2N ∏=∏=∆ϕ,根据环路工作原理,数字环路滤波器输出的控制电压加到NCO 的控制端,来调整输出频率,即当数字环路滤波器输出的数字控制电压为)(k u c 时,相应的频率控制字变化量就为)(k u M c =∆,NCO 输出频率和输出相位为:N N 2/2/M f M f f s o s out ∆+=)()(k k θϕθ∆+∆= )()(''k u K M K k c o o =∆=∆θ式中,N 2/2)(M k ∏∆=∆θ,定义N 2/2s o f K ∏=为NCO 的频率控制增益,单位为rad/(sV)。

NCO 相当于一相位累加器,即一差分方程,转换到Z 域,其传递方程即为)1/()()(11'2---=z z K k u k o c θ。

由此,便可以构造其仿真模型,仿真图如下所示。

5.仿真模型及所遇到的问题5.1.无噪声模型锁相环simulink仿真图如下所示参数设置如表所示:输入信号频率110e3HZ采样频率300e3HZ2*pi*10e3nK0 2C1 8.8844e+004C2 1.3159e+004Simulation time 0.002s 运行模型后得到输入与输出频谱图比较如下:动态看,NCO输出信号品率将从100e3HZ快速牵引到110e3HZ,但是有杂波存在,而输出与输入有20dB的差别,所以也可接受。

) (k ud 和)(kuc分别的波形波如下:这样可以较清楚看到捕获时间为0.0001s左右,理论计算值为1.1256e-005,还是存在差别,这个问题还有待研究。

总体而言,此仿真已起到了数字锁相环仿真的效果,输出信号跟上了输入信号的相位,并有较好的稳定性,入锁之后能够保持同步。

为了更好的看到)(kud 和)(kuc的入锁稳定过程图,和更好的达到入锁效果,我们必须修改参数来达到预想效果,新参数设置如下:输入信号频率 110e3HZ 采样频率300e3HZ n2*pi*10e3 K0 2*3e3 C1 8.4424e+004/300e3 C2 1.3159e+004/300e3Simulation time0.125s)(k u d 和)(k u c 的波形如下:我们这时可以非常清楚的看到在0.122s时达到稳定,此时锁相环快捕入锁。