边界扫描及其描述语言

BSDL边界扫描语言(一)

BSDL边界扫描语言(一)BSDL边界扫描描述语言边界扫描是一个完善的测试技术。

边界扫描在自当联合测试行动组(JTAG)90年代初发明了一种解决方案来测试使用了许多新的印刷电路,正在开发和制造的地方几乎没有或根本没有测试探针板的物理访问。

一旦边界扫描成立后,下一步是制定一个标准的芯片供应商的模型边界扫描设备,工具供应商开发自动化工具,以及为最终用户创建的边界扫描测试的建模语言。

因此,边界扫描描述语言(BSDL)已建立。

BSDL是边界扫描设备的标准建模语言。

它的语法是一个VHDL的子集,它符合IEEE 的规定。

它是由使用边界扫描测试开发人员,设备模拟器,半导体测试仪,电路板级测试,任何人利用边界扫描。

使用的的BSDL促进整个电子行业的一致性。

此外,它使任何边界扫描中的一个有用的,可以理解的,一致的方式和设备的功能规范。

BSDL走出了边界扫描测试哲学的发展。

最初的IEEE 标准的(见[符合IEEE (JTAG接口)])标准描述的边界扫描并于1990年批准发布,并作为结果,使用边界扫描技术开始增长。

该标准的下一次修订在1993年发生。

在1994年进一步修订纳入了IEEE 标准的BSDL。

什么是的BSDL?边界扫描描述语言使用户能够提供的方式,边界扫描在任何特定的设备实施的说明。

由于每个芯片设计趋于应用边界扫描方式略有不同标准,这是一个需要理解的表达,具体和实用的方式测试。

是书面的BSDL在VHDL的子集。

VHDL语言是常用的一种为FPGA 和ASIC设计输入的数字电路电子设计自动化的语言,因此它是与边界因为许多芯片设计扫描是用这种语言进行工作相适应的。

但是的BSDL是一个”子集和标准做法”的VHDL,即VHDL语言的范围,从而对边界扫描应用受到限制。

设计过程中的BSDL有两种语言的主要标准:它很容易使用它是由计算机可解析在一个简单的和毫不含糊的时尚BDSL使设备的使用边界扫描功能,准确和有用的说明。

BSDL 文件是所使用的边界扫描工具,使设备的使用功能,使任何测试性分析测试程序生成,?故障诊断,以及使用。

电子英文术语及解释

术语词汇表术语表ABELABEL是在CPLD设计中曾被广泛使用的一种原始的硬件描述语言ABEL通常被认为在建立高级硬件描述方面不如VHDL或Verilog有效ADC模数转换器一个模拟信号在各个间隔采样并被建模为数字信号AGP高级图形接口关于图形的电压接口标准AllianceAlliance是Xilinx的与第三方供应商配合之协议的名称在此协议下相互共享信息以在Xilinx的工具和其它EDA工具之间建立无缝的接口Alliance软件包包含了Xilinx的实现工具但是这个包没有包括仿真综合和原理图抓取软件如果你在使用Xilinx 的Alliance系列软件这就假定了你在为这些应用使用了第三方EDA供应商的工具analyze分析是用来描述在综合中的语法检查过程的术语ASIC专用集成电路此器件是用户为特定的应用设计的而不是一个诸如微处理器的通用器件ASSP专用标准部件或产品ASIC的别称ATPG自动测试模式产生测试向量生成并在电路中运行以测试这个部件behavioral一个常用来描述HDL或仿真形式的术语行为级HDL是一种未必可综合的系统模型行为级仿真是对源代码RTL或行为级的一种仿真BGA球栅阵列一种非常流行的表贴器件封装它使用网格状的焊球作为它的连接器可以有塑封和陶封两种形式BGA封装以其紧凑的尺寸高的引线数目和较低的感抗使得可以应用在较低的电压场合而倍受关注BIST内建自测试存储器资源特别是RAM的测试功能BitgenBitgen是Xilinx实现工具执行配置这一步的命令行名称参见Configurationbitstream位流bitstream被用来对Xilinx器件进行编程它包含设计者建立的器件布线和逻辑资源内部配置的所有信息block SelectRAM通常是指分块 RAM.Xilinx的块RAM是基于Virtex架构器件中的专用的块RAMXilinx的块 RAM可以存储多达16 千位的数据数据宽度和深度可以变化块RAM是全同步的有适合双端口存取的不同端口每个块可以有独立的时钟使能复位数据输入数据输出和端口宽度BLVDS总线LVDS这个标准允许两个或多个器件之间双向LVDS通信此标准的外部终端电阻与标准LVDS中的是不同的BSCAN边界扫描边界扫描逻辑在生产中被用来测试PCB的互连BSDL边界扫描描述语言 BSDL是在一个IC中如何实现边界扫描逻辑的软件描述边界扫描测试软件接受BSDL描述BUFGCEBUFGCE是Xilinx的原语是Virtex-II时钟管理的一部分BUFGCE 被用来分布高扇出的带时钟使能的时钟信号时钟信号用时钟使能信号来选通无毛刺在当使能信号被禁止时时钟也被禁止BUFGMUXBUFGMUX 是Xilinx的原语是Virtex-II器件中时钟管理的一部分BUFGMUX被用来在两个时钟间实现无毛刺切换BUFTBUFT 是 Xilinx的原语表示一个三态缓冲器carry logic进位逻辑存在于每个slice中是主要用于实现算术逻辑功能的专用逻辑进位逻辑或称进位链在Xilinx器件中垂直分布ChipScope ILAChipScope 集成逻辑分析器ILA)是Xilinx的附加软件可以代替逻辑分析仪来测试和抓取Xilinx器件内部的数据ChipScope ILA 包括两个基本部件在计算机中的ChipScope软件和在芯片中的ChipScope核软件被用来建立触发事件和抓取数据在芯片中的核被用来连接到待测试设计的内部测试节点上器件和软件间信息交互是通过连接到PC和器件上的JTAG口的MultiLinx 电缆或并行电缆IIICLB可配置逻辑块Xilinx 的CLB 是在FPGA内实现大部分逻辑的地方CLB是由slice组成的CMOS互补MOS是实现数字处理器和存储器最为广泛使用的集成电路技术CMOS采用以某种方式连接在一起的PMOS和NMOS晶体管这使得它的功耗比单用PMOS或单用NMOS的电路的功耗要低combinational参见combinatorial Combinational是combinatorial 的另外一种措辞combinatorial组合逻辑用需要持续驱动的门来实现组合逻辑有别于不需要持续驱动的寄存逻辑如果激励信号不保持组合逻辑就不会保持它的值compile一个设计的编译可以出现在不同的位置当你综合HDL时你是将代码编译为硬件网表编译表示代码或一个文件到一个不同格式的转换configuration配置是Xilinx实现过程中的一步在配置这一步将生成用于对器件编程的位流core核通常是指知识产权IP核的功能事先经过了测试可以被很快使用而无需花费太多的工程时间和代价核也可被认为是即插即用的设计CORE Generator system核生成器CORE Generator 系统是Xilinx的软件用于为你的设计生成核这些已经制作好的功能块可以直接例化到你的设计中去它们也可进行功能仿真这些核按照复杂性和价格排列大部分的简单的功能块是免费的也可以进行用户配置块RAM FIR滤波器等等而其它的一些核PCI USB等等需要一定的费用CPLD复杂可编程逻辑器件是一种包含了在逻辑块之间可编程互连的可编程器件一个CPLD通常是由多个互连的PAL构成CPU中央处理单元.CS芯片比例封装CTT中央抽头终端电压接口标准 3.3伏的存储器总线标准DAC数模转换器将数字信号转换为模拟信号daisy chain菊花链是多个Xilinx部件的串接以便通过串行配置方式按次序对每个器件进行编程DCI数字可控阻抗Xilinx的Virtex -II中的 DCI为单端I/O提供了可控阻抗驱动器和片上终端这就可以省去片外的电阻并能提高信号的完整性DCM数字时钟管理器 Xilinx的DCM有四个时钟管理功能块时钟数字延时锁定环CLKDLL数字频率合成器 (DFS)数字移相器DPS和数字扩谱DSSDDR双数据速率使用时钟的两个沿来抓取数据Design Manager设计管理器是一个管理某个Xilinx器件实现的软件在设计管理器中你可以设置实现选项使用其它各种工具管理你的设计实现的版本和子版本.die小片硅晶元以相邻的垂直方向上和水平方向上的划线为边界它包含了制造好了的完整的芯片也称为芯片和微芯片DFT测试设计设计中用于测试内部电路功能和/或集成的电路目的是使器件可以进行自测DLL延时锁定环PLL的数字版本数字式时钟锁定电路比较两个时钟信号并使它们相对齐.DSM深亚微米也被称做二阶效应或三阶效应一个电路中在时延和噪声方面的布线效应EA嵌入阵列ASIC是一种由门阵列和标准胞元组合而成的ASIC晶片包括已部分制作部分门阵列和空白部分与标准的胞元ASIC一样嵌入阵列也允许有用户定制的宏和存储器ECO工程更改定单一旦ASIC被掩膜对掩膜进行修改需要重整re-spin”这需要付一定的费用EDA电子设计自动化就是利用计算机来设计和仿真芯片上的电子线路的性能EDIFEDIF 是工业标准的网表格式equivalency checking一致性检查也被称为形式验证形式验证被用来检查一个电路综合前后的一致性FG微间距球栅阵列封装FIFO先进先出器FIFO通常用一个RAM块来实现一个FIFO被用来以一个速率时钟速率存储数据而以另外一个不同的速率来读数据flash memory一种存储器件可以重新写入数据而且掉电后内容仍被保留Flow Engine流程机制是Xilinx的软件被用来实现通常指布局布线设计和生成配置Xilinx器件的位流文件FoundationFoundation 是Xilinx的软件包它包含了原理图抓取仿真和针对Xilinx器件实现的一整套解决方案footprintfootprint表示封装布局footprint也可指用作IO以及用作电源和地线的引脚的数目FPGA现场可编程门阵列-现场可重编程ICFPGA Compiler IIFPGA Compiler II是由Synopsys公司制作的一个综合工具FPGA ExpressFPGA Express是Synopsys公司制作的一个综合工具FSM有限状态机一个使用需要解决特定问题的操作状态来设计的计算部件这些电路对应用而言是最小化的特定的和优化的状态机控制电路的操作它提供了在合适的时间产生的输出以控制其它的逻辑function generatorXilinx查找表LUT Xilinx的查找表由SRAM制成但它的功能像一个16x1的ROM Xilinx的查找表使用四个输入查找表被置入了基于来自四输入逻辑函数的16个可能的输出的可能的逻辑值查找表也被称为函数发生器gate array门阵列一种使用已部分制作好的圆片的ASIC它只使用布线层的掩膜来定制它的作门阵列的特点是初期成本低开发时间短密度低性能有限在量少的情况下价格便宜这种形式的ASIC正逐步被废弃因为其它的技术在规模和低成本方面已超过它gating门控通常是指门控一个时钟当你门控一个时钟时时钟信号与另外一个信号组合起来产生一个新的时钟信号这是一个不好的设计实践门控时钟会产生毛刺会使你的设计不可靠Xilinx 的Virtex -II器件有无毛刺时钟管理资源可以用它们来产生一个门控时钟参见BUFGMUX和BUFGCEGDSII图形设计系统II在ASIC设计过程中使用的Polygon布局格式global clock buffer全局时钟缓冲器被用来驱动Xilinx器件内部的专用时钟树这些时钟网络被优化以传播贯穿整个芯片的低偏差的高频时钟信号每个部件有四到十六个全局时钟缓冲器全局时钟缓冲器也被称为BUFGgray code格雷编码是指这样的逻辑当它的状态变化时只有一位会变化这可以被用来降低二进制序列引起的毛刺它通常也比二进制编码逻辑更快这是因为它需要更多的寄存器来表示状态但需要解码一个状态的逻辑时仅需要看较少的位就可对所在的状态进行解码GSR全局置位复位全局置位复位是一个专用的布线网络在配置的最后的启动序列期间使用它给出了器件上电时的状态寄存器处于置位或复位状态下这取决于代码全局置位复位可以被用户用来在配置后置位/复位芯片内所有的同步元件在基于Virtex 的器件中不建议采用因为它很慢GTL注射收发逻辑终端电压接口标准GTS全局三态全局三态网络是一个专用的布线网络在配置期间被用来使器件所有的IO引脚在配置期间未被使用的所有的IO处于三态在配置的启动序列期间这个网络被释放然后它可以被用来对处于工作状态下的器件的所有的输出进行三态控制GUI图形用户界面在这个界面中用户可以设定选项以控制如何来优化或实现一个设计HDL硬件描述语言一种用来建模设计和仿真硬件的语言最常用的两种形式是VHDL和VerilogHQ高散热方型扁平封装HSTL高速收发器逻辑电压接口标准是一种1.5伏的总线接口标准IBM国际商用机器公司世界上最大的计算机公司标准胞元ASIC的供应商IBIS输入输出缓冲器信息规范IBIS 是通过V/I数据而无需揭示任何电路/工艺信息就可提供器件的输入/输出特性的一种方法它可以被看作是一个适合数字系统传输线仿真的行为模型规范并且它可应用于大部分的数字元件Xilinx之所以提供IBIS模型而不是SPICE模型是因为SPICE模型含有专利信息IC集成电路计算机芯片的正式名称制作电路的硅片ICE集成电路工程implementation实现是Xilinx所指的包括布局布线进程在内的许多步骤这些步骤包括转换映射布局布线静态时序分析和位流产生用于编程instantiate例化是HDL中的一个术语它表示在代码中放置一个层次块的行为它与在一个原理图中放置一个逻辑符号是同义的Intellectual Property参见IPIO输入和输出是指器件的端口I/O输入和输出是指器件的端口IOB输入输出块Xilinx的IOB被用来与外部信号接口Xilinx的 IOB有一个引脚输入输出缓冲器和寄存器IP知识产权是一大类被法律认定为属于某个组织的专利的无形材料在计算机领域硬件电路软件和文本都是有版权的在一些情况下硬件电路和软件中所使用的算法也可以受专利保护而且大部分的商标名称可以受商标权保护ISE集成综合环境 ISE是Xilinx公司提供的一个软件包它包括了仿真综合和针对Xilinx器件实现的一整套解决方案ISE常常被读成iceJTAG联合测试行动组一种边界扫描技术的IEEE标准latency延迟是处理信息所需要的时钟周期数目Leonard SpectrumLeonardo Spectrum是由Exemplar制作的一种综合工具LFSR线性反馈移位寄存器LFSR使用了一个伪随机计数序列 LFSR非常有用因为它能在比二进制序列更高的时钟频率下运行而且可以重复这个序列LFSR也可被称为伪随机位流生成器或PRBS生成器Libraries Guide库指南是一个软件手册它包含了关于所有的Xilinx宏和原语的一个列表它按照字母顺序排列对于每一个宏/原语都有一个原理图用来显示用于HDL例化的端口名称一个功能描述和一个根据输入而产生期望输出的真值表LM分层金属在集成电路中用于提供布线线路的金属层的数目LOC位置约束位置约束被用来锁定管脚位置或将逻辑放置在芯片的特定位置LogiBLOXLogiBLOX 软件可以用来生成XC4000和Spartan系列器件的一些小规模的核LUT查找表Xilinx的查找表由SRAM制成但它的功能通常像一个16x1的ROM Xilinx的查找表使用四个输入查找表被置入了基于四输入逻辑函数的16个可能的输出的可能的逻辑值查找表也被称为函数发生器LVCMOS低电压CMOSLVDS低电压差分信号 LVDS 是一种差分输入输出标准它需要两个信号线来荷载一个数据位与所有的差分信号标准一样LVDS具有优于单端I/O标准的固有的抗噪能力两个信号线间的电压的摆率约为350毫伏它不需要使用参考电压V REF 或板级终端电压V TT对每一个输入或输出LVDS需要两个管脚LVDS也需要外部的电阻终端LVPECL低电压正射极耦合逻辑LVTTL低电压TTL电压接口标准macro术语宏常可以与核互用参见coremapmap是Xilinx器件实现过程中的一个步骤特别地在映射这一步将网表中的逻辑如果输入网表来自于原理图工具优化成Xilinx 器件资源如LUT寄存器三态缓冲器等等然后将LUT寄存器等打包到slice和IOB中MP微处理器MHz百万赫兹ModelSimModelSim是Model Technology公司制作的一个行为仿真工具MTIModel Technology公司参见ModelSimNCF网表约束文件 NCF是由综合工具产生的用来在综合工具和Xilinx的实现工具间传递约束Netlist网表是组成电路的逻辑门及其互连的一个列表通常是文本形式 Xilinx使用的大部分网表采用 EDIF 或 XNF格式NGDBuildNGDBuild是转换的命令行名称参见 translateNRE非重复性工程成本开发ASIC时付给ASIC供应商的最开始的费用nW纳瓦OFFSET IN是一个覆盖从输入管脚到同步元件之间的路径的时序约束OFFSET OUT是一个覆盖从同步元件到输出管脚之间的路径的时序约束one-hot一位有效编码逻辑是指这样的逻辑其中有一位有效或为高电平而所有的其它位无效或为低电平optimize硬件优化是优化逻辑布尔的行为使得可以有效地利用硬件资源pad-to-pad是一个时序规范覆盖从输入引脚经过组合逻辑到达输出引脚的路径管脚-到-管脚约束不会穿过任何寄存的边界PAL可编程阵列逻辑它是一类包含可编程的与门阵列和预先定义的或门阵列只有与门连接可以被编程的可编程逻辑器件PLD PAL通常被排列好以提供乘积和sum-of-products (SOP)逻辑的表达P&R布局和布线是将逻辑放到硅片中并对逻辑间的信号进行布线以满足时序要求的行为PAR布局和布线是将逻辑放到硅片中并对逻辑间的信号进行布线以满足时序要求的行为PCI外设部件互连是一个通常用于PC机Macintosh计算机和工作站中的外设总线PCI 为CPU和外设部件如视频磁盘网络等等之间提供一个高速的数据通路period同步元件到同步元件的时序规范pipeline流水化一个设计是将寄存器置于组合逻辑间的行为它可以通过牺牲延迟来提高一个设计的吞吐量时钟频率PECL正射极耦合逻辑发送每个数据位需要两个信号线对于每一个输入或输出这个标准指定两个引脚在这两个信号线间的电压摆率约为850毫伏它不需要使用参考电压V REF 或板级终端电压V TT LVPECL需要外部的电阻终端pin locking管脚锁定是将输入输出信号放在部件中特定管脚上的行为因为FPGA是完全可编程的设计者可以将信号放在器件中的任意特定的管脚上注意通常建议在器件中建立水平方向分布上的数据流总线的最低位被放在芯片左右两侧较下部分这常常是因为进位逻辑进位链在芯片中在垂直方向上自下而上分布PLA可编程逻辑阵列它是一类包含可编程的与门和或门阵列与门和或门连接都可以被编程的可编程逻辑器件PLD PLA通常被排列好以提供乘积和sum-of-products(SOP)逻辑的表达Place and Route是将逻辑放到硅片中并对逻辑间的信号进行布线以满足时序要求的行为是Xilinx实现进程中的一步pipelining在组合逻辑间插入寄存器以提高电路的吞吐量性能或时钟频率但是以牺牲延迟为代价的PLD可编程逻辑器件包括FPGA和CPLDPLL锁相环模拟式时钟锁定电路比较两个时钟信号并将它们对齐PQ塑料方型扁平封装PRBS generator参见LFSRpriority encoded是指一种逻辑结构在这种结构中逻辑被级联起来以实现一定逻辑功能通常级联的逻辑并不像用并行结构实现的逻辑那样有效Project Navigator项目导航器是软件程序ISE的图形用户界面GUI在这个图形用户界面GUI中你能够指定综合仿真和实现选项另外在图形用户界面中GUI你可以执行综合仿真和实现的每一项功能RAM随机存取存储器可读写的存储器um微米 (micron)用来度量晶体管和布线线路的几何尺寸regression是指两个或更多相关变量之间的功能关系它常常从一些数据中来经验地确定当其它变量的值被给定时这个关系可以用来预测一个变量的值在硬件系统中回归测试被使用使得不需利用所有可能的测试向量例如对一个两输入的与门有四个可能的可以被应用的逻辑向量回归测试可以只测试这些向量中的一个或两个如果它能正常工作就可以认为这个与门能正确工作revisionXilinx工具的一个子版本代表Xilinx实现选项的一个变化子版本的建立由用户所控制RLOC相对位置约束 RLOC被用来将一些逻辑元件成组放在一起以降低设计中的布线时延通过将逻辑放得靠近在一起将不允许布局布线这一步将属于一起的任何逻辑分开这样就建立起了RPM也就是一片逻辑被放置在与另一片逻辑相对的位置上它不是被硬放置在芯片上的RPM相对放置的宏相对放置的宏利用RLOC约束来将相关的逻辑成组放在一起以便降低与布线相关的数量和时延RTL寄存器传输级是一个通常被用来描述可综合的HDL代码的术语SC标准胞元ASIC ASIC使用标准的逻辑胞元以实现紧凑的封装一个标准胞元ASIC 使用空白的圆片而不是已部分制作好的一个标准胞元ASIC的特点是初期成本高开发时间长可以提供尽可能的最大的密度和最高的性能在量大的时候是最便宜和最有效的scan内部扫描链建立用于测试部件功能的内部移位寄存器SDF标准时延格式 SDF文件被用来传递用于时序仿真的在硬件电路中与逻辑和布线相关的时延信息SDF文件通常与一个用来提供逻辑功能和连接的结构化的HDL文件一起使用.SelectI/OSelectI/O 是Xilinx的专有术语它可以支持与外部器件接口的许多电压阈值电平目前Virtex-II支持19种不同的I/O标准SelectRAMSelectRAM 是指将内部的查找表用做RAM而不是函数发生器SelectRAM也被称作分布式RAM或查找表式RAM每个查找表可以被配置成一个深度为16宽度为1的RAM这个RAM的特点是可以同步写和异步读SelectRAM也可指双端口RAMSelectROMSelectROM是指将内部的查找表用做ROM而不是函数发生器SelectROM也被称作分布式ROM或查找表式ROM每个查找表可以被配置成一个深度为16宽度为1的ROM 这个ROM可以异步读Silicon芯片中使用的基本材料它的原子结构和易获性使得它可以作为一个理想的半导体材料在芯片制作的时候首先从白石英石中提取然后在高温下通过一个化学过程来提纯为了改变它的电学特性在融化状态下将其与其它的化学物质相混合搀杂simulation就是在计算机上执行一个概念设计来模拟实际的功能在硬件系统中在实现硬件之前仿真通过用软件来建模和验证硬件概念的方法来实现simprims仿真原语这些仿真原语被用来为用Xilinx器件实现的一个设计进行时序仿真skew偏差表示信号到达不同终点的时间上的差异slicesSlice存在于CLB中每个slice包含两个查找表和两个寄存器在每个slice中还存在其它的逻辑如多路选择器F5F6F7和F8多路选择器布线和进位逻辑SRAM静态RAM是一种需要电源才能保持其内容的存储器静态RAM不像动态RAM一样需要刷新电路SRL移位寄存器查找表SRL将查找表用做移位寄存器SRL16 是一个SRL宏这个移位寄存器可以实现多达16个时钟周期的串行移位对每个查找表而言SRL 可以实现不带任何复位功能的串行入串行出的单纯的移位寄存器功能然而SRL可以在上电时用数据来初始化在ucf文件中使用INIT属性而且在SRL中的每一个寄存器可以被动态地读取在Virtex-II中宏SRLC16有两个输出可用一个动态可寻址输出和一个最终输出SSTL短线串行收发器逻辑电压接口标准存储器总线接口标准ST以前称为 SGS汤姆生STA静态时序分析时序分析被用来确定一个电路的最差情况下的延时或性能通常这些时延被用来与以时序约束格式提供的时序目标相比较stampStamp模型是板级时序验证的工业标准格式startup启动块在配置阶段被用来控制内部的复位全局写使能和全局三态网络启动块在Virtex 器件中被称作STARTUP_VIRTEX 而在Virtex -II 器件中被称为STARTUP_VIRTEX2Static Timing Analysis参见上面的STAsynchronous同步设计是指这样一种设计它只使用一个时钟时钟的一个沿D触发器和层次的合适应用SynplifySynplify是Synplicity公司制作的一个综合工具synthesis将HDL代码Verilog 或 VHDL编译为电路的硬件描述综合工具通常会生成edif格式的网表synthesizesynthesis的动词形式TI德州仪器公司最大的DSP处理器制造商也是标准胞元和嵌入式阵列ASIC的供应商timing constraints时序约束被设计者用来向Xilinx 实现工具传递一个设计的设计性能目标Xilinx的实现工具是时序驱动的所以在实现过程中实现工具试图对逻辑进行布局布线以满足时序约束translate转换是Xilinx器件实现进程中的一个步骤特别地在转换这一步将所有的输入网表进行合并检查约束以及查找输入网表中的常见问题TTL晶体管传输逻辑它是一个含有以一定方式连接的双极晶体管的数字电路TTL逻辑从数字电路的早期就被广泛使用TTL标识可以出现在不同器件的输入或输出端口上它用来表明是数字电路而不是模拟电路TTM上市时间TWRTWR 文件是由Xilinx的静态时序时序分析工具时序分析器生成的这个文件包含了与加到设计中的时延约束有关的时序时延信息versionXilinx工具中的一个版本代表了输入网表的一个变化这通常代表HDL源代码一个变化或网表的重新综合Verilog一种硬件描述语言 (HDL)VHDL超高速集成电路HDLVITAL通向 ASIC库的VHDL初始库VITAL是用来建立与VHDL语言一起使用的时序仿真模型的工业标准UCF用户约束文件 UCF文件被用来与Xilinx的实现工具交互约束UCF文件是Xilinx所特有的UI用户界面参见GUIUnisim统一的仿真原语这些仿真文件被用来仿真在HDL代码中例化的Xilinx原语uP微处理器Xilinx CoreLib由核生成系统为IP生成的Xilinx的仿真文件。

jtag边界扫描的概念

jtag边界扫描的概念

边界扫描(Boundary Scan)是一种测试技术,用于在集成电路板内进行测试,特别是对于那些无法通过传统的测试方法进行测试的复杂电路板。

它利用在每个芯片的输入输出管脚上增加的移位寄存器单元(Boundary-Scan Register Cell),这些寄存器单元分布在芯片的边界上,被称为边界扫描寄存器。

在JTAG调试中,边界扫描是一个非常重要的概念。

当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制。

对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。

正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

它可以串行地输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制。

一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过TAP(Test Access Port)Controller来完成。

以上内容仅供参考,如需更多信息,建议查阅相关文献或咨询专业人士。

边界扫描

边界扫描背景:早在1985年,几家欧洲的厂商为解决高复杂度IC的测试问题,成立了一个JETAG(Joint European Test Action Group)的组织。

稍后,包含HP(Hewlett Packard)及一些美商公司亦加入了这个组织,该组织更名为JTAG(Joint Test Action Group)。

JTAG发展了BOUNDARY-SCAN 的技术,并于1989年将BOUNDARY-SCAN 的JTAG Rev 2.0 版,移转给电机电子工程师协会(Institute Electrical and Electronic Engineers, IEEE),并于1990年成为IEEE Standard1149.1-1990。

定义:边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。

所谓“边界”是指测试电路被设置在IC器件逻辑功能电路的四周,位于靠近器件输入、输出引脚的边界处。

所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一组串行移位寄存器,这种串行移位寄存器被叫做“扫描路径”,沿着这条路径可输入由“0” 和“1”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确。

结构:引脚:寄存器:1指令寄存器:用来决定是否进行扫描测试和访问数据寄存器操作。

2旁路寄存器:旁路寄存器只有1位,它提供了一条从TDI到TDO之间的最短通道。

当选择了旁路寄存器,实际上没有执行边界扫描测试,它的作用是为了缩短扫描路径,将不需要测试的数据寄存器旁路掉,以减少不必要的扫描时间。

3边界扫描寄存器边界扫描寄存器由大量置于集成电路输入输出引脚附近的边界扫描单元组成。

边界扫描单元首尾相连构成一个串行移位寄存器链,它使用TDI引脚作为输入,TDO引脚作为输出。

在测试时钟TCK的作用下,从TDI加入的数据可以在边界扫描寄存器中进行移动扫描。

设计人员可用边界扫描寄存器来测试外部引脚的连接,或是在器件运行时捕获内部数据。

边界扫描技术和IEEE 1149.1标准

~一

() 2 测试 配 或 t B之间的连线 。 ' C 2边界扫描的硬件结构和 I E 19 1 准 E E 14 . 标 根据 IE 1 标准 , E E 14 1 9 边界扫描设计 的硬 件应 包括以下四个部分 : (1 1测 存取通道( A ) TP ;

( T P控 制 器 ; 2)A

() 3 指令寄存器(r ; i) t () 4 测试数据寄存器组 (D ) TR; 其中测试数 据寄 存 器组 'R又包 括边 缘 扫捕 寄存 器 ( S . 旁路 寄存 器 ( Y 和器 件标 志 寄存 器 I D BB 、 ) B R) ( R 。同时还包 括一个或几个专用 的其他寄存器 。 I ) D

。

收稿 i :0 1 2 3 t期 2 0 —1 —0

维普资讯

边界 扫描技 术和 IE 19. 标 准 E E l4 I

2 [ oI 数 据 , 也可输 出数据 () 2 所有 的寄存器 可连接成一个移位寄存器

( l t n sEg er gC lg , aa U  ̄ rt o B睁 曲晤. aj g 2 1 O E c oi ni ei o e N vl m ' s f er c n n le ei y N nn , 1g ) i C

Aba t hs p P rit le st e t ,  ̄ o y o md I s ̄ :T i a e r u e h e l l g f n m: cu y ̄mia d I t 1 9 1 sa d r n ics e t u &m t u n EE ;1 4 . tn a d a d ds u ss i fn  ̄na , s l

Boundary scan

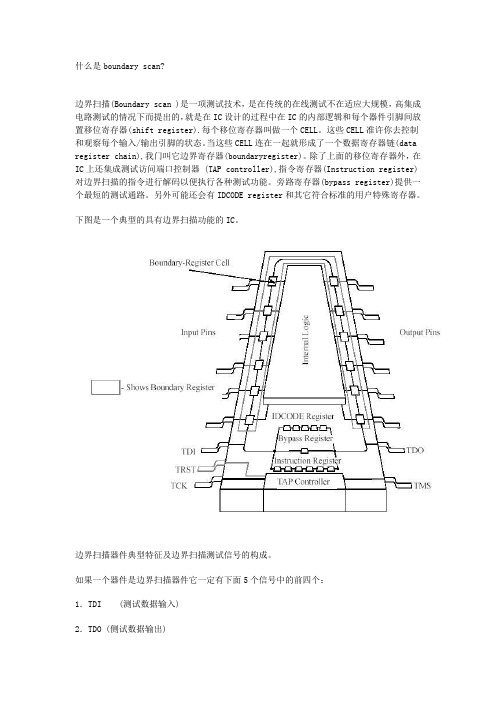

什么是boundary scan?边界扫描(Boundary scan )是一项测试技术,是在传统的在线测试不在适应大规模,高集成电路测试的情况下而提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做一个CELL。

这些CELL准许你去控制和观察每个输入/输出引脚的状态。

当这些CELL连在一起就形成了一个数据寄存器链(data register chain),我门叫它边界寄存器(boundaryregister)。

除了上面的移位寄存器外,在IC上还集成测试访问端口控制器 (TAP controller),指令寄存器(Instruction register)对边界扫描的指令进行解码以便执行各种测试功能。

旁路寄存器(bypass register)提供一个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的用户特殊寄存器。

下图是一个典型的具有边界扫描功能的IC。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果一个器件是边界扫描器件它一定有下面5个信号中的前四个:1.TDI (测试数据输入)2.TDO (侧试数据输出)3.TMS (测试模式选择输入)4.TCK (测试时钟输入)5.TRST (测试复位输入,这个信号是可选的)测试访问端口控制器(TAP controller)TMS,TCK,TRST构成了边界扫描的测试访问端口控制器(TAP controller)。

TAP (the test access port)是一个通用的端口,用来引入控制信号到边界扫描器件(TCK,TMS,TRST*)并且为边界扫描提供串行的输入,输出信号(TDI,TDO)TAP controller是一个16位的状态机,可以通过TMS(test mode selection)和TCK(test clock input)对TAP controller进行编程控制它的状态,TAP controller控制进入指令寄存器(instruction register)和数据寄存器(data register)数据流。

GenRad边界扫描测试解决方案介绍

GenRad边界扫描测试解决方案介绍GenRad边界扫描解决方案包括两个基本组成部分,即BasicSCAN和ScanPathfinder。

BasicSCANBasicSCAN为一需要单独注册的软件产品,该软件用以解决ASICs和复杂的商用边界扫描器件的测试程序生成问题。

BasicSCAN降低了边界扫描器件开发测试矢量的难度,并同时带来以下优势:简化了测试程序的准备及调试过程提高了开路管脚的故障覆盖率缩短了测试程序开发时间降低了测试的复杂程度并减少了所需测试矢量的数目。

一旦BasicSCAN检测到器件具有边界扫描功能,便能够为该器件为该器件在测试程序生成时提供数字测试源模型(Digital Test Source (.DTS)model)。

所有BasicSCAN生成的数字模型均使用相同的测试架构。

其中包括隔离(disable)和预置(inhibit)选择,用以描述如何防止其它器件对被测器件的干扰,并且能够对不同的绕线设置进行处理。

如果做相应的设定,BasicSCAN还可以生成内建自检测试(built--in self test)。

BasicSCAN测试能够检查:器件的指令寄存器(instruction register)捕获的数据。

该数据的错误可以用来判断器件失效或器件贴装错误指令寄存器及边界扫描寄存器(Boundary Scan Register)的长度是否正确IDCODE及USERCODE是否符合期望值测试系统驱动/相应探针与器件输入/输出管脚间的开路。

这种类型的故障能够标识出贴装错误或贴装质量不良的器件器件管脚能够被预置或响应逻辑“0”或逻辑“1”,这样便能够检测出器件输入/输出缓冲区中的任何粘滞型(stuck--at)故障Scan PathfinderScan Pathfinder为一需要单独注册使用的软件选项,该软件能够为符合IEEE1149.1--1990标准的边界扫描链路生成测试程序并已集成至GR Navigate软件中Scan Pathfinder软件:不仅能够测试全部具有测试点的单个IC的开路故障,而且能够对测试点不全,且同时使用非边界扫描器件的被测单板上复杂的相互作用(interaction)及互连(interconnect)中的开路故障进行检测校验边界扫描描述语言(BSDL)模型的语法及结构。

基于边界扫描的测试技术

基于边界扫描的测试技术作者:陈孟东,刘鹏,张辉华来源:《电脑知识与技术》2009年第25期摘要:鉴于工程实践中对边界扫描技术的忽视,分析了它在实际使用中存在的误区,介绍了边界扫描接口的定义及其具体硬件结构,阐述了边界扫描的工作原理。

并分析总结了其用于实际测试中的作用与优点,提出了对边界扫描测试进行优化时需要注意的方面,以利于更好地普及应用。

关键词:联合测试行动组;边界扫描;测试存取口;扫描链路;测试向量中图分类号:TP206文献标识码:A 文章编号:1009-3044(2009)25-7295-03Test Technology Based on Boundary ScanCHEN Meng-dong, LIU Peng, ZHANG Hui-hua(Jiangnan Institute of Computing Technology, Wuxi214083, China)Abstract: Because of the neglect of boundary scan technology in project practice, the misapprehension in practical use is analysed. The definition of boundary scan interface, it’s hardware configuration and it's detailed working principle are introduced. Also introduced is the usage and advantage in practice use. In order to populize it better, the aspects of optimizing it are discussed.Key words: JTAG; boundary scan; test access port; scan link; test vector联合测试行动组于1987 年提出了边界扫描技术, 并于1990 年被IEEE接纳, 形成了IEEE1149. 1 标准。

EDA名词解释

EDA名词解释ASIC:专用集成电路(Application Specific Integrated Circuit)AMPP:Altera宏功能模块和IP核开发伙伴组织(Altera Megafunction Partners Program)BGA:球状矩阵排列(ball grid array)BSDL:边界扫描描述语言(Boundary-Scan Description Language) BST:边界扫描测试(Boundary-Scan Testing)CAD:计算机辅助设计(Computer - Aided Design) CAE:计算机辅助工程(Computer Aided Engineering) CAM:计算机辅助制造(computer-aided manufacturing);中央地址存储器(Central AddressMemory)CAT:计算机辅助测试(computer-aided test)CPLD:复杂可编程逻辑器件(Complex Programable Logic Device) DFT:可测试设计(Design For Test)EAB:嵌入式阵列块(Embedded Array Block)EDA:电子设计自动化(Electronic Design Automation) EDIF:电子设计交换格式(electronic design interchange format) EEPROM:电可擦除可编程只读存储器(Electrically Erasable Programmable Read-OnlyMemory)EPROM:可擦除可编程ROM(Erasable Programmable Read-Only Memory) FPGA:现场可编程门阵列(Field Programmable Gata Array) EPLD:可擦除可编程逻辑器件(Erasable Programmable Logic Device) FPSLIC:现场可编程系统级集成电路(Field Programmable System Level Integration Circu) FSM:有限状态机(Finite State Machine)GAL:通用阵列逻辑(Generic Array Logic)HDL:硬件描述语言(hardware description language)IEEE:电子电气工程师协会(Institute of Electrical and Electronic Engineers) IP:知识产权核(Intellectual Property)ISP:在系统可编程(In System Programmability)JTAG:联合测试行动组(Joint Test Action Group);在EDA领域又称“边界扫描测试技术”,常用于可编程逻辑器件的测试下载LAB:逻辑阵列块(Logic Array Block)LE:逻辑单元(Logic Element)LPM:参数可设置模块库(Library of Parameterized Modules) LUT:查找表(lookup talbe)OLMC: 输出逻辑宏单元(Output Logic Macro Cell)OTP:一次性可编程(One Time Programmable)PAL:可编程阵列逻辑:(Programmable Array Logic)PCB:印刷电路板PGA:可编程门阵列(Programmable Gate Array)PIA:可编程连线阵(Programmable Interconnect Array) PLA:可编程逻辑阵列(Programmable Logic Array)PLD:可编程逻辑电路(Programable Logic Device)PROM:可编程序只读存储器(Programmable Read-Only Memory) ROM:只读内存(Read-Only Memory)SRAM:静态随机存储器(Static Random Access Memory)RTL:寄存器传输级(Register Transport Level) SOC:单芯片系统(System on a Chip) SOPC:片上可编程系统(System On Programmable Chip) UART:通用异步收发器(Universal Asynchronous Receiver,Transmitter)VHDL:超高速集成电路硬件描述语言(Very High Speed Integrated Circuits HardwareDescription Language)UES:用户电子标签(User Electronic Signature)ASIC:专用集成电路CPLD:复杂可编程逻辑器件EAB:嵌入式阵列块EDA:电子设计自动化FPGA:现场可编程门阵列GAL:通用阵列逻辑HDL:硬件描述语言IEEE:电子电气工程师协会IP:知识产权核JTAG:联合测试行动组LAB:逻辑阵列块LPM:参数可设置模块库LUT:查找表PLD:可编程逻辑器件RTL:寄存器传输级SOPC:可编程片上系统VHDL:超高速集成电路硬件描述语言。

边界扫描的原理及应用

边界扫描的原理及应用1. 引言边界扫描是一种常见的图像处理技术,用于检测和提取图像中物体的边界。

在计算机视觉、图像处理和模式识别等领域,边界扫描被广泛应用于目标检测、物体测量和图像分割等任务。

本文将介绍边界扫描的基本原理,以及其在实际应用中的一些例子。

2. 边界扫描的原理边界扫描的原理基于图像的灰度变化。

在图像中,物体的边界通常具有明显的灰度变化。

边界扫描算法通过分析图像中灰度的变化来检测边界。

边界扫描通常分为以下几个步骤:2.1 图像预处理在边界扫描之前,需要对图像进行预处理,以便提高边界的检测效果。

预处理步骤可以包括图像去噪、灰度化、平滑滤波等。

这些步骤的目的是减少图像中的噪声,并使边界更加明显。

2.2 边缘检测边缘检测是边界扫描的核心步骤。

它通过分析图像中灰度的变化来确定边界的位置。

常用的边缘检测算法包括Sobel算子、Canny算子、拉普拉斯算子等。

这些算子能够在图像中检测出灰度变化较大的区域,从而确定物体的边界。

2.3 边界提取边界提取是根据边缘检测的结果,提取出物体的实际边界。

在边界提取过程中,可以使用一些形态学操作来平滑边界的形状,以及去除噪声。

常用的形态学操作包括膨胀、腐蚀、开运算和闭运算等。

3. 边界扫描的应用边界扫描在许多领域中都有广泛的应用。

以下是一些边界扫描应用的例子:3.1 目标检测边界扫描可以用于目标检测,即通过边界提取来确定图像中是否存在特定的目标。

例如,在交通监控系统中,可以使用边界扫描来检测车辆或行人的位置。

3.2 物体测量边界扫描可以用于物体测量,即通过测量边界的长度、面积或形状来获得物体的尺寸信息。

例如,在工业生产中,可以使用边界扫描来测量产品的尺寸,以进行质量控制。

3.3 图像分割边界扫描可以用于图像分割,即将图像分割为不同的区域或物体。

例如,在医学图像处理中,可以使用边界扫描来分割肿瘤或病变区域,以便进行疾病诊断。

3.4 视觉导航边界扫描可以用于视觉导航,即通过检测环境中的边界来确定机器人或车辆的位置。

JTAG边界扫描测试技术原理

4.9 边界扫描的主要应用-PPT

Class 1 Pure scan nets. Class 2 Partial scan nets that have at least one scan driver, one scan receiver, and one non-scan device lead. Class 3 Nets where scan out-puts or tester chan-nels drive non-scan inputs. Class 4 Boundary-scan inputs connected to power or ground. Class 5 Non-scan nets with no tester access. Class 6 TAP nets.

2 边界扫描器件

2.1 边界扫描器件的结构 2.2 测试存取通道 2.3 边界扫描寄存器单元结构 2.4 指令寄存器单元结构 2.5 TAP控制器 2.6 指令寄存器 2.7 数据寄存器组

3 测试指令

第三页第,二共页35页。

课程目录

4 主要应用(ICT)

4.1 TAPIT 4.2 BICT 4.3 VIT 4.4 VCCT 4.5 器件功能(Intest)测试 4.9 PLD编程

第二十一第页二,十页共35页。

4.3 边界扫描的主要应用-BICT

第二十二第页二十,一共页 35页。

4.4 边界扫描的主要应用-BICT

BICT:BoundaryScan In Circuit Test

需要BS器件的管脚有ICT测试点 可以测试到器件管脚的开路 可以测试到器件管脚的短路

第二十第三二页十,二共页35页。

(0000000111), "& (0000001010), "& (0000001011)";

边界扫描技术

标准边界扫描结构

测试存取口(TAP)

• • • • • • 由四个专用引脚组成: 测试数据输入(Test Data In TD I) 测试数据输出(Test Data Out TDO ) 测试模式选择(Test Mode Select TM S ) 测试时钟(Test Clock TCK )。 (另有一个TRST* 为可选)

BSDL语言

• BSDL语言是硬件描述语言的一个子集,可以用 来对边界扫描器件的边界扫描特性进行描述, 主要用来沟通边界扫描器件厂商、用户与测试 工具之间的联系。 • 其应用包括:厂商将BSDL文件作为边界扫描器 件的一部分提供给用户;BSDL文件为自动测试 图形生成(ATPG)工具测试特定的电路板提供 相关信息;在BSDL的支持下生成由IEEE1149.1 标准定义的测试逻辑。 • 现在,BSDL语言已经正式成为IEEE1149.1标准 文件的附件。

边界扫描工作方式

• • • • 内部测试方式 外部测试方式 采样测试方式 电路板正常工作方式

外部测试原理

• 边界扫描外部测试是完成对电路板上的互 连故障进行测试诊断,基本思想是在靠近 器件的输入输出管脚处增加一个移位寄存 器单元。在测试期间,这些寄存器单元用 于控制输入管脚的状态(高或低),并读 输出管脚的状态,利用这种基本思想可以 测试出电路板中器件互连的正确性。在正 常工作期间,这些附加的移位寄存器单元 是“透明” 的,不影响电路板的正常工作。

N输入/N输出系统

一般N输入/N输出系统静态系统

• 上述过程可以通过一个简单线性方程:

Y=D X

其中,X和Y分别代表输入和输出矩阵,D为 系统特征矩阵。 系统的故障诊断问题转化为已知Y和X矩阵求 D的辨识问题,即:矩阵求逆过程。

边界扫描介绍

地址:北京市海淀区知春路 108 号豪景大厦 C1501

邮编:100086

应用范围:

准确的测试线路的开短路 解决PCB测试点减少的问题(针对于物理探测点少) 测试晶片的焊接问题 (特别是BGA) 可以直接在板上通过边界扫描芯片对可编程晶片进行编程(包括FLASH和CPLD等) 对新产品的测试使用时间短 快速生产测试可以节省测试时间 高级与快速板卡修理 测试和技术再利用 (产品周期), 随时 –随地测试 – 无需培训 (运行测试)

联系人:赵栓平 电话:86-10-62102917 手机:13146577482

E-mail: zhaoshuanping1981@

地址:北京市海淀区知春路 108 号豪景大厦 C1501

邮编:100086

内部故障定位浏览器:

通过内部故障定位器准确的反应了当前电路板的情况,无需输入复杂的指令来进行操 作,通过接口信号传输利用扫描,可以快速的对当前所反映出的错误来进行维修.

美国ASSET InterTech:

美国 ASSET InterTech 边界扫描公司是一家有 13 年历史,专业从事边界扫描技术开发与 研究的公司,其开发的边界扫描工具在销售市场的占有率第一,并且与摩托罗拉,诺基亚, 思科等知名公司有着长期良好的合作关系,在边界扫描项目中连续三年获得 Best in Test 大奖,参与(IEEE1149.1, 1149.4, 1532,1149.6,IJTAG)标准的制定,在业内享有良好的口 碑和信誉。

联系人:赵栓平 电话:86-10-62102917 手机:13146577482

E-mail: zhaoshuanping1981@

地址:北京市海淀区知春路 108 号豪景大厦 C1501

边界扫描(boundaryscan)

边界扫描(boundaryscan)边界扫描(Boundary scan )是⼀项测试技术,是在传统的在线测试不在适应⼤规模,⾼集成电路测试的情况下⽽提出的,就是在IC设计的过程中在IC的内部逻辑和每个器件引脚间放置移位寄存器(shift register).每个移位寄存器叫做⼀个CELL。

这些CELL准许你去控制和观察每个输⼊/输出引脚的状态。

当这些CELL连在⼀起就形成了⼀个数据寄存器链(Data Register Chain),我们叫它边界寄存器(Boundary Register)。

除了上⾯的移位寄存器外,在IC上还集成测试访问端⼝控制器 (TAP controller),指令寄存器(Instruction Register)对边界扫描的指令进⾏解码以便执⾏各种测试功能。

旁路寄存器(bypass register)提供⼀个最短的测试通路。

另外可能还会有IDCODE register和其它符合标准的⽤户特殊寄存器。

边界扫描器件典型特征及边界扫描测试信号的构成。

如果⼀个器件是边界扫描器件它⼀定有下⾯5个信号中的前四个:1.TDI (测试数据输⼊)2.TDO (侧试数据输出)3.TMS (测试模式选择输⼊)4.TCK (测试时钟输⼊)5.TRST (测试复位输⼊,Optional)TMS,TCK,TRST构成了边界扫描测试端⼝控制器(TAP controller),它负责测试信号指令的输⼊,输出,指令解码等,TAP controller是⼀个16位的状态机,边界扫描测试的每个环节都由它来控制。

在后续的⽂章中还会向⼤家介绍边界扫描的其它⽅⾯。

边界扫描为开发⼈员缩短开发周期,并且提供良好的覆盖率和诊断信息。

在不了解IC内部逻辑的情况下快速的开发出优秀的测试程序。

在未来的测试领域,边界扫描将会得到⼴泛的应⽤。

边界扫描测试发展于上个世纪90年代,随着⼤规模集成电路的出现,印制电路板制造⼯艺向⼩,微,薄发展,传统的ICT 测试已经没有办法满⾜这类产品的测试要求。

边界测试技术原理

4.7 边界扫描的主要应用-VCCT

4.8 边界扫描的主要应用-VCCT

VCCT:Virtual Component Cluster Test

4.10 边界扫描的主要应用-PPT

PPT:Parallel Port Test

通 过 计 算 机 并 口 进 行 BS测 试 , 不 需 要 其 他 任 何 设 备 可 以 测 试 到 5种 类 型 的 网 络 : 纯 粹 的 BS器 件 之 间 的 网 络 ( VIT) ; VC C T的 网 络 ; 上 下 拉 的 网 络 ; 有 测 试 点 的 网 络 ; TAP 口 的 网 络 。

5.1 边界扫描设计规范

JTAG 管脚上下拉须符合规 范,且都有测试点。 尽可能使用 2× 5PIN 插 座。 尽可能连成一条菊花链。 应能保证菊花链的信号质 量。 DKBA01-200101-010 《 JTAG 接口电路设计规 范》 DKBA3551-2001.08 《 ICT 可测性设计规范》

0 0

0

0

2.5 TAP控制器

TAP 控 制 器 是 16-states 的 有 限 状 态 机 TAP 控 制 器 的 状 态 在 TCK 的 上 升 沿 变 化 TAP 控 制 器 在 上 电 时 进 入 逻 辑 复 位 状 态 Shift-IR state 扫 描 IR , TDO 输 出 有 效 Shift-DR state 扫 描 DR , TDO 输 出 有 效 其 它 状 态 下 TDO 输 出 无 效

3.4 BYPASS指令的执行

边界扫描及其描述语言

7.2IEEE 1149.1 JTAG 先进的边界扫描& 描述语言(BSDL)7.2IEEE 1149.1 JTAG 先进的边界扫描& 描述语言(BSDL)专用扫描单元和引腿单元时序/ 连线约束单元延迟测量边界扫描描述语言 小结仅观察扫描单元仅观察扫描单元控制& 观察扫描单元控制& 观察扫描单元双向引腿双向引腿三态引腿—1个使能引腿控制三态引腿—1个使能引腿控制违法单元的应用违法单元的应用数据非-倒置要求数据非-倒置要求系统数据非-倒置系统数据非-倒置单元延迟约束单元延迟约束TCK下降沿之间的延迟和器件输出引腿的变化可能是歪斜的避免同时输出开关减小功耗或避免烧毁具有锁存并行输出的边界扫描寄存器单元可设置到逻辑0或1当进入Test-Logic-Reset TAP 控制器状态时在Test-Logic-Reset状态的第一个TCK下降沿设置和保持时间设置和保持时间延迟测量延迟测量传播延迟传播延迟延迟测量方法延迟测量方法板级总线测试板级总线测试测试老化问题采用的电路测试老化问题采用的电路边界扫描描述语言(BSDL)的用途边界扫描描述语言(BSDL)的用途 便于描述的部件测试逻辑信息的通信: 公司和CAD 工具之间自动测试矢量生成器所采用综合工具综合测试逻辑所测试不能作为模拟模型不能描述电压, 电流, 或时序 VHDL 的子集对特定的VHDL 工具必须修改BSDL可描述的特点BSDL可描述的特点可描述的:边界扫描寄存器的长度&结构.任选的TRST引腿的有效性TAP 引腿的物理定位指令代码器件标识码不可描述的:TAP 控制器状态图旁路寄存器器件标识寄存器的长度SAMPLE / PRELOAD, BYPASS, EXTEST指令的存在用户定义指令的工作BSDL 描述构成BSDL 描述构成主体(Entity )描述–组成特殊测试逻辑参数 标准VHDL组件(package )& 组件体(package body )定义BSDL VHDL的子集通常用于定义边界扫描单元的类型用户专用的VHDL组件& 组件体BSDL 例子BSDL 例子entity diff isgeneric (Physical_Pin_Map: string:= “Pack”); port ( TDI, TMS, TCK: in bit;TDO: out bit; IN1, IN2: in bit;OUT1: out bit; OUT2: buffer bit;OUT3: out bit_vector (1 to 8);OUT4: out bit_vector (4 downto 1);BIDIR1, BIDIR2, BIDIR3: inout bit;GND, VCC: linkage bit);use STD_1194_1_1994.all;attribute BOUNDARY_REGISTER ofdiff:entity is ...Pin 描述Pin 描述Standard USE statement (required):use STD_1149_1_1994.all;PIN Types:in(input-only)out(may be tri-state or open-collector)buffer(active, 2-state, always driven)inout(bidirectional)linkage(power, ground, analog, non-connect) Relate logical signals to package physical pins Group ports --differential voltage or current pairs (one signal is always complement of other)TAP 描述TAP 描述TAP包含的逻辑信号指出输入端口逻辑值使能JTAG兼容(部件可遵循JTAG 或不遵循)指令寄存器描述:长度操作代码–增加任选的指令从位矢量影射为指令操作代码定义专用指令在Capture-IR控制器状态下(2 LSB’s 总是“01”) 指出俘获的位矢量IDCODE和USERCODE寄存器内容扫描单元定义扫描单元定义定义边界扫描寄存器单元的存在和长度–类型包括: INPUT--control & observe, observe-onlyCLOCK--cell at clock inputOUTPUT2--drives 2-state outputOUTPUT3--drivers 3-state outputCONTROL--controls 3-state outputCONTROLR--disabled in Test-Logic-ResetstateINTERNAL--not associated with digital pin BIDIR--reversible cell for bidirectional pinOBSERVE_ONLY--single input observe-only cell定义访问寄存器的指令小结小结边界扫描标准已经成为基本的方法--针床测试仪已不适合现代电路板和器件测试支持BIST, ATE的外测试和电路内测试等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7.2IEEE 1149.1 JTAG 先进的边界扫描& 描述语言(BSDL)7.2IEEE 1149.1 JTAG 先进的边界扫描& 描述语言(BSDL)

专用扫描单元和引腿

单元时序/ 连线约束

单元延迟测量

边界扫描描述语言 小结

仅观察扫描单元仅观察扫描单元

控制& 观察扫描单元控制& 观察扫描单元

双向引腿双向引腿

三态引腿—

1个使能引腿控制

三态引腿—1个使能引腿控制

违法单元的应用违法单元的应用

数据非-倒置要求数据非-倒置要求

系统数据非-倒置系统数据非-倒置

单元延迟约束

单元延迟约束

TCK下降沿之间的延迟和器件输出引腿的变化可能是歪斜的

避免同时输出开关减小功耗或避免烧毁

具有锁存并行输出的边界扫描寄存器单元

可设置到逻辑0或1

当进入Test-Logic-Reset TAP 控制器状态时

在Test-Logic-Reset状态的第一个TCK下降沿

设置和保持时间设置和保持时间延迟测量

延迟测量

传播延迟

传播延迟延迟测量方法

延迟测量方法

板级总线测试板级总线测试

测试老化问题采用的电路测试老化问题采用的电路

边界扫描描述语言(BSDL)的用途

边界扫描描述语言(BSDL)的用途 便于描述的部件测试逻辑信息的通信: 公司和CAD 工具之间

自动测试矢量生成器所采用

综合工具综合测试逻辑所测试

不能作为模拟模型

不能描述电压, 电流, 或时序 VHDL 的子集

对特定的VHDL 工具必须修改

BSDL可描述的特点

BSDL可描述的特点

可描述的:

边界扫描寄存器的长度&结构.

任选的TRST引腿的有效性

TAP 引腿的物理定位

指令代码

器件标识码

不可描述的:

TAP 控制器状态图

旁路寄存器

器件标识寄存器的长度

SAMPLE / PRELOAD, BYPASS, EXTEST指令的存在

用户定义指令的工作

BSDL 描述构成

BSDL 描述构成

主体(Entity )描述–组成特殊测试逻辑参数 标准VHDL组件(package )& 组件体(package body )

定义BSDL VHDL的子集

通常用于定义边界扫描单元的类型

用户专用的VHDL组件& 组件体

BSDL 例子

BSDL 例子

entity diff is

generic (Physical_Pin_Map: string:= “Pack”); port ( TDI, TMS, TCK: in bit;

TDO: out bit; IN1, IN2: in bit;

OUT1: out bit; OUT2: buffer bit;

OUT3: out bit_vector (1 to 8);

OUT4: out bit_vector (4 downto 1);

BIDIR1, BIDIR2, BIDIR3: inout bit;

GND, VCC: linkage bit);

use STD_1194_1_1994.all;

attribute BOUNDARY_REGISTER of

diff:entity is ...

Pin 描述

Pin 描述

Standard USE statement (required):

use STD_1149_1_1994.all;

PIN Types:

in(input-only)

out(may be tri-state or open-collector)

buffer(active, 2-state, always driven)

inout(bidirectional)

linkage(power, ground, analog, non-connect) Relate logical signals to package physical pins Group ports --differential voltage or current pairs (one signal is always complement of other)

TAP 描述

TAP 描述

TAP包含的逻辑信号

指出输入端口逻辑值使能JTAG兼容(部件可遵循JTAG 或不遵循)

指令寄存器描述:

长度

操作代码–增加任选的指令

从位矢量影射为指令操作代码

定义专用指令

在Capture-IR控制器状态下(2 LSB’s 总是“01”) 指出俘获的位矢量

IDCODE和USERCODE寄存器内容

扫描单元定义

扫描单元定义

定义边界扫描寄存器单元的存在和长度–类型包括: INPUT--control & observe, observe-only

CLOCK--cell at clock input

OUTPUT2--drives 2-state output

OUTPUT3--drivers 3-state output

CONTROL--controls 3-state output

CONTROLR--disabled in Test-Logic-Reset

state

INTERNAL--not associated with digital pin BIDIR--reversible cell for bidirectional pin

OBSERVE_ONLY--single input observe-only cell

定义访问寄存器的指令

小结

小结

边界扫描标准已经成为基本的方法--

针床测试仪已不适合现代电路板和器件测试

支持BIST, ATE的外测试和电路内测试等。

目前已经得到广泛的应用,如ASIC、FPGA和

CPLD;VLSI、PCB、MCM、系统。

2004/5/25北京大学微电子学研究院21。