音响对管试用笔记

音箱元件配件知识点总结

音箱元件配件知识点总结音箱元件配件是构成音箱系统的重要组成部分,它们的质量和性能直接影响着整个音箱系统的音质和效果。

对于音箱爱好者和从业人员来说,了解音箱元件配件的知识是非常重要的。

本文将从音箱元件配件的基本原理、类型、选购和维护等方面进行总结,希望能帮助读者更好地了解和应用音箱元件配件。

一、音箱元件配件的基本原理1. 音箱元件配件的作用音箱元件配件是音箱系统的重要组成部分,主要包括音箱箱体、喇叭单元、分频器、线材、声学棉等。

它们各自承担着不同的功能,共同构成了完整的音箱系统。

1)音箱箱体:用来固定和保护喇叭单元,同时起到隔音和散射的作用,对音箱系统的声音特性有很大的影响。

2)喇叭单元:是音箱系统的声音发声装置,主要负责将电信号转换成机械振动,产生声音。

3)分频器:用来将音频信号分成不同频段,分别送到对应的喇叭单元,以实现不同频段的音频处理。

4)线材:用于连接各种音频设备,传输音频信号。

5)声学棉:用于吸收和隔离声音,在音箱系统中起到调整音响效果的作用。

2. 音箱元件配件的工作原理不同的音箱元件配件有着不同的工作原理,下面简单介绍一下它们的工作原理:1)音箱箱体的工作原理:音箱箱体通常采用压音技术,通过合理的箱体结构设计和选择合适的材料,可以有效地减少共振,提高箱体的结构刚度和密封性,从而减小箱体的声学失真。

2)喇叭单元的工作原理:喇叭单元采用电磁感应原理,当有音频信号输入时,由音圈和磁铁组成的振动系统将电信号转换成磁场效应,驱动锥形振膜产生机械振动,进而产生声音。

3)分频器的工作原理:分频器采用电子滤波原理,对输入的音频信号进行频率分割,分别输出不同频段的音频信号给对应的喇叭单元,使得不同频段的音频信号得到合理的处理和放大。

4)线材的工作原理:线材主要有传输音频信号的作用,其工作原理主要是通过导体传导电流的方式将音频信号从音源传输到喇叭单元。

合理选用高品质的线材可以减小传输损耗和提高音质。

5)声学棉的工作原理:声学棉可以有效地吸收和隔离声音,减小音响系统中的共振和回声,对声音特性的调整起到很大的作用。

如何用三垦大功率音响对管2SA2l5l2SC6011制作一款500W高性能功放电路

如何用三垦大功率音响对管2SA2l5l2SC6011制作一款500W高性能功放电路本人获得《无线电》杂志赠送的三垦大功率音响对管2SA2l5l/2SC6Oll,并应用这两对大功率管,设计出了一款高性能500W大功率功放电路,电路如下图所示,印制板图如下图所示。

全电路由输入级、电压放大级、缓冲变换级、功率预放级和功率输出级等电路组成,各级间还设有电流负反馈电路,使音质得到进一步的改善,不失真输出功率可达500W以上。

它可广泛应用于学校、舞厅、影院、车站等大型公共音响场所,现介绍给大家。

工作原理输入级由VT1-VT3组成带射极恒流源的差分放大器,由VD2-VD4的正向导通电压作基准电压提供给VT3,而VD2-VD4的供电又由VT4及外围元件组成的恒流源提供,提高了输入级的稳定性,并具有较高的共模抑制能力,对于电网电压的变化、电网干扰、电位漂移、温度漂移等都有较强的抑制作用,并能很好地消除“厄雷效应(晶体管VCE的变化引起结电容的变化),输入管静态电流取1.5mA以保证足够的动态。

调RP2可以改变输入级静态电流的大小。

电压放大级是由VT5与VT6组成共基极电路,这种电路多用于宽带放大器,其电流放大倍数略小于1,但电压增益并不比共发射极低,并具有极好的高频特性,调RP4可以改变电压放大级电流的大小,本级电流取为5mA一6mA,VT7、VT8是它的镜像负载。

由于电压放大级的输出阻抗较高,故加入VT1O、VT11作为缓冲级进行阻抗匹配,推动了着名的场效应对管K214、J77组成的功率预放级,并且有较大的预放电流带动功率输出级(在4mA以上)。

此处加K214、J77对管,既起到功率预放的作用,又可使级间阻抗得到变换,提高放大器带负载的能力。

末级功率输出采用了4只三垦大功率对管2SA2l5l/2SC6Oll两两并联推挽的放大形式,能充分发挥出三垦大功率管音色温暖的特色,同时也提高了输出功率。

在功率输出级公共点处还按有到输入级的电流负反馈电路,使电路更加稳定、理想与实用。

音响设备操作手册

音响设备操作手册音响设备很多种,对于我们音响师来说要把每一台音响设备都调整好,我们说的人为操作故障主要发生在演出期间,如:无声、断音、回输、噪音等多种,下面我们就逐一讲一下容易发生人为操作故障的常用音响设备:◆◆调音台◆◆我们一般把调音台比喻成一套音响系统的心脏或大脑,因此调音台也是产生人为操作故障最多的音响设备,调音台的人为操作故障一般表现为:无声、声音很小、声音失真、声音忽大或忽小、严重回输、明显噪音等等。

1、调音台通道电平衰减开关有的调音台在增益旋钮前增加了一个20dB左右的电平衰减转换开关,当CD等音源从高阻端口输入进来后,由于电平较高,可能需要按下此转换开关把音源信号衰减20dB才合适,但有些音响师在演出时要是不小心把这个开关按了起来,那就是:老板很生气,后果很严重了!这时的声音信号没有经过衰减突然大了20dB,后果可想而知,轻者全部听众会吓得从椅子上蹦起来,重者部分音响设备会当场报销,因此我们在对每一个旋钮或开关进行调整时都要有清晰、明确的目的,不要盲目操作。

2、调音台增益调整有些音响师不知道通道增益的重要性,对此旋钮信手乱调,有时候把增益旋钮关掉,甚至还同时按下了20dB电平衰减开关,想下这时候的声音会有多么小?根本谈不上音乐的信噪比和动态了,如果对话筒通道也如此思路调整,那歌手只有自认倒霉了,就是喊破天也不会有高昂具备穿透力的歌声出来;当然也有些音响师喜欢把增益调到很大,对于音乐还好,最多是显得音乐硬邦邦的,但歌手可就惨了,稍微一大声就像洪水冲破了堤坝一样显得无法控制,高昂的歌声会变得像破锣或爆豆一样的嘈杂,因为此时电平太大信号已经严重失真了,另外这种情况下话筒还会经常回输。

由此可见增益之重要,搞不好就会造成演出期间事故。

3、调音台均衡组调整调音台顾名思义主要是用来调整音色的,调整音色主要还是要靠均衡组,说来很简单,无非就是高中低音再加上几个相应的选频旋钮,正常操作下虽然音色不一定就会很好,但也不会发生演出事故,但有些音响师对均衡旋钮有时候大胆地转来转去,我看到这样的音响师都会觉得心惊,如果把低音加到很大,整个功放和音箱的负担就大大增加了,可能会损坏设备,同时声音也会很容易失真;如果中音高音加到很大,那么高音喇叭就危险了,总之提升均衡旋钮要有个度,过度提升会产生不可预期的故障。

常用音响功放对管资料,功率管并联大管配对问题探讨

常用音响功放对管资料,功率管并联大管配对问题探讨功放对管有C5198/A1941,2SC5200/2SA1943,2SC3280/2SA1301,2SC3281/2S A1302,2SC3858/2SA1494D718 NPN 120V8A80W/ B688 PNP 120V8A80W 如果没有散热器的话,可能连5W都承受不了。

但加上理想散热器的话可以使用到极限的80W,但这时的性能肯定大受影响,也很容易损坏。

一般使用不应超过50W。

大功率音响配对管GT20D101/GT20D201 (东芝250V20A180W)K1530/J201 (东芝200v12A200W)K1529/J200 (东芝180V10A150W)K1058/J162 (日立160V7A100W)K405/J115 (东芝160V8A100W)K133/J48 (日立金封120V7A100W)K413/J118 (日立140V8A100W)A1186/C2837 (三肯150V10A100W)A1694/C4467 (三肯160V8A80W)A1695/C4468 (三肯140V10A100W)A1215/C2921 (三肯160V15A150W)A1216/C2922 (三肯180V17A200W)A1295/C3264 (三肯230V17A200W)A1494/C3858 (三肯200V17A200W)A1492/C3856 (三肯180V15A130W)A1491/C3855 (三肯140V10A100W)A1301/C3280 (东芝160V12A120W)A1516/C3907 (东芝180V12A130W)A1941/C5198 (东芝140V10A100W)2SA1942/2SC5199(东芝180V12A120W30MHz)A1943/C5200 (东芝230V15A150W)A1264/C3181 (东芝120V8A80W)A1265/C3182 (东芝140V10A100W)A1633/C4278 (罗姆150V10A100W)A1075/C2525* (120V12A120W)B688/D718 (东芝120V8A80W)B817/D1047 (三洋160V12A100W)MJ15024/15025 (摩托罗拉250V16A250W) MP1620/MN2488SAP15N/SAP15P (三肯160V15A150W)中功率音响配对管K2013/J313 (东芝180V1A25W)K214/J77 (日立160V0.5A30W)A1837/C4793 (东芝230V1A20W)A1859/C4883 (三肯150V2A20W)A1930/C5171 (东芝180V2A20W)A1306/C3298 (东芝160V1.5A20W)A1360/C3423 (东芝150V15mA5W)B649/D669 (日立160V1.5A20W)2SC2275/2SA985 (东芝160V1.5A25W)A940/C2073 (东芝150V 1.5A 25W)TIP41C/TIP42C(100V6A65W)小功率音响配对管K170/J74 (东芝40V400mW)K246/J103 (东芝50V14mA300mW)A872/C1775 (日立120V0.05A0.3W)A1191/C2856 (日立120V0.1A0.4W)A970/C2240 (东芝100V0.1A0.4W)A1145/C2705 (东芝150V0.05A0.8W)A1175/C2785 (日电60V0.1A0.3W)A1013/C2383 (东芝160V1A0.9W)B647/D667 (日立120V1A0.9W)B716/D756 (日立120V50mA0.75W)孪生音响配对管K389/J109 (东芝50V20MA200MW)A1349/C3381 (东芝80V0.1A0.4W)NPD5566 (国半60V20MA0.5W)IH5020 (60V20MA0.5W)LM394 (国半50V20MA0.5W)TTC5200,TTA1943 与 2SC5200,2SA1943 的区别通常所说的东芝管C5200,A1943,准确的说是2SC5200,2SA1943,但这对“名管”在几年前出现了兄弟:TTC5200,TTA1943,给烧友们带来了很大的疑惑,他们采用相同的To-3PL封装,大致参数相同,TTC5200,TTA1943没有根据放大倍数范围再进行细分,Ic=1A的放大倍数在80到160,和O档的2SC5200,2SA1943相同,差距比较大的参数是Cob ,分别是145和200;从Ic-Vce曲线来看,似乎是TTC5200,TTA1943要好些,但是Ic-Hfe曲线则显示2SC5200,2SA1943在大电流的时候放大倍数相对更坚挺一些,TTC5200,TTA1943的Ic-Hfe要变小的要早些。

大功率功放对管-概述说明以及解释

大功率功放对管-概述说明以及解释1.引言1.1 概述概述部分应该对大功率功放对管进行简要介绍,概括其重要性和相关背景知识。

可以按照以下方式编写:概述大功率功放对管在现代电子设备中具有重要地位和广泛的应用。

它作为一种重要的电子元器件,被广泛应用于各种工业领域和消费电子产品中,如音响系统、电视、通信设备等。

大功率功放对管的作用是放大弱信号,使之达到足够的功率,以驱动各种负载,如扬声器、电机等。

在音响系统中,大功率功放对管对于提高音质和增强音乐的力度具有重要作用。

在过去的几十年里,大功率功放对管经历了快速的发展和革新。

随着科技进步和人们对高品质音响的要求不断提高,研究人员们不断改进大功率功放对管的设计和性能,以满足日益增长的市场需求。

现代的大功率功放对管不仅功率输出更高,而且体积更小、效率更高、失真更低,能够更好地适应各种应用场景和音响要求。

本文将重点探讨大功率功放对管的原理、优势和应用前景。

首先,我们将介绍大功率功放对管的基本原理,包括工作原理和结构特点。

接着,将详细讨论大功率功放对管相比其他功放形式的优势,如功率输出、音质表现、效率等方面的优势。

最后,我们将展望大功率功放对管在未来的应用前景,探讨其在音响领域和其他领域的潜在应用可能性。

通过本文的阅读,读者将对大功率功放对管有更加深入的了解,了解其重要性和应用前景。

同时,本文也为研究人员、工程师和音响爱好者提供了参考和启发,以便在实践中更好地应用和发展大功率功放对管技术。

文章结构部分的内容可以是对整篇文章的主要段落和论述进行简要的介绍和概述。

下面是一个可能的写作示例:1.2 文章结构本文将围绕大功率功放对管展开分析和讨论。

为了便于读者更好地理解和掌握这一主题,文章分为三个主要部分。

首先,在引言部分,我们将概述论文的主要目的和内容。

我们会简要介绍高功率功放的背景和重要性,并明确本文的目标和意义。

接下来,正文部分将分为两个小节。

首先,我们将在2.1节对高功率功放进行简要介绍,包括其定义、特点和常见应用领域。

音响电子管的测试和配对

音响电子管的测试和配对电子管为高压工作的器件,除灯丝是否断路可以直接用万用表检测以外,其他参数直接用万用表是检测不出的。

不过,电子管的测试也并不困难,只要利用一组高低压供电电源,在万用表的辅助下也可以对基本参数进行检测,从而判断电子管的老化程度和得到配对时的参考数据。

虽然电子管已有近百年历史,但随着半导体的发展,使其在年青音响发烧友中无异是全新概念,加之有关电子管知识的资料几乎失传,使一般发烧友对其违莫如深,以致要判断其质量、衰老程度都较困难。

正因为如此,在市场上购买配对管的价格与单独同型号产品的差价在一倍以上。

其实,电子管生产工艺成熟,产品参数误差远小于晶体管(以其主要参数跨导为例),即使一般普通民用级(M级),其误差也在25%以内,在一般应用中既不需要调整外围元件参数,也不需要配对。

但并联或串联应用,或对称的推挽电路中,对某些参数配对还是必需的。

具体到胆机电路中,所有的对称放大电路,包括倒相级、对称驱动级和工作于A—B类的输出级都需要配对。

另外,有时为了增大输出功率或提高驱动级的驱动能力,将电子管并联使用时也需要配对。

其中推挽输出电路的配对对音响的效果影响是比较明显的。

不严格对称的推挽放大器其两臂输出信号波形也不对称,此波形在输出变压器中叠加以后,会产生额外的失真。

其影响程度以A、ADl、AB2、B类放大器的排列顺序增大。

不对称的推挽输出级,在A类、A趴类中,两只末级电子管静态板极电流不相等,加人信号以后,板极电流的变化幅度也不对称,输出变压器中产生的直流激磁电流不能抵消变压器磁芯的磁化,使初级等效电感减小,直接影响放大器的频率特性。

而在并联应用中,如果两只电子管参数不同,将使并联效果大减。

同时,随信号幅度变化其失真度也产生相应的变化。

长期使用中,其跨导较大、内阻较小的(相对性能比较好的)一只电子管衰老速度加快。

如果输出级中并联应用,当放大器输出功率越大时,其中一只性能好的电子管板耗将超过规定值而使板极中心部位被烧红,甚至损坏。

音响电器知识点总结大全

音响电器知识点总结大全第一部分:音响的基本组成1. 音箱音箱是音响系统的重要组成部分,它起到了扩音器的作用。

音箱分为主音箱和低音炮两种类型。

主音箱主要负责中高音频的输出,而低音炮则主要用来输出低音频的声音。

音箱的大小和声音效果有很大的关系,一般来说,音箱越大,声音效果越好。

2. 换能器换能器是音箱的核心部件,它负责将电信号转换为声音信号。

换能器的种类繁多,常见的有电动机换能器、电磁式换能器和压电换能器等。

3. 音频源音频源是音响系统中的输入设备,包括CD机、MP3、手机等。

一般来说,音频源的质量决定了音响系统的音质。

4. 放大器放大器负责将音频源发出的微弱信号放大,使其能够推动换能器发出声音。

放大器的种类繁多,包括晶体管放大器、电子管放大器和集成放大器等。

5. 信号处理器信号处理器主要负责音频信号的调节和加工,包括音源选择、音量调节、音响效果的控制等。

信号处理器的种类也很多,常见的有均衡器、混响器、调音台等。

第二部分:音响系统的布局和搭配1. 音箱的摆放音箱的摆放对音响效果有很大的影响,一般来说,音箱应该尽量与房间的布局相匹配,避免在房间的角落放置音箱,以免影响声音的散射效果。

此外,音箱的高度和倾斜角度也需要考虑,一般来说,音箱的高度应与听众的耳朵处于同一水平线上,倾斜角度则要根据实际布局来确定。

2. 换能器的搭配换能器的选择和搭配也是音响系统设计的重要环节,一般来说,不同类型的音箱和换能器要根据其频率响应和功率匹配来选择。

此外,换能器的排列位置也需要考虑,一般来说,主音箱要放在前方,低音炮则放在后方。

3. 放大器的选择放大器的选择要考虑其输出功率、阻抗匹配和音质等因素。

一般来说,放大器的输出功率应与音箱的最大承受功率相匹配,阻抗也要与音箱匹配,以免影响音响系统的稳定性和效果。

此外,放大器的音质也是需要考虑的因素,一般来说,数字放大器的音质较高,但成本也较高。

第三部分:音响系统的应用和维护1. 室内音响系统室内音响系统主要用于家庭、会议室、影音室等室内环境,其设计和布局需根据实际情况来确定,一般来说,家庭室内音响系统应该以声音的均匀覆盖和舒适音量为标准,避免过度放大声音,以免影响居民的休息和生活。

功放场效应对管

功放场效应对管

嘿,朋友!咱今天来聊聊功放场效应对管这玩意儿。

您知道吗,功放场效应对管就像是乐队里的灵魂鼓手,掌控着节奏的关键!它的作用那可不容小觑。

比如说,在音响系统里,功放场效应对管就好比是大力士,负责把音频信号放大,让声音变得响亮又清晰。

这就好像您在一个大大的广场上讲话,如果没有一个强有力的扩音设备,那您的声音能传多远?估计没几个人能听得清楚。

但有了功放场效应对管,那就不一样啦,哪怕您声音再小,它也能给您放大得妥妥的,让所有人都能听到。

再想想,一个好的功放场效应对管,就像是一位超级厨师,能把各种食材(音频信号)巧妙地融合在一起,烹制出美味的“声音大餐”。

如果这“厨师”水平不行,那这“大餐”可就变味啦,不是声音失真,就是各种杂音乱入,多糟心呐!

那怎么才能选到好的功放场效应对管呢?这可得有点眼力见儿。

就像挑水果,得看色泽、闻味道、摸手感。

对于功放场效应对管,咱得看它的参数,什么导通电阻啦、耐压值啦、最大电流啦等等。

这就好比选运动员,跑得快、跳得高、耐力强的才是好苗子。

还有啊,安装功放场效应对管也有讲究。

这就跟搭积木似的,得一步一步来,每个步骤都不能出错。

要是马虎了,那可就前功尽弃,整个系统都可能出问题。

您说是不是?

另外,使用过程中也得注意保养。

别让它过热啦,别给它过大的压力啦。

这就像照顾小孩,得细心呵护,不然它闹起脾气来,您可就头疼咯。

总之,功放场效应对管在音频系统中可真是个关键角色。

选得好、用得好、保养得好,就能让您享受到高质量的声音;要是没弄好,那可就只能听着那糟心的声音干着急啦!所以,可得重视起来哟!。

音响对管配对方法

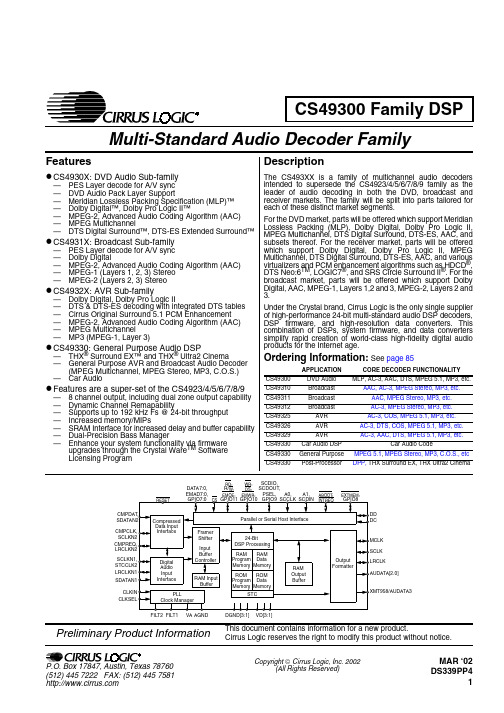

Copyright Cirrus Logic, Inc. 2002This document contains information for a new product.Cirrus Logic reserves the right to modify this product without notice.Preliminary Product InformationCS49300 Family DSPMulti-Standard Audio Decoder FamilyFeaturesz CS4930X: DVD Audio Sub-family—PES Layer decode for A/V sync —DVD Audio Pack Layer Support—Meridian Lossless Packing Specification (MLP)™—Dolby Digital™, Dolby Pro Logic II™—MPEG-2, Advanced Audio Coding Algorithm (AAC)—MPEG Multichannel—DTS Digital Surround™, DTS-ES Extended Surround™z CS4931X: Broadcast Sub-family—PES Layer decode for A/V sync —Dolby Digital—MPEG-2, Advanced Audio Coding Algorithm (AAC)—MPEG-1 (Layers 1, 2, 3) Stereo —MPEG-2 (Layers 2, 3) Stereoz CS4932X: AVR Sub-family—Dolby Digital, Dolby Pro Logic II—DTS & DTS-ES decoding with integrated DTS tables —Cirrus Original Surround 5.1 PCM Enhancement —MPEG-2, Advanced Audio Coding Algorithm (AAC)—MPEG Multichannel —MP3 (MPEG-1, Layer 3)z CS49330: General Purpose Audio DSP—THX ® Surround EX™ and THX ® Ultra2 Cinema—General Purpose AVR and Broadcast Audio Decoder(MPEG Multichannel, MPEG Stereo, MP3, C.O.S.)—Car Audioz Features are a super-set of the CS4923/4/5/6/7/8/9—8 channel output, including dual zone output capability —Dynamic Channel Remapability—Supports up to 192kHz Fs @ 24-bit throughput —Increased memory/MIPs—SRAM Interface for increased delay and buffer capability —Dual-Precision Bass Manager—Enhance your system functionality via firmwareupgrades through the Crystal Ware TM Software Licensing ProgramDescriptionThe CS493XX is a family of multichannel audio decoders intended to supersede the CS4923/4/5/6/7/8/9 family as the leader of audio decoding in both the DVD, broadcast and receiver markets. The family will be split into parts tailored for each of these distinct market segments.For the DVD market, parts will be offered which support Meridian Lossless Packing (MLP), Dolby Digital, Dolby Pro Logic II,MPEG Multichannel, DTS Digital Surround, DTS-ES, AAC, and subsets thereof. For the receiver market, parts will be offered which support Dolby Digital, Dolby Pro Logic II, MPE G Multichannel, DTS Digital Surround, DTS-ES, AAC, and various virtualizers and PCM enhancement algorithms such as HDCD ®,DTS Neo:6TM , LOGIC7®, and SRS Circle Surround II ®. For the broadcast market, parts will be offered which support Dolby Digital, AAC, MPEG-1, Layers 1,2 and 3, MPEG-2, Layers 2 and 3.Under the Crystal brand, Cirrus Logic is the only single supplier of high-performance 24-bit multi-standard audio DSP decoders,DSP firmware, and high-resolution data converters. This combination of DSPs, system firmware, and data converters simplify rapid creation of world-class high-fidelity digital audio products for the Internet age.Ordering Information: See page 85APPLICATIONCORE DECODER FUNCTIONALITY CS49300DVD Audio MLP, AC-3, AAC, DTS, MPEG 5.1, MP3, etc.CS49310Broadcast AAC, AC-3, MPEG Stereo, MP3, etc.CS49311Broadcast AAC, MPEG Stereo, MP3, etc.CS49312Broadcast AC-3, MPEG Stereo, MP3, etc.CS49325AVR AC-3, COS, MPEG 5.1, MP3, etc.CS49326AVR AC-3, DTS, COS, MPEG 5.1, MP3, etc.CS49329AVR AC-3, AAC, DTS, MPEG 5.1, MP3, etc.CS49330Car Audio DSP Car Audio CodeCS49330General Purpose MPEG 5.1, MPEG Stereo, MP3, C.O.S., etc CS49330Post-ProcessorDPP, THX Surround EX, THX Ultra2 CinemaDATA7:0,FILT1VA FILT2 AGND DGND[3:1]VD[3:1]EMAD7:0,R/W ,EMOE ,RD ,DS ,EMWR ,WR ,SCDOUT,PSEL,SCDIO,A0,A1,ABOOT ,EXTMEM ,MAR ‘02CS49300 Family DSPTABLE OF CONTENTS1.CHARACTERISTICS AND SPECIFICATIONS (6)1.1 Absolute Maximum Ratings (6)1.2 Recommended Operating Conditions (6)1.3 Digital D.C. Characteristics (6)1.4 Power Supply Characteristics (6)1.5 Switching Characteristics — RESET (7)1.6 Switching Characteristics — CLKIN (7)1.7 Switching Characteristics — Intel® Host Mode (8)1.8 Switching Characteristics — Motorola® Host Mode (10)1.9 Switching Characteristics — SP I Control Port (12)1.10 Switching Characteristics — I2C® Control Port (14)1.11 Switching Characteristics — Digital Audio Input (16)1.12 Switching Characteristics — CMPDAT, CMPCLK (18)1.13 Switching Characteristics — Parallel Data Input (18)1.14 Switching Characteristics — Digital Audio Output (19)2.FAMILY OVERVIEW (21)2.1 Multichannel Decoder Family of Parts (21)3.TYPICAL CONNECTION DIAGRAMS (24)3.1 Multiplexed Pins (24)3.2 Termination Requirements (25)3.3 Phase Locked Loop Filter (25)4.POWER (25)4.1 Decoupling (25)4.2 Analog Power Conditioning (25)Contacting Cirrus Logic SupportFor a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: /corporate/contactsDolby Digital, AC-3, Dolby Pro Logic, Dolby Pro Logic II, Dolby Surround, Surround EX, Virtual Dolby Digital, MLP and the “AAC” logo are trademarks and the “Dolby Digital” logo, “Dolby Digital with Pro Logic II” logo, “Dolby” and the double-”D” symbol are registered trademarks of Dolby Laboratories Licensing Corporation. DTS, DTS Digital Surround, DTS-ES Extended Surround, DTS Neo:6, and DTS Virtual 5.1 are trademarks and the “DTS”,“DTS-ES”, “DTS Virtual 5.1” logos are registered trademarks of the Digital Theater Systems Corporation. The “MPEG Logo” is a registered trademarkof Philips Electronics N.V. Home THX Cinema and THX are registered trademarks of Lucasfilm Ltd. Surround EX is a jointly developed technologyof THX and Dolby Labs, Inc. AAC (Advanced Audio Coding) is an “MPEG-2-standard-based” digital audio compression algorithm (offering up 5.1 discrete decoded channels for this implementation) collaboratively developed by AT&T, the Fraunhofer Institute, Dolby Laboratories, and the Sony Corporation. In regards to the MP3 capable functionality of the CS49300 Family DSP (via downloading of mp3_493xxx_vv.ld and mp3e_493xxx_vv.ld application codes) the following statements are applicable: “Supply of this product conveys a license for personal, private and non-commercial use. MPE G Layer-3 audio decoding technology licensed from Fraunhofer IIS and THOMSON Multimedia.” MLP and Meridian Lossless Packing are registered trademarks of Meridian Audio Ltd. Harman VMAx is a registered trademark of Harman International. The LOGIC7 logo and LOGIC7 are registered trademarks of Lexicon. SRS Circle Surround, and SRS TruSurround are trademarks of SRS Labs, Inc. The HDCD logo, HDCD, High Definition Compatible Digital and Pacific Microsonics are either registered trademarks or trademarks of Pacific Microsonics, Inc. in the United States and/or other countries. HDCD technology provided under license from Pacific Microsonics, Inc. This product’s software is covered by one or more of the following in the United States: 5,479,168; 5,638,074; 5,640,161; 5,872,531; 5,808,574; 5,838,274; 5,854,600; 5,864,311; and in Australia: 669114; with other patents pending. Intel is a registered trademark of Intel Corporation. Motorola is a registered trademark of Motorola, Inc. I2C is a registered trademark of Philips Semiconductor. Purchase of I2C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use those components in a standard I2C system. The “Cirrus Logic Logo” is a registered trademark of Cirrus Logic, Inc. All other names are trademarks, registered trademarks, or service marks of their respective companies.Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic web site or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consentof Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks canbe found at .CS49300 Family DSP4.3 Ground (32)4.4 Pads (32)5.CLOCKING (32)6.CONTROL (32)6.1 Serial Communication (33)6.1.1 SPI Communication (33)6.1.2 I2C Communication (35)6.1.3 INTREQ Behavior: A Special Case (39)6.2 Parallel Host Communication (41)6.2.1 Intel Parallel Host Communication Mode (43)6.2.2 Motorola Parallel Host Communication Mode (45)6.2.3 Procedures for Parallel Host Mode Communication (46)7.EXTERNAL MEMORY (48)7.1 Non-Paged Memory (49)7.2 Paged Memory (49)8.BOOT PROCEDURE & RESET (52)8.1 Host Boot (52)8.1.1 Serial Download Sequence (52)8.1.2 Parallel Download Sequence (55)8.2 Autoboot (56)8.2.1 Autoboot INTREQ Behavior (57)8.3 Decreasing Autoboot Times Using GFABT Codes (Fast Autoboot) (59)8.3.1 Design Considerations when using GFABT Codes (61)8.4 Internal Boot (61)8.5 Application Failure Boot Message (61)8.6 Resetting the CS493XX (61)8.7 External Memory Examples (63)8.7.1 Non-Paged Autoboot Memory (63)8.7.2 32 Kilobyte Paged Autoboot Memory (64)8.8 CDB49300-ME MA.0 (65)9.HARDWARE CONFIGURATION (67)10.DIGITAL INPUT & OUTPUT (67)10.1 Digital Audio Formats (67)10.1.1 I2S (67)10.1.2 Left Justified (67)10.1.3 Multichannel (67)10.2 Digital Audio Input Port (68)10.3 Compressed Data Input Port (69)10.4 Byte Wide Digital Audio Data Input (69)10.4.1 Parallel Delivery with Parallel Control (69)10.4.2 Parallel Delivery with Serial Control (70)10.5 Digital Audio Output Port (70)10.5.1 IEC60958 Output (71)11.HARDWARE CONFIGURATION (72)11.1 Address Checking (72)11.2 Input Data Hardware Configuration (72)11.2.1 Input Configuration Considerations (75)11.3 Output Data Hardware Configuration (76)11.3.1 Output Configuration Considerations (78)11.4 Creating Hardware Configuration Messages (78)CS49300 Family DSP12.PIN DESCRIPTIONS (80)13.ORDERING INFORMATION (85)14.PACKAGE DIMENSIONS (85)LIST OF FIGURESFigure 1. RESET Timing (7)Figure 2. CLKIN with CLKSEL = VSS = PLL Enable (7)Figure 3. Intel® Parallel Host Mode Read Cycle (9)Figure 4. Intel® Parallel Host Mode Write Cycle (9)Figure 5. Motorola® Parallel Host Mode Read Cycle (11)Figure 6. Motorola® Parallel Host Mode Write Cycle (11)Figure 7. SPI Control Port Timing (13)Figure 8. I2C® Control Port Timing (15)Figure 9. Digital Audio Input Data, Master and Slave Clock Timing (17)Figure 10. Serial Compressed Data Timing (18)Figure 11. Parallel Data Timing (when not in a parallel control mode) (18)Figure 12. Digital Audio Output Data, Input and Output Clock Timing (20)Figure 13. I2C® Control (26)Figure 14. I2C® Control with External Memory (27)Figure 15. SPI Control (28)Figure 16. SPI Control with External Memory (29)Figure 17. Intel® Parallel Control Mode (30)Figure 18. Motorola® Parallel Control Mode (31)Figure 19. SPI Write Flow Diagram (33)Figure 20. SPI Read Flow Diagram (34)Figure 21. SPI Timing (36)Figure 22. I2C® Write Flow Diagram (37)Figure 23. I2C® Read Flow Diagram (38)Figure 24. I2C® Timing (40)Figure 24. Intel Mode, One-Byte Write Flow Diagram (44)Figure 25. Intel Mode, One-Byte Read Flow Diagram (44)Figure 26. Motorola Mode, One-Byte Write Flow Diagram (45)Figure 27. Motorola Mode, One-Byte Read Flow Diagram (46)Figure 28. Typical Parallel Host Mode Control Write Sequence Flow Diagram (47)Figure 29. Typical Parallel Host Mode Control Read Sequence Flow Diagram (48)Figure 30. External Memory Interface (51)Figure 31. External Memory Read (16-bit address) (51)Figure 32. External Memory Write (16-bit address) (51)Figure 33. Typical Serial Boot and Download Procedure (53)Figure 34. Typical Parallel Boot and Download Procedure (54)Figure 35. Autoboot Timing Diagram (56)Figure 37. Autoboot INTREQ Behavior (57)Figure 36. Autoboot Sequence (58)CS49300 Family DSPFigure 38. Fast Autoboot Sequence Using GFABT Codes (60)Figure 39. Performing a Reset (62)Figure 40. Non-Paged Memory (64)Figure 41. Example Contents of a Paged 32 Kilobytes External Memory (Total 256 Kilobytes) (64)Figure 42. CDB49300-MEMA.0 Daughter Card for the CDB4923/30-REV-A.0 (66)Figure 43. I2S Format (68)Figure 44. Left Justified Format (Rising Edge Valid SCLK) (68)Figure 45. Multichannel Format (68)LIST OF TABLESTable 1. PLL Filter Component Values (25)Table 2. Host Modes (32)Table 3. SPI Communication Signals (33)Table 4. I2C® Communication Signals (35)Table 5. Parallel Input/Output Registers (42)Table 6. Intel Mode Communication Signals (43)Table 7. Motorola Mode Communication Signals (45)Table 8. Memory Interface Pins (49)Table 9. Boot Write Messages (52)Table 10. Boot Read Messages (52)Table 11. Reduced Autoboot Times using GFABT8.LD, GFABT6.LD, and GFABT4.LDon a CS493264-CL Rev. G DSP (59)Table 12. Memory Requirements for Example 5.1, 6.1 and 7.1 Channel Systems (63)Table 13. Digital Audio Input Port (68)Table 14. Compressed Data Input Port (69)Table 15. Digital Audio Output Port (70)Table 16. MCLK/SCLK Master Mode Ratios (71)Table 17. Output Channel Mapping (71)Table 18. Input Data Type Configuration(Input Parameter A) (73)Table 19. Input Data Format Configuration(Input Parameter B) (73)Table 20. Input SCLK Polarity Configuration(Input Parameter C) (75)Table 21. Input FIFO Setup Configuration(Input Parameter D) (75)Table 22. Output Clock Configuration(Parameter A) (76)Table 23. Output Data Format Configuration(Parameter B) (76)Table 24. Output MCLK Configuration(Parameter C) (77)Table 25. Output SCLK Configuration(Parameter D) (77)Table 26. Output SCLK Polarity Configuration(Parameter E) (77)Table 27. Example Values to be Sent to CS493XX After Download or Soft Reset (79)CS49300 Family DSP1.CHARACTERISTICS AND SPECIFICATIONS1.1. Absolute Maximum Ratings(AGND, DGND = 0V; all voltages with respect to 0V)CAUTION:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.1.2. Recommended Operating Conditions(AGND, DGND = 0V; all voltages with respect to 0V)1.3. Digital D.C. Characteristics(T A = 25°C; VA, VD[3:1] = 2.5V ±5%; measurements performed under static conditions.)1.4. Power Supply Characteristics(T A = 25°C; VA, VD[3:1] = 2.5V ±5%; measurements performed under operating conditions)ParameterSymbolMin Max Unit DC power supplies:Positive digitalPositive analog ||VA| – |VD||VD VA –0.3–0.3- 2.752.750.3V V V Input current, any pin except supplies I in -±10mA Digital input voltage V IND –0.3 3.63V Storage temperatureT stg–65150°CParameterSymbol Min Typ M ax Unit DC power supplies:Positive digital Positive analog ||VA| – |VD||VD VA 2.372.37- 2.52.5- 2.632.630.3V V V Ambient operating temperatureT A-70°CParameterSymbol M in Typ Max Unit High-level input voltage V IH 2.0--V Low-level input voltageV IL --0.8V High-level output voltage at I O = –2.0mA V OH VD ×0.9--V Low-level output voltage at I O = 2.0mA V OL --VD ×0.11V Input leakage currentI in-- 1.0µAParameterSymbol Min TypM ax Unit Power supply current:Digital operating: VD[3:1]Analog operating: VA--2001.73104mA mACS49300 Family DSP1.5. Switching Characteristics — RESET(T A = 25°C; VA, VD[3:1] = 2.5V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)Notes: 1.The minimum RESET pulse listed above is valid only when using the recommended pull-up/pull-downresistors on the RD, WR, PSEL and ABOOT mode pins. For Rev. D and older parts, pull-up/pull-down resistors may be 4.7 k or 3.3 k. For Rev. E and newer parts, pull-up/pull-down resistors must be 3.3 k.2.This specification is characterized but not production tested.1.6. Switching Characteristics — CLKIN(T A = 25°C; VA, VD[3:1] = 2.5V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)ParameterSymbol Min Max Unit RESET minimum pulse width low (-CL)(Note 1)T rstl 100-µs RESET minimum pulse width low (-IL)(Note 1)T rstl 530-µs All bidirectional pins high-Z after RESET low (Note 2)T rst2z -50ns Configuration bits setup before RESET high T rstsu 50-ns Configuration bits hold after RESET highT rsthld15-nsParameterSymbol Min Max Unit CLKIN period for internal DSP clock mode T clki 353800ns CLKIN high time for internal DSP clock mode T clkih 18ns CLKIN low time for internal DSP clock modeT clkil18nsFigure 1. RESET TimingFigure 2. CLKIN with CLKSEL = VSS = PLL EnableCS49300 Family DSP1.7. Switching Characteristics — Intel® Host Mode(T A = 25°C; VA, VD[3:1] = 2.5V±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)Parameter Symbol Min Max Unit Address setup before CS and RD low or CS and WR low T ias5-ns Address hold time after CS and RD low or CS and WR low T iah5-ns Delay between RD then CS low or CS then RD low T icdr0∞ns Data valid after CS and RD low(Note 3)T idd-21ns CS and RD low for read (Note 1)T irpw DCLKP + 10-ns Data hold time after CS or RD high T idhr5-ns Data high-Z after CS or RD high(Note 2)T idis-22ns CS or RD high to CS and RD low for next read(Note 1)T ird2*DCLKP + 10-ns CS or RD high to CS and WR low for next write(Note 1)T irdtw2*DCLKP + 10-ns Delay between WR then CS low or CS then WR low T icdw0∞ns Data setup before CS or WR high T idsu20-ns CS and WR low for write (Note 1)T iwpw DCLKP + 10-ns Data hold after CS or WR high T idhw5-ns CS or WR high to CS and RD low for next read(Note 1)T iwtrd2*DCLKP + 10-ns CS or WR high to CS and WR low for next write(Note 1)T iwd2*DCLKP + 10-nsNotes: 1.Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP = 1/DCLK. The DSP clock can be defined as follows:External CLKIN Mode:DCLK == CLKIN/4 before and during bootDCLK == CLKIN after bootInternal Clock Mode:DCLK == 10MHz before and during boot, i.e. DCLKP == 100nsDCLK == 65 MHz after boot, i.e. DCLKP == 15.4nsIt should be noted that DCLK for the internal clock mode is application specific. The application codeusers guide should be checked to confirm DCLK for the particular application.2.This specification is characterized but not production tested. A 470 ohm pull-up resistor was used forcharacterization to minimize the effects of external bus capacitance.3.See T idd from Intel Host Mode in Table6 on page43CS49300 Family DSP® Parallel Host Mode Read CycleFigure 3. IntelCS49300 Family DSP1.8. Switching Characteristics — Motorola ® Host Mode(T A = 25°C; VA, VD[3:1] = 2.5V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)Notes: 1.Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP =1/DCLK. The DSP clock can be defined as follows:External CLKIN Mode:DCLK == CLKIN/4 before and during boot DCLK == CLKIN after bootInternal Clock Mode:DCLK == 10MHz before and during boot, i.e. DCLKP == 100ns DCLK == 65 MHz after boot, i.e. DCLKP == 15.4nsIt should be noted that DCLK for the internal clock mode is application specific. The application code users guide should be checked to confirm DCLK for the particular application.2.This specification is characterized but not production tested. A 470 ohm pull-up resistor was used forcharacterization to minimize the effects of external bus capacitance.3.See T mdd from Motorola Host Mode in Table 7 on page 45ParameterSymbol Min Max Unit Address setup before CS and DS low T mas 5-ns Address hold time after CS and DS lowT mah 5-ns Delay between DS then CS low or CS then DS low T mcdr 0∞ns Data valid after CS and RD low with R/W high (Note 3)T mdd -21ns CS and DS low for read(Note 1)T mrpw DCLKP + 10-ns Data hold time after CS or DS high after read T mdhr 5-ns Data high-Z after CS or DS high low after read (Note 2)T mdis -22ns CS or DS high to CS and DS low for next read (Note 1)T mrd 2*DCLKP + 10-ns CS or DS high to CS and DS low for next write (Note 1)T mrdtw 2*DCLKP + 10-ns Delay between DS then CS low or CS then DS low T mcdw 0∞ns Data setup before CS or DS high T mdsu 20-ns CS and DS low for write(Note 1)T mwpw DCLKP + 10-ns R/W setup before CS AND DS low T mrwsu 5-ns R/W hold time after CS or DS high T mrwhld 5-ns Data hold after CS or DS highT mdhw 5-ns CS or DS high to CS and DS low with R/W high for next read(Note 1)T mwtrd 2*DCLKP + 10-ns CS or DS high to CS and DS low for next write(Note 1)T mwd2*DCLKP + 10-nsCS49300 Family DSPFigure 5. Motorola® Parallel Host Mode Read CycleFigure 6. Motorola® Parallel Host Mode Write CycleCS49300 Family DSP1.9. Switching Characteristics — SPI Control Port(T A = 25°C; VA, VD[3:1] = 2.5V±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)Parameter Symbol Min Max Units SCCLK clock frequency(Note 1)f sck-2000kHz CS falling to SCCLK rising t css20-ns Rise time of SCCLK line(Note 7)t r-50ns Fall time of SCCLK lines(Note 7)t f-50ns SCCLK low time t scl150-ns SCCLK high time t sch150-ns Setup time SCDIN to SCCLK rising t cdisu50-ns Hold time SCCLK rising to SCDIN(Note 2)t cdih50-ns Transition time from SCCLK to SCDOUT valid(Note 3)t scdov-40ns Time from SCCLK rising to INTREQ rising (Note 4)t scrh-200ns Rise time for INTREQ(Note 4)t rr-(Note 6)ns Hold time for INTREQ from SCCLK rising(Note 5, 7)t scrl0-ns Time from SCCLK falling to CS rising t sccsh20-ns High time between active CS t csht200-ns Time from CS rising to SCDOUT high-Z(Note 7)t cscdo20nsNotes: 1.The specification f sck indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. Therelevant application code user’s manual should be consulted for the software speed limitations.2.Data must be held for sufficient time to bridge the 50ns transition time of SCCLK.3.SCDOUT should not be sampled during this time period.4.INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for thesecond-to-last bit of the last byte of data during a read operation as shown.5.If INTREQ goes high as indicated in (Note 4), then INTREQ is guaranteed to remain high until the nextrising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treatthis condition as a new read transaction. Raise chip select to end the current read transaction and thendrop it, followed by the 7-bit address and the R/W bit (set to 1 for a read) to start a new read transaction.6.With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pullup value will affect the rise time.7.This time is by design and not tested.CS49300 Family DSPF i g u r e 7. S P I C o n t r o l P o r t T i m i n gCS49300 Family DSP1.10. Switching Characteristics — I2C® Control Port(T A = 25°C; VA, VD[3:1] = 2.5V±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)Parameter Symbol Min Max Units SCCLK clock frequency(Note 1)f scl400kHz Bus free time between transmissions t buf 4.7µs Start-condition hold time (prior to first clock pulse)t hdst 4.0µs Clock low time t low 1.2µs Clock high time t high 1.0µs SCDIO setup time to SCCLK rising t sud250ns SCDIO hold time from SCCLK falling(Note 2)t hdd0µs Rise time of SCCLK(Note 3), (Note 7)t r50ns Fall time of SCCLK(Note 7)t f300ns Time from SCCLK falling to CS493XX ACK t sca40ns Time from SCCLK falling to SCDIO valid during read operation t scsdv40ns Time from SCCLK rising to INTREQ rising(Note 4)t scrh200ns Hold time for INTREQ from SCCLK rising(Note 5)t scrl0ns Rise time for INTREQ(Note 6)t rr**ns Setup time for stop condition t susp 4.7µsNotes:. 1.The specification f scl indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. Therelevant application code user’s manual should be consulted for the software speed limitations.2.Data must be held for sufficient time to bridge the 300-ns transition time of SCCLK. This hold time is bydesign and not tested.3.This rise time is shorter than that recommended by the I2C specifications. For more information, seeSection 6.1, “Serial Communication” on page 33.4.INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for thelast data bit of the last byte of data during a read operation as shown.5.If INTREQ goes high as indicated in Note 8, then INTREQ is guaranteed to remain high until the nextrising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treatthis condition as a new read transaction. Send a new start condition followed by the 7-bit address andthe R/W bit (set to 1 for a read). This time is by design and is not tested.6.With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pullup value will affect the rise time.7.This time is by design and not tested.CS49300 Family DSPF i g u r e 8. I 2C ® C o n t r o l P o r t T i m i n gCS49300 Family DSP1.11. Switching Characteristics — Digital Audio Input(T A = 25°C; VA, VD[3:1] = 2.5V±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C L = 20pF)Parameter Symbol Min Max Unit SCLKN1(2) period for both Master and Slave mode(Note 1)T sclki40-ns SCLKN1(2) duty cycle for Master and Slave mode(Note 1)4555% Master Mode(Note 1, 2)LRCLKN1(2) delay after SCLKN1(2) transition(Note 3)T lrds-10ns SDATAN1(2) setup to SCLKN1(2) transition(Note 4)T sdsum10-ns SDATAN1(2) hold time after SCLKN1(2) transition(Note 4)T sdhm5-ns Slave Mode(Note 5)Time from active edge of SCLKN1(2) to LRCLKN1(2) transition T stlr10-ns Time from LRCLKN1(2) transition to SCLKN1(2) active edge T lrts10-ns SDATAN1(2) setup to SCLKN1(2) transition(Note 4)T sdsus5-ns SDATAN1(2) hold time after SCLKN1(2) transition(Note 4)T sdhs5-nsNotes: 1.Master mode timing specifications are characterized, not production tested.2.Master mode is defined as the CS493XX driving LRCLKN1(2) and SCLKN1(2). Master or Slave modecan be programmed.3.This timing parameter is defined from the non-active edge of SCLKN1(2). The active edge ofSCLKN1(2) is the point at which the data is valid.4.This timing parameter is defined from the active edge of SCLKN1(2). The active edge of SCLKN1(2) isthe point at which the data is valid.5.Slave mode is defined as SCLKN1(2) and LRCLKN1(2) being driven by an external source.。

TC.XO24音箱管理器

XO24音箱管理器用户手册a1阅读说明书.2 要记住操作指导.3 留意警示点.4 要完全按指导操作.5 设备要避免受到溅水6 只能用干布清洁设备.7不要堵塞设备的各个通风口,设备的安装应遵从制造商的要求.8 不要安装在靠近诸如取暖电炉、暖气片、火炉或其它能产生热量的热源旁9 不要使两极型或接地型插头的安全功用失效。

两极型插头有两片插脚,一片插脚比另一片要宽,而接地型插头有两片插脚外加第三片接地脚。

宽插脚或第三片接地脚就是用来提供安全接地。

如果设备的插头不能插入到插座上去的话,则可请电工更换过时的电源插座10电源线的布线要避免有人跨越,在插头处的线不要拽得太紧,插座的位置要便于插拔11 只能使用由制造商所指定的附件/ 配件12只使用由制造商指定的包装,支架三脚架,桌子,或与配件一同售出的。

使用手推车时,一定要小心在移动时不要发生滑动,发生受伤13在闪电或长时间不使用时,应将设备的电源插头拔出。

.14 有关所有的维修工作要请取得资格的维修人员来进行。

设备一旦受到损坏,例如电源线或插头受损、液体流入或物件掉落入设备内、设备暴露在雨水中或受潮、或跌落在地等因而不能正常工作时,都应请有关人员进行维修•本设备应安装在电源插座附近,并且应能便捷地拔出电源插头•为了彻底断开交流电源,应该将电源线从交流电插座中拔出•电源插头应该保持坚固耐用.•请勿将设备安装在狭窄的空间内.•请勿擅自打开设备机盖,因为里面有电击的危险注意:要注意到设备的功能有某些变化或修改,不一定在本手册内作详细说明,因而在操作本设备时有可能是无效操作.维修:•本手册内没有用户自己维修的内容说明•所有的维修工作应该请有资格的维修人员来进行警告!•尽量降低火灾或电击的危害,避免设备受雨淋或受潮。

• 设备必须接地。

• 使用三芯接地型的电源线。

• 不同的工作电压需用不同型号的线缆和接插件。

•检查在本地区的电源电压并使用正确的插头型号。

见下表:在三角形内标有闪光箭头的符号,用来警告用户:在设备的这些部位存在有未被隔离的“危险电压”,该电压的幅度可足以构成对人身电击的危害。

一文看懂音响系统设备的连接要点

一文看懂音响系统设备的连接要点一、设备连接顺序1、低音系统设备连接顺序:调音台(1-2编组)→均衡器→分频器→压限器→低音功放→低音音箱。

2、辅助音响系统设备连接顺序:调音台(3-4编组)→均衡器→延时器(可选)→压限器→辅助音箱功放→辅助音箱。

3、主音响系统设备连接顺序:调音台(L-R主通道)→均衡器→激励器(可选)→反馈抑制器(可选)→压限器→主音箱功放→主音箱。

4、监听系统设备连接顺序:调音台(AUX输出)→均衡器→压限器→监听音箱功放→监听音箱。

二、最简单的系统1、组成部分:音源设备、调音台、效果器、功放、全频音箱2、连接方式音源设备-调音台-功放-音箱,设备间采用链式连接。

链式连接方式:前级设备输出口(OUT 或OUTPUT)与后级设备输入口(IN或INPUT)相连接的方式。

3、设备接口专业设备的接口,无论是卡农口还是直插口,一律使用卡农或大三芯接插件用平衡方式连接,CD机之类用RCA莲花插座输出信号的音源设备,可使用莲花转大二芯线接入调音台LINE IN接口。

效果器IN口与调音台的推子后POST AUX SEND口连接(有些台子的推子后辅助输出用FX或EFX表示),效果器OUT与调音台LINE IN连接。

三、增加均衡器的系统1、组成部分:音源设备、调音台、均衡器、效果器、功放、全频音箱2、连接方式:音源设备-调音台-均衡器-功放-全频音箱,链式连接,效果器与调音台连接方式(同1)。

注:现在一般把多个喇叭组合在一起,形成音箱,也组成了很多种类的音箱。

四、增加分频器和超低音音箱的系统1、组成部分:音源设备、调音台、均衡器、分频器、全频音箱功放、超低音功放、全频音箱、超低频音箱2、连接方式:音源设备-调音台-均衡器-分频器-(分频器HIGH OUT接全频音箱功放,分频器LOW OUT接超低音音箱功放)-(全频音箱和超低音音箱)链式连接,效果器接法(同1)。

五、增加限幅器的系统1、组成部分:音源设备、调音台、均衡器、分频器、压限器、全频音箱功放、超低音功放、全频音箱、超低频音箱。

多少音响人都不懂的音响设备连接技巧!(下)

多少音响人都不懂的音响设备连接技巧!(下)相信很多音响人看完上篇肯定会意犹未尽,今天小编继续分享其他音响设备连接技巧。

GO~三、电子分频器的连接:电子分频器是指能将20Hz--20000Hz频段的音频信号分成合适的、不同的几个频率段,然后分别送给相应功放,用来推动相应音箱的一种音响周边设备。

目前的电子分频器输入部分还较简单,但输出部分就比较复杂:有高音输出、中音输出、低音输出等。

在连接时低音信号的输出和中高音信号的输出一定不要搞混了,否则高音信号给了低音音箱,低音信号给了高音音箱,这样一来音响系统中就可能没有声音出来了,因为频率不对,搞不好还会烧坏音箱等设备!电子分频器在连接发面可以采用XLR接头的平衡线路或TRS接头的平衡线路。

四、反馈抑制器的连接:在设备连接方面也是采用XLR接头的平衡线路或TRS接头的平衡线路,连接方法大致可分为以下3种:1、像均衡器等周边设备那样顺序串接在音响系统中,这样连接的优点是:连接和操作十分简单,适用于较简单的系统中。

但缺点是:此连接法在抑制话筒声反馈时,也会影响到通过反馈抑制器的其它音源信号。

2、利用调音台通道里的INS插入/插出接口,将反馈抑制器单独串接在相应的通道里,这样连接的优点是:可以最大限度对反馈抑制器进行调整,不必顾及会影响其它音源。

缺点是:利用这种连接法,一台反馈抑制器最多只能控制调音台的2个通道,设备利用率太低。

3、利用调音台编组里的INS插入/插出接口,将反馈抑制器串接在相应的编组通道里,其优点是:可对编进此编组内的话筒进行集中处理,而且不会影响到其它音源。

总起来说由于这种方法可以充分的利用反馈抑制器,因此也是目前采用最多的连接方法。

五、激励器的连接:音频激励器实际上是一种谐波发生器,利用人的心理声学特性,对声音信号进行修饰和美化的音频处理设备。

激励器一般有以下三种连接使用方法:1、可以像均衡器等周边设备那样串接在音响系统里需要激励的信号通道中,比如在一个调音台里,1-2编组是人声,如果要对这个编组的人声进行激励处理,可以把激励器利用插入/插出接口连接到调音台的1-2编组通道中。

关于音箱导向管的一点认识

关于音箱导向管的一点认识倒相箱可以说是目前市场占有率最大的箱体了,如果不能很好的理解倒相管的原理,那么就很难设计好倒相箱,因为看似简单的这种箱子,其实是很难设计的。

在开始之前,我现给大家讲一种现象。

就是如果你手拿一个注射器,医院打针的那种,那么你就会发现一种现象,针头开孔大的那种,你在打针的时候,手很容易就能够把液体推出去。

如果开口和针管一样粗,那么是最容易的,开口越小,哪么推起来就越费力。

这一点是直观可以体会的。

我要说的是,扬声器在倒相箱里的情况,和你打针是类似的,只不过打针是液体,压缩率小,而箱体中是空气,压缩率高。

那么我们来分析扬声器在箱体中的情况。

可以说当扬声器振膜向后移动的时候,(向后指的是向箱内)我们知道,箱内的空气被压缩,试想,这时速度是很快的,箱内空气的压缩,是扬声器背面的先被压缩,然后再向其他地方传导。

这就会产生一个问题,扬声器带来的空气压缩,在箱体内导致了箱内空气压强的不均衡,而我们知道倒相箱的空气泄放,只有倒相孔这条通路,因为我们就可以得知,压强的传导是向倒相孔附近传递的,而且箱内在这一时刻,是扬声器附近压强高,倒相孔压强低,空气向倒相孔移动。

要命的问题来了,在扬声器向后位移到最大的时候,这个不听话的家伙,又向前移动了。

而空气向倒相孔传导是有惯性的,实际上地球上任何运动的物体都有惯性,也就是说,空气在扬声器向前运动的时候,他还是继续在向导相孔移动,这就产生了一个问题,扬声器此刻背后的空气的压强又突然变小,产生了一个把空气拉回来的拉力。

然后这个可怜的空气没办法,当惯性不足以抵抗拉力的时候,他又被从倒相孔往回拉。

周而复始,一次次的折腾。

这里面最重要的问题是,我们可以看到,扬声器的运动总是快于空气的运动,也就是说空气的运动总是滞后于扬声器的运动。

说到这里我们先打住,你只要理解了空气运动滞后于扬声器的运动就可以了。

再来说一下声波,物理我们大家都学过。

声波在在空气中的传播有一个重要的理论就是,如果两个声波,在空气中叠加,如果相位一致,那么会使得波峰和波峰叠加,那么振幅会使叠加后的振幅,如果相位相差180度,那么会导致波峰和波谷叠加,会抵消,甚至为0。

音响设备连接调试说明书

音响设备连接调试说明书一、产品概述音响设备是一种用于提供音频输出和增强音质的设备。

本说明书旨在为用户提供正确、安全地连接和调试音响设备的指导。

二、设备连接在使用音响设备之前,请确保正确连接各个组件。

以下是连接音响设备的步骤:1. 主音箱连接:a. 将主音箱的电源线插入电源插座。

b. 使用音频信号线将音频源(如电视、音响播放器等)连接到主音箱的音频输入端口。

c. 检查所有连接是否牢固。

2. 子音箱连接:a. 如果您使用了包含子音箱的音响设备,请将子音箱的电源线插入电源插座。

b. 使用音频信号线将主音箱的音频输出端口连接到子音箱的音频输入端口。

c. 确保所有连接均牢固可靠。

3. 额外音频设备连接:a. 如果您希望连接额外的音频设备(如麦克风、乐器等),请根据设备规格进行连接。

b. 使用适当的音频线连接额外音频设备到音响设备的音频输入端口。

c. 检查所有连接是否正确连接。

三、设备调试在完成设备连接后,进行调试是确保音响设备能正常工作的重要一步。

以下是调试音响设备的步骤:1. 开启音响设备:a. 打开主音箱的电源开关,并确认指示灯亮起。

b. 如适用,打开子音箱的电源开关,并确认指示灯亮起。

2. 调节音量:a. 将音频源(电视、音响播放器等)的音量调至适当位置。

b. 逐渐调节主音箱的音量旋钮,以达到理想的音响效果。

c. 如适用,逐渐调节子音箱的音量旋钮,使其与主音箱平衡。

3. 声道平衡调整:a. 如您使用了具有多个声道的音响设备,请根据设备规格调整每个声道的音量平衡,以获得最佳音效。

4. 音效调节:a. 根据个人喜好,使用音响设备提供的音效调节功能,如均衡器、混响效果等,对音质进行调整。

5. 测试音效:a. 播放不同类型的音频内容(如音乐、电影、游戏等),以确保音响设备能够输出清晰、平衡的声音。

四、安全注意事项为确保您的安全和设备的正常运行,请务必注意以下事项:1. 使用标准电源插座,并避免使用损坏的电源线或插头。

全面的专业音响使用宝典知识

全面的专业音响使用宝典知识-专业音响必懂1、什么叫音箱的承受功率?顾名思义,音箱的承受功率就是指“输入音箱不超过此标示功率就不会损坏,就能承受得了”。

音箱的承受功率有几种表述方法,很容易造成使用者的误解,从而不当使用造成音箱的损坏。

音箱的参数标注中有的是标注额定功率,也就是长期功率,表示在此功率状态下长期使用不会损坏。

工厂检测额定功率是在恒温20℃条件下,用粉红噪声信号连续工作48小时为准。

在KTV包房中使用环境比较恶劣,音乐中又包含很多大动态的峰值信号,建议输入功率低于额定功率20%以上使用音箱,将会安全很多。

有的音箱参数标注的是峰值功率,这个值是额定功率的3-4倍,例如BMB牌CS-450MKII的功率标注就是峰值功率450W。

音箱对峰值功率的承受是有条件限制的,时间设定是1秒钟,反复也只能10次,如果超过就可能损坏,对峰值功率标注的音箱要特别小心使用,建议使用功率不超过峰值功率的1/4。

2、什么是功放的额定输出功率?功放的额定输出功率是指:“在不失真条件下的长期输出功率(一般指输出失真不超过1%)”,此种状态下功放是安全可靠工作的。

其实这里有几个前提条件:其一是要求市电电压为标准的220V,若市电波动,则功放的输出功率也会随之变化;其二是对负载(音箱)有阻抗规定,例如2*150W(8Ω)的功放,在4Ω负载的情况下可能输出功率会达到230W左右。

其三工厂在功放的输出功率测试时的环境温度为20℃,在KTV包房中使用时若散热不好,即使是在额定功率条件下工作,都有可能损坏功放,其四功放的额定功率是指不失真输出功率,并不是说功放只能输出这个功率,如果任由功率失真也加大输出(增大音量旋钮),则输出的失真功率是很大的,远远超过额定功率。

例如150W(8Ω)的功放在不失真时的最大输出电压应小于35V(功率=电压2/电阻),当失真时,输出电压可能会升到40V,则此时的失真功率会达到402/8=200W。

3、在选用功放和音箱时应该如何匹配功率?在选择功放和音箱时,我们建议功放额定功率要略大于音箱的额定功率,一般大小20-30%为宜,最起码也要相等,一定不能让功放额定功率小于音箱额定功率,形成“小马拉大车”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

音响对管试用笔记吴红奎说在前面高反压、大功率硅材料PNP晶体管生产技术的日臻成熟,在互补推挽音频功率放大器的舞台上,准互补推挽输出级渐成昨日黄花,无论是音频功放集成电路、电压推动级+功率输出级组合以及分立元件功放,纯互补推挽功率输出级已经是一统天下。

所谓准互补是指采用一对NPN/PNP(极性相反)的中小功率推动管与两个NPN(极性一致)的大功率管复合成一对极性互补的大功率达林顿晶体管,在高反压、大功率PNP晶体管制造技术还不成熟的时代,这种方式被广泛应用,以OTL(无输出变压器)放大器居多;采用互补型的中小功率管和互补型的大功率复合成一对互补的大功率达林顿晶体管,或者功率输出级直接采用极性互补的一对大功率晶体管,这样可以更好的保证推挽输出的上下臂的特性更加一致,随着高反压、大功率PNP晶体管制造技术的逐渐成熟,这种纯互补对称电路伴随着OCL(无输出电容)电路的流行而被广泛应用。

应用于OCL电路中的纯互补对称功率输出级,中点电位始终为零的保证很大程度上取决于NPN/PNP大功率管的特性的一致性,但是这与晶体管生产技术的离散性相矛盾,从大量特性有差别的功率管中挑选出特性一致的大功率晶体管来可不是一件容易的事情,不但需要一定的仪器设备和专业知识,还需要足够的耐心,“配对”似乎是发烧友永远的痛,于是“对管”应运而生。

所谓“对管”,是由晶体管制造商依靠生产工艺来保证极性互补的晶体管的特性尽量一致,其β(H FE)一般用字母分档,同档的对管在业余条件下一般可以不用再配对就可以直接使用。

除此之外还有一种称为“孪生对管”的,极性互补的一对晶体管管芯采用特定的硅芯片生产工艺以保证特性更加接近,然后将两个管芯封装在一个单体中形成六脚或者五脚(两个电极一起引出降低生产成本并减少PCB连线)器件,这种方式还可以有效避免流通过程中对管失配,此类器件主要是小功率器件,虽然价格高了些,但特性更加接近,用于差分放大器非常理想。

东芝、三肯、日立、富士等公司在八十年代末到九十年代,生产了大量用于音响功放的对管,从小功率到大功率,从单管到达林顿以及集成了温度补偿器件、发射极电阻的复合管一应俱全,2000年以后,大功率集成电路的发展,促使分立元件功放的市场逐渐萎缩而主要集中在高档和专业功放领域,音响对管市场也随之变得清淡,少见有新型号问世。

目前只有主要针对中低档市场的ON (ON Semiconductor,安森美半导体)算是比较活跃,适合音频应用的ThermalTrak TM和PowerBase TM系列大功率晶体管在刚刚过去的2006年都有新品推出。

对管的出现大大减少了分立元件功放的调整工作量,减少了生产复杂程度,也大大减少了生产成本,同时大大提高了电路的性能,使“无负反馈”的功放曾经鼓噪一时;在非专业条件下,功率晶体管配对的过程甚至可以省略,中低档音响整机的生产也是如此,配对和工作点的精确调整似乎只是专业音响和高端民用音响需要采用的工序了。

这次笔者有机会拿到5种针对音频功率放大器功率输出级设计的对管,拿来用非专业的手段测试一下,把方法与过程与大家共享,请行家拍砖。

一、材料与对象这次拿到的对管每个型号有2个,表1是这5种对管的型号和主要技术参数。

其中三肯公司出品的以MN/MP打头的对管并非该公司在市场上公开销售的产品,而是SONY等专业音响公司向三肯公司定制的产品,属于OEM类型。

如ONKYO(安桥)的高级AV放大器TX-SR803、TX-SR701中就使用了3对MN150S/MP150S并联做功率输出级,在SONY的QS系列中档家庭影院放大器产品中则可以看到MN2488/MP1620的身影,如STR K750P、STR-DB790等。

这次拿到此类管子也属机会难得。

图1是此次拿到的5种对管的实际外形图,是笔者用数码相机实拍的,而第6种则是拿来做比较基准的,是ST出品的MJE2955T和MJE3055T;一方面是因为这次测试采用的是某成品机型的功放板,原板就是采用了二者做功率输出级,另一方面这两位仁兄是老牌的音响对管了,现在看起来它们的规格似乎低了些,但从其在国内应用的历史和广泛性来看,却不可小觑,至今很多中低档音响仍在应用,而ST 的产品,其品质也无需置疑,后续的测试也部分证明了这一点。

所以顺手把它们最为基准比较一下,其技术规格一并列于表1。

表1:5对双极型功率晶体三极管的主要技术参数(TA=25℃,典型值)。

序号 型号 类型 P CM (W) I CM (A) U CEO (V) f T (MHz) I CBO (μA) β (h FE ) C ob(pF) 批号封装 形式 制造商01 2SC3263 NPN 130 15 230 60 ≤100Y(70~140) 250 67 TO3P Sanken2SA1294 PNP 35500 54 02 2SC6011 NPN 160 15 200 20 ≤10P (70~140) 270 4D TO3P2SA2151 PNP 20450 03 MN150S NPN 150 15 180 20 ≤100Y (90~180) 300 55 TO3P MP150S PNP500 40 04 MN100S NPN 100 8 120 20 ≤10Y (90~140) 200 55 TO3PMP100S PNP300 56 05 2SC5200 NPN 150 15 230 30 ≤5O (80~160) 200 632 TO3PL TOSHIBA 2SA1493 PNP360 628 06 MJE3055T NPN 75 10 60 2 ≤1000 20~70- - TO220STMJE2955T PNP - -备注:β一栏,字母是字母分档标识,括号中是该字母表示的β范围。

图1 5种对管的实际外形图表1中的所有技术数据都来自原厂公开发表的最新版本的电子数据文档,因为版本或者来源不同,可能与某些公开发表的数据有所不同。

没有采用实际测试数据,原因是笔者这测拿到的对管数量比较少,测试数据很难具有广泛的代表性。

关于表1中批号的含义,对于三肯的管子,算是比较清楚:从左至右,第一位数字表示生产日期的年份的最后一位数字,如6则表示1996年;后一位数字或字母表示生产的月份,1~9表示1~9月份,O、N、D分别表示10~12月份;对于东芝的管子,采用3位数表示的含义笔者尚不清楚。

二、测试的电路与方法㈠、非专业条件下对管的简单测试在非专业应条件下,如果条件有限,对管可以不进行配对而选取β同档的直接应用,万用表可以直接进行“好”和“坏”的判别,也可以对β进行粗略测试,部分型号的万用表还可以进行反压测试;市场上还有一种很廉价的专门测试工具:晶体管参数测试仪,俗称“打压表”,因主要用来测量晶体管的U CEO(俗称耐压、反压)而得名,很多电子元件店里都有卖的,100元左右,用来做晶体管的简单测试非常方便;如果你刚好可以蹭到单位的晶体管图示仪,对拿到的晶体管进行一下包括各种特性曲线在内的测试也并非多余,做的心中有数,有备无患。

只是晶体管图示仪这种昂贵的仪器社会拥有量不大,可以熟练使用者更是寥寥,笔者在这里想介绍一种简单的非专业的方法,这种方法不需要很专业的仪器设备,被很多发烧友包括笔者在内经常使用,其一般的原理图如图2所示。

这种方法原理是:理想条件下,两个晶体管的特性如果完全一致(如果是对管,极性相反除外),则I B相同,I C就应该相同。

不难得出,在实践中,I B相同,I C就应该越接近越好;测试大电流条件下I B一定时待测对管I C的差别,就可以粗略评价大功率对管在这种条件下的β的对称性;通过观察I C短暂稳定后上升的速度和最终是否能够稳定在某一数值来粗略评价其温度稳定性。

通过这两项指标一般就可以对待测对管特性的一致性做出粗略评价,也可以实现非专业条件下的大功率晶体管的粗略配对。

图2 大功率晶体管在大电流条件下的一般简单测试方法图2所示的方法一般需要两块万用表或者直流电流表,如果想提高读数精度可以采用数字万用表,由于最终测试结果是要比较相对值,所以使用数字表对测试精度和误差影响不大。

VCC1最好直接采用功放中准备供给功率输出级使用的直流电源,这样对管的状态和实际情况更为接近;也可以采用电压幅度相近的其他电源,但功率裕量要够用。

VCC2最好采用稳压电源以避免因为电压波动引起I B的波动从而影响测试结果的准确性;待测晶体管需要配上散热器或者直接使用给末级准备的散热器。

NPN和PNP管的测试电路有所不同,测试完所有的NPN管再测试PNP管比较省事也不容易出错,不同型号的晶体管为了使I C的大小合适,I B会有一点差别,这就需要来回调节VR,但为了方便比较,又需要同一对管中的NPN和PNP管使用同样大小的I B,使用可调电阻,I B的重复性就比较差,即使采用多圈电位器也是如此,所以笔者这次采用了如图3所示的改进电路以方便I B数值的重复和调节。

图3中用5个100欧姆的固定电阻代替图2中的电位器VR,可以很方便的实现I B数值的重复,I B的测试回路的mA表可以省略,以探针的档位代替,缺点是I B不能连续调节;图中的探针可以使用小号的鳄鱼夹,如果想做为仪器经常使用,可以用多掷开关。

如果是初次测试,应该从5档开始,逐步减小。

图3 大功率晶体管在大电流条件下的改良测试方法最终采用多大的I C来比较,有些发烧友认为应该采用晶体管手册中给出的I CM的二分之一,即10A 的管子,I C应该定为5A;笔者认为可以根据待测晶体管的发热程度来定:在实际测试过程中,I C的读数应在1秒内快速上升到某一数值并在随后的3~5秒内接近稳定或者极其缓慢上升为准,这时候也比较方便准确读数并具备可比性。

最终笔者实际试测的结果采用I CM的四分之一左右做为I C的比较基准。

测试电路与晶体管管脚的连接可以采用鳄鱼夹以方便待测晶体管的更换,不过要注意I C测试回路的鳄鱼夹连线不能太细,市场上零售的带线的鳄鱼夹连线大多很细,最好更换成比较粗一点的连线;也可以直接焊接,但对于经销商“不焊接保换”的条款不太适用,也要多费些时间;还可以给待测晶体管做一个专门的插座,笔者就是用电脑电源的T形插头做了一个,对于TO3P封装的晶体管,宽度刚好合适,将管脚插到底,T形插头的底面也刚好被散热器的平面撑住,晶体管的管脚刚好被压紧。

表2是这测5种对管的测试结果,每个型号的管子有两个,所以I C的数值用字母A、B加以区分。

测试时每个型号的晶体管测试了两个不同I B,为了节省篇幅这里只列出了一个I B数值及其测试出来的对应的I C数值。

表2 5种对管大电流条件下的测试结果序号01 02 03 04 05型号2SC3263 2SA1294 2SC6011 2SA2151 MN150S MP150S MN100S MP100S 2SC5200 2SA1493 探头档位 2 2 3 4 3I b(mA)19.00 19.3 13.5 10.25 13.45I C (A) A 2.58 3.21 3.25 2.56 3.22 2.81 3.08 2.76 2.32 4.80B 2.45 3.01 3.20 3.51 3.42 2.62 3.10 2.58 2.18 4.72分析表2可以发现同极性的管子差别相对比较小,而对管中不同极性的管子,多数差别还是明显的;测试中还发现2SC5200/2SA1493的温度稳定性不如其他4对管子,大电流条件下I C上升很快并且难以稳定;2SC3263/2SA1294的β相对比较小,因为它们需要更大的I B,这意味着推动级的推动能力应该大一些。