8QUARTUS使用及原理图设计

实验1 原理图输入设计8位全加器

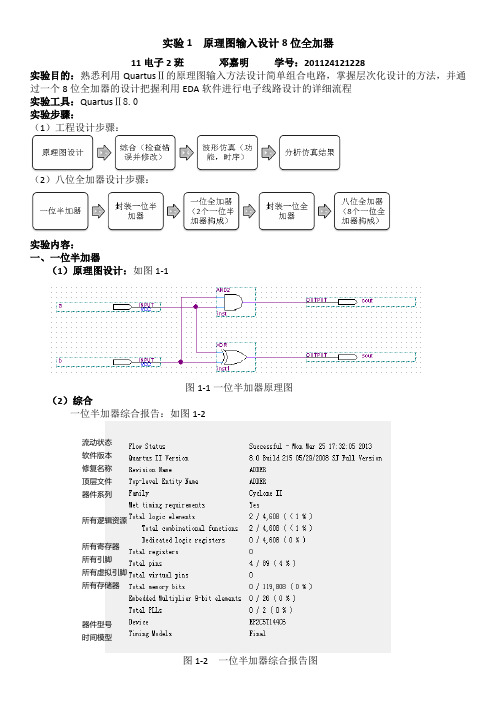

实验1 原理图输入设计8位全加器11电子2班 邓嘉明 学号:201124121228实验目的:熟悉利用Quartus Ⅱ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA 软件进行电子线路设计的详细流程 实验工具:Quartus Ⅱ8.0 实验步骤:(1)工程设计步骤:(2)八位全加器设计步骤:实验内容:一、一位半加器(1)原理图设计:如图1-1图1-1一位半加器原理图(2)综合一位半加器综合报告:如图1-2图1-2 一位半加器综合报告图流动状态 软件版本 修复名称 顶层文件 器件系列所有逻辑资源所有寄存器 所有引脚 所有虚拟引脚 所有存储器 器件型号 时间模型(3)功能仿真半加器功能仿真波形图:如图1-3图1-3半加器波形仿真图半加器理论的结果:如表1-1结论:图所以波形图仿真时成功的。

(4)时序仿真半加器时序仿真波形图:如图1-4图1-4 半加器时序仿真波形图结论:时序仿真没有出现毛刺,只能说明这次试验比较幸运。

延时情况:如图1-5注:tsu(建立时间),th(保持时间),tco(时钟至输出延时),tpd(引脚至引脚延时)图1-5 半加器时序仿真延时情况(5)封装一位半加器的封装:如图1-6图1-6 一位半加器封装二、一位全加器(1)一位全加器原理图设计:如图2-1图2-1 一位全加器原理图(2)综合一位全加器综合报告:如图2-2图2-2 一位全加器综合报告(3)功能仿真一位全加器功能仿真波形图:如图2-3果,所以波形图仿真时成功的。

(4)时序仿真一位全加器时序仿真波形图:如图2-4图2-4 一位全加器时序仿真波形图结论:一位全加器时序仿真结果没有出现毛刺,只能说明这次试验比较幸运。

延时情况:如图2-5图2-5 一位全加器时序仿真延时情况(5)封装一位全加器封装:如图2-6图2-6 一位全加器封装三、八位全加器(1)原理图设计一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现。

EDA技术3-QUARTUS使用方法

厦门理工学院通信系 刘虹

26

3.4 LPM_ROM宏模块应用

使用Quartus II 的MegeWizard Plug-In Manager中的宏功能模块可以帮助用户完成一些复 杂系统的设计,并可以方便地对现有的设计文件 进行修改。这些宏功能模块包括LPM(Library Parameterized Megafunction)、MegaCore(例 如FFT、FIR等)和AMMP(Altera Megafunction Partners Program,例如PCI、DDS等)。下面以 波形发生器的设计为例,介绍Quartus II宏功能 模块的使用方法。

厦门理工学院通信系 刘虹 2

为了方便电路设计,设计者首先应当在计 算机中建立自己的工程目录(如d:\myeda)。 将自己的全部EDA设计文件放在文件夹中。

注意:工程文件夹的名称不要使用汉字,最好 也不要使用数字。

厦门理工学院通信系 刘虹

3

Quartus II原理图输入的基本操作

编辑原理图

引脚锁定

厦门理工学院通信系 刘虹

24

在设计中嵌入SignalTap Ⅱ逻辑分析

仪有两种方法:第一种方法是建立一个

SignalTap Ⅱ文件(.stp),然后定义STP文

件的详细内容;第二种方法是用

MegaWizard Plug-InManager建立并配臵

STP文件,然后用MegaWizard实例化一个

HDL输出模块。

厦门理工学院通信系 刘虹

29

1. 加入计数器元件 用鼠标双击原理图编辑窗, 在弹出的元件选择窗的 “Libraries”栏目中选择 “arithmetic”的 “lpm_counter”(计数器) LPM元件。LPM是参数化的多功 能库元件,每一种LPM元件都 具有许多端口和参数,通过对 端口的选择与参数的设臵得到 设计需要的元件。

Quartus原理图输入法指南

6

二、形成原理图设计文件

1、建立原理图设计文件 从菜单File→New进入,在6种设计输入法中选择原理图输 入法,单击OK,即可进入原理图编辑器

提 示 : 硬 件 实 验 课 程 要 求 如 此

7

2、编辑原理图设计文件 ⑴元件的选择与放置 *可在Symbol对话框中选择元件,单击OK

提示: *弹出Symbol方法:双 击鼠标左键、工具条… *元件库包含系统库和 Project库两类 *Project库由用户自定 义符号文件(.bsf)组成 *亦可在编辑区用Copy 及Paste命令实现选择

*在编辑区可移动元件,放置到合适的位置管脚类型,使工具箱相应连接线有效 *在源处按下鼠标左键、移至目标处、松开鼠标左键即可

提示: *连接线有3种:Node、 Bus、Conduit *所连接的源端、目标 端元件管脚类型应相同 *应避免移动元件时产 生多余交叉点 *工具箱有多种功能

提示: 修改原理图文件 后,必须重新编译、 生成仿真网表

19

⑵进行功能仿真 *在对话框的Simulator input中输入仿真波形文件名 *在对话框中单击Start,即可开始功能仿真 *在对话框中单击Report,可查看、核对输出波形

20

五、对原理图设计文件进行硬件测试

1、器件设置及引脚锁定

⑴器件设置 [该步骤可缺省] *从菜单Assignments→Device进入,可重新选择器件 *单击Device & Pin Options…,可配置Unused Pins状态等

提示: 有多种方法 触发编译开始

*编译结束时,会报告警告或错误的统计情况 *编译出错时,按Message提示修改错误,直至编译通过

13

四、对原理图设计文件进行时序仿真

QUARTUS使用及原理图设计

QUARTUS使用及原理图

电子信息工程学院

20

3.编译设计文件

QuartusⅡ软件中的编译类型有全编译和分步编译两种。 全编译的过程包括分析与综合(Analysis & Synthesis

)、适配(Fitter)、编程(Assembler)、时序分析 (Classical Timing Analysis)这4个环节,而这4个环节 各自对应相应的菜单命令,可以单独分步执行,也就是分 步编译。

(1)实例Instances,能够被展开成低层次模块或 实例;

(2)原语Primitives,不能被展开为任何低层次模 块的低层次节点;

(3)引脚Pin,当前层次的I/O端口,如果端口是总 线,也可以将其展开,观察到端口中每一个端口的信 号;

(4)网线Net,是连接节点的连线,当T”

(2) 输入信号节点。

图4-8 从SNF文件中输入设计文件的信号节点

QUARTUS使用及原理图

电子信息工程学院

最后点击“OK”

图4-9 列出并选择需要观察的信号节点

用此键选择左窗 中需要的信号 进入右窗

QUARTUS使用及原理图

电子信息工程学院

(4) 设定仿真时间。

(3) 设置波形参量。

全编译操作简单,适合简单的设计。对于复杂的设计,选 择分步编译可以及时发现问题,提高设计纠错的效率,从 而提高设计效率。

QUARTUS使用及原理图

电子信息工程学院

21

3.编译设计文件

RTL阅读器:在设计的调试和优化过程中,可以使 用RTL阅读器观察设计电路的综合结果,同时也可 以观察源设计如何被翻译成逻辑门、原语等

电子信息工程学院

60

10

设计流程归纳

Quartus_II设计八位加法器

Q u a r t u s_I I设计八位加法器(总19页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--摘要关键词: 8位加法器;EDA(电子设计自动化);QuartusⅡ(可编程逻辑软件)目录第1章概述..................................................................................................... 错误!未定义书签。

EDA的概念 ...................................................................................................... 错误!未定义书签。

硬件描述语言概述........................................................................................ 错误!未定义书签。

第2章QUARTUS II ...................................................................................... 错误!未定义书签。

QUARTUSII概述............................................................................................. 错误!未定义书签。

QUARTUSII建立工程项目......................................................................... 错误!未定义书签。

QUARTUSII建立原理图输入文件 .......................................................... 错误!未定义书签。

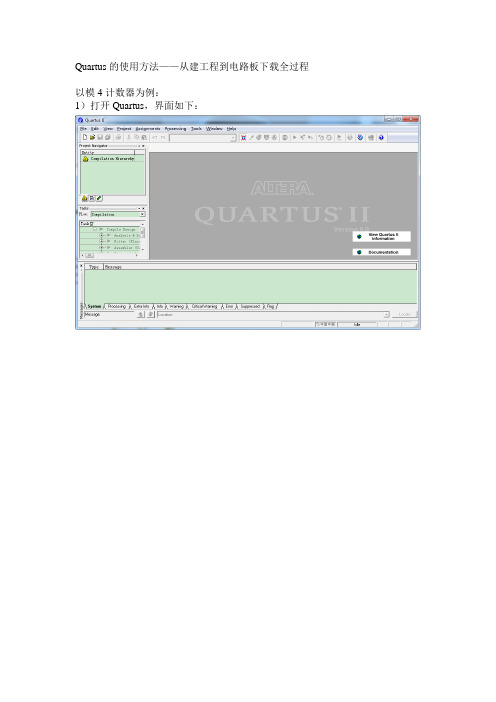

图解Quartus的使用方法

Quartus的使用方法——从建工程到电路板下载全过程以模4计数器为例:1)打开Quartus,界面如下:2)创建工程,点击File—>New Project Wizard跳过第一个默认的界面,直接进入第二个:注意工程文件名与顶层实体名相同,这在写VHD文件时尤其要注意,在定义entity时名字必须与工程名一致,否则会报错。

下一步需要向工程里添加文件和库,我们现在不需要,暂时直接跳过。

3)选择器件这个器件的选择不能臆想,其实仔细看电板上的芯片就可以看到相应的型号。

一定要根据实际情况选择,否则仿真时会出现问题。

当然如果创建工程时没有选择也没有关系,到时候可以在device里面选择或者更改。

下一步基本上也是默认,直接next。

4)信息确认点击finish即可创建工程,如果发现信息需要修改,可以点击back。

5)创建设计文件点击File—>New,选择Block Diagram/Schematic File,单击OK。

弹出空白的编辑界面6)在空白处双击,在弹出的原件对话框中的Name里直接输入74161,或者可以根据上面的library属性图一级级的查找。

如果熟悉的话还是直接输入器件名称快。

单击OK,或者直接输入enter即可选中原件,然后在适当位置单击鼠标即可安置原件。

7)连接好的电路图如下注意这里有一个命名技巧:注意到右上角的输出线比其他线要粗,这是Bus line表示单向总线,而一般的细线叫Line。

选中该output,单击右键,在properties中的General中根据提示命名,比如这里的q[1..0]。

表明有两根线分别是q[0]和q[1]。

当然需指定这个总线在电路中是哪几根线,上图中是指从74161到与非门的输出线,所以要分别选中,并为之赋予相应的名字。

如果省略这一步,将会提示该q[1..0]没有指定,编译都不通过。

8)保存文件File—>save,注意文件名与工程名要相同,即不改变默认名即可。

EDA实验2 原理图输入法设计8位二进制全加器

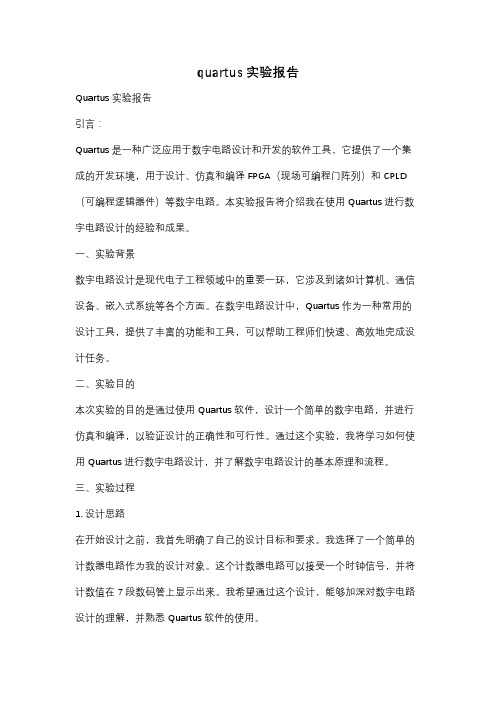

实验2原理图输入法设计8位二进制全加器一、实验目的进一步熟悉QuartusⅡ的使用方法,学习时序仿真。

二、实验内容用V erilog HDL设计一个8位二进制全加器。

可以直接编写程序,也可以利用例化语句调用1位全加器构成8位全加器。

并进行编译、综合、适配和仿真。

三、实验步骤:1.为本项工程设计建立文件夹2.建立V erilog HDL文件3.存盘并建立工程4.全程编译5.时序仿真⑴建立矢量波形文件菜单操作:file—new图2-1 选择编辑矢量波形文件图2-2 波形编辑器⑵设置仿真时间长度菜单操作:Edit—end time图2-3 设置仿真时间长度⑶存盘图2-4 vwf激励波形文件存盘⑷将工程test2的端口信号选入波形编辑器中。

菜单操作:View—Utility Windows—Node Finder,并按图2-5 向波形编辑器拖入信号节点选项:Look:工程名;filer:Pins all⑸编辑输入波形单击输入信号a使之变成蓝色条,激活波形编辑器图2-6波形编辑器按图2-7设置输入信号a的周期在Tool Zoom 状态下调整波形图图2-8 设置好的激励波形图⑹菜单操作:Assignments –setting进入以下窗口:图2-9 选择仿真控制图2-10 仿真波形输出图2-11 选择全时域显示⑺仿真:Processing-Start Simulation 或。

注:该实验也可用硬件测试的方法来验证其设计的正确性。

四、实验报告详细叙述实验内容所要求的设计流程;给出仿真波形图;给时序分析情况。

五、参考程序module ADDER8B(A,B,CIN,COUT,DOUT);output [7:0] DOUT; output COUT;input [7:0] A,B; input CIN; wire [8:0] DA TA;assign DA TA =A+B+CIN;assign COUT=DA TA[8];assign DOUT=DA TA[7:0];endmodule。

Quartus原理图设计

(2)添加文件

(3)选择目标芯片

(4)指定其它EDA工具

Project name: adder Top-level design entity: adder Device assignments:

Family name: ACEX1K

Device: EP1K10TC100-3

(3)编辑波形

a)设置仿真时间 Edit | End Time

b)设置栅格时间 Edit | Grid Size

c)波形编辑工具箱

找节点 未初始化

缩放视图

替换节点 强制未知

强制低电平

强制高电平

高阻抗 弱低电平 无关 计数值 任意值 对齐网格

弱未知 弱高电平 翻转波形 时钟信号 随机值 排序

(2)添加编程文件

(3)启动编程

√

primitives | pin

bidir input output

真值表 a 0 0 1 b 0 1 0 cout 0 0 0 sout 0 1 1

1

1

1

0

cout a b sout a b

半加器原理图

(4)保存文件 File | Save As

2 创建工程 File | New Project Wizard

d)设置时钟

e)设置节点顺序

f)设置节点属性

输入信号波形

(4)设置时序仿真模式 Assignment | Settings Simulator Settings

(5)观看仿真结果 Processing | Start Simulation View | Fit in Window

半加器时序仿真波形图

创建工作目录 D :\ PLD \ adder

基于QUARTUS的ADC0809的应用仿真设计

目录一、设计任务及性能指标 (2)二、设计要求 (2)三、方案设计与论证 (2)3.1 方案设计原理 (2)3.2 方案论证 (3)四、具体设计过程 (4)4.1AD0809的工作时序图 (4)4.2 程序流程图 (5)五、测试结果 (6)5.1仿真时序图 (6)5.2RTL原理图 (7)5.3 Moore型有限状态机状态图 (7)六、附录 (8)6.1程序代码 (8)6.2 心得体会 (11)7.参考文献 (14)ADC0809的应用一、设计任务及性能指标1.利用实验箱上FPGA芯片控制ADC0809的时序,进行AD转换,然后将ADC0809转换后的数据以十六进制的数据显示出来。

2.实现时必须严格遵守ADC0809的工作时序,在编写代码时要注意。

对选定的通道输入一个模拟量,调节电位器改变输入的模拟量。

3.了解ADC0809的工作原理4.了解用扫描方式驱动七段码管显示的工作原理。

5.了解时序电路FPGA的实现。

6.学习用VHDL语言来描述时序电路的过程。

二、设计要求基本要求:1、采用状态机2、控制ADC0809的第三通道进行AD转换3、转换结果显示格式00~FF三、方案设计与论证3.1 方案设计原理ADC0809是CMOS的8位A/D转换器,片内有8路模拟开关,可控制8个模拟量中的一个进入转换器中。

ADC0809的分辨率为8位,转换时间约100us,含锁存控制的8路多路开关,输出有三态缓冲器控制,单5V电源供电。

主要控制信号说明:如图3.1所示,START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC、ADDB、ADDA)信号的锁存信号。

当模拟量送至某一输入端(如IN1或IN2等),由3位地址信号选择,而地址信号由ALE锁存;EOC是转换情况状态信号(类似于AD574的STATUS),当启动转换约100us后,EOC产生一个负脉冲,以示转换结束;在EOC的上升沿后,若使输出使能信号OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。

FPGA轻松学习用QuartusII通过原理图完成与门电路设计

FPGA轻松学习用QuartusII通过原理图完成与门电路设计打开QuartusII软件,程序主界面如下:1,新建一个工程点击File——>New Project Wizard,打开创建新工程向导,这里你将完成工程的基本设定选项。

1,Project name and directory——工程的名称与目录2,Name of the top-level design entity——顶层设计实体的名称3,Project files and libraries——项目文件与库4,Target device family and device——目标设备的族类5,EDA tool settings——EDA工具设定这里一般设定好工程名称和目录,顶层设计实体名称以及目标设备族类就可以了,其他的暂时直接使用默认项就可以了。

2,新建一个设计文件通过点击File——>New打开新建文件选择框,由于我们这里使用原理图描述实现的,则文件类型选择Design Files——>Block Diagram/Schematic File,就新建了一个原理图文件,将其保存起来,注意命名要跟前面设置的顶层设计实体名称相同。

3,编写设计文件接下来开始在文件中绘制原理图,这里首先完成与门的添加,点击左侧工具栏中的Symbol Tool按钮,打开Symbol选择框,选择primitives——>logic——>and2,点击OK后即可在原理图中添加一个2输入的与门了。

在同样通过Symbol Tool中的加入和primitives——>pin——>output加入输入和输出引脚,然后在原理图中把他们用Orthogonal Node Tool即导线连接起来,双击输入输出引脚,为他们设定好名字,pinA,pinB,pinC,就完成了原理图中的设计。

4,编译(分析综合)点击Processing——>Start——>Start Analysis & Synthesis,进行分析综合,就好像是对程序进行编译,等待片刻,如果没有错误,编译报告会输出出来。

北邮数电实验Quartus原理图输入法设计与实现

北京邮电大学实验报告Quartus原理图输入法设计与实现学院:信息与通信工程学院班级:姓名:学号:一、实验名称:Quartus II 原理图输入法设计二、实验任务要求:1.用逻辑门实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。

2.用实验内容一中生成的半加器模块和逻辑门实现一个全加器,仿真验证其功能,并下载到实验板上测试,要求用拨码开关设定输入信号,发光二极管显示输出信号。

3. 用3 线-8 线译码器(74LS138)和逻辑门设计并实现相应的函数,仿真验证其功能,并下载到实验板上测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

二.设计思路与过程:真值表:1 1 1 1 1(3)逻辑函数为F=C B A +C B A +C B A +CBA,真值表如下A B C F0 0 0 10 0 1 10 1 0 10 1 1 01 0 0 01 0 1 01 1 0 01 1 1 1运用数字电路中所学习的知识,可以简单设计出半加器,全加器和译码器的实验原理图。

运行并观察仿真结果。

在菜单中选择Pin 项,将自己的输入信号与输出信号与实验板的引脚进行绑定。

将其成功下载后,便可以在实验板上实现相应的功能。

三.实验原理图:1.半加器:2.全加器:3.译码器:四.仿真波形图:1. 半加器:2.全加器:3.译码器:五.仿真波形分析:1. 半加器:半加器是能实现两个1 位二进制数相加求得和数及向高位进位的逻辑电路,加数和被加数分别用a,b 表示,求得的和与向高位进位用变量s,c 来表示。

易得c=ab,s=a⊕b,故只有当a,b 同时为高位时,c才输出高位,只要当a,b 不同时,则s 输出高位。

波形与理论完全符合。

2. 全加器:全加器是实现两个1 位二进制数及低位来的进位相加(即将3 个二进制数相加)求得和数及向高位进位的逻辑电路。

,由其原理易得,s=a⊕b⊕ci ,(a⊕b)c= ci+ab,将理论与波形图对比,完全符合。

QuartusII使用-原理图输入步骤

下载完成后,检查是否有错误信息,如有需要,根据 错误提示进行相应的处理。

谢谢观看

配置引脚分配

根据目标板上的可用引脚,为设计中的各个模块分配引脚。

开始编译

点击“开始编译”按钮,Quartus II将开始对原理图进行编译。

在编译过程中,可以实时查看编译进度和状态信息。

查看编译结果

01

编译完成后,Quartus II将显示编译结果,包括成功、警告和错 误信息。

02

根据编译结果,检查是否存在错误或警告,并相应地调整设计

或编译设置。

如果存在错误,可以查看错误详细信息,以便定位问题并进行

03

修复。

06

下载到 FPGA 设备

选择合适的下载方式

JTAG

通过JTAG接口进行下载,适用于大多数FPGA设备。

USB Blaster

使用USB Blaster进行下载,适用于Altera FPGA设备。

PCIe

通过PCIe接口进行下载,适用于某些高性能FPGA设备。

导出文件

将原理图导出为所需的文件格 式,如PDF、PNG等。

02

创建新项目

选择合适的项目类型

数字逻辑设计

适用于基本的数字逻辑电路设计,如 门电路、触发器等。

微处理器设计

适用于基于微处理器的系统设计,如 单片机、DSP等。

FPGA设计

适用于基于FPGA的硬件设计,如数 字信号处理、图像处理等。

嵌入式系统设计

03

打开原理图编辑器

启动原理图编辑器

打开Quartus II软件,点击"File"菜单, 选择"New" -> "Schematic File"。

用原理图法设计一个3-8译码器组合电路

用原理图法设计一个3-8译码器组合电路用原理图法设计一个3,8译码器组合电路一、实验目的1.通过一个简单的3,8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2.掌握组合逻辑电路的静态测试方法。

3.初步了解可编程器件设计的全过程。

二、实验器材1.台式计算机 1台。

2.可编程逻辑逻辑器件实验软件1套。

3.下载电缆一套。

4.示波器一台。

三、实验说明(台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载1 的平台,供用户使用。

2(可编程逻辑逻辑器件实验软件向原理图的设计提供平台,并将调试好的原理图下载到可编程逻辑逻辑器件中。

3(下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4(示波器用于观察可编程逻辑器件执行程序时输出信号的变化。

四、实验原理说明3线-8线译码器具有将一组三位二进制代码翻译为相对应的输出信号的电路特点。

输出信号D7,D0的表达式功能表输入输出C B A D7 D6 D5 D4 D3 D2 D1 D0Y 0 0 0 0 0 0 0 0 0 0 1 0Y 0 0 1 0 0 0 0 0 0 1 0 1Y 0 1 0 0 0 0 0 0 1 0 0 2Y 0 1 1 0 0 0 0 1 0 0 0 3Y 1 0 0 0 0 0 1 0 0 0 0 4Y 1 0 1 0 0 1 0 0 0 0 0 5Y 1 1 0 0 1 0 0 0 0 0 0 6Y 1 1 1 1 0 0 0 0 0 0 0 7五、实验内容和步骤、建立工程 1(1)软件的启动:打开 Quartus II软件,如图1-1所示。

图1-1(2)启动File菜单,点击New Project Wizard,如下图1-2所示。

图1-2(3)进入向导,选择Next,如图1-3所示。

图1-3(4)设置保存路径,以及项目名称,项目名称为decode3_8,如图1-4所示。

quartus实验报告

quartus实验报告Quartus实验报告引言:Quartus是一种广泛应用于数字电路设计和开发的软件工具,它提供了一个集成的开发环境,用于设计、仿真和编译FPGA(现场可编程门阵列)和CPLD (可编程逻辑器件)等数字电路。

本实验报告将介绍我在使用Quartus进行数字电路设计的经验和成果。

一、实验背景数字电路设计是现代电子工程领域中的重要一环,它涉及到诸如计算机、通信设备、嵌入式系统等各个方面。

在数字电路设计中,Quartus作为一种常用的设计工具,提供了丰富的功能和工具,可以帮助工程师们快速、高效地完成设计任务。

二、实验目的本次实验的目的是通过使用Quartus软件,设计一个简单的数字电路,并进行仿真和编译,以验证设计的正确性和可行性。

通过这个实验,我将学习如何使用Quartus进行数字电路设计,并了解数字电路设计的基本原理和流程。

三、实验过程1. 设计思路在开始设计之前,我首先明确了自己的设计目标和要求。

我选择了一个简单的计数器电路作为我的设计对象。

这个计数器电路可以接受一个时钟信号,并将计数值在7段数码管上显示出来。

我希望通过这个设计,能够加深对数字电路设计的理解,并熟悉Quartus软件的使用。

2. 设计步骤我按照以下步骤完成了我的设计:(1)绘制电路原理图:我使用Quartus提供的原理图编辑器,绘制了我的电路原理图。

在绘制原理图的过程中,我使用了逻辑门、触发器等基本的数字电路元件,并进行了连接和布线。

(2)仿真验证:在完成电路原理图的绘制之后,我使用Quartus提供的仿真工具,对我的电路进行了仿真验证。

通过仿真,我可以观察到电路的输出结果,并检查其是否符合我的设计要求。

(3)编译和下载:在仿真验证通过之后,我使用Quartus的编译工具,将我的设计编译为可下载到FPGA上的二进制文件。

然后,我使用Quartus提供的下载工具,将编译好的文件下载到FPGA上,以实现我的设计功能。

最新quartus__用原理图输入法设计八位全加器实验

q u a r t u s__用原理图输入法设计八位全加

器实验

实验一用原理图输入法设计八位全加器

一实验目的

熟悉利用Quartus II 的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二实验原理

一个8位全加器可以由8个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出 cout 与相邻的高位加法器的最低进位输入信号 cin 相接。

而1位全加器可以按照5.4节介绍的方法来完成。

三实验内容

1:完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设计成一个硬件符号入库。

键1、键2、键3(PIO0/1/2)分别接ain、bin、cin;发光管D2、D1(PIO9/8)分别接sum和cout。

半加器原理图如下所示:

半加器仿真波形图如下图所示:

一位全加器原理图如下所示:

一位全加器仿真波形如下图所示:

2,建立一个更高层次的原理图设计,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真、和硬件测试。

建议选择电路模式1(附图F-2):键2、键1输入8位加数:键4、键3输入8位被加数:数码6和数码5显示加和:D8显示进位cout。

八位全加器原理图如下所示:

八位全加器波形图如下所示:

四实验总结

通过本次实验,我掌握了Quartus II 的原理图输入方法设计简单组合电路和层次化设计的方法和详细流程。

计算机组成原理实验报告_八位补码加减法器的设计与实现

计算机科学与技术学院计算机组成原理实验报告书实验名称八位补码加/减法器的设计与实现班级学号姓名指导教师日期成绩实验1八位补码加/减法器的设计与实现一、实验目的1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握8位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法二、实验任务1.设计一个8位补码加/减法运算器(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

(2)创建波形文件,对该8位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

2.设计8位运算器通路电路参考下图,利用实验任务1设计的8位补码加/减法运算器芯片建立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线BUS7~BUS0上的值与IN0~IN7端输入的数据是否一致。

(2)给DR1存入55H,检查数据是否存入,请说明检查方法。

(3)给DR2存入AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

(6)求12H+34H-56H,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

三、实验要求(1)做好实验预习,掌握运算器的数据传送通路和ALU的功能特性。

(2)实验完毕,写出实验报告,内容如下:①实验目的。

②实验电路图。

③按实验任务3的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。

要求一个控制任务填一张表,并可用文字对有关内容进行说明。

⑤实验体会与小结。

四、实验预习内容1.实验电路设计原理及思路说明本实验利用基本逻辑门电路设计一位全加器(FA),如表1:表1-一位全加器(FA)电路的输入输出信号说明然后以此基础上实现八位补码加/减法器的设计,考虑到实现所需既可以实现加法又可以实现减法,所以使用了一个M输入来进行方式控制加减。

最新Quartus-II使用—原理图输入步骤PPT课件

关闭文件:点击文件右上方“×”符或主菜单File/Close命 令

打开一个已经创建的工程

启动Quartus II后,点击File/Open Project…

(*.qpf)

三、设计输入——原理图设计输入

宏功能函数(megafunctions)库中包含很多种可直接使用的 参数化模块,基本单元符号(Primitives)库中包含所有Altera 公司的基本单元,其他库(Others)中包含与MAX+PLUS II兼 容的所有中规模器件,如常用的74系列符号。

际地刮着,使窗户随隙发出一阵阵鸣叫。

我呆呆地坐在座位上看杂志,看到了一篇关于母爱的文章,是我不禁想起了 妈妈......

以前有的晚上学习到很晚,这时,妈妈就会端来我最喜欢的绿豆汤,慈祥地

看着我,把汤一口一口喝完。然后替我整理好床,劝我早点去睡觉;有时,在 外面受了气,就在妈妈面前大发脾气,但妈妈从不计较,反而还安慰我,是我 心情好起来;以前......

3、编辑输入节点波形

时钟节点波形的输入——

在时钟节点名(如CLK)上单击鼠标右键,然后从弹出的快捷菜单中选择 “Value→Clock”命令

总线信号波形的输入——

在总线节点名上单击鼠标右键,然后选择“Value/Count Value”命令, 便可设置总线为计数输入;同时也可以通过选择“Value/Arbitrary Value” 命令,设置总线为任意固定值输入。

9.树立靶子。 写驳论文,最好是在文章的开头就先亮出对

方的谬论,并将其当做靶子深入批驳。 例如,《个人与集体》这篇文章,作者就是

先提出: 有人提出这样一种人生哲学,叫“人人为我,

也就是大家为我”,接着便具体分析这种错误的 人生观,并进行了抨击。

8QUARTUS使用及原理图设计

电子信息工程学院

60

10

设计流程归纳

2位十进制数字频率计设计

用74390设计一个有时钟使能的两位十进制计数器 (1) 设计电路原理图。

图4-23 MAX+plusII一般设计流程

QUARTUS使用及原理图

QUARTUS使用及原理图

电子信息工程学院

20

3.编译设计文件

QuartusⅡ软件中的编译类型有全编译和分步编译两种。 全编译的过程包括分析与综合(Analysis & Synthesis

)、适配(Fitter)、编程(Assembler)、时序分析 (Classical Timing Analysis)这4个环节,而这4个环节 各自对应相应的菜单命令,可以单独分步执行,也就是分 步编译。

消去这里的勾, 以便方便设置 输入电平

图4-9 列出并选择需要观察的信号节点 图4-10 在Options菜单中消去网格对齐Snap to Grid的选择(消去对勾)

QUARTUS使用及原理图

电子信息工程学院

选择END TIME 调整仿真时间

区域。

图4-11 设定仿真时间

QUARTUS使用及原理图

电子信息工程学院

电子信息工程学院

42

7

步骤3:将设计项目设置成工程文件(PROJECT)

首先点击这里

最后注意此路 径指向的改变

然后选择此项, 将当前的原理图 设计文件设置成

工程

注意,此路径指 向当前的工程!

Q图UA4R-T5US将使用当及前原设理计图 文件设置成工电子程信文息件工程学院

43

QUARTUS使用及原理图

一位全加器可由两个一位半加器完成。 为全加器新建工程,并将半加器生成的符号文件

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

点击“LIST”

(2) 输入信号节点。

图4-8 从SNF文件中输入设计文件的信号节点

QUARTUS使用及原理图

电子信息工程学院

最后点击“OK”

图4-9 列出并选择需要观察的信号节点

用此键选择左窗 中需要的信号 进入右窗

QUARTUS使用及原理图

电子信息工程学院

(4) 设定仿真时间。

(3) 设置波形参量。

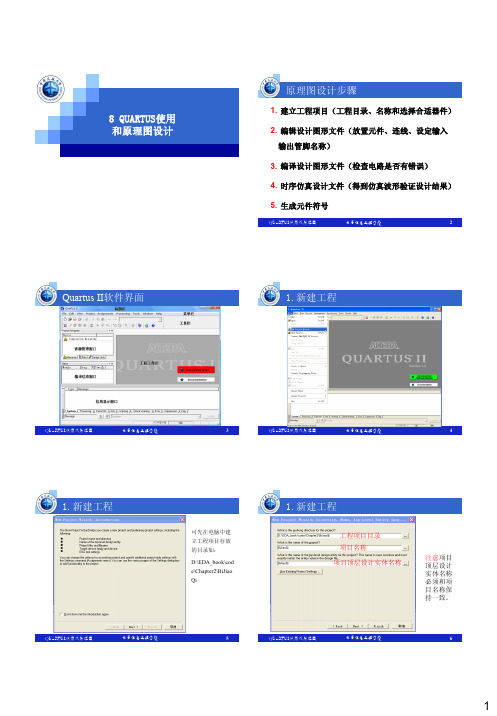

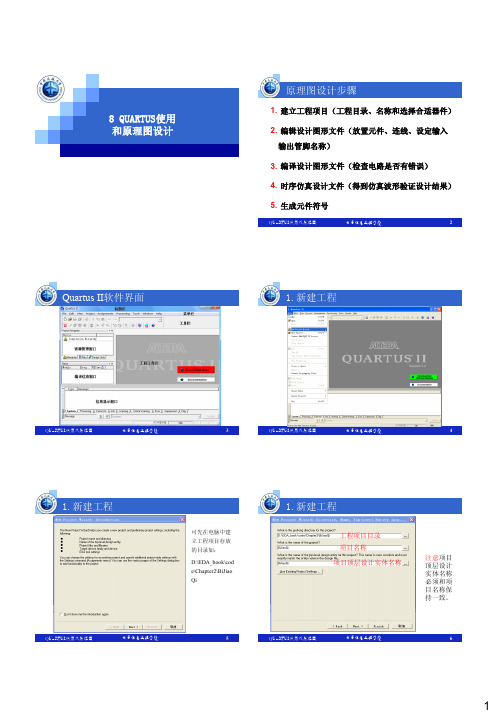

8 QUARTUS使用 和原理图设计

Quartus II软件界面

原理图设计步骤

1. 建立工程项目(工程目录、名称和选择合适器件)

2. 编辑设计图形文件(放置元件、连线、设定输入 输出管脚名称)

3. 编译设计图形文件(检查电路是否有错误)

4. 时序仿真设计文件(得到仿真波形验证设计结果)

5. 生成元件符号

电子信息工程学院

40

输入引脚: INPUT

输出引脚: OUTPUT

将所需元件全部调入原理图编辑窗

将他们连接 成半加器

连接好的原理图

QUARTUS使用及原理图

电子信息工程学院

41

首先点击这里

文件名取为: h_adder.gdf

注意,要存在 自己建立的

文件夹中

连接好原理图并存盘

QUARTUS使用及原理图

连接各个元件符号:把鼠标移置一个input元件连接处,单 击鼠标左键,移到要与之相连的非门元件的连接处,松开 鼠标即可连接两个要连的元件。

2.编辑原理图设计文件

设定各输入、输出引 脚名:双击任意一个 input元件,将会弹出 右图所示的引脚属性 编辑对话框

QUARTUS使用及原理图

电子信息工程学院

19

QUARTUS使用及原理图

电子信息工程学院

2

1.新建工程

QUARTUS使用及原理图

电子信息工程学院

3

QUARTUS使用及原理图

电子信息工程学院

4

1.新建工程

可先在电脑中建 立工程项目存放 的目录如:

D:\EDA_book\cod e\Chapter2\BiJiao Qi

1.新建工程

工程项目目录 项目名称 项目顶层设计实体名称

一位全加器可由两个一位半加器完成。 为全加器新建工程,并将半加器生成的符号文件

和原理图文件(.bdf)都拷贝到全加器工程目录 中。

37

QUARTUS使用及原理图

电子信息工程学院

38

全加器

原理图设计实例(Maxplus II)

半加器 全加器

QUARTUS使用及原理图

电子信息工程学院

39

QUARTUS使用及原理图

QUARTUS使用及原理图

电子信息工程学院

7

1.新建工程

选择Cyclone系列

QUARTUS使用及原理图

电子信息工程学院

选择器件的封 装形式、引脚 数目和速度级 别约束可选器 件的范围。

8

1.新建工程

1.新建工程

询问是否选择其他EDA工具

QUARTUS使用及原理图

电子信息工程学院

显示由新建工程指南建立的工程文件摘要

原理图绘制区

2.编辑原理图设计文件

QUARTUS使用及原理图

电子信息工程学院

13

QUARTUS使用及原理图

电子信息工程学院

14

2.编辑原理图设计文件

比较器的原理图

QUARTUS使用及原理图

电子信息工程学院

2.编辑原理图设计文件

双击鼠标的左键,将弹出Symbol对话框,或单击鼠标右键,在弹出 的选择对话框中选择Insert-Symbol,也会弹出该对话框。

电子信息工程学院

29

QUARTUS使用及原理图

电子信息工程学院

30

5

4.时序仿真

5.生成原件符号

执行File-Create/Update-Create Symbol File for Current File 命令将本设计电路封装成一个元件符号,供以后在原理图编 辑器下进行层次设计时调用。

QUARTUS使用及原理图

全编译操作简单,适合简单的设计。对于复杂的设计,选 择分步编译可以及时发现问题,提高设计纠错的效率,从 而提高设计效率。

QUARTUS使用及原理图

电子信息工程学院

21

3.编译设计文件

RTL阅读器:在设计的调试和优化过程中,可以使 用RTL阅读器观察设计电路的综合结果,同时也可 以观察源设计如何被翻译成逻辑门、原语等

QUARTUS使用及原理图

电子信息工程学院

57

全加器

(1) 仿照前面的“步骤2”,打开一个新的原理图编辑窗口

QUARTUS使用及原理图

在顶层编辑窗中调出已 设计好的半加器元件

电子信息工程学院

58

(2) 完成全加器原理图设计,并以文件名f_adder.gdf存在同一目录中。

(5) 对应f_adder.gdf的波形仿真文件,参考图中输入信号cin、bin和ain输 入信号电平的设置,启动仿真器Simulator,观察输出波形的情况。

电子信息工程学院

31

QUARTUS使用及原理图

电子信息工程学院

32

5.生成原件符号

生成的符号存放在本工程目录下,文件名BiJiaoQi, 文件后缀名.bsf

原理图设计实例

半加器 1. 调入原件 2. 连线 3. 端口命名 4. 存盘编译 5. 时序验证 6. 生成符号

全加器

QUARTUS使用及原理图

电子信息工程学院

27

QUARTUS使用及原理图

电子信息工程学院

28

4.时序仿真

设置仿真时间长度:默认为1us,通常将其设置为100us

4.时序仿真

设置网格尺寸:默认为10ns, 由于竞争冒险的存在,在仿 真时信号波形和大量毛刺混 叠在一起,影响仿真结果, 通常设置为500ns

QUARTUS使用及原理图

消去这里的勾, 以便方便设置 输入电平

图4-9 列出并选择需要观察的信号节点 图4-10 在Options菜单中消去网格对齐Snap to Grid的选择(消去对勾)

QUARTUS使用及原理图

电子信息工程学院

选择END TIME 调整仿真时间

区域。

图4-11 设定仿真时间

QUARTUS使用及原理图

电子信息工程学院

图4-21 在顶层编辑窗中设计好全加器 (3) 将当前文件设置成Project。 (4) 编译此顶层文件f_adder.gdf,然后建立波形仿真文件。

QUARTUS使用及原理图

电子信息工程学院

59

图4-22 1位全加器的时序仿真波形 (6) 锁定引脚、编译并编程下载,硬件实测此全加器的逻辑功能。

QUARTUS使用及原理图

选择编译器

QUARTUS使用及原理图

电子信息工程学院

编译窗

完成编译!

步骤5:时序仿真

首先选择此项, 为仿真测试新 建一个文件

选择波形 编辑器文件

QUARTUS使用及原理图

电子信息工程学院

QUARTUS使用及原理图

(1)

建立波形文件。

电子信息工程学院

8

从SNF文件中 输入设计文件

的信号节点

SNF文件中 的信号节点

9

QUARTUS使用及原理图

电子信息工程学院

10

1.新建工程

QUARTUS使用及原理图

电子信息工程学院

AHDL文本文件 流程图和原理图文件

网表文件 在线系统文件 Verilog HDL文本文件 VHDL文本文件

11

QUARTUS使用及原理图

电子信息工程学院

12

2

2.编辑原理图设计文件

工程文件名

绘制工具

基本元件库 Logic子库包含与门、或门和非门

重复-插入模式选否 作为流程图模块插入符号选否

15

QUARTUS使用及原理图

电子信息工程学院

16

2.编辑原理图设计文件

2.编辑原理图设计文件

QUARTUS使用及原理图

电子信息工程学院

17

QUARTUS使用及原理图

电子信息工程学院

18

3

2.编辑原理图设计文件

选择60微秒 比较合适

(5) 加上输入信号。

(6) 波形文件存盘。

用此键改变仿真 区域坐标到合适

位置。

点击‘1’,使拖黑 的电平为高电平

图4-12 为输入信号设定必要的测试电平或数据

QUARTUS使用及原理图

电子信息工程学院图4-13 保存仿真波形文件

(7) 运行仿真器。 选择仿真器

图4-14 运行仿真器

电子信息工程学院

42

7

步骤3:将设计项目设置成工程文件(PROJECT)

首先点击这里

最后注意此路 径指向的改变

然后选择此项, 将当前的原理图 设计文件设置成

工程

注意,此路径指 向当前的工程!

Q图UA4R-T5US将使用当及前原设理计图 文件设置成工电子程信文息件工程学院

43

QUARTUS使用及原理图

QUARTUS使用及原理图

电子信息工程学院

22

3.编译设计文件

QUARTUS使用及原理图

电子信息工程学院

3.编译设计文件

RTL阅读器窗口的右边,是过程设计结果的主窗口,包 括设计电路的模块和连线,RTL阅读器的左边是层次列 表,在每个层次上一树状形式列出了设计电路的所有 单元。层次列表的内容包括以下几个方面:

注意项目 顶层设计 实体名称 必须和项 目名称保 持一致。

QUARTUS使用及原理图

电子信息工程学院

5