TLC2543中文数据手册

TLC2543 芯片资料

IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

tlc2543中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9688601QRA ACTIVE CDIP J201TBD A42N/A for Pkg Type TLC2543CDB ACTIVE SSOP DB2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CDBG4ACTIVE SSOP DB2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TLC2543CDBLE OBSOLETE SSOP DB20TBD Call TI Call TITLC2543CDBR ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CDBRG4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CDW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CDWG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CDWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CDWRG4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543CFN ACTIVE PLCC FN2046Green(RoHS&no Sb/Br)CU SN Level-1-260C-UNLIMTLC2543CFNG3ACTIVE PLCC FN2046Green(RoHS&no Sb/Br)CU SN Level-1-260C-UNLIMTLC2543CFNR ACTIVE PLCC FN201000Green(RoHS&no Sb/Br)CU SN Level-1-260C-UNLIMTLC2543CFNRG3ACTIVE PLCC FN201000Green(RoHS&no Sb/Br)CU SN Level-1-260C-UNLIMTLC2543CN ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLC2543CNE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLC2543IDB ACTIVE SSOP DB2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDBG4ACTIVE SSOP DB2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDBR ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDBRG4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDW ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDWG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDWR ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IDWRG4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLC2543IFN ACTIVE PLCC FN2046Green(RoHS&no Sb/Br)CU SN Level-1-260C-UNLIMTLC2543IFNG3ACTIVE PLCC FN2046Green(RoHS&CU SN Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)TLC2543IFNR OBSOLETE PLCC FN20TBD Call TI Call TITLC2543IN ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLC2543INE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type TLC2543MJ ACTIVE CDIP J201TBD A42N/A for Pkg Type TLC2543MJB ACTIVE CDIP J201TBD A42N/A for Pkg Type (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF TLC2543,TLC2543M:•Automotive:TLC2543-Q1•Enhanced Product:TLC2543-EPNOTE:Qualified Version Definitions:•Automotive-Q100devices qualified for high-reliability automotive applications targeting zero defects•Enhanced Product-Supports Defense,Aerospace and Medical ApplicationsTAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant TLC2543CDBR SSOP DB 202000330.016.48.27.5 2.512.016.0Q1TLC2543IDBRSSOPDB202000330.016.48.27.52.512.016.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) TLC2543CDBR SSOP DB202000346.0346.033.0TLC2543IDBR SSOP DB202000346.0346.033.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。

TLC2543程序

//========================================================== ===========// tlc2543驱动程序//tlc2543.c//writer:谷雨2008年3月12日于EDA实验室整理//========================================================== ===========#include#define uint unsigned int#define uchar unsigned char//**************************修改硬件时要修改的部分********************************sbit clock = P0^0; //输入、输出时钟端sbit input = P0^1; //数据输入端sbit output = P0^2; //数据输出端sbit CS = P0^3; //片选端,负电平有效void delay(uchar N){while(N--);}uint read2543(uchar CON_WORD) //CON_WORD为选择的通道,为0--10 {uint ad=0;uchar i;CON_WORD<<=4;clock=0;CS=0;for(i=0;i<12;i++){if(output==1) //读取DATAOUTad=ad|0x01;if(CON_WORD&0x80) //读取控制字到INPUTinput=1;elseinput=0;clock=1;delay(10);clock=0;delay(10);CON_WORD<<=1;ad<<=1;}CS=1;ad>>=1;return(ad);}void init_serial() //初始化串口{TMOD=0x20; //定时器T1使用工作方式2TH1=250; //设置初值TH0=250;TR1=1; //开始计时PCON=0x80; //SMOD=1;SCON=0x50; //工作方式1,波特率9600bit/s,允许接收TI=1;}void main(){uint ad=0;float fVoltage1;uchar buf[5],i;init_serial();IE=0; //屏蔽中断while(1){ad=read2543(0);fVoltage1=(float)ad/0x0fff*5;buf[0]=(uchar)fVoltage1;buf[0]=buf[0]+0x30;buf[1]=''.'buf[2]=(uchar)(fVoltage1*10)%10;buf[2]=buf[2]+0x30;buf[3]=(uchar)(fVoltage1*100-buf[0]*100)%10;buf[3]=buf[3]+0x30;buf[4]=(uchar)((fVoltage1*1000)-buf[0]*1000-buf[1]*100)%10; buf[4]=buf[4]+0x30;i=0;while(i<5){if(TI==1){SBUF=buf[i];TI=0;i++;}}} }。

TLC2543中文资料

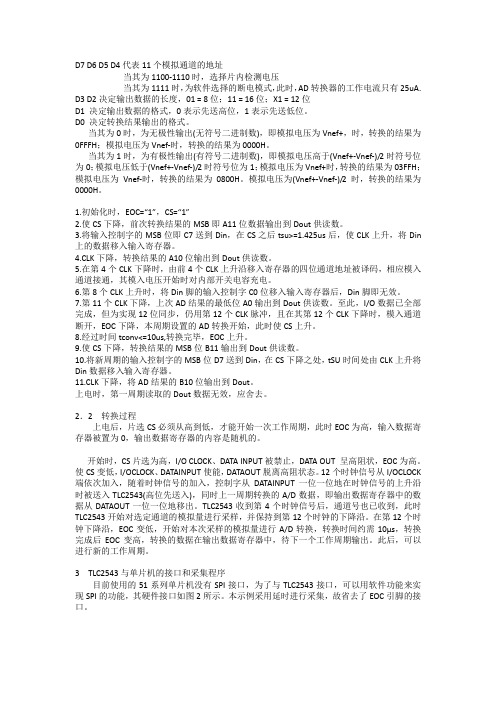

D7 D6 D5 D4代表11个模拟通道的地址当其为1100-1110时,选择片内检测电压当其为1111时,为软件选择的断电模式,此时,AD转换器的工作电流只有25uA. D3 D2决定输出数据的长度,01 = 8位;11 = 16位;X1 = 12位D1 决定输出数据的格式,0表示先送高位,1表示先送低位。

D0 决定转换结果输出的格式。

当其为0时,为无极性输出(无符号二进制数),即模拟电压为Vnef+,时,转换的结果为0FFFH;模拟电压为Vnef-时,转换的结果为0000H。

当其为1时,为有极性输出(有符号二进制数),即模拟电压高于(Vnef+-Vnef-)/2时符号位为0;模拟电压低于(Vnef+-Vnef-)/2时符号位为1;模拟电压为Vnef+时,转换的结果为03FFH;模拟电压为Vnef-时,转换的结果为0800H。

模拟电压为(Vnef+-Vnef-)/2时,转换的结果为0000H。

1.初始化时,EOC=“1”,CS=“1”2.使CS下降,前次转换结果的MSB即A11位数据输出到Dout供读数。

3.将输入控制字的MSB位即C7送到Din,在CS之后tsu>=1.425us后,使CLK上升,将Din 上的数据移入输入寄存器。

4.CLK下降,转换结果的A10位输出到Dout供读数。

5.在第4个CLK下降时,由前4个CLK上升沿移入寄存器的四位通道地址被译码,相应模入通道接通,其模入电压开始时对内部开关电容充电。

6.第8个CLK上升时,将Din脚的输入控制字C0位移入输入寄存器后,Din脚即无效。

7.第11个CLK下降,上次AD结果的最低位A0输出到Dout供读数。

至此,I/O数据已全部完成,但为实现12位同步,仍用第12个CLK脉冲,且在其第12个CLK下降时,模入通道断开,EOC下降,本周期设置的AD转换开始,此时使CS上升。

8.经过时间tconv<=10us,转换完毕,EOC上升。

2543中文资料

2543中⽂资料PROTECTEDQUAD POWER DRIVERProviding interface between low-level logic and power loads to 100 W, the UDx2543B and UDx2543EB quad power drivers combine AND logic gates and high-current bipolar outputs. Each of the four independent outputs can sink up to 700 mA in the ON state. The outputs have a minimum breakdown voltage (load dump) of 60 V and a sustaining voltage of 35 V. The inputs are compatible with most TTL, DTL, LSTTL, and 5 V CMOS and PMOS logic systems.Over-current protection has been designed into each channel of the UDx2543B/EB and typically occurs at 1 A. It protects any one channel from output short circuits with supply voltages up to 25 V.When the maximum output current is reached, that output stage is driven linearly. If the over-current condition continues, that output’s thermal limiting will operate, limiting that output’s power dissipation to approximately 2.4 W. The outputs also include diodes for voltage clamping with inductive loads such as relays, solenoids, or dc stepper motors.These devices are supplied in a 16-pin power DIP of batwing construction (suffix ‘B’) to provide for maximum package power dissi-pation. They are also available in a 28-lead PLCC (suffix ‘EB’) for surface-mount applications. All devices are rated for continuousoperation over the temperature range of -20°C to +85°C (UDN2543B/EB) or for use in automotive applications over an extended tempera-ture range as the UDQ2543B/EB.FEATURESI 700 mA Output Current per Channel I Low Output-Saturation VoltageI Integral Output Transient-Suppression Diodes I TTL, CMOS, PMOS, NMOS Compatible InputsIIndependent Over-Current Protection for Each OutputData Sheet29317.2BAlways order by complete part number:Part Number Package Operating Temperature UDN2543B 16-Pin DIP -20°C to +85°C UDN2543EB 28-Lead PLCC -20°C to +85°C UDQ2543B 16-Pin DIP -40°C to +85°C UDQ2543EB28-Lead PLCC-40°C to +85°C25432543PROTECTEDQUAD POWER DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000NOTE:These devices do not include an absolute thermal shutdown. Package power dissipation under fault conditions (2.4 W in the faultedchannel) must therefore be evaluated at maximum operating temperature.GROUNDGROUND GROUNDGROUNDDwg. PP-019-1KN O C O N N E C T I O NE N A B L ES U P P L YO U T 1O U T 2O U T 3O U T 4I N 4I N 3I N 2I N 1N OC O N N E C T I O NKUDN/UDQ2543EB10642A L L O W AB L E P AC K A G E P O W E RD I S S I P A T I O N I N W A T T STEMPERATURE IN °C8Dwg. GP-004-1ACopyright ? 1986, 1993, Allegro MicroSystems, Inc.2543PROTECTEDQUAD POWER DRIVERELECTRICAL CHARACTERISTICS at T A= +25°C (UDN2543B/EB) or over operating temperature range (UDQ2543B/EB only), V CC = 4.75 V to 5.25 VLimits Characteristic Symbol Test Conditions Min.Max.Units Output Leakage Current I CEX V OUT = 60 V, V IN = 0.8 V, VEN = 2.0 V—100µAV OUT = 60 V, V IN = 2.0 V, V EN = 0.8 V—100µA Output Sustaining Voltage V OUT(SUS)I OUT = 100 mA, V IN = V EN =0.8 V35—V Output Saturation Voltage V OUT(SAT)I OUT = 100 mA, V IN = V EN = 2.0 V—200mVI OUT = 400 mA, V IN = V EN = 2.0 V—400mVI OUT = 700 mA, V IN = V EN = 2.0 V—600mVInput Voltage Logic 1V IN(1) or V EN(1) 2.0—VLogic 0V IN(0) or V EN(0)—0.8V Input Current Logic 1V IN(1) or V EN(1) = 2.0 V—20µALogic 0V IN(0) or V EN(0) = 0.8 V—-10µA Total Supply Current I CC I OUT = 700 mA*, V IN? = V EN = 2.0 V—65mA Outputs Open, V IN? = 0.8 V, V EN = 2.0 V—15mA Clamp Diode Forward Voltage V F I F = 1.0 A— 1.6VI F = 1.5 A— 2.0VClamp Diode I R V R = 60 V, V IN = V EN = 2.0 V,—50µA Leakage CurrentD1 + D2 or D3 + D4Negative current is defined as coming out of (sourcing) the specified terminal.As used here, -100 is defined as greater than +10 (absolute magnitude convention) and the minimum is implicitly zero.* Pulse test, allowable package power dissipation will be exceeded at increased ambient temperatures.All inputs simultaneously, all other tests are performed with each input tested separately.2543PROTECTEDQUAD POWER DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TYPICAL OUTPUT BEHAVIORCIRCUIT DESCRIPTION AND APPLICATIONINCANDESCENT LAMP DRIVERFor incandescent lamp applications, the UDx2549B/EB or UDx2559B/EB, with improved shortcircuit protection and thermal limiting, are recommended.INDUCTIVE LOAD DRIVERBifilar (unipolar) stepper motors, relays, or solenoids can be driven directly. The internal flyback diodes prevent damage to the output transistors by suppressing the high-voltage spikes that occur when turning OFF an inductive load. For rapidcurrent decay (fast turn-OFF speeds), the use of Zener diodes will raise the flyback voltage andimprove performance. However, the peak voltage must not exceed the specified minimum sustaining voltage (V SUPPLY + V Z + V F ≤ V OUT(SUS)).FAULT CONDITIONSIn the event of a shorted load, the load current will attempt to increase. As described above, the drive current to the affected output stage is diverted, causing the output stage to go linear, limiting the peak output current to approximately 1 A. As the power dissipation of that output stage increases, a thermal gradient sensing circuit will become operational, further decreasing the drive current to the af-fected output stage and reducing the output current to a value depen-dent on supply voltage (I OUT ≈ 2.4/V SUPPLY ). If the fault condition is corrected, the output stage will return to its normal saturated condition.Due to the independent operation of the four channels, only a single channel should be shorted at a time. Multiple overload conditions may be tolerated provided rated package power dissipation is not exceeded.TIMEDwg. WP-013-1O U T P U T C U R R E N T2543PROTECTEDQUAD POWER DRIVERNOTES:1.Exact body and lead configuration at vendor ’s option within limits shown.2.Lead spacing tolerance is non-cumulative3.Lead thickness is measured at seating plane or below.4.Webbed lead frame. Leads 4, 5, 12, and 13 are internally one piece.UDN2543B and UDQ2543BDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)Dwg. MA-001-17A in18Dwg. MA-001-17A mm182543PROTECTEDQUAD POWER DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000UDN2543EB and UDQ2543EBDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)NOTES:1.Exact body and lead configuration at vendor ’s option within limits shown.2.Lead spacing tolerance is non-cumulative3.Webbed lead frame. Leads 5 through 11 and 19 through 25 are internally one piece. Dwg. MA-005-28A in5Dwg. MA-005-28A mm52543PROTECTEDQUAD POWER DRIVERThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use. 2543PROTECTEDQUAD POWER DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWER SINK DRIVERSIN ORDER OF 1) OUTPUT CURRENT, 2) OUTPUT VOLTAGE, 3) NUMBER OF DRIVERSOutput Ratings *Features Serial Latched Diode Internal mAV #Input DriversClampOutputsProtectionPart Number75178X X –constant current –62751716X X –constant current –627610020 8–––saturated –25953032X X –––58334032X X –saturated –583250 8addressable decoder/driver DMOS –6B25950 8–X –DMOS –6B27350 8X X –DMOS –6B59525050 8addressable decoder/driver DMOS –625950 8–X –DMOS –627350 8X X –DMOS –6595135 7––X ––700330045 1–Hall sensor/driver X –X 514050 7––X ––200350 8––X ––280350 8––X saturated –259660 4––X saturated X 255795 7––X ––202395 8––X ––282335050 4–X X ––580050 7––X ––200450 8––X ––280450 8–X X ––580150 8X X –––582150 8X X X ––584150 8addressable decoder/driver DMOS –6A25950 8X X –DMOS –6A59580 8X X –––582280 8X X X ––584295 7––X ––202495 8––X ––2824 4503028dual 4- to 14-line decoder/driver ––681760060 4–––saturated X 254760 4––X saturated X 254970060 4––X saturated X 2543 and 255975050 8––X saturated –259790014 2–Hall sensor/driver X saturated X 362526 2–Hall sensor/driver X saturated X 3626100046 4stepper motor controller/driver MOS –7024 and 7029120046 4microstepping controller/driver MOS –7042125050 4stepper motor translator/driver –X 580450 4––X ––2064 and 2068150080 4––X ––2065 and 2069180050 4––X ––254450 4––X ––2540300046 4stepper motor controller/driver MOS –702646 4microstepping controller/driver MOS –7044400050 4––X ––287880 4––X ––2879over-current protection voltage limits.Complete part number includes additional characters to indicate operating temperature range and package style.。

TLC2543中文资料

串行A D转换器T L C2543中文资料TLC2543是TI公司的12位串行模数转换器,使用开关电容逐次逼近技术完成A/D转换过程。

由于是串行输入结构,能够节省51系列单片机I/O资源;且价格适中,分辨率较高,因此在仪器仪表中有较为广泛的应用。

2TLC2543的特点(1)12位分辩率A/D转换器;(2)在工作温度范围内10μs转换时间;(3)11个模拟输入通道;(4)3路内置自测试方式;(5)采样率为66kbps;(6)线性误差±1LSBmax;(7)有转换结束输出EOC;(8)具有单、双极性输出;(9)可编程的MSB或LSB前导;(10)可编程输出数据长度。

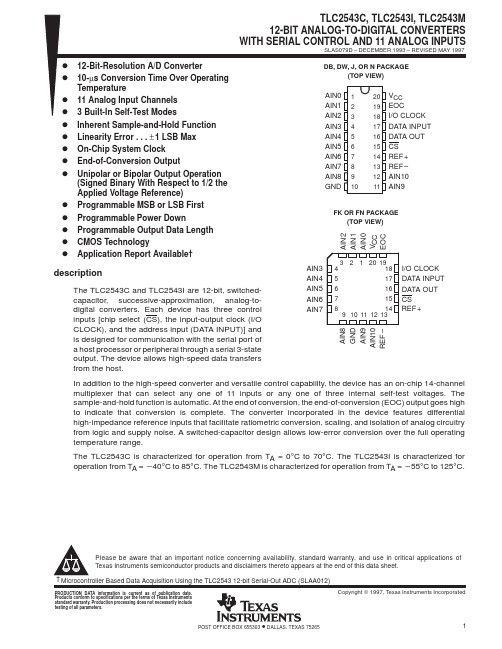

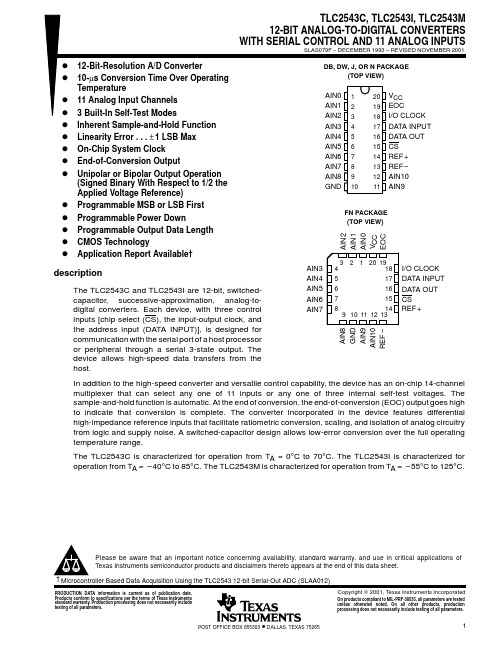

3TLC2543的引脚排列及说明TLC2543有两种封装形式:DB、DW或N封装以及FN封装,这两种封装的引脚排列如图1,引脚说明见表1。

图1T L C2543的封装4接口时序可以用四种传输方法使T L C2543得到全12位分辩率,每次转换和数据传递可以使用12或16个时钟周期。

一个片选()脉冲要插到每次转换的开始处,或是在转换时序的开始处变化一次后保持为低,直到时序结束。

图2显示每次转换和数据传递使用16个时钟周期和在每次传递周期之间插入的时序,图3显示每次转换和数据传递使用16个时钟周期,仅在每次转换序列开始处插入一次时序。

引脚号名称I/O说明1~9,11,12AIN0~AIN10I模拟量输入端。

11路输入信号由内部多路器选通。

对于的I/OCLOCK,驱动源阻抗必须小于或等于50Ω,而且用60pF电容来限制模拟输入电压的斜率15I片选端。

在端由高变低时,内部计数器复位。

由低变高时,在设定时间内禁止DATAINPUT和I/OCLOCK17DATAINPUT I串行数据输入端。

由4位的串行地址输入来选择模拟量输入通道16DATAOUT O A/D转换结果的三态串行输出端。

为高时处于高阻抗状态,为低时处于激活状态19EOC O转换结束端。

TLC2543 中文资料

TLC2543 中文资料TLC2543是TI公司的12位串行模数转换器,使用开关电容逐次逼近技术完成A/D转换过程。

由于是串行输入结构,能够节省51系列单片机I/O资源;且价格适中,分辨率较高,因此在仪器仪表中有较为广泛的应用。

2 TLC254 ...TLC2543是TI公司的12位串行模数转换器,使用开关电容逐次逼近技术完成A/D 转换过程。

由于是串行输入结构,能够节省51系列单片机I/O资源;且价格适中,分辨率较高,因此在仪器仪表中有较为广泛的应用。

2 TLC2543的特点(1)12位分辩率A/D转换器;(2)在工作温度范围内10μs转换时间;(3)11个模拟输入通道;(4)3路内置自测试方式;(5)采样率为66kbps;(6)线性误差±1LSBmax;(7)有转换结束输出EOC;(8)具有单、双极性输出;(9)可编程的MSB或LSB前导;(10)可编程输出数据长度。

3TLC2543的引脚图(管脚图)及说明TLC2543有两种封装形式:DB、DW或N封装以及FN封装,这两种封装的引脚排列如图1,引脚说明见表1。

表1 TLC2543引脚说明引脚号名称I/O 说明1~9,11,12 AIN0~AIN10 I 模拟量输入端。

11路输入信号由内部多路器选通。

对于4.1MHz的I/OCLOCK,驱动源阻抗必须小于或等于50Ω,而且用60pF电容来限制模拟输入电压的斜率15 I 片选端。

在端由高变低时,内部计数器复位。

由低变高时,在设定时间内禁止DATAINPUT和I/O CLOCK17 DATAINPUT I 串行数据输入端。

由4位的串行地址输入来选择模拟量输入通道16 DATA OUT O A/D转换结果的三态串行输出端。

为高时处于高阻抗状态,为低时处于激活状态19 EOC O 转换结束端。

在最后的I/OCLOCK下降沿之后,EOC从高电平变为低电平并保持到转换完成和数据准备传输为止10 GND 地。

关于TLC2543的总结

关于TLC2543的一些问题TLC2543是我调的第四个模块,严格意义上说第三个,因为A/D与D/A是相互配合使用的,在原理上有很多相同的地方。

比如逐次逼近式的A/D转换芯片,内部就存在一个D/A转换器。

总之二者在原理上有相通的地方,下面是我在调试芯片过程中遇到的一些问题:1、下面是它的管脚图以及结构框图:图1、TLC2543NC管脚图图2、2543的结构框图2、它有0~10共11个输入端口,也就是有11个通道,这11个通道是由DA TA IN的高四位决定的,而DA TA IN的低四位决定了是采用8位、12位还是16位数据输出格式,以及输出是单极性输出还是双极性输出,详见表1.需要注意的是这里的DATA IN并不是用于转换的输入数据,而是对输入通道,及一些相关格式的选择数据,相当于命令数据。

DATA OUT是一个串行的输出端,将输入的模拟量转换为数字量后,一位一位输出出来。

转换结束的信号是由EOC决定的,当它为低时表示转换结束,为高时表示正在转换,这里需要注意的是,现在转换的信号,并须在下一次有效输出信号来临时,才被输出;而当前输出的数据世上一次操作转换的结果,所以要输出当前的转换结果,至少要执行两次有效输出,才能得到正确结果。

表1、2543的输入数据功能表3、下面是2543在使用时的两种不同模式,一种是使用~CS端进行控制,一种是不使用。

很显然,第二种,2543时刻都被选通,时刻都在准备进行数据的转换,这样必然会有一定的功耗,所以如果能合理地设计~CS的选通状态,就可以减少电路的功耗。

同样的,还有以8位数据及16位数据格式输出,原理及时序图都与12位的相同,只有输出结果的位数不同,当然,相应的精度也就不同。

可根据具体需要,进行设置。

图3、采用12位输出数据并使用~CS时的序图图4、采用12位输出数据并不使用~CS时的序图。

TL2543

图3.5TLC2543芯片引脚图图3.6内部结构图3.6 TLC2543芯片引脚及内部结构TLC2543是德州仪器公司生产的12位开关电容型逐次逼近模数转换器,最大转换时间10us,11个模拟输入通道,3路内置自测试方式,采样率为66KSPS,线性误差±1LSBmax,有转换结束输出EOC,具有单极、双极性输出,可编程的MSB或LSB前导,可编程输出数据长度。

它具有三个控制输入端,采用简单三线SPI串行接口可方便的与微机进行连接,图3.5和图3.6分别是TLC2543的引脚排列图和内部结构图。

表3.2是TLC2543的引脚功能说明。

3.7 TLC2543的工作方式和输入通道的选择TLC2543是一个多通道和多工作方式的模数转换器件。

图3.5为其芯片引脚图,图3.6是它的内部结构图。

其工作方式和输入通道的选择是通过向TLC2543的控制寄存器写入一个八位的控制字来实现的。

这个八位控制字由四个部分组成:D7D6D5D4选择输入通道,D3D2选择输出数据长度,D1选择输出数据顺序,D0选择转换结果的极性。

八位控制字的各位的含义如表3.3所示。

主机以MSB为前导方式将控制字写入TLC2543的控制寄存器,每个数据位都是在CLOCK序列的上升沿被写入控制器。

表3.2引脚功能说明3.7.1 TLC2543的读写时序当片选信号/CS为高电平时,CLOCK和DATA-IN被禁止、DATA-OUT为高阻状态,以便SPI总线上的其它器件让出总线。

在片选信号/CS的下降沿,A/D转换结果的第一位数据出现在DATA-OUT引脚上,A/D转换结果的其他数据位在时钟信号CLOCK的下降沿被串行输出到DATA-OUT。

在片选信号/CS下降以后,时钟信号CLOCK的前八个上升沿将八位控制字从DATA_IN引脚串行输入到TLC2543的控制寄存器。

在片选信号/CS下降以后,经历8个(12个或16个)时钟信号完成对A/D转换器的一次读写。

TLC2543中文资料_数据手册_参数

万联芯城专注电子元器件配单服务,只售原装现货库存,万联芯城 电子元器件全国供应,专为终端生产,研发企业提供现货物料, 价格优势明显,BOM配单整单采购可享优惠价,提交BOM表报价 ,最快可当天发货,万联芯城电子元器件配单服务可以为客户节 省采购成本,满足客户物料需求,丰富的电子元器件供应链体系 已为全国多家终端企业服务,点击进入万联芯城。

合格的汽车ApplicationsD 12位分辨率A / D ConverterD 10-µs转换时间在OperatingTemperatureD 11模拟输入ChannelsD三内建自测ModesD固 有取样保持的FunctionD线性误差。±1 LSB MaxD片上TLC2543系统ClockD转换末尾OutputD单极或双极输出操作(签署二进制对1/2 theApplied参考电压)D可编程MSB和LSB FirstD可编程电源DownD可编程输出数据LengthD CMOS TechnologyD申请报告可用‡ descriptionThe TLC2543 12位,开关电容,逐次逼近,数模转换器。每台设备有三个控制输入(芯片选择(CS)、输入-输出时钟和地址输入(数据 输入)),通过串行三态输出与主机处理器或外围设备的串口通信。该设备允许从主机高速传输数据。除了高速转换器和多用途控制能 力,该设备还有一个芯片上的14通道多路复用器,可以选择11个输入中的任意一个或3个内部自检电压中的任意一个。这个功能是自动 的。在转换结束时,转换结束(EOC)输出变高,表示转换已经完成。TLC2543集成在器件中的转换器具有不同的高阻抗参考输入,便于 比值转换、缩放和模拟电路与逻辑和电源噪声隔离。开关电容设计允许在整个工作温度范围内的低误差转换。订货信息工作原理首先, 芯片选择(CS)高,I/O时钟和数据输入被禁用,TLC2543数据输出处于高阻抗状态。CS低电平通过启用I/O时钟和数据输入开始转换序 列,并从高阻抗状态中删除数据。输入数据为8位数据流,包括4位模拟信道地址(D7−D4)、2位数据纵向选择(D3−D2)、输出MSB或LSB 第一个位(D1)和应用于数据输入的单极或双极输出选择位(D0)。TLC2543应用于I/O时钟终端的I/O时钟序列将此数据传输到输入数据寄 存器。在这个传输过程中,I/O时钟序列还将之前的转换结果从输出数据寄存器转移到数据输出。I/O时钟接收8、12或16个时钟周期长 的输入序列,这取决于输入数据寄存器中的数据长度选择。TLC2543模拟输入的采样从输入I/O时钟序列的第四个下降沿开始,并在I/O 时钟序列的最后一个下降沿之后进行。I/O时钟序列的最后一个下降沿也将EOC降低并开始转换。转换器的操作转换器的操作被组织成 两个不同的周期的序列:1)I/O周期和2)实际的转换周期。I/O周期I/O周期由外部提供的I/O时钟定义,持续8、12或16个时钟周期,取决于 所选输出数据的长度。在I/O周期中,同时执行以下两个操作。一个由地址和控制信息组成的8位数据流被提供给数据输入。这些数据被 转移到前八个I/O时钟上升边缘的设备中。在12或16个时钟的I/O传输过程中,第一个时钟后的数据输入将被忽略。数据输出(长度为 8、12或16位)是在数据输出时串行提供的。当CS值较低时,第一个输出数据位出现在EOC上升沿。当CS在两次转换之间被否定时,第 一个outputdata位出现在CS的下降边缘。该数据是前一个转换周期的结果,在第一个输出数据位之后,每个后续的位都被锁定在每个后 续I/O时钟的下降边缘。转换周期转换周期对用户是透明的,它由一个内部时钟同步toI/O时钟控制。在转换期间,该装置对模拟输入电 压进行逐次近似转换。EOC输出在转换周期开始时较低,在转换完成并锁定输出数据寄存器时较高。转换周期只有在I/Ocycle完成后才 开始,这样可以将外部数字噪声对转换精度的影响降到最低。

我的TLC2543学习笔记——基于msp430g2553单片机

我的TLC2543学习笔记——基于msp430g2553单⽚机还是贴不了图⽚我的TLC2543学习笔记Created on: 2012-9-8Author: zhang bin学习笔记for msp430g2553redesigned by zhang bin2012-09-08versions:12_09_01All Rights ReservedTLC2543具有4线制串⾏接⼝,分别为⽚选端(CS),串⾏时钟输⼊端(I/O CLOCK),串⾏数据输⼊端(DATA IN)和串⾏数据输出端(DATA OUT)(转换结束脚EOC可以不接)。

它可以直接与SPI器件进⾏连接,不需要其他外部逻辑。

同时,它还在⾼达4MHz的串⾏速率下与主机进⾏通信。

TLC2543的特点及引脚TLC2543是TI的12 bit串⾏A/D转换器,11个模拟输⼊通道。

使⽤开关电容逐次逼近技术完成,A/D转换过程.由于是串⾏输⼊结构,能够MCU的I/O资源.其特点有:1)12 bit分辨率A/D转换器;2)在⼯作温度范围内10us转换时间;3)11个模拟输⼊通道;4)3路内置⾃测试⽅式;5)采样率为66 kb/s;6)线性误差+1LSB(max);7)有转换结束(EOC)输出;8)具有单、双极性输出;9)可编程的MSB或LSB前导;10)可编程的输出数据长度.��� 12-Bit-Resolution A/D Converter��� 10-µs Conversion Time Over OperatingTemperature��� 11 Analog Input Channels��� 3 Built-In Self-Test Modes��� Inherent Sample-and-Hold Function��� Linearity Error . . . ±1 LSB Max��� On-Chip System Clock��� End-of-Conversion Output��� Unipolar or Bipolar Output Operation(Signed Binary With Respect to 1/2 theApplied Voltage Reference)��� Programmable MSB or LSB First��� Programmable Power Down��� Programmable Output Data Length��� CMOS Technology��� Application Report Available我⽤的tlc2543是直插的,引脚图如下:各引脚的详细说明如下:引脚号名称I/O说明1~9,11,12AIN0~AIN10I模拟量输⼊端。

TLC2543及其接口电路

TLC2543在仪器仪表中的应用摘要介绍TI公司的TLC2543的特性,与51系列单片机的接口以及在仪器仪表中的应用。

关键词串行A/D应用1引言TLC2543是TI公司的12位串行模数转换器,使用开关电容逐次逼近技术完成A/D转换过程。

由于是串行输入结构,能够节省51系列单片机I/O资源;且价格适中,分辨率较高,因此在仪器仪表中有较为广泛的应用。

2TLC2543的特点(1)12位分辩率A/D转换器;(2)在工作温度范围内10μs转换时间;(3)11个模拟输入通道;(4)3路内置自测试方式;(5)采样率为66kbps;(6)线性误差±1LSBmax;(7)有转换结束输出EOC;(8)具有单、双极性输出;(9)可编程的MSB或LSB前导;(10)可编程输出数据长度。

3TLC2543的引脚排列及说明TLC2543有两种封装形式:DB、DW或N封装以及FN封装,这两种封装的引脚排列如图1,引脚说明见表1。

图1TLC2543的封装表1TLC2543引脚说明4接口时序可以用四种传输方法使TLC2543得到全12位分辩率,每次转换和数据传递可以使用12或16个时钟周期。

一个片选()脉冲要插到每次转换的开始处,或是在转换时序的开始处变化一次后保持为低,直到时序结束。

图2显示每次转换和数据传递使用16个时钟周期和在每次传递周期之间插入的时序,图3显示每次转换和数据传递使用16个时钟周期,仅在每次转换序列开始处插入一次时序。

图216时钟传送时序图(使用,MSB在前)图316时钟传送时序图(不使用,MSB在前)5TLC2543在智能仪器仪表中的应用TLC2543是12位分辩率,与MAX186在功能上基本相同,但价格比MAX186低得多,因此TLC2543在便携式数据记录仪、医用仪器、电力检测仪表中具有广泛的应用。

下面主要讲述TLC2543在电力监控显示屏中的应用。

在电厂和变电站中,电网中的电压和电流由于多种原因常常处于波动状态,为了给工作人员提供有效数据,并在超值范围内采取有效措施,监测电网中电压和电流值是非常必要的。

TLC2543中文数据手册

TLC2543使用手册一、简要说明:TLC2543是一款8位、10位、12位为一体的可选输出位数的11通道串行转换芯片。

每一路转换时间为10us。

外部输入信号为:DATA input ;_CS;AD_IO_CLK;Analog input;四种信号;输出为:EOC转换结束信号,DATA output信号。

工作原理为:_CS由高变为低时候,允许DATA input;AD_IO_CLK;Analog input信号输入,DATA out 信号输出;由低到高禁止DATA input;AD_IO_CLK;信号输入。

当忽略ADC转换启动的CS时候,数据的输出是在CS的下降沿,既是将片选的时候,而考虑到CS时候,第一个输出数据发生在EOC变为高的时候的上升沿。

注意:初始化时候,必须将CS由高拉低才能进行数据输出或者是数据输入。

也就是说,当一次转换完成后,进行下一次或者是下一个通道的转换,需要将CS由低拉高,为下一次转换做好准备,当进行下一个转换时候,进行CS 拉低,DATA input输入或者DATA out输出(忽略CS转换作用时候)。

信号解释:DATA input:4位串行地址输入,用来选择模拟输入通道功能或者测试引脚;高位在前,在每一个AD_IO_CLK的上升沿输入ADC的寄存器。

由八位组成:前四位:D7:D4用作选择模拟输入通道,D3:D2用作选择数据长度,D1是选择输出高低位顺序的,D0选择是选择输出极性(单双极性)。

DA TA INPUT的表含义DATA OUT:当_CS为高时DATA out输出为高阻抗,当CS有效时,驱动转换结果,并在AD_IO_CLK的下降沿按位顺序输出。

EOC:ADC的EOC在DATA input输入的最后一个AD_IO_CLK时,由高变为低,并保持到转换结束和数据准备输出结束时候变为高。

AD_IO_CLK:输入和输出时钟,主要完成以下功能:A、在IO_CLK的前八个时钟的上升沿将DATA input的八位数据输入数据寄存器中。

12位TLC2543模数转换总结

Lcd_wcd(1,0x2e);

Lcd_wcd(1,0x30+shi);

Lcd_wcd(1,0x30+ge);

Lcd_wcd(1,0x30+xiao);

/*for(i=0;i<SUM;i++)

{

temp1+=redad(0x01);//选择通道1,并读取AD转换的数

GND

地。GND是内部电路的地回路端。除另有说明外,所有电压测量都相对GND而言

18

I/O CLOCK

I

输入/输出时钟端。I/OCLOCK接收串行输入信号并完成以下四个功能:(1)在I/O CLOCK的前8个上升沿,8位输入数据存入输入数据寄存器。(2)在I/OCLOCK的第4个下降沿,被选通的模拟输入电压开始向电容器充电,直到I/OCLOCK的最后一个下降沿为止。(3)将前一次转换数据的其余11位输出到DATA OUT端,在I/OCLOCK的下降沿时数据开始变化。(4)I/OCLOCK的最后一个下降沿,将转换的控制信号传送到内部状态控制位

//uchar code dis1[]={"采集电压:000 v"};

/*************延时**************/

void delay(uint z)

{//一毫秒

uint y;

for(;z>0;z--)

for(y=110;y>0;y--) ;

}

void delay_us(uchar n)//微秒

shi=x/1000%10;

ge=x/100%10;

xiao=x/10%10;

}

/****************主函数****************/

TLC2543资料c语言

2.2TLC2543的内部寄存器

从编程角度看,TLC2543内部寄存器有输入数据寄存器与输出数据寄存器。输入数据寄存器存放从DATA INPUT端移入的控制字。输出数据寄存器存放转换好的数据,以供从DATA OUT端移出。

(4)控制字输入引脚

DATA TNPUT,17脚:控制字输入端,选择通道及输出数据格式的控制字由此输入。

(5)转换数据输出引脚

DATA OUT,16脚:A/D转换结果输出的3态串行输出端。

2TLC2543的编程要点

2.1控制字的格式

控制字为从DATA INPUT端串行输入TLC2543芯片内部的8位数据,它告诉TLC2543要转换的模拟量通道、转换后的输出数据长度、输出数据的格式。其中高4位(D7~D4)决定通道号,对于0通道至10通道,该4位分别为0000、0001、…、1010,该4位为其它数字时的功能,用于检测校正,本文不作具体介绍。低4位决定输出数据长度及格式,其中D3、D2决定输出数据长度,TLC2543的输出数据长度有8位、12位、16位,但由于TLC2543为12位A/D转换芯片,经过分析可以看出,8位、16位输出对TLC2543的应用意义不大,宜定在12位输出,D3、D2两位为00即可。D1决定输出数据是高位先送出,还是低位先送出,若为高位先送出,该位为0,反之为1。D0决定输出数据是单极性(二进制)还是双极性(2的补码),若为单极性,该位为0,反之为1。

关键词:A/D转换;TLC2543芯片;51系列单片机;接口技术

中图法分类号:TP334.7文献识别码:B

TLC2543AD采集

主函数#include<reg52.h>#include<lcd1602.h>#define uchar unsigned char#define uint unsigned intsbit clk=P1^4;sbit cs=P1^5;sbit din=P1^6;sbit dout=P1^7;sbit bit7=B^7; // 数据的最高位uchar conword;//控制字的高四位决定通道口bit cy;void write_sfm(uchar add,uint date){uint qian,bai,shi,ge;ge=date%10;shi=date%100/10;bai=date%1000/100;qian=date/1000;write_com(0x80+add);write_data(0x30+qian);write_com(0x80+0x08);write_data(0x2e);write_data(0x30+bai);write_data(0x30+shi);write_data(0x30+ge);}uint readad(uchar conword){char i;uint advalue=0;uchar value=0;conword=conword<<4; // 控制字高四位与低四位互换变成了高四位就是选择的通道口clk=0;cs=1; //cs为高,clk din 被禁止dout成高阻态cs=0; //cs为低clk din使能dout脱离高阻状态B=conword; //控制字for(i=8;i>0;i--){cy=dout; //dout 的高位传给cydin=bit7;//控制字高位先送入clk=1; //控制字在时钟信号的上升沿送入B=B<<1; //控制字的次高位移入高位clk=0;value=value<<1;if(cy==1) value++;//value是dout的高八位}advalue=value;advalue=advalue<<4; //高四位与低四位互换得出输出值value=0x00;for(i=4;i>0;i--) //dout 高四位的值赋给value{cy=dout;value=value<<1;if(cy==1){value++;}clk=1;clk=0;}advalue=advalue+value;cs=1;return advalue; // TLC 转换出的advalue=U(显示的电压值)*4096/5 ;}main(){uint ad;init();while(1){ad=readad(0x00);ad=ad*0.00122*1000;// 将ad转换为与输入的电压值相等ad*5/4096 在扩大1000write_sfm(7,ad);}}显示函数#include<lcd1602.h>#include<reg52.h>sbit lcdrs=P3^4;sbit lcden=P3^5;sbit rd=P3^7;void delay(uint z){uint x,y;for(x=z;x>0;x--)for(y=110;y>0;y--); }void write_com(uchar com) {lcdrs=0;lcden=0;P0=com;delay(5);lcden=1;delay(5);lcden=0;}void write_data(uchar date) {lcdrs=1;lcden=0;P0=date;delay(5);lcden=1;delay(5);lcden=0;}void init(){rd=0;lcden=0;write_com(0x38);write_com(0x0c);write_com(0x06);write_com(0x01);write_com(0x80);}仿真。

TLC2543中文资料

串行A D转换器T L C2543中文资料T L C2543是T I公司的12位串行模数转换器,使用开关电容逐次逼近技术完成A/D转换过程。

由于是串行输入结构,能够节省51系列单片机I/O资源;且价格适中,分辨率较高,因此在仪器仪表中有较为广泛的应用。

2T L C2543的特点(1)12位分辩率A/D转换器;(2)在工作温度范围内10μs转换时间;(3)11个模拟输入通道;(4)3路内置自测试方式;(5)采样率为66k b p s;(6)线性误差±1L S B m a x;(7)有转换结束输出E O C;(8)具有单、双极性输出;(9)可编程的M S B或L S B前导;(10)可编程输出数据长度。

3T L C2543的引脚排列及说明T L C2543有两种封装形式:D B、D W或N封装以及F N封装,这两种封装的引脚排列如图1,引脚说明见表1。

图1T L C2543的封装4接口时序可以用四种传输方法使T L C2543得到全12位分辩率,每次转换和数据传递可以使用12或16个时钟周期。

一个片选()脉冲要插到每次转换的开始处,或是在转换时序的开始处变化一次后保持为低,直到时序结束。

图2显示每次转换和数据传递使用16个时钟周期和在每次传递周期之间插入的时序,图3显示每次转换和数据传递使用16个时钟周期,仅在每次转换序列开始处插入一次时序。

引脚号名称I/O说明1~9,11,12AIN0~AIN10I模拟量输入端。

11路输入信号由内部多路器选通。

对于4.1MHz的I/OCLOCK,驱动源阻抗必须小于或等于50Ω,而且用60pF电容来限制模拟输入电压的斜率15I片选端。

在端由高变低时,内部计数器复位。

由低变高时,在设定时间内禁止DATAINPUT和I/O CLOCK17DATAINPUT I串行数据输入端。

由4位的串行地址输入来选择模拟量输入通道16DATA OUT O A/D转换结果的三态串行输出端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TLC2543使用手册

一、简要说明:

TLC2543是一款8位、10位、12位为一体的可选输出位数的11通道串行转换芯片。

每一路转换时间为10us。

外部输入信号为:DATA input ;_CS;AD_IO_CLK;Analog input;四种信号;

输出为:EOC转换结束信号,DATA output信号。

工作原理为:

_CS由高变为低时候,允许DATA input;AD_IO_CLK;Analog input信号输入,DATA out 信号输出;由低到高禁止DATA input;AD_IO_CLK;信号输入。

当忽略ADC转换启动的CS 时候,数据的输出是在CS的下降沿,既是将片选的时候,而考虑到CS时候,第一个输出数据发生在EOC变为高的时候的上升沿。

注意:初始化时候,必须将CS由高拉低才能进行数据输出或者是数据输入。

也就是说,当一次转换完成后,进行下一次或者是下一个通道的转换,需要将CS由低拉高,为下一次转换做好准备,当进行下一个转换时候,进行CS拉低,DATA input输入或者DATA out输出(忽略CS转换作用时候)。

信号解释:

DATA input:4位串行地址输入,用来选择模拟输入通道功能或者测试引脚;高位在前,在每一个AD_IO_CLK的上升沿输入ADC的寄存器。

由八位组成:前四位:D7:D4用作选择模拟输入通道,D3:D2用作选择数据长度,D1是选择输出高低位顺序的,D0选择是选择输出极性(单双极性)。

DA TA INPUT的表含义

DATA OUT:当_CS为高时DATA out输出为高阻抗,当CS有效时,驱动转换结果,并在AD_IO_CLK的下降沿按位顺序输出。

EOC:ADC的EOC在DATA input输入的最后一个AD_IO_CLK时,由高变为低,并保持到转换结束和数据准备输出结束时候变为高。

AD_IO_CLK:输入和输出时钟,主要完成以下功能:

A、在IO_CLK的前八个时钟的上升沿将DATA input的八位数据输入数据寄存器中。

B、在IO_CLK的第四个时钟下降沿到来时候,已经完成了输入通道选择,并开始给输

入采样电容进行充电,直到第八个下降沿到来。

C、将前11位转换结果进行移位输出。

DATA out

D、在最后一个时钟下降沿来临时候,将转换控制权力交给内部状态控制器。

二、供电等说明

供电电压:VCC4.5V-5.5V

参考电压:VREF+最大到VCC,VREF-接到地。

AD_IO_CLK最大频率:4.1MHz

转换时间:10us

整体时间(地址、采样和转换):10us+TOTAL IO CLK+IOEOC=12.2us+(4-12)IO_cycle CS到DA TA out输出时间:1.3us

IO最后一个下降沿到开始转换既是EOC变为低的时间为:2.2us

转换结束到数据输出延迟时间为:100ns

数据输出到IO_CLK下降沿的延迟时间:150ns 既是最大允许的时钟时间。

如果低于这个时间就不能建立数据输出了。

如图可以看出,整体时间(地址、采样和转换):10us+TOTAL IO CLK+IOEOC=12.2us+(4-12)IO_cycle。