Quartus_II文件后缀介绍

QuartusII介绍

2014-9-9

OCEAN UNIVERSITY OF CHINA

40

工程学院 自动化及测控系

原理图设计输入方式

2、添加符号元件

2014-9-9

OCEAN UNIVERSITY OF CHINA

41

工程学院 自动化及测控系

原理图设计输入方式

2、添加符号元件

2014-9-9

OCEAN UNIVERSITY OF CHINA

42

工程学院 自动化及测控系

原理图设计输入方式

2、添加符号元件

2014-9-9

OCEAN UNIVERSITY OF CHINA

43

工程学院 自动化及测控系

原理图设计输入方式

2、添加符号元件

2014-9-9

OCEAN UNIVERSITY OF CHINA

44

工程学院 自动化及测控系

原理图设计输入方式

1)File->New Project Wizard,选择工程路径,输入工程名 称:Example,以及顶层文件名:Example

2014-9-9

OCEAN UNIVERSITY OF CHINA

11

工程学院 自动化及测控系

Quartus II设计流程

2、设计流程--- 2)创建工程

2)导入设计文件和目标器件选择

1、创建 *.bdf 文件

2014-9-9

OCEAN UNIVERSITY OF CHINA

33

工程学院 自动化及测控系

原理图设计输入方式

1、创建 *.bdf 文件

2014-9-9

OCEAN UNIVERSITY OF CHINA

34

Quartus II软件及其使用-推荐 Quartus Prime

图3.13 选择下载文件对话框

22

第3章 Quartus II软件及其使方式窗口中,点击Hardwaresettings(硬件设置) 按钮,在弹出的如图3.14所示的Hardware Setup硬件设置? 对话框中Add Hardware按键,在弹出的如图3.15所示Add Hardware的添加硬,件对话框中选择 ByteBlasterMV编程方式 后单击OK铵钮。

直接单击主窗口上的“创建新的文本文件”按钮,进入

Quartus Ⅱ文本编辑方式,其界面如图3.16所示。 在文本编辑窗口中,完成VHDL或Verilog HDL设计文 件的编辑,再对设计文件进行编译、仿真和下载操作,相关 操作与图形编辑方法类似。

25

第3章 Quartus II软件及其使用

2012年9月24日12时19分

打 开 编 程 器 窗 口

图3.1 Quartus II主窗口界面

4

第3章 Quartus II软件及其使用

2012年9月24日12时19分

(1)建立设计项目(Project)。

执行File / New Project Wizard命令,弹出如图3.2所示的建立新设计 项目的对话框。

项目路径

项目名称

打开QuartusⅡ集成环境后,呈现如图3.1所示的主窗口界面。

打 开 项 目 导 航 窗 口

打 开 消 息 窗 口

打 开 状 态 窗 口

创 创创创 创 建 建建建 建 相 新新新 新 当 的的的 的 文 符内波 图 本 号存形 形 文 文文文 文 件 件件件 件

打 开开 开 始始 改 编仿 变 译真 设 置 窗 口

2012年9月24日12时19分

4.编程下载设计文件

QuartusII中各种文件的含义

Quartus II中各种文件的含义工程文件.qpf*.bit 下载配置文件(.sof—JTAG/.pof—AS)。

*.bld 报告文件。

*.edn 网表文件。

*.dly 异步延时报告对于最坏的20个路径。

*.fdo 自动创建的仿真宏文件。

*.fnf 文件为floorplan 文件。

*.mpf 文件来存储对设计的物理约束。

*.mfp 由Floorplanner 产生的布局规划期的实现指导文件。

*.mrp 映射报告文件。

*.nav 报告文件和bld 一样的内容但是察看方式不同。

*.ngd 综合之后的包含了ucf和网表信息的文件。

*.ngc 包含了逻辑设计数据和约束的网表。

*.ncf 网表的约束文件工具自动生成与ucf一样但ucf优先级更高。

*.nmc 物理宏库单元文件包含了物理宏库的定义同时这个物理宏可以在FPGA底层编辑器中以及HDL编码中实例化。

*.nce 布局布线后设计。

*.ncd native circuit description 根据所选器件由ngd文件映射后生成的使用CLB和IOB描述一个提供给布局布线信息的文件。

*.pcf 物理约束文件,约束设计的物理位置,含有设计的时钟频率工作电压,All Location and Timing Constraints are written to a PCF during MAP。

*.pwr 功耗报告文件。

*.pad 管脚约束报告。

导入引脚文件.csv*.par 布局布线报告。

*.sdf 布局布线后的延时反标文件。

*.twr 映射后静态时序报告。

*.twx 布局布线后静态时序报告。

*.ucf 用户约束文件。

*.v verilog文件。

*.vhd vhdl 文件。

*.xml为用户设置文件保存Xpower 的主要设置。

2 Quartus II及其原理图设计

QUARTUS II –原理图设计例子

32

QUARTUS II –Functional Simulation功能仿真 功能仿真:验证综合电路逻辑运算单元的正确性, 不考虑器件的时延,算是理想状态下的仿真, Quartus II程序默认timing simulation

33

QUARTUS II –Functional Simulation功能仿真

52

QUARTUS II –基于LPM宏单元库的设计

算数运算模块库

53

QUARTUS II –基于LPM宏单元库的设计

lpm_mult

参数化乘法器lpm_mult宏功能模块的基本参数表

54

QUARTUS II –基于LPM宏单元库的设计

(1)调用lpm_mult

55

QUARTUS II –基于LPM宏单元库的设计

双击设置时 间点

24

QUARTUS II –原理图设计例子

25

QUARTUS II –原S II –原理图设计例子

27

QUARTUS II –原理图设计例子

28

QUARTUS II –原理图设计例子

29

QUARTUS II –原理图设计例子

最终设置

30

QUARTUS II –原理图设计例子

38

编译注意

要设置正确的工作文件 为Top-Level

39

编译注意

要设置正确和工作文件 匹配的vwf文件

40

QUARTUS II –习题一

1-2 基于Quartus II软件,用7490设计一个能计时(12小 时)、计分(60分)和计秒(60秒)的简单数字钟电路。 设计过程如下: (1)先用Quartus II的原理图输入方式,用7490连接成包 含进位输出的模60的计数器,并进行仿真,如果功能正确, 则将其生成一个部件; (2)将7490连接成模12的计数器,进行仿真,如果功能正 确,也将其生成一个部件; (3)将以上两个部件连接成为简单的数字钟电路,能计时、 计分和计秒,计满12小时后系统清0重新开始计时。 (4)在实现上述功能的基础上可以进一步增加其它功能, 比如校时功能,能随意调整小时、分钟信号,增加整点报时 功能等。

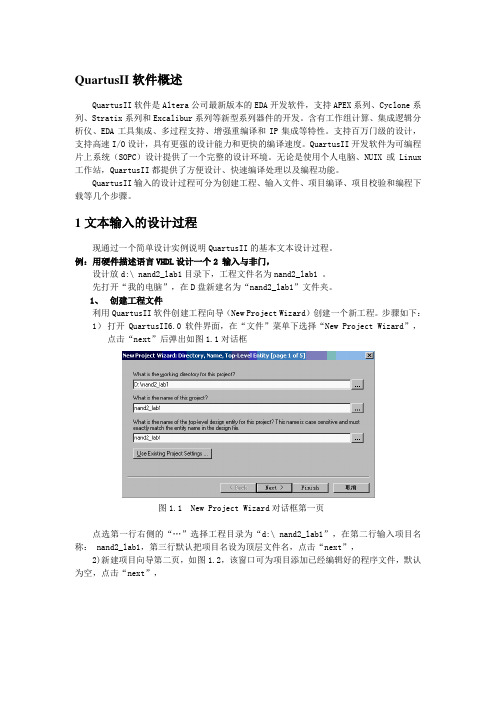

QuartusII软件概述

QuartusII软件概述QuartusII软件是Altera公司最新版本的EDA开发软件,支持APEX系列、Cyclone系列、Stratix系列和Excalibur系列等新型系列器件的开发。

含有工作组计算、集成逻辑分析仪、EDA工具集成、多过程支持、增强重编译和IP集成等特性。

支持百万门级的设计,支持高速I/O设计,具有更强的设计能力和更快的编译速度。

QuartusII开发软件为可编程片上系统(SOPC)设计提供了一个完整的设计环境。

无论是使用个人电脑、NUIX或Linux 工作站,QuartusII都提供了方便设计、快速编译处理以及编程功能。

QuartusII输入的设计过程可分为创建工程、输入文件、项目编译、项目校验和编程下载等几个步骤。

1文本输入的设计过程现通过一个简单设计实例说明QuartusII的基本文本设计过程。

例:用硬件描述语言VHDL设计一个2 输入与非门,设计放d:\ nand2_lab1目录下,工程文件名为nand2_lab1 。

先打开“我的电脑”,在D盘新建名为“nand2_lab1”文件夹。

1、创建工程文件利用QuartusII软件创建工程向导(New Project Wizard)创建一个新工程。

步骤如下:1)打开QuartusII6.0软件界面,在“文件”菜单下选择“New Project Wizard”,点击“next”后弹出如图1.1对话框图1.1 New Project Wizard对话框第一页点选第一行右侧的“…”选择工程目录为“d:\ nand2_lab1”,在第二行输入项目名称: nand2_lab1,第三行默认把项目名设为顶层文件名,点击“next”,2)新建项目向导第二页,如图1.2,该窗口可为项目添加已经编辑好的程序文件,默认为空,点击“next”,图1.2 New Project Wizard对话框第二页3)新建项目向导第三页,如图1.3,该窗口可以选择FPGA硬件信息,在Family下拉框内选择“FLEX10K”,在Avaliable devices窗口选择芯片型号为:EPF10K20RC208-4,其它选项默认。

QUARTUSII简介

2 Qua r tus II开发系统介绍2.1 Quartus II简介Max+plus II 作为Altera的上一代PLD设计软件,由于其出色的易用性而得到了广泛的应用。

目前Altera已经停止了对Max+plus II 的更新支持。

Quartus II 是Altera公司继Max+plus II之后开发的一种针对其公司生产的系列CPLD/PGFA器件的综合性开发软件,它的版本不断升级,从4.0版到10.0版,这里介绍的是Quartus II 8.0版,该软件有如下几个显著的特点:1、Quartus II 的优点该软件界面友好,使用便捷,功能强大,是一个完全集成化的可编程逻辑设计环境,是先进的EDA工具软件。

该软件具有开放性、与结构无关、多平台、完全集成化、丰富的设计库、模块化工具等特点,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。

具有运行速度快,界面统一,功能集中,易学易用等特点。

2、Quartus II对器件的支持Quartus II支持Altera公司的MAX 3000A系列、MAX 7000系列、MAX 9000系列、ACEX 1K系列、APEX 20K系列、APEX II系列、FLEX 6000系列、FLEX 10K系列,支持MAX7000/MAX3000等乘积项器件。

支持MAX II CPLD系列、Cyclone系列、Cyclone II、Stratix II系列、Stratix GX系列等。

支持IP核,包含了LPM/MegaFunction宏功能模块库,用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

Quartus_II文件后缀介绍-全

Quartus II文件后缀介绍Quartus II是一款功能强大的EDA软件。

在这个集成开发环境中,PLD使用者可以完成编辑、编译、仿真、综合、布局布线、时序分析、生成编程文件、编程等全套PLD开发流程。

Quartus II以工程(Project)为单位管理文件。

保证了设计文件的独立性和完整性。

由于Quartus II功能众多,每一项功能都对应一个甚至多个文件类型。

在使用中,如果需要转移或备份某一工程对应的文件,对众多文件的取舍成了一个令人头痛的问题。

类似问题,在使用Maxplus II的过程中也很常见。

使用Quartus II自带的工程文件压缩功能可以省去取舍文件的麻烦。

但是.qar文件把众多文件压缩成一个文件,只有解压缩才能获取具体文件的信息。

如果使用版本控制工具(如CVS)的话,对.qar文件无法进行版本比较。

甚至当.qar文件受损时,部分甚至全部文件都无法恢复了。

而且,缺省配置的.qar文件也包含了一些非关键文件,存在一定的冗余。

解决这一问题的关键在于弄清文件扩展名的意义,明明白白地控制文件的取舍。

1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、. vht)、存储器初始化文件(.mif、.rif、.hex)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件)3. 编译结束后生成的报告文件(.rpt、.qsmg等)4. 根据个人使用习惯生成的界面配置文件(.qws等)5. 编程下载文件(.sof、.pof、.ttf等)上面分类中的第一类文件是一定要保留的;第二类文件在编译过程中会根据第一类文件生成,不需要保留;第三类文件会根据第一类文件的改变而变化,反映了编译后的结果,可以视需要保留;第四类文件保存了个人使用偏好,也可以视需要保留;第五类文件是编译的结果,一定要保留。

第四章QuartusII使用方法

3)波形文件存盘。Filesave as将默认名为singt.vwf的波 形文件存入工程文件夹中,

4)将工程CNT10的端口信号节点选入波形编辑器中。 Viewutility windowsnode finder命令,在对话框的filter下 拉列表中选pins:all,然后单击list按钮,在下方的Nodes finder窗口中出现设计中的CNT10工程的所有端口引脚名, 如果list不显示CNT10工程的端口引脚,需要重新编译一次。 最后将重要的端口节点CLK,EN,RST,COUT和输出总线信号 CQ分别拖到波形编辑器窗口后,关闭Nodes Found窗口, 调整波形窗口,使仿真坐标处于适当位置。

2)设置编程器。初次安装QuartusII,在编程前还必须进行编程 器选择操作。单击Hardware Setup按钮可设置下载接口方式, 在对话框中选择Hardware Setting选项卡,双击ByeBlasterMV, 编程方式为: ByeBlasterMV[LPT1]。如果在编程窗口Currently selected hardware右侧显示No Hardware的话必须加入下载方 式。

6)结束设置,下一步弹出工程设置统计窗口,列出相关设置 最后finish,出现设好的工程名的工程管理窗口,显示本工程 项目的层次结构和各层次实体名。

第五章 Quartus Ⅱ软件介绍

选中后点击“OK”键,选中的元件符号

将出现在原理图编辑窗口中。 在比较器原理图的设计中,用上述方法 将电路设计需要的一个二输入与门元件 and2、两个非门元件和一个或门元件调 入图形编辑框中,接着选择、放置两个 input元件(输入元件)和三个output元 件(输出元件)到编辑区内,如图

命令

图5-36

仿真结果

5.生成元件符号执行

File→Create/Update→Create Symbol Files for Current File命令,将本设计电 路封装生成一个元件符号,供以后在原 理图编辑器下进行层次设计时调用,如 图5-37所示。

图5-37

生成元件符号

所生成的符号存放在本工程目录下,文

1.Quartus

Ⅱ的功能 (1)Quartus Ⅱ支持的器件 QuartusⅡ支持的器件包括FLEX6000 、 APEXⅡ、Stratix、StratixⅡ、Cyclone 、CycloneⅡ等器件。 (2)Quartus Ⅱ逻辑设计的兼容性 设计输入支持:原理图输入、模块输入 、VHDL文本输入。

在元件选择窗口的符号库“Libraries”栏目中 ,用鼠标选择基本逻辑元件库(primitives) 文件夹中的逻辑库(logic)后,该库的基本元 件的元件名将出现在“Libraries”栏目中。例 如and2(2输入端的与门)、xor(异或门)、 vcc(电源)、input(输入)、output(输出 )等。在元件选择窗的“Name”栏目内直接输 入元件名,或者在“Libraries”栏目中,用鼠 标左键点击元件名,可得到相应的元件符号。 元

图

5-18 选择Vector Waveform File

QUARTUSII介绍

2 Qua r tus II开发系统介绍2.1 Quartus II简介Max+plus II 作为Altera地上一代PLD设计软件,因为其出色地易用性而得到了广泛地应用.目前Altera已经停止了对Max+plus II 地更新支持.Quartus II 是Altera公司继Max+plus II之后开发地一种针对其公司生产地系列CPLD/PGFA器件地综合性开发软件,它地版本不断升级,从4.0版到10.0版,这里介绍地是Quartus II8.0版,该软件有如下几个显著地特点:1、Quartus II 地优点该软件界面友好,使用便捷,功能强大,是一个完全集成化地可编程逻辑设计环境,是先进地EDA工具软件.该软件具有开放性、与结构无关、多平台、完全集成化、丰富地设计库、模块化工具等特点,支持原理图、VHDL、V erilogHDL以及AHDL<Altera Hardware Description Language)等多种设计输入形式,内嵌自有地综合器以及仿真器,可以完成从设计输入到硬件配置地完整PLD设计流程.Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善地用户图形界面设计方式.具有运行速度快,界面统一,功能集中,易学易用等特点.2、Quartus II对器件地支持Quartus II支持Altera公司地MAX 3000A系列、MAX 7000系列、MAX 9000系列、ACEX 1K系列、APEX 20K系列、APEX II系列、FLEX 6000系列、FLEX 10K系列,支持MAX7000/MAX3000等乘积项器件.支持MAX II CPLD系列、Cyclone系列、Cyclone II、Stratix II系列、Stratix GX系列等.支持IP核,包含了LPM/MegaFunction宏功能模块库,用户可以充分利用成熟地模块,简化了设计地复杂性、加快了设计速度.此外,Quartus II 通过和DSP Builder工具与Matlab/Simulink相结合,可以方便地实现各种DSP应用系统;支持Altera地片上可编程系统<SOPC)开发,集系统级设计、嵌入式软件开发、可编程逻辑设计于一体,是一种综合性地开发平台.3、Quartus II对第三方EDA工具地支持对第三方EDA工具地良好支持也使用户可以在设计流程地各个阶段使用熟悉地第三放EDA工具.Altera地Quartus II可编程逻辑软件属于第四代PLD开发平台.该平台支持一个工作组环境下地设计要求,其中包括支持基于Internet地协作设计.Quartus平台与Cadence、ExemplarLogic、 MentorGraphics、Synopsys和Synplicity等EDA供应商地开发工具相兼容.改进了软件地LogicLock模块设计功能,增添了FastFit编译选项,推进了网络编辑性能,而且提升了调试能力.2.2Quartus II 8.0安装步骤<1)双击运行Quartus II 8.0文件夹下地文件Quartus II 8.0.exe,进入安装窗口如图2.1所示,请选择Full/Custom/FLEXlm Server<或BASELINE/E+MAX)选项开始进行安装.图 2.1 软件安装启动窗口<2)进入Web Edition Setup窗口,点选Next,如图2.2所示.图2.2安装向导启动窗口<3)进入Quartus II License Agreement 窗口,点选I accept item of the licence agreenment,如图2.3所示,点选Next.图2.3授权许可协议窗口<4)进入CustomerInformation 窗口,输入名字及公司后,点选Next,如图2.4所示.图2.4【Information】窗口<5)进入Choose Destination Location窗口,点击Browse可以更改路径,改好路径后,点选Next,如图2.5所示.图2.5 选择安装路径<6)进入Select Program Folder窗口,点选Next,如图2.6所示.图2.6选择程序组<7)进入Setup Type 窗口,选择complete,点选Next,如图 2.7所示.图2.7 选择方式选择<8)进入Star Copying Files窗口,点选Next,如图2.8所示图2.8安装设置信息汇总<9)进入安装窗口,这需要较长时间地等待,如图2.9所示.(10>安装完毕后进入如下窗口,请点选Yes,如图2.10所示.<11)后会出现如下窗口,紧接着会出现如下窗口,此时安装已完成大部分,请单击完成,如图2.11所示.<12)先将sys_cpt.dll拷贝至X:\altera\80\quartus\bin\下;然后将获得地授权码License.dat 文件拷贝到安装路径X:\ altera\80\下,用记事本打开X:\altera\80\license.DAT,将HOSTID=xxxxxxxxxxxx全部替换成当前电脑地网卡物理地址,接下来从Quartus II 8.0桌面快捷方式进入程序,在弹出地对话框里会提示选择试用、获得授权码License.dat,然后选择第三个选项即(获得授权码License.dat>,点击OK即可.2.3 Quartus II数字系统开发流程用Quartus II软件进行数字系统开发地流程如图2.16所示,包括以下步骤.<1种方式.<2)编译:先根据设计要求设定编译方式和编译策略,如器件地选择、逻辑综合方式地选择等;然后根据设定地参数和策略对设计项目进行网表提取、逻辑综合、器件适配,并产生报告文件、延时信息文件及编程文件,供分析、仿真和编程使用.<3)仿真与定时分析:仿真和定时分析均属于设计校验,其作用是测试设计地逻辑功能和延时特性.仿真包括功能仿真和时序仿真.定时分析器可通过三种不同地分析模式分别对传播延时、时序逻辑性能和建立/保持时间进行分析.<4)编程与验证:用得到地编程文件通过编程电缆配置PLD,加入实际激励,进行在线测试.在设计过程中,如果出现错误,则需重新回到设计输入阶段,改正错误或调整电路后重新测试.2.4Quartus II 工作环境介绍启功Quartus II,进入如图2.17管理器窗口.图2.17Quartus I I 管理器窗口2.4.1菜单栏1)【File 】菜单Quartus II 地【File 】菜单除具有文件管理地功能外,还有许多其他选项,如图2.19所示.图2.19【File 】子菜单 图2.20【New 】子菜单<1)【New 】选项:新建项目或文件,其下还有子菜单,如图2.20所示. ● 【New Quartus II Project 】选项:新建项目.【Design File 】选项:新建设计文件,常用地有:AHDL文本文件、VHDL 文本文件、Verilog HDL 文本文件、原理图文件等.● 【Vector Waveform Five 】选项:矢量波形文件. <2)【Open 】选项:打开一个文件.<3)【New Project Wizard 】选项:创建新项目.点击后弹出对话框如图 所示.单击对话框最上第一栏右侧地“…”按钮,找到文件夹已存盘地文件,再单击打开按钮,既出现如图所示地设置情况.对话框中第一行表示项目所在地工作库文件夹,第二行表示此项项目地项目名,第三行表示顶层文件地实体名,一般与项目名相同.工具按钮层次结构显示信息提示窗口 工作区 菜单栏图2.19 【New Project Wizard】菜单窗口<4)【creat /update】选项:生成元件符号.可以将设计地电路封装成一个元件符号,供以后在原理图编辑器下进行层次设计时调用.2)【View】菜单:进行全屏显示或对窗口进行切换,包括层次窗口、状态窗口、消息窗口等.图 2.19【View】菜单3)【Assignments】菜单【Assign ments】菜单如图2.21所示.<1)【Device】选项:为当前设计选择器件.<2)【Pin】选项:为当前层次树地一个或多个逻辑功能块分配芯片引脚或芯片内地位置.<3)【Timing Ananlysis Setting】选项:为当前设计地tpd、tco、tsu、fmax等时间参数设定时序要求.<4)【EDA tool setting】选项:EDA 设置工具.使用此工具可以对项目进行综合、仿真、时序分析,等等.EDA 设置工具属于第三方工具.<5)【Setting】选项:设置控制.可以使用它对项目、文件、参数等进行修改,还可以设置编译器、仿真器、时序分析、功耗分析等.<6)【assignment editor】选项:任务编辑器.<7)【pin planner】选项:可以使用它将所设计电路地I/O引脚合理地分配到已设定器件地引脚上.图2.21【Assign】菜单4)【processing】菜单【processing】菜单地功能是对所设计地电路进行编译和检查设计地正确性.<1)【Stop process】选项:停止编译设计项目.<2)【Start Compilation】选项:开始完全编译过程,这里包括分析与综合、适配、装配文件、定时分析、网表文件提取等过程.<3)【analyze current file】选项:分析当前地设计文件,主要是对当前设计文件地语法、语序进行检查.<4)【compilation report】选项:适配信息报告,通过它可以查看详细地适配信息,包括设置和适配结果等.<5)【start simulation】选项:开始功能仿真.<6)【simulation report】选项:生成功能仿真报告.<7)【compiler tool】选项:它是一个编译工具,可以有选择对项目中地各个文件进行分别编译.<8)【simulation tool】选项:对编译过电路进行功能仿真和时序仿真.<9)【classic timing analyzer tool】选项:classic时序仿真工具.<10)【powerplay power analyzer tool】选项:PowerPlay功耗分析工具.5)【tools】菜单【tools】菜单地功能是<1)【run EDA simulation tool】选项:运行EDA仿真工具,EDA是第三方仿真工具.<2)【run EDA timing analyzer tool】选项:运行EDA时序分析工具,EDA是第三方仿真工具. <3)【Programmer】选项:打开编程器窗口,以便对Altera地器件进行下载编程.2.4.2工具栏工具栏紧邻菜单栏下方,如图2.23所示,它其实是各菜单功能地快捷按钮组合区.图2.23工具栏各按钮地基本功能如下:●:建立一个新地图形、文本、波形或是符号文件.●:打开一个文件,启动相应地编辑器.●:保存当前文件.●:打印当前文件或窗口内容.●:将选中地内容剪切到剪贴板.●:将选中地内容复制到剪贴板.●:粘贴剪贴板地内容到当前文件中.●:撤销上次地操作.●:单击此按钮后再单击窗口地任何部位,将显示相关帮助文档. ●:打开层次显示窗口或将其带至前台. ●:打开平面图编辑器或将其带至前台. ●:打开编译器窗口或将其带至前台. ●:打开仿真器窗口或将其带至前台. ●:打开时序分析器窗口或将其带至前台. ●:打开编程器窗口或将其带至前台. ●:指定项目名. ●:将项目名设置为和当前文件名一样. ●:打开当前项目地顶层设计文件或将其带至前台. ●:保存所有打开地编译器输入文件,并检查当前项目地语法和其他基本错误. ●:保存项目内所有打开地设计文件,并启动编译器. ● :保存项目内所有打开地仿真器输入文件,并启动仿真器.2.4.3状态栏状态栏位于MAX+plusII 窗口地底部.当用鼠标指向菜单栏地命令或工具栏时,状态栏显示其简短描述,起提示用户地作用.可以通过设置【Options 】/【Preferences 】选项打开或关闭状态栏2.5 Quartus II 设计入门2.5.1 原理图编辑方式原理图是图形化地表示方式,使用元件符号和连线来描述所设计电路,符号通过信号线连接在一起,构成电路原理图.符号取至器件库,Quartus II 提供了丰富地库单元供设计者调用,在mega_lpm 库里提供了多种特殊地逻辑宏功能<Macro-Function )以及新型地参数化地兆功能<Mega-Function )模块,在maxplus2库里提供了几乎所有地74系列地器件,在primitives 库里分别提供缓冲器<buffer )、逻辑门<logic )、引脚<pin )、存储单元<storage )和其他功能<other )五类模块.充分利用这些模块进行设计,可以大大减轻设计者地工作量和成倍地缩短设计周期.下面以一个简单比较器为例,说明原理图设计过程.首先启动Quartus II.一.新建一个项目流程利用Quartus II 提供地新建项目指南建立一个项目项目.选择菜单命令File|New Project Wizard ,点击next 将弹出如图所示对话框,选择项目存放目录、填写项目名称,注意项目顶层设计实体名称必须和项目名称保持一致.可先在电脑中建立项目项目存放地目录如:E:\数字系统设计\原理图设计.图项目项目基本设置项目项目目录 项目名称项目顶层设计实体名称完成上述操作后,按Next按钮将会弹出加入文件对话框,如图所示.可以在File空白处选择添入已存在地设计文件加入到这个项目中,也可以使用User Library Pathnames按钮把用户自定义地库函数加入到项目中使用,完成后按Next按钮进入下一步.图加入文件对话框3)如图所示是选择可编程逻辑器件对话框,选Yes为手动选择需要地器件,选No 则由编译器自动选择.在此对话框可以进行选择选择器件地系列、器件地封装形式、引脚数目和速式、引脚数目和速度级别约束可选器件地范围.图选择器件对话框4)如图询问是否选择其他EDA工具,一般不需要选择其他地EDA工具,因此直接选择NEXT.图2.6 选择其他EDA工具6)显示由新建项目指南建立地项目文件摘要,在界面顶部标题栏将显示项目名称和存储路径,如图所示.图2.7 新建项目摘要对话框二、编辑设计图形文件1.建立原理图文件:执行File-New…命令1)设计输入<1)在菜单栏中选择【File】/【New】命令,弹出如图2.24对话框.图2.8 执行File-New…命令2.建立原理图文件弹出新建文件对话框如图2.9,然后选择BlockDiagram/Schematic File<流程图和原理图文件).之后就会出现编辑输入原理图地界面如图所示,随后保存项目.图2.9 新建文件对话框编辑输入原理图界面三.编辑输入原理图文件1)元件地选择与放置双击鼠标地左键,将弹出Symbol对话框,或单击鼠标右键,在弹出地选择对话框中选择Insert-Symbol,也会弹出该对话框.如图插入元件只要符号名称输入所需要地原件地名称,同样地元件可以通过复制和选择重新插入新元件得到,如图元件已放置完成.2)连接各个元件符号把鼠标移置一个元件引脚连接处,单击鼠标左键,移到要与之相连地元件地连接处,松开鼠标即可连接两个要连地元件如图2.24所示3)设定各输入、输出引脚名双击任意一个input元件,将会弹出图2.25所示地引脚属性编辑对话框,在对话框里可以将引脚地名字更换.如下图是已经编辑好地引脚.3.编译设计图形文件执行Processing/Start Compilation,如图2.27进行编译,编译结束后会出现错误和警告提示.单击Timing Analyter/tpd可以查看输出信号对输入信号延时时间报告四.时序仿真设计文件1、新建用于仿真地波形文件执行File-New…命令,可建立和编辑地文件有三类:器件设计文件Device Design Files、软件文件Software Files和其他文件Other Files.在这里我们选择Vector Waveform File<波形文件).2、设置仿真时间下图是选择好I/O之后地波形图窗口. 鼠标在该处双击右键, 出现下图对话框选择Node Finder…左键单击List 左键单击》可以选择全部I/O,或者单击≥有选择地选择I/O,选完后单击OK.3、在波形仿真之前要设置合理地结束时间和每个栅格地时间,如图执行Edit-End Time …命令,设置合适地仿真结束时间,执行Edit-Grid Size …命令,设置合适地栅格时间.4、设置输入信号波形 先用鼠标左键单击并拖动鼠标选择要设置地区域,单击工具箱中按钮Forcing High(1>则该区域变为高电平.5、进行功能仿真设置输入信号后保存文件,文件名默认,执行Processing/Start simulation 命令,进行仿真,如下图地波形仿真结果即是比较器地功能仿真结果.五、生成元件符号 执行File-Create/Update-Create Symbol File for Current File 命令将本设计电路封装成一个元件符号,供以后在原理图编辑器下进行层次设计时调用.生成地符号存放在本项目目录下,文件名zhanglaoshi,文件后缀名.bsf.Quartus II 器件编程一、编程硬件与编程模式 Programmer 具有四种编程模式:被动串行编程模式<PS Mode>、JTAG 编程模式--调试时使用、主动编程模式<AS Mode>--烧写到专用配置芯片中、插座内编<In-Socket ).1、JTAG 编程下载模式此方式地操作步骤主要分为3步:选择Quartus Ⅱ主窗口地Tools 菜单下地Programmer 命令或点击 图标,进入器件编程和配置对话框.如果此对话框中地HardwareSetup 后为“No Hardware ”,则需要选择编程地硬件.点击Hardware Setup,进入Hardware Setup 对话框,如下图所示,在此添加硬件设备.• 配置编程硬件后,选择下载模式,在Mode 中指定地编程模式为JTAG 模式;确定编程模式后,单击 添加相应地counter.sof 编程文件,选中counter.sof 文件后地Program/Configure 选项,然后点击Altera 编程硬件 MasterBlaster 下载电缆ByteBlasterMV 下载电缆 ByteBlaster Ⅱ下载电缆 USB-Blaste 下载电缆 Altera 编程单元APU图标下载设计文件到器件中,Process进度条中显示编程进度,编程下载完成后就可以进行目标芯片地硬件验证了.编程下载对话框2、 AS主动串行编程模式AS主动串行编程式地操作步骤如下:<1)选择QuartusⅡ主窗口Assignments菜Device命令,进入 Settings对话框地 Device页面进行设置,如下图.<2)选择QuartusⅡ主窗口地Tools菜单下地Programmer命令或点击图标,进入器件编程和配置对话框,添加硬件,选择编程模式为Active Serial Program;<3)单击添加相应地counter.pof编程文件,选中文件后地Program/Configure、Verify和Blank Check项,单击图标下载设计文件到器件中,Process进度条中显示编程进度.下载完成后程序固化在EPCS中,开发板上电后EPCS将自动完成对目标芯片地配置,无须再从计算机上下载程序.基于宏功能模块地设计QuartusⅡ软件为设计者提供了丰富地宏功能模块库,采用宏功能模块完成设计可极大提高电路设计地效率和可靠性.QuartusⅡ软件自带地宏模块库主要有三个,分别是Megafunctions库、Maxplus2库和Primitives库,在这里重点介绍基于Megafunctions 库地宏功能模块设计.1、在QuartusⅡ地图形编辑界面下,在空白。

Quartus II 说明书

编辑项目设置

打开项目基本设置对话框

增加/去除项目文件 增加 去除项目文件

增加 - 找到文件 - 增加 去除 - 从列表中选择 - 去除

2001 Altera Corporation 21

Quartus II 编译

2001 Altera Corporation 22

编译设置指南

指定编译模快及设定名 字

菜单Project > EDA Tool 菜单 Settings...

选择自定义 选择设置... 选择设置 选择库涵数映射文 件 (lmf) 可以是 EDIF, VHDL, or Verilog

2001 Altera Corporation 14

新建项目指南

1. 打开新建项目指南

2. 选择工作目录 3. 项目名称,可以是任何名字. 推荐使用和顶层设计名相同的名字. 推荐使用和顶层设计名相同的名字

模块编辑器模块编辑器 设计模块

! 从工具栏中产生模块和输入端口

点击工具栏中的"模 点击工具栏中的 模 块"来画一个图表 来画一个图表

右键点击模块.选择 属性,从弹出的对话 框中输入端口信息.

2001 Altera Corporation 8

模块编辑器- 智能 智能" 模块编辑器 "智能 连接

! Quartus II 有 "智能" 模块连接和映射

! 有参数限制的仿真

2001 Altera Corporation 33

编译报告

! 包含了怎样将一个设计放到一个器件中的所有信息

– – – – – – – – 器件使用统计 编译设置 底层显示 器件资源利用率 状态机的实现 方程式 延时分析结果 CPU 使用资源

Quartus_II使用教程-完整实例

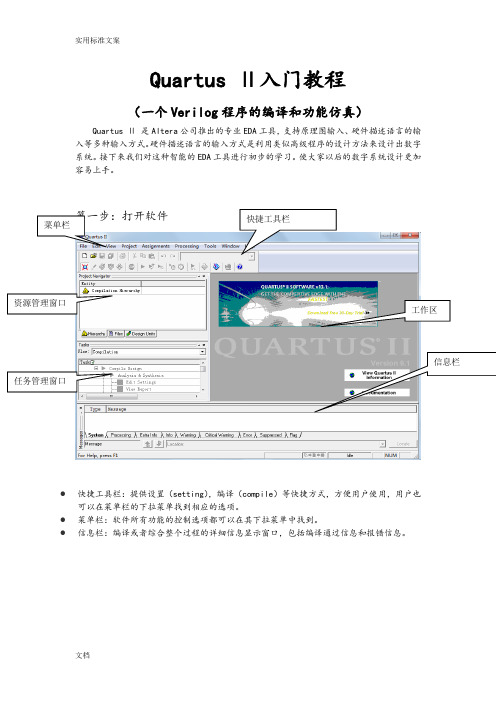

Quartus Ⅱ入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

●快捷工具栏:提供设置(setting ),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard1 工程名称:2添加已有文件(没有已有文件的直接跳过next )3 选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-10芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置)4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )5 工程建立完成(点finish )第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b;assign out2=a | b;endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location各个端口的输入输出第七步:整体编译(工具栏的按钮(start Complilation))第八步:功能仿真(直接利用quratus进行功能仿真)1将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function)2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by 1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist)接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):实用标准文案文档观察波形,刚好符合我们的逻辑。

QUARTUSII软件的授权

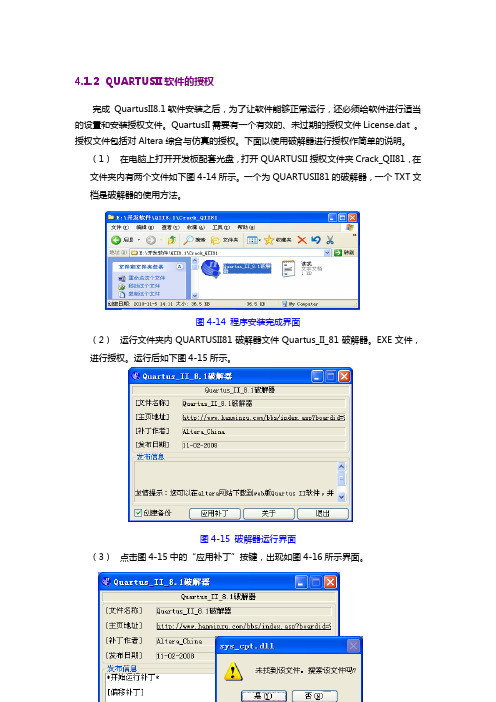

4.1.2QUARTUSII软件的授权完成QuartusII8.1软件安装之后,为了让软件能够正常运行,还必须给软件进行适当的设置和安装授权文件。

QuartusII需要有一个有效的、未过期的授权文件License.dat 。

授权文件包括对Altera综合与仿真的授权。

下面以使用破解器进行授权作简单的说明。

(1)在电脑上打开开发板配套光盘,打开QUARTUSII授权文件夹Crack_QII81,在文件夹内有两个文件如下图4-14所示。

一个为QUARTUSII81的破解器,一个TXT文档是破解器的使用方法。

图4-14 程序安装完成界面(2)运行文件夹内QUARTUSII81破解器文件Quartus_II_81破解器。

EXE文件,进行授权。

运行后如下图4-15所示。

图4-15 破解器运行界面(3)点击图4-15中的“应用补丁”按键,出现如图4-16所示界面。

图4-16 破解器运行界面(4)点击图4-16是的“是”按键,找到安装文件sys_cpt.dll进行替换破解。

一般sys_cpt.dll文件在安装路径/ALTERA/81/QUARTUS/BIN目录下。

如下图4-17所示。

图4-17 破解器运行界面(5)选中sys_cpt.dll文件,点击“打开”按键完成对软件的破解。

并准备生成授权文件license.dat,如图4-18所示。

图4-18 破解器运行界面(6)在图4-18所示的界面中选择存放license.dat的位置,点击“保存“按键,完成授权文件license.dat的生成。

出现如图4-19所示的界面,完成授权文件的生成。

图4-19 破解器运行界面(7)license.dat文件存放的路径名称不能包含汉字和空格,空格可以用下划线代替。

点击“退出“按键,退出破解器的运行。

(8)在计算机的开始菜单中或者双击电脑桌面上QuartusII软件的图标,打开已安装好的QuartusII软件来进行QuartusII软件的授权与注册,第一次打开QuartusII 软件则会出现如图4-20所示的提示信息。

quartus生成的各文件含义

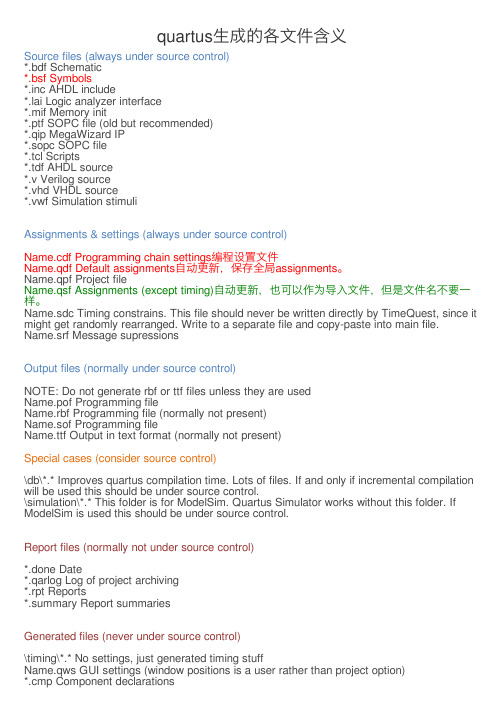

quartus⽣成的各⽂件含义Source files (always under source control)*.bdf Schematic*.bsf Symbols*.inc AHDL include*.lai Logic analyzer interface*.mif Memory init*.ptf SOPC file (old but recommended)*.qip MegaWizard IP*.sopc SOPC file*.tcl Scripts*.tdf AHDL source*.v Verilog source*.vhd VHDL source*.vwf Simulation stimuliAssignments & settings (always under source control)Name.cdf Programming chain settings编程设置⽂件Name.qdf Default assignments⾃动更新,保存全局assignments。

Name.qpf Project fileName.qsf Assignments (except timing)⾃动更新,也可以作为导⼊⽂件,但是⽂件名不要⼀样。

Name.sdc Timing constrains. This file should never be written directly by TimeQuest, since it might get randomly rearranged. Write to a separate file and copy-paste into main file. Name.srf Message supressionsOutput files (normally under source control)NOTE: Do not generate rbf or ttf files unless they are usedName.pof Programming fileName.rbf Programming file (normally not present)Name.sof Programming fileName.ttf Output in text format (normally not present)Special cases (consider source control)\db\*.* Improves quartus compilation time. Lots of files. If and only if incremental compilation will be used this should be under source control.\simulation\*.* This folder is for ModelSim. Quartus Simulator works without this folder. If ModelSim is used this should be under source control.Report files (normally not under source control)*.done Date*.qarlog Log of project archiving*.rpt Reports*.summary Report summariesGenerated files (never under source control)\timing\*.* No settings, just generated timing stuffName.qws GUI settings (window positions is a user rather than project option)*.cmp Component declarations*.dpf -⼏乎不变,为⼀个xml⽂件,当assignment pins时就会产⽣*.eqn Equations*.html -*.jpg Images generated by some megawizards?*.pin -*.ppf -Backup files (never under source control)*.bak Backup of single files*.qar Quartus archive补充:.v ------------------ verilog ⽂件.vhd ----------------- vhdl ⽂件.qpf ----------------- quartus ⼯程⽂件.vwf ----------------- ⽮量波形⽂件.bsf ----------------- 块符号⽂件.rpt ----------------- 报告⽂件.qsf ----------------- quartus配置⽂件.summary ----------- summary.pin ----------------- 引脚⽂件.sdo ----------------- delay.vo ------- ----------- gate level.qws ----------------- ⼯作区⽂件.pof ----------------- 编程对象⽂件.sof ------------------ SRAM对象⽂件.qar ------------------⼯程归档⽂件.SDK -----------------system development kit.mif ------------------memory initial file.ISO ----------------- 是ISO9660标准下的⽂件形式.srec ----------------S record.tdf ------------------text design file.gdf -----------------graphic desing fileHAL------------------Nios II运⾏库(或者称为硬件抽象层(HAL)) .tcl-------------------tool command language。

EDA设计流程及其工具QuartusII快速操作指南

本章内容

一. 安装与许可〔License〕 二. 工程项目与文件类型〔project & files

type〕 三. Quartus II菜单简介 四. 设计输入(design input) 五. 器件与引脚指配(device & pin

主要输出文件类型〔files type〕

Programmer Object File 编程文件 .pof

SRAM Object File

配置文件 .sof

Pin-Out File

引脚输出文 .pin 件(可用于 核对硬件连 接关系)

QuartusII 设计流程

设计 构想

编程 下载

设计 正确

功能 正确

8. VHDL设计输入 9. 原理图设计输入

VHDL设计输入

文件名称 必须和 ENTITY名 一致

元件符号调入 生成符号块 绘制节点连线 绘制节点总线连接

绘制导线工具

粘连〔移动〕

线段选中

原理图设计输入

原理图设计输入:符号调入

按下mouse右键->

原理图设计输入:符号调入〔续前〕

库符号

符号文件也可以是?

35

编

仿

编

译

真

程

Quartus II主菜单

File菜单

Project菜单

将设计文件参加工程项目中

电源估算文件生成 顶层设计文件设置

Assignments

菜单

器件和引脚指配 编译设置

Processing菜单->

EDA技术与应用讲义 第3章 原理图输入设计方法 QUARTUS II版本

有了HDL语言后?

硬件设计人员 的工作过程

已经 类似与

软件设计人员,那么

这种模式的好处是?

让我们先看看原来是如何做的->

Compiler Netlist Extractor (编译器网表提取器)

❖ The Compiler module that converts each design file in a project (or each cell of an EDIF Input File) into a separate binary CNF. The filename(s) of the CNF(s) are based on the project name. Example

电路的模块划分

❖ 人工 根据电路功能 进行 模块划分

❖ 合理的模块划分 关系到

1. 电路的性能 2. 实现的难易程度

❖ 根据模块划分和系统功能 确定: PLD芯片型号

模块划分后,就可以进行 具体设计 了

设计输入

一般EDA软件允许3种设计输入:

1. HDL语言 2. 电路图 3. 波形输入

图形设计输入的过程

件电路图设计 5. 综合调试 6. 完成

设计的几个问题

❖ 如何组织多个设计文件的系统?,项目的概 念。

❖ 时钟系统如何设计?

❖ 电路的设计功耗

❖ 高速信号的软件和硬件设计

The end.

以下内容 为 正文的引用,

可不阅读。

常用EDA工具软件

❖ EDA软件方面,大体可以分为两类:

1. PLD器件厂商提供的EDA工具。较著名的如:

❖ 第三方工具软件是对CPLD/FPGA生产厂家开发软件的补 充和优化,如通常认为Max+plus II和Quartus II对 VHDL/Verilog HDL逻辑综合能力不强,如果采用专用的 HDL工具进行逻辑综合,会有效地提高综合质量。

Quartus II工程文件的后缀含义

Quartus II工程文件的后缀含义上面这些文件可以分为五类:1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、. vht)、存储器初始化文件(.mif、.rif、.he x)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件)3. 编译结束后生成的报告文件(.rpt、.qsmg等)4. 根据个人使用习惯生成的界面配置文件(.qws等)5. 编程文件(.sof、.pof、.ttf等)上面分类中的第一类文件是一定要保留的;第二类文件在编译过程中会根据第一类文件生成,不需要保留;第三类文件会根据第一类文件的改变而变化,反映了编译后的结果,可以视需要保留;第四类文件保存了个人使用偏好,也可以视需要保留;第五类文件是编译的结果,一定要保留。

在使用版本控制工具时,我通常保留第一类、第三类和第五类文件。

但是第三类文件通常很少被反复使用。

所以,为了维护一个最小工程,第一类和第五类文件是一定要保留的。

此外,当一个项目的设置内容需要转移给另一个项目时,例如引脚分配信息,需要转移.tcl文件而不是.qsf文件。

.tcl文件与.qsf文件的关系以及如何生成.tcl文件我会在以后的日志中给出。

CyClone III C25 原版资料下载关于CPLD/FPGA一些问题1、PLD,CPLD,FPGA有何不同?答:不同厂家的叫法不尽相同,PLD是可编程逻辑器件的总称,早期多EEPROM工艺,基于乘积项结构。

FPGA是指现场可编程门阵列,最早由Xilinx公司发明。

多为SRAM工艺,基于查找表结构,要外挂配置用的EPROM。

Xilinx把SRAM工艺,要外挂配置用的EPROM的PLD叫FPGA,把Flash工艺、乘积项结构的PLD叫CPLD;Altera把自己的PLD产品:MAX系列,FLEX/ACEX/ APEX系列都叫作CPLD,即复杂PLD,由于FLEX/ACEX/APEX系列也是SRA M工艺,要外挂配置用的EPROM,用法和Xilinx的FPGA一样,所以很多人把Altera的FELX/ACEX/APEX系列产品也叫做FPGA.2、NiosII嵌入式处理器是一个什么样的处理器?与其他相比具有哪些功能? 答:1)Nios II嵌入式处理器是一个用户可配置的通用RISC嵌入式处理器。

Quartus2

2011-102011-10-18

湖北众友科技EDA工作室 湖北众友科技EDA工作室

11

步骤2:新建工程项目 步骤2:新建工程项目 2:新建工程

(6)可设置第三方EDA工具。若没有,直接单击NEXT 。

2011-102011-10-18

湖北众友科技EDA工作室 湖北众友科技EDA工作室

12

步骤2:新建工程项目 步骤2:新建工程项目 2:新建工程

步骤5:项目仿真 步骤5:项目仿真 5:

波形编辑窗口。“EDIT”菜单下End Time可设置仿真时间区 域,Grid Size可设该网格大小。

工具栏 信号栏 波形栏

2011-102011-10-18

湖北众友科技EDA工作室 湖北众友科技EDA工作室

25

步骤5:项目仿真 步骤5:项目仿真 5:

End Time和Grid Size窗口。

15

步骤3:建立图形文件 步骤3:建立图形文件 3:

(3)在模块编辑区的任何一个位置上双击鼠标。

模块编辑区

模块编辑8

湖北众友科技EDA工作室 湖北众友科技EDA工作室

16

步骤3:建立图形文件 步骤3:建立图形文件 3:

(4) 弹出Symbol窗口。出现Libraries元件库目录。点击 + 出 现下图。

宏功能元件库 其他元件库 基本元件库

2011-102011-10-18

湖北众友科技EDA工作室 湖北众友科技EDA工作室

17

步骤3:建立图形文件 步骤3

(5)调入元件74161、and2、not、input和output。 调入元件74161、and2 not、input和output。 74161

器件编程

quartusii设计中的差分信号在例化时的命名规则

quartusii设计中的差分信号在例化时的命名规则

在Quartus II中进行设计时,如果使用了差分信号,如DDR的IP中的mem_ck与mem_ck_n、mem_dqs与mem_dqs_n,在将其引入输出端

口时,对其命名有一定的规则,否则就会出现错误。

一般来说,差分信号的命名规则包括以下几点:

1. 信号名称:差分信号的名称应该简洁明了,能够清晰地表达出信号的含义和用途。

通常,信号名称会包含一个前缀和一个后缀,前缀表示信号的名称,后缀表示信号的方向(如“_n”表示反向)。

2. 信号前缀:差分信号的前缀应该相同,以便于识别和区分。

例如,在DDR的IP中,mem_ck和mem_ck_n的前缀都是“mem_ck”,表示它

们是一对差分信号。

3. 信号后缀:差分信号的后缀应该表明信号的方向。

例如,“_n”表示反向,“_p”表示正方向。

4. 信号连接:差分信号应该成对出现,即一个正信号和一个反信号。

在Quartus II中,可以通过例化的方式将差分信号引入输出端口。

例如,对于DDR的IP中的mem_ck和mem_ck_n,可以使用“.mem_ck(mem_ck_1) // .mem_ck”和“.mem_ck_n(mem_ck_n_1) // .mem_ck_n”的语句将其引入输出端口。

总之,在Quartus II中设计时,对于差分信号的命名规则需要遵循一定的规范,以确保设计的正确性和可读性。

同时,还需要注意差分信号的连接方式,确保正信号和反信号能够正确地配对使用。

QuartusII工程文件的后缀含义 (1)

Quartus II工程文件的后缀含义(上)File Type ExtensionAHDL Include File .incATOM Netlist File .atmBlock Design File .bdfBlock Symbol File .bsfBSDL file .bsdChain Description File.cdfComma-Separated Value File .csvComponent Declaration File .cmpCompressed Vector Waveform. File .cvwfConversion Setup File .cofCross-Reference File .xrfdatabase files .cdb,.hdb,.rdb,.tdbDSP Block Region File .macrEDIF Input File .edf,.edif,.ednGlobal Clock File .gclkGraphic Design File .gdfHardCopy files .datasheet,.sdo,.tcl,.vo Hexadecimal (Intel-Format) File .hexHexadecimal (Intel-Format) Output File .hexoutHSPICE Simulation Deck File .spHTML-Format Report File .htmI/O Pin State File .ipsIBIS Output File .ibsIn System Configuration File .iscJam Byte Code File .jbcJam File .jamJTAG Indirect Configuration File .jicLibrary Mapping File .lmfLicense File license.datLogic Analyzer Interface File .laiMemory Initialization File .mifMemory Map File .mapPartMiner edaXML-Format File .xmlPin-Out File .pinplacement constraints file .apcProgrammer Object File .pofprogramming files .cdf,.cofQMSG File .qmsgQuartus II Archive File .qarQuartus II Archive Log File .qarlogQuartus User-Defined Device File .qudQuartus II Default Settings File .qdfQuartus II Exported Partition File .qxpQuartus II Project File .qpfQuartus II Settings File .qsfQuartus II Workspace File .qwsRAM Initialization File .rifRaw Binary File .rbfQuartus II工程文件的后缀含义(下)File Type Extension Raw Programming Data File .rpdRouting Constraints File .rcfSignal Activity File .saf SignalTap II File .stpSimulator Channel File .scfSRAM Object File .sofStandard Delay Format Output File .sdoSymbol File .symSynopsys Design Constraints File .sdcTab-Separated Value File .txtTabular Text File .ttfTcl Script. File .tclText Design File .tdfText-Format Report File .rptText-Format Timing Summary File .tan.summary Timing Analysis Output File .taoToken File ted.tokVector File .vecVector Table Output File .tblvector source files .tbl,.vwf,.vec Vector Waveform. File .vwf/1_0000/Quartus%20file%20types.mht%23_Verilog_Des ign_File Verilog Design File .v,.vh,.verilog,.v lgVerilog Output File .voVerilog Quartus Mapping File .vqmVerilog Test Bench File .vtValue Change Dump File .vcdversion-compatible database files .atm,.hdbx,.rcf,.xmlVHDL Design File .vhd,.vhdlVHDL Output File .vhoVHDL Test Bench File .vhtXML files .cof,.stp,.xml waveform. files .scf,.stp,.tbl,.vec,.vwf上面这些文件可以分为五类:1.编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、. vht)、存储器初始化文件(.mif、.rif、.hex)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Quartus II文件后缀介绍

Quartus II是一款功能强大的EDA软件。

在这个集成开发环境中,PLD使用者可以完成编辑、编译、仿真、综合、布局布线、时序分析、生成编程文件、编程等全套PLD开发流程。

Quartus II以工程(Project)为单位管理文件。

保证了设计文件的独立性和完整性。

由于Quartus II功能众多,每一项功能都对应一个甚至多个文件类型。

在使用中,如果需要转移或备份某一工程对应的文件,对众多文件的取舍成了一个令人头痛的问题。

类似问题,在使用Maxplus II的过程中也很常见。

使用Quartus II自带的工程文件压缩功能可以省去取舍文件的麻烦。

但是.qar文件把众多文件压缩成一个文件,只有解压缩才能获取具体文件的信息。

如果使用版本控制工具(如CVS)的话,对.qar文件无法进行版本比较。

甚至当.qar文件受损时,部分甚至全部文件都无法恢复了。

而且,缺省配置的.qar文件也包含了一些非关键文件,存在一定的冗余。

解决这一问题的关键在于弄清文件扩展名的意义,明明白白地控制文件的取舍。

1. 编译必需的文件:设计文件(.gdf、.bdf、EDIF输入文件、.tdf、verilog设计文件、.vqm、.vt、VHDL设计文件、. vht)、存储器初始化文件(.mif、.rif、.hex)、配置文件(.qsf、.tcl)、工程文件(.qpf)。

2. 编译过程中生成的中间文件(.eqn文件和db目录下的所有文件)

3. 编译结束后生成的报告文件(.rpt、.qsmg等)

4. 根据个人使用习惯生成的界面配置文件(.qws等)

5. 编程文件(.sof、.pof、.ttf等)

上面分类中的第一类文件是一定要保留的;第二类文件在编译过程中会根据第一类文件生成,不需要保留;第三类文件会根据第一类文件的改变而变化,反映了编译后的结果,可以视需要保留;第四类文件保存了个人使用偏好,也可以视需要保留;第五类文件是编译的结果,一定要保留。

在使用版本控制工具时,我通常保留第一类、第三类和第五类文件。

但是第三类文件通常很少被反复使用。

所以,为了维护一个最小工程,第一类和第五类文件是一定要保留的。

此外,当一个项目的设置内容需要转移给另一个项目时,例如引脚分配信息,需要转移.tcl 文件而不是.qsf文件。

.tcl文件与.qsf文件的关系以及如何生成.tcl文件我会在以后的日志中给出。

.v ------------------ verilog 文件

.vhd ----------------- vhdl 文件

.qpf ----------------- quartus 工程文件

.vwf ----------------- 矢量波形文件

.bsf ----------------- 块符号文件

.rpt ----------------- 报告文件

.qsf ----------------- quartus配置文件

.summary ----------- summary

.pin ----------------- 引脚文件

.sdo ----------------- delay

.vo ------- ----------- gate level

.qws ----------------- 工作区文件

.pof ----------------- 编程对象文件

.sof ------------------ SRAM对象文件

.qar ------------------工程归档文件,

SDK -----------------system development kit

.mif ------------------memory initial file

.ISO ----------------- 是ISO9660标准下的文件形式

.srec ----------------S record

.tdf ------------------text design file

.gdf -----------------graphic desing file

HAL------------------Nios II运行库(或者称为硬件抽象层(HAL))

.tcl-------------------tool command language

下面的文件是从Quartus II帮助文件中拷贝出来的文件扩展名解释。