【精品】PPT课件 Viterbi译码

卷积码的译码ppt

所谓“最佳”是指具有最大后验条件概率

P(C

/

R)

max[ j

P(C

j

/

R)]

(5-34)

信道模型一般只告知先验的转移概率,因此必须

通过贝叶斯公式找出先、后验两种概率间关

P(C j

/ R)

P(C j )P(R / C j ) P(R)

其他特 VIP专享精彩活动

权

VIP专属身份标识

专属客服

! 开通VIP后可以享受不定期的VIP优惠活随时随地彰显尊贵身份。 VIP专属客服,第一时间解决你的问题。专属客服Q全部权益:1.海量精选书免费读2.热门好书抢先看3.独家精品资源4.VIP专属身份标识5.全站去广告6.名

档消耗一个共享文档下载特权。

年VIP

月VIP

连续包月VIP

享受100次共享文档下载特权,一次 发放,全年内有效

赠每的送次VI的发P类共放型的享决特文定权档。有下效载期特为权1自个V月IP,生发效放起数每量月由发您放购一买次,赠 V不 我I送 清 的P生每 零 设效月 。 置起1自 随5每动 时次月续 取共发费 消享放, 。文一前档次往下,我载持的特续账权有号,效-自

VIP有效期内享有搜索结果页以及文档阅读页免广告特权,清爽阅读没有阻碍。

–知识影响格局,格局决定命运 多端互通

抽奖特权

VIP有效期内可以无限制将选中的文档内容一键发送到手机,轻松实现多端同步。 开通VIP后可以在VIP福利专区不定期抽奖,千万奖池送不停!

福利特权

开通VIP后可在VIP福利专区定期领取多种福利礼券。

特权福利

特权说明

自适应Viterbi译码器技术

自适应Viterbi译码器技术摘要:随着现代通信技术的迅速发展,高速和高可靠性成为衡量信息传输质量的关键指标。

信道编码技术能够对信道差错进行控制,降低误码率,实现可靠性通信,具有重要的军事和民事意义。

Viterbi译码算法及其实现技术是信道编码技术的一个重要组成部分,但是其存在自身的缺陷或不足。

Viterbi译码算法的译码性能将会随着码的相关长度k增加而提高,但其实现的复杂度将以2k的比例增长。

本文提出了一种自适应Viterbi译码算法——IA VA(Improved Adaptive Viterbi Algorithm)。

该算法利用信噪比评估模块自适应地调整门限值的高低,并利用复杂度评估模块自适应地改变译码器的基状态数,从而合理利用硬件资源。

当译码器工作于低信噪比环境中时门限被自动调高,保证译码性能的同时适当减少了译码器的复杂度;当工作于高信噪比环境中时门限被自动调低,此时译码器复杂度得到锐减,译码模式将切换到基-4模式从而提高了译码速度,因此在大动态信噪比环境下该算法具有优越的性能。

关键词:信道编码;自适应Viterbi译码;Viterbi译码;卷积码The Technology of Adaptive Viterbi DecodingYIN Qinghong,XU Xin,LI Nan,SUN Zhao Lin(College of Electronic Science and Engineering, National University of Defense and Technology, Changsha410073, China )Abstract: With the development of modern communication technology, high speed and high stability have come into being two key factors when measuring the quality of information tansmission. The technology of channel encoding, which can control the channel errors, reduce the code error rate, and ensure the stable communication, has a deep meaning in military affairs and civil applicaton. The Viterbi decoding algorithm and the methd of its implementation are important parts of the channel encoding. However, they have their own limitation as well. In 1 the algorithm of Viterbi decoding, while the performance of decoding is improved with the increasing of length of the convolutional encoding , the complexity to implement it increases at the rate of 2k. A modified Viterbi decoding arithm IA V A is put forward. In the algorithm, while a SNR evaluating module is utilized to automatically adjust the gate-vaule, a complexity evaluating module is used to automatically adjust the decoder’s radix mode, through which, the resource is reasonably used. When working at the condition of low SNR, the gate-vaule is increased automatically. This way, reduces the decoding complexity while ensuring the good performance at the same time. When working at the condition of high SNR, the gata-vaule is decreased automatically to reduce thedecoding complexity. In this working condition, the decoding mode is changed to radix-4 mode, which resultes in a rapid improvement in the decoding speed, thus the algorithm has a good performance in the condition of wide dynamic SNR.Key words:channel encoding, adaptive Viterbi decoding, Viterbi decoding, convolutional encoding1. 引 言在高斯白噪声通道通信中,对于卷积译码Vterbi 译码算法是一种最优的解码算法。

译码器及译码显示课件

显示器选择

根据显示需求选择合适的显示器,如LED显示屏、LCD显示屏等, 考虑分辨率、亮度、色彩等方面。

性能参数

比较不同产品性能参数,如响应时间、稳定性、寿命等,选择符合实 际需求的设备。

译码器与显示器的接口连接

接口类型

了解译码器与显示器支持的接口类型,如TTL、 RS232、USB等,确保接口匹配。

译码器及译码显示 课件

目录

• 译码器概述 • 常见译码器芯片 • 译码器应用实例 • 译码显示技术 • 译码器与显示器的选择与使用

01

CATALOGUE

译码器概述

译码器的定义与功能

定义

译码器是一种多输入、多输出的 组合逻辑电路,用于将输入的二 进制代码转换为相应的输出信号 。

功能

译码器的主要功能是根据给定的 输入地址,将对应的存储单元或 电路驱动,从而实现数据的读取 、写入或控制操作。

优点

结构简单,使用方便,能够实现多路选择功能。

3

缺点

仅适用于3位二进制代码译码,扩展性有限。

用74HC4040实现BCD到7段显示译码

应用实例

在数字显示系统中,使用74HC4040驱动7段数码管 显示数字。

优点

能够直接驱动7段数码管,显示效果好。

缺点

仅适用于BCD码到7段数码管的译码,应用范围较窄 。

02

CATALOGUE

常见译码器芯片

74HC138译码器

一个3线-8线译码器,具有使能输入端,可以控制译码器在有 效电平下工作。

74HC138是一个3线-8线译码器,具有3个使能输入端和8个 输出端。当使能输入端处于有效电平时,译码器将输入的3位 二进制代码译码为对应的输出信号。这种译码器常用于地址 解码、数据分路等应用中。

最新-高速Viterbi译码器的优化和实现 精品

高速Viterbi译码器的优化和实现摘要大约束度卷积码作为信道纠错编码在通信中得到了广泛的应用,而其相应的译码器硬件复杂度大,限制了译码速度。

分析了译码器的结构,优化了各模块,合理地组织了存储器结构,简化了接口电路。

用实现译码器,提高了译码器速度。

关键词卷积码译码路径度量存储实现算法是一种基于最大后验概率的卷积译码算法,应用广泛。

的-95标准和3标准将卷积码作为高速实时数据传输的信道纠错编码,使译码器成为移动通信系统的重要组成部分。

为保证纠错性能,卷积码结束度一般选择比较大的,在3中规定约束度=9。

出于实时性的考虑,移动通信系统中对译码时延的要求比较高,需要高速译码器的支持。

可是译码算法的复杂度、所需存储器容量与结束长度成指数增长关系,成为限制译码器速度的瓶颈。

译码器每解码一位信息位就需对2-1个寄存器的状态进行路径度量,并对相应的存储单元进行读写。

这种情况下,可以采用状态路径存储单元分块的方法,以提高其译码性能,缺点是单元与存储器之间的接口电路十分复杂,不易实现。

本文分析和优化了译码器的结构,提出了一种实现方案,简化了接口电路,提高了速度。

用这种结构实现的单片集成译码器译码速率达350、时钟频率30。

以下先分析译碱器总体结构,然后对各模块设计和实现做详细说明。

1算法简述及译码器结构本文采用3标准规定的=9,码率=12的753,561卷积码,卷积编码器送出的码序列,经过信道传输后送入译码器的序列为。

译码器根据接受序列,按最大似然准则力图找出正确的原始码序列。

译码过程可用状态图表示,图1表示2个状态的状态转移图。

,和+2,表示时刻的两个状态。

在+1时刻,这两个状态值根据路径为0或者1,转移到状态2+1和2+1,+1。

每一种可能的状态转移都根据接收到的有噪声的序列计算路径度量,然后选择出各个状态的最小度量路径幸存路径。

算法就是通过在状态图中寻找最小度量路径向前回溯步,最后得到的即为译码输出。

本设计采用600芯片,在公司的-仿真环境下,用语言完成,并用的4综合实现。

简单的维特比译码

L1=M1/N1;%译码输出码长

%w=zeros(1,M1); %w表示判决输出;

%for mm=1:M1

% if abs(r(mm))>1

% w(mm)=1 ;

%else w(mm)=0;

% end

for k=1:L1 %输出序列码长

for st=1:numStates %状态

for i=0:numInputs-1 %当前输入

dout=dec2bin(trellis.outputs(st,i+1),N1)-48;

dist=sum((r((k-1)*N1+1:k*N1)-dout).^2); %计算汉明码距

next_metric(nextState)=x;

sur_path(nextState,1:k)=[path(st,1:k-1) i];

else

if x<next_metric(nextState) % 择优路径

cur_metric=zeros(1,numStates)+Inf;%汉明码距

cur_metric(1)=0;

next_metric=-ones(1,numStates);%下一状态码距

path=zeros(numStates,L1);

sur_path=zeros(numStates,L1);

next_metric=-ones(1,numStates);

path=sur_path; %最佳路径

end

out1=path(1,:); %输出

next_metric(nextState)=x;

sur_path(nextState,1:k)=[path(st,1:k-1) i];

卷积编码和Viterbi译码

卷积编码和Viterbi译码摘要本文的目的是向读者介绍了前向纠错技术的卷积编码和Viterbi译码。

前向纠错的目的(FEC)的是改善增加了一些精心设计的冗余信息,正在通过信道传输数据的通道容量。

在添加这种冗余信息的过程称为信道编码。

卷积编码和分组编码是两个主要的渠道形式编码。

简介前向纠错的目的(FEC)的是改善增加了一些精心设计的冗余信息,正在通过信道传输数据的通道容量。

在添加这种冗余信息的过程称为信道编码。

卷积编码和分组编码是两个主要的渠道形式编码。

卷积码串行数据操作,一次一个或数位。

分组码操作比较大(通常,多达几百个字节的情侣)消息块。

有很多有用的分组码和卷积多种,以及接收解码算法编码信息的DNA序列来恢复原来的各种数据。

卷积编码和Viterbi译码前向纠错技术,是一种特别适合于在其中一个已损坏的发射信号加性高斯白噪声(AWGN)的主要通道。

你能想到的AWGN信道的噪声,其电压分布也随着时间的推移,可以说是用高斯,或正常,统计分布特征,即一钟形曲线。

这个电压分布具有零均值和标准差这是一个信号与噪声比接收信号的信噪比(SNR)函数。

让我们承担起接收到的信号电平是固定的时刻。

这时如果信噪比高,噪声标准偏差小,反之亦然。

在数字通信,信噪比通常是衡量Eb /N的它代表噪声密度双面能源每比特除以之一。

卷积码通常是描述使用两个参数:码率和约束长度。

码率k/n,是表示为比特数为卷积编码器(十一)信道符号卷积编码器输出的编码器在给定的周期(N)的数量之比。

约束长度参数,钾,表示该卷积编码器的“长度”,即有多少K位阶段提供饲料的组合逻辑,产生输出符号。

K是密切相关的参数米,这表明有多少位的输入编码器周期被保留,用于编码后第一次在卷积编码器输入的出现。

的m参数可以被认为是编码器的记忆长度。

在本教程中,并在此示例的源代码,我集中精力率1 / 2卷积码。

Viterbi译码是一种两个卷积编码与解码,其他类型的算法类型的顺序解码。

经典:维特比译码精讲

编码器相关术语

(m,k,n)码,约束长度m,每次移位的比特k,码速率k/n, 状态S=(σ1 σ2 σ3 σ4),共2km钟状态

3

卷积码的状态转移图与栅格描述

[例1] (2,1,2)码的状态向量为σ=(σ2σ1),共有4种状态 S0=(0,0),S1=(1,0),S2=(0,1),S3=(1,1),如图所示。

状态图不能反映出状态转移与时间的关系 栅格图/篱笆图:将开放型的状态转移图按时间顺序

级联形成一个栅格图。 编码路径:状态序列σ在栅格图中形成的一条有向路

径。 当有向路径始于全“0”状态S0,又终于S0时,表明此

时编码器又回到全“0”状态,

8

卷积码的状态转移的栅格描述

红实线表示U=0时输入产生的转移分支; 黄虚线表示U=1时输入产生的转移分支。

从 S0 状态有两个分支,它们是 00 和 11,R0与这两个分支

比较,比较的结果和到达的状态如表 6.4.2 所示:

表 6.4.2

1

S0

幸存路径 第 0 分支的距离 到达状态

1

S1

00

1

S0

11

1

S1

S2

每个状态/节点都有两个存储器: 路径存储器:存储该状态的部分路径;

S3

R= 10

(2,1,2)码栅格图第一步

19

维特比译码的基本原理

对本例而言,按上述算法进行到第十一个分支后,四条路径 的前面分支都合并在一起。所以,只要译码深度足够,就可 达到较低的错误概率。一般,约为 (5~6)mn,所以,维特比译 码的延时可达 (5~6)m 个单位时刻(每个单位时刻为 n 个码元 长度)就可以对第0个接收码组的信息元进行判决。依此类推, 对接收序列中的诸码组进行译码。

卷积码的Viterbi译码设计设计

摘要在数字通信系统中,通常采用差错控制编码来提高系统的可靠性。

自P.Elias 首次提出卷积码编码以来,这一编码技术至今仍显示出强大的生命力。

目前,卷积码已广泛应用在无线通信标准中,如GSM,CDMA2000和IS-95等无线通信标准中。

针对N-CDMA数据传输过程中的误码问题,本文论述了旨在提高数据传输质量的维特比译码器的设计。

虽然Viterbi译码复杂度较大,实现较为困难,但效率高,速度快。

因此本文着重分析和讨论了1/2速率的(2,1,9)卷积码编码和其Viterbi译码算法。

深入研究卷积码编码原理和Viterbi算法原理后,提出了(2,1,9)卷积码编码以及Viterbi算法的初始化、加—比—选和回溯设计方案,运用查表的方法,避免了大量繁琐计算,使得译码简洁迅速,译码器的实时性能良好。

并充分利用TMS320C54X系列DSP芯片,用汇编语言完成了(2,1,9)卷积码编码和Viterbi 译码的程序。

关键词:差错控制编码、卷积码、Viterbi译码、TMS320C54X、DSPAbstractIn digital communication systems, error control coding is usually used to improve system reliability. Since P.Elias put forward the convolutional coding the first time, the coding is still showing strong vitality.,has become widely used in satellite communications, wireless communications and many other communication systemsas a kind of channel coding method. such as GSM, CDMA2000 and has been a wireless communication standards of IS-95.In view of the error problem in the process of N-CDMA data transmission, this paper discusses the aims to improve the quality of data transmission of victor design than the decoder.Although Viterbi decoding complexity is bigger, more difficult to achieve, but high efficiency and fast speed. So this article emphatically analyzed and discussed the 1/2 rate (2,1,9) convolution code coding and its Viterbi decoding algorithm. In-depth study on principle of convolution code coding and Viterbi algorithm, proposed the convolution code coding and Viterbi algorithm (2,1,9) initialization, add - than - choose and back design, using look-up table method, to avoid a large amount of tedious calculation, the decoding and quick, good real-time performance of the decoder. Make full use of the series of TMS320C54X DSP chip, using assembly language to complete the(2,1,9)convolution code coding and Viterbi decoding process.Keywords: error control coding, convolutional code, Viterbi decoding, TMS320C54X目录摘要 (1)Abstract (2)目录 (3)1.绪论 (1)1.1 移动通信及N-CDMA背景 (1)1.2 数字通信概述 (1)1.3 卷积编码与译码的发展 (3)1.4 主要研究工作 (3)2.DSP与CCS简介 (5)2.1 DSP概述 (5)2.1.1 DSP的主要特点 (5)2.1.2 CSSU单元概述 (7)2.2 CCS概述 (8)2.3 本章小结 (8)3.卷积码的理论基础 (9)3.1 卷积码的概述 (9)3.1.1 卷积码基本原理 (9)3.1.2 卷积码的纠错能力 (9)3.1.3 卷积码的表示方法 (10)3.2 Viterbi译码的概述 (11)3.3 本章小结 (14)4.卷积编码的实现 (15)4.1 (2,1,9)卷积码编码 (15)4.1.1 (2,1,9)卷积码编码设计方案 (15)4.1.2 (2,1,9)卷积码编码流程图 (16)4.1.3 (2,1,9)卷积编码程序实现 (16)4.1.4 (2,1,9)的程序仿真 (17)4.2 (2,1,9)卷积码状态转换表 (17)4.2.1 (2,1,9)卷积码状态转换表的设计算法 (18)4.2.2 (2,1,9)卷积码状态转换表的流程图 (18)4.2.3 (2,1,9)卷积码状态表 (18)4.2.4 (2,1,9)卷积码状态表的蝶形结构 (21)4.3 本章小结 (22)5. Viterbi译码的实现 (23)5.1 Viterbi译码基础 (23)5.2 Viterbi译码算法 (23)5.3 变量定义情况 (25)5.4 初始化 (26)5.4.1 初始化流程图 (27)5.4.2 初始化程序仿真 (27)5.5 加-比-选 (28)5.5.1加-比-选流程图 (29)5.5.2加-比-选程序仿真 (30)5.6 回溯 (31)5.6.1 回溯流程图 (32)5.6.2 回溯仿真图 (33)5.7 Viterbi纠错测试 (34)5.8 本章小结 (34)总结 (36)致谢 ............................................................................ 错误!未定义书签。

支持不同约束长度VITERBI译码器的设计实现与重构【控制理论与控制工程..

知识水坝为您整理

知识水坝为您整理

第四章Viterbi译码器重构策略研究

V'lrtex支持的重构方式有两种,一是按列重构,图4一H为其局部动态重构的示意图,它要求设计时必须有严格的模块划分,将电路划分为固定的逻辑块(FixedLogic)和重构的逻辑块口artialReconfiguredLogic),模块之间的数据必须通过磁总线∞usMacro)进行交换。

微总线保证了重构时各个模块之间的数据正常交换。

还有一种是小比特流的重构方式,使用于对设计改动比较小的场合,重构时仅仅比较电路前后的差别,产生相应的bit流,修改设计完成重构。

图4.11VirtexFPGA局部重构示意

对于第一种方法,可重构逻辑的划分有如下一些规则:

①重构模块必须占满FPGA的一整列,即是按列重构;

②重构模块的边界是不可改变的,重构模块所占据的位置和面积在一次划分好后,

再不可随意改变。

③重构模块与其他重构模块及固定模块之间必须通过微总线来实现信号的传递。

4.1.4重构技术的应用和性能

动态重构技术运用于系统设计中是一种对灵活性和速度的一种设计方法,与传统的纯软件设计和硬件设计方法相比较,既有软件的灵活性,又有纯硬件系统的速度,如图4—12所示:

灵活件

软件

可重构件

硬件速度

图4—12可重构技术与软、硬件设计性能对比

可重构系统主要适用于如下系统设计:①最新通信系统:DR-FPGA的动态重构特性正好可以适应不同制式和不同标准的通信要求,满足软件无线电技术的发展和第三代移动通信系统(3G)的需要,本文主要是针对此项应用,设计了不同参数的

45。

动态规划:卷积码Viterbi译码算法

动态规划:卷积码的Viterbi译码算法学院:网研院姓名:xxx 学号:xxx 一、动态规划原理动态规划(dynamic programming)是运筹学的一个分支,是求解决策过程(decision process)最优化的数学方法。

动态规划算法通常用于求解具有某种最优性质的问题。

在这类问题中,可能会有许多可行解,每一个解都对应于一个值,我们希望找到具有最优值的解。

动态规划算法与分治法类似,其基本思想也是将待求解问题分解成若干个子问题,先求解子问题,然后从这些子问题的解得到原问题的解。

与分治法不同的是,适合于用动态规划求解的问题,经分解得到子问题往往不是互相独立的。

若用分治法来解这类问题,则分解得到的子问题数目太多,有些子问题被重复计算了很多次。

如果我们能够保存已解决的子问题的答案,而在需要时再找出已求得的答案,这样就可以避免大量的重复计算,节省时间。

动态规划程序设计是对解最优化问题的一种途径、一种方法,而不是一种特殊算法。

不象搜索或数值计算那样,具有一个标准的数学表达式和明确清晰的解题方法。

动态规划程序设计往往是针对一种最优化问题,由于各种问题的性质不同,确定最优解的条件也互不相同,因而动态规划的设计方法对不同的问题,有各具特色的解题方法,而不存在一种万能的动态规划算法,可以解决各类最优化问题。

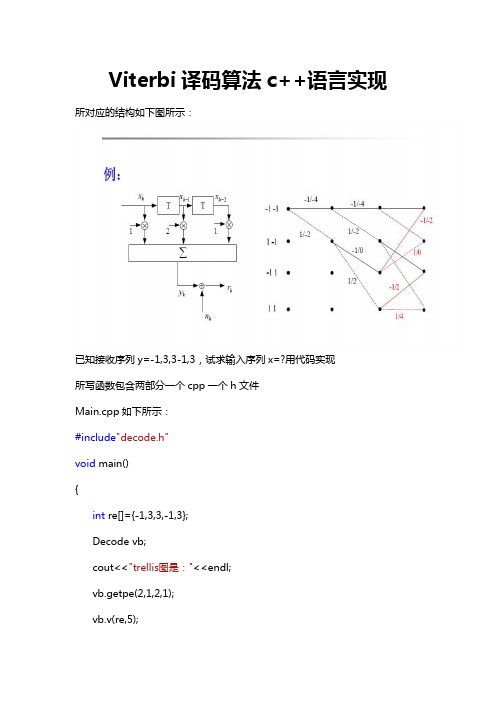

二、卷积码的Viterbi译码算法简介在介绍维特比译码算法之前,首先了解一下卷积码编码,它常常与维特比译码结合使用。

(2,1,3)卷积码编码器是最常见的卷积码编码器,在本次实验中也使用了(2,1,3)卷积码编码器,下面介绍它的原理。

(2,1,3)卷积码是把信源输出的信息序列,以1个码元为一段,通过编码器输出长为2的一段码段。

该码段的值不仅与当前输入码元有关,而且也与其之前的2个输入码元有关。

如下图所示,输出out1是输入、第一个编码器存储的值和第二个编码器存储的值逻辑加操作的结果,输出out2是输入和第二个编码器存储的值逻辑加操作的结果。

3G测试系统中的Viterbi译码及其DSP实现及优化(精)

3G测试系统中的Viterbi译码及其DSP实现及优化来源:EDN电子设计技术| 发表于:2007年07月10日本文相关DataSheet:TMS320C54X TMS320C55X TMS320C55x摘要介绍了一种用于测试TD-SCDMA手机终端测试平台中的关键技术——Viterbi译码。

研究用约束度K=9的卷积编码和最大似然Viterbi译码的差错控制方案,在Viterbi译码算法中,提出了原位运算度量、保存路径转移过程和循环存取幸存路径等方法,能有效地减少存储量、降低功耗,使得K=9的Viterbi译码算法可在CCS集成环境平台和TMS320C55X DSP芯片上实现,其性能指标符合3G PP通信协议标准要求,文中给出了适用于DSP编程的算法,给出了DSP 具体实现,同时给出了硬件的仿真结果。

0、引言随着TD-SCDMA产业化进程的日益明朗,3G之战还未吹号,硝烟味已弥漫了黎明前的市场。

这就要求尽快提供好的手机终端。

对手机终端的性能测试越显得迫在眉睫。

由于重邮信科3G研究院在TD方面有着很成熟的技术和经验,在此基础上我们不但推出了3G样机,而且致力于开发好的TD手机测试平台,本文所介绍的Viterbi译码方法是独具特色的TD测试平台中所用到的。

3GPP中TD-SCDMA系统采用了3种信道编码方案:卷积编码、Turbo编码和不编码。

不同类型的传输信道所使用的编码方案和编码效率是不同的。

本文介绍针对卷积编码的Viterbi译码方案。

针对DSP设计的特点,本文在不改变纠错性能的前提下提出了一系列的方法,如原位运算、保存转移、循环存取等,旨在将存储器的容量减到最小,将整体功耗降到最低。

1、Viterbi译码原理[1]Viterbi译码算法(简称VA算法)是由Viterbi在1967年首先提出的,它是一种针对卷积码的最大似然译码算法。

他不是在网格图上依次比较所有的可能路径,而是接受一段,计算、比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。

第9章 Viterbi译码及其实现

“黑色经典”系列之《DSP嵌入式系统开发典型案例》第9章Viterbi译码及其实现华清远见<ARM开发培训班>培训教材在通信系统中,信息传输的可靠性和有效性是相当重要的。

信息在传输时是经由信道(Channel)传输。

当其在信道传输过程中会受到各种干扰,使得传输信息掺杂各种错误序列在其中。

因此,在通信系统中,良好的纠错码可以有效地应用在信息传输过程中,以降低信息的误码率。

信息在传输时,先由信源发出消息,如语言、图像、文字等,消息进入通信系统后,经由信源编码器编码成信息序列1。

编码过程中,为了使传输有效,还加上一些与传输信息无关的冗余度。

接着信息序列1经过信道编码器编码成信息序列2,序列2是将信息序列1加入了更多的冗余数据(Redundancy Data),以抵抗信道中的各种干扰。

数字信号一般不适合直接在信道上传输,所以调制器是将数字信号转变成模拟信号,使其在信道中传输。

而信道中难免会受到噪声干扰,使信道的输出序列不同于信道的输入序列。

解调器将信道的输出序列由原来的模拟信号转化成数字信号,既是接收序列3,信息序列中因噪声干扰会掺杂一些错误的码元在其中。

信道译码器利用序列中的冗余码元去纠正错误,并且根据信道译码器的结果,产生接近于信息序列1的接收序列1。

整个译码过程是根据信道编码的结果和噪声在信道中的特性所得到的。

理想的结果是所有的错误都被更正回来,即接收序列等同于发送序列。

9.1 Viterbi译码概述在众多的纠错码中,卷积码(Convolutional Code)是一种在实际中得到广泛应用、性能很好的纠错码。

卷积码是不同于分组码的另一种码,它虽然也是把k个信息比特编成n个比特,但k和n都很小,延时小,特别适宜于以串行形式传输信息。

与分组码不同,卷积码中编码后的n个码元不但与当前段的众个信息码元有关,而且与前面(N−1)段的信息有关,编码过程中相互关联的码元为Nn个。

在编码器复杂程度相同的情况下,卷积码的性能优于分组码。

viterbi译码算法C++实现

Viterbi译码算法c++语言实现所对应的结构如下图所示:已知接收序列y=-1,3,3-1,3,试求输入序列x=?用代码实现所写函数包含两部分一个cpp一个h文件Main.cpp如下所示:#include"decode.h"void main(){int re[]={-1,3,3,-1,3};Decode vb;cout<<"trellis图是:"<<endl;vb.getpe(2,1,2,1);vb.v(re,5);cout<<"输入的x序列是:"<<endl;for(int i=0;i<5;i++)cout<<re[i]<<" ";getchar();cout<<endl;}Decode.h如下所示:/*对此进行简单的viterbi译码,将viterbi算法具体的细分,最后得到的函数,并且说明详细by:molongXidian University2013年月日23:12:04*/#include<iostream>#include<vector>using namespace std;class Decode{public:void gettrellis();void getpe(int a,int b1,int b2,int b3);void v(int *re,int n);void get_pre(int now,int *pre);int getcurrent(int j,int i,int in);int min_path(int a,int b);int get_out(int pre,int next);private:int trellis[4][4],s_number,multi1,multi2,multi3;struct get_path{int pre;int out;};};/*函数名称:getpe()作用:作为构造类创建对象的时候进行传参,其中第一个参数a 代表的是存储器个数,第二个参数代表的是所看到的从左到右,输入,存储器,存储器所乘的系数,将这三个参数传给类的对象*/void Decode::getpe(int a,int b1,int b2,int b3){s_number=a;multi1=b1;multi2=b2;multi3=b3;}/*函数名称:gettrellis()作用:得到基本的trellis转移图,存储器的个数为,所以有四个状态,定义trellis[4][4];其中trellis[i][j]代表的是原来的状态是i,其中当j=0的时候表示的是输入为的时候所对应的输出,j=1代表的是当输入为时转移到的下一个状态,j=2时代表的是输入为的时候所对应的输出,j=3的时候表示的是当输入为的时候转移到的下一个状态,所得到的trellis图在为类里面定义的私有变量,均可用*/void Decode::gettrellis(){for(int i=0;i<4;i++)for(int j=0;j<4;j++){int l,h;l=i&1;h=(i>>1)&1;if(j%2==0)trellis[i][j]=multi1*(j-1)+multi2*(2*h-1)+multi3*(2*l-1);//输入是或者的时候的输出elsetrellis[i][j]=(j&2)^h;//所转移到的下一状态cout<<trellis[i][j]<<" ";if(j==3)cout<<endl;}}/*函数名称:v(int *re,int n)输入参数:re为接收到的序列,对其进行直接操作,n为序列的个数输出参数:re同样作为输出参数,来表示最后译码所输出来的结果函数作用:对所接收到的序列进行viterbi译码*/void Decode::v(int *re,int n){gettrellis();vector<vector<int>>remb(4);vector<vector<get_path>>path(4);for(int i=0;i<4;i++){remb[i].resize(n);path[i].resize(n);for(int j=0;j<n;j++){remb[i][j]=0;path[i][j].out=100;path[i][j].pre=100;//remb[i][j]=min_path(remb[pre1][j-1]+getcurrent(pre1,i,re[j]),remb[ pre2][j-1]+getcurrent(pre2,i,re[j]));}}/*remb[i][j]的作用是存储当接收第j个序列的时候,到i状态的路径最小值path[i][j].out表示的是i所对应前一个状态pre到状态i时所对应的输出path[i][j].pre表示的是第i个状态所对应的前一个状态是哪一个通过path的存储,最后在remb里面找到路径的最小值,顺着path来输出最后的译码结果*/for(int i=0;i<4;i++){remb[i][0]=getcurrent(0,i,re[0]);path[i][0].pre=0;path[i][0].out=get_out(0,i);}/* 对remb的首列以及path的首列进行初始化操作*/for(int j=1;j<n;j++){for(int i=0;i<4;i++){int pre[2];/*有两个前状态转移到状态i,定义pre[2]*/get_pre(i,pre);/*得到i所对应的前一状态所对应的两个值*/int a=getcurrent(pre[0],i,re[j]);int b=getcurrent(pre[1],i,re[j]);remb[i][j]=min_path(remb[pre[0]][j-1]+getcurrent(pre[0],i,re[j]),remb [pre[1]][j-1]+getcurrent(pre[1],i,re[j]));/*存储到i的最小距离*/if(remb[i][j]==(remb[pre[0]][j-1]+getcurrent(pre[0],i,re[j]))){path[i][j].pre=pre[0];path[i][j].out=get_out(pre[0],i);/*判断前一状态到底是哪一个,删除一条路径,只剩下最小路径*/}else{path[i][j].pre=pre[1];path[i][j].out=get_out(pre[1],i);}}}int minimum;int min=1000;for(int i=0;i<4;i++){if(remb[i][4]<min){min=remb[i][4];minimum=i;}/*通过对最后一列的寻找得到最小距离*/ }for(int j=n-1;j>=0;j--){re[j]=path[minimum][j].out;minimum=path[minimum][j].pre;/*通过path倒序得到译码所对应的输出*/ }}/*函数名称:get(int pre,int now)输入参数:pre表示前一个状态,now表示当前的状态输出参数:从状态pre转移到状态now所对应的输出函数作用:通过前一状态以及当前状态,来确定输出*/int Decode::get_out(int pre,int now){int out,count=0;for(int j=0;j<2;j++)if(trellis[pre][2*j+1]==now){out=2*j-1;count++;}if(count==0)out=1000;return out;}/*函数名称:get_pre(int now,int *pre)输入参数:当前状态now,*pre代表的是now所对应的前一状态的两个值输出参数:得到前一状态的两个值,即得到是哪两个状态可以转移到状态now 函数作用:得到可以转移到当前状态的前一状态的两个值,例如状态->2,0->2那么这就是得到和这两个值*/void Decode::get_pre(int now, int *pre){int count=0;for(int i=0;i<4;i++)for(int k=0;k<2;k++){if(trellis[i][2*k+1]==now&&count==0){pre[0]=i;count++;}if(trellis[i][2*k+1]==now&&count!=0){pre[1]=i;}}}/*函数名称:getcurrent(int j,int i,int in)输入参数:j表示的是前一状态,i表示的是当前状态,in表示的是接收到的数字输出参数:result表示从状态j到状态i所对应的输出和接收参数in的汉明距离函数作用:得到每一个分支的汉明距离,返回的值是绝对值*/int Decode::getcurrent(int j,int i,int in)//j代表前一个,i表示后一个,in表示输入接收到的数字{int result;int count=0;for(int k=0;k<2;k++){if(trellis[j][2*k+1]==i){result=in-trellis[j][2*k];count++;}}if(count==0)result=10000;return abs(result);}//在此处应该返回的是绝对值,不能是单纯的带符号的值/*函数名称:min_path(int a,int b)输入参数:a和b两个数值输出参数:a和b之间的最小值函数作用:取两条转移路径的最小值*/int Decode::min_path(int a,int b){if(a>b)return b;elsereturn a; }。

卷积编码和Viterbi译码-ZCL.SPACE

卷积编码和Viterbi译码zcl.space目录1引言1 2编码1 3译码2 4回溯4 5回溯深度6 6软译码61引言1965年,Peter Elias发明卷积码。

1967年,Andrew J.Viterbi(高通的创始人之一)发明了一种高效的译码算法:Viterbi算法。

Viterbi译码器可能是当前应用最广泛的一种卷积译码器。

2005年,G.David Forney在南加州大学的Viterbi Conference上提到:每秒,全世界的Viterbi译码器恢复的的二进制比特数是1015。

今天,我们来看看viterbi译码器如何实现译码。

2编码译码之前,先看如何卷积编码。

描述卷积编码器的方法有很多,按照每种描述,我们都可以实现卷积编码。

以约束长度为3,码率为1/2,生成多项式为g0=[111],g1=[101]的卷积码为例,图1左侧给出了移位寄存器电路图表示,图1右侧的表格是左侧的等价描述,显然左侧的表示更直观,右侧的表述更具体。

图1:卷积编码器的两种描述:移位寄存器和输入输出状态表卷积编码器还有一种描述:篱笆图描述。

篱笆图让Viterbi译码过程生动了许多,我认为是一个很伟大的发明,其作用和法拉力用磁感线表示磁场的存在一样,让难以理解的抽象过程瞬间活灵活现。

另外,在Turbo码的译码分析过程中,篱笆图也发挥着非常重要的作用。

图1右侧的表格可以表示如图2所示。

图2:卷积编码器篱笆图描述通过对篱笆图2进行时间上的延展,给定输入,我们可以很容易获得输出。

假设输入为(010111001010001)2(2.1)则编码输出为(001110000110011111100010110011)2(2.2)输出的获得过程如图3所示。

值得注意的是,在图3中,t=16和t=17时刻依然有0输入。

这两个0的作用是冲洗编码器,使得编码器的状态归零。

这样做的好处是Viterbi译码器知道编码器的最后一个状态是零状态。