基于单片机制作高频DDS信号发生器

基于DDS的信号发生器设计

基于DDS的信号发生器设计摘要本设计主要是基于DDS的信号发生器的设计,该信号发生器主要有三大模块,主控制器模块、信号发生模块和液晶显示模块。

采用A T89S52单片机为主控制器,由它来控制DDS芯片AD9835再通过LCD12864显示输出信号信息,可以完成数字量输入到模拟量输出的转换,然后经运放调节电压幅度,产生0Hz~15MHz的正弦波、三角波和方波,最后由液晶屏显示。

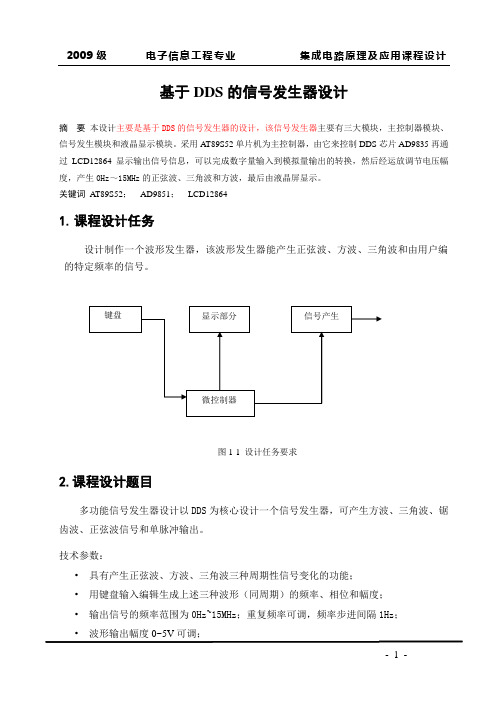

关键词A T89S52;AD9851;LCD128641.课程设计任务设计制作一个波形发生器,该波形发生器能产生正弦波、方波、三角波和由用户编的特定频率的信号。

图1-1设计任务要求2.课程设计题目多功能信号发生器设计以DDS为核心设计一个信号发生器,可产生方波、三角波、锯齿波、正弦波信号和单脉冲输出。

技术参数:•具有产生正弦波、方波、三角波三种周期性信号变化的功能;•用键盘输入编辑生成上述三种波形(同周期)的频率、相位和幅度;•输出信号的频率范围为0Hz~15MHz;重复频率可调,频率步进间隔1Hz;•波形输出幅度0~5V可调;•具有显示输出波形的类型、重复频率(周期)和幅度的功能;发挥部分•用键盘或其他输入装置产生任意波形;•波形输出幅度0~5V可调;•增加稳幅输出功能,当负载变化时,输出电压幅度比那化不大于±3‰(负载电阻变化范围:100Ω~∞);•具有掉电存储功能,可存储掉电前用户编辑的波形和设置;3.设计总体方案选择本设计的核心问题是信号的控制问题,其中包括信号频率、信号种类以及信号强度的控制。

在设计的过程中,我们综合考虑了以下四种实现方案:3.1方案一采用555集成芯片函数发生器,555可以产生可变的正弦波、方波、三角波及实现频率控制,但由于产生的频率较低,本方案将不采用。

3.2 方案二采用低温漂、低失真、高线性单片压控函数发生器ICL8038,产生频率(0.001~300KHZ)可变的正弦波、三角波、方波及数控频率调整。

基于单片机的DDS信号发生器设计毕业论文

摘要本文首先介绍了信号发生器的发展以及直接数字频率合成技术(DDS)的现状和发展趋势,然后介绍了DDS的原理结构及其主要构成部分。

再根据系统的要求,比较合理地采用了DDS技术,以单片机AT89S52和AD9850芯片为核心,设计了一种结构简单性能优良的信号发生器。

最后详细分析了该信号发生器的系统结构,软硬件设计和具体电路实现。

信号发生器的硬件部分包括三个模块,分别是单片机主控制模块,DDS模块和信号频率显示模块。

软件部分主要开发基于单片机AT89S52的数据处理和控制程序,以及信号发生器的外部通信程序。

最终完成实验电路板的制作,并通过电路板的调试,实现电路工作正常。

根据系统的最终测试结果可知该信号发生器具有输出信号波形精度高,频带宽等特点。

关键词:信号发生器;DDS;AT98S52;AD9850;频率;ABSTRACTThis article describes the development of the signal generator, the status and development trends of direct digital frequency synthesis (DDS) technology at first, then introduces the principle of DDS structure and its main components. According to system requirements, more rational use of DDS technology, single-chip AT89S52 and AD9850 chip as the core, has designed a simple structure and excellent performance of the signal generator. Finally, there is a detailed analysis of the signal generator system architecture, hardware and software design and specific circuit implementation. The hardware portion of the signal generator consists of three modules, namely, single-chip main control module, DDS module and signal frequency display module. Some of the major software development based on MCU AT89S52 data processing and control procedures, as well as external communication signal generator program. Completing the pilot circuit board production, and through the debug board to realize the circuit is working properly. According to the results of final test, the system shows that the output signal waveform signal generator has high accuracy, bandwidth and other characteristics.Keywords: Signal Generator; DDS; AT98S52; AD9850; Frequency目录摘要 (I)ABSTRACT .................................................................................................................. I I 第1章绪论 (1)1.1 课题背景 (1)1.2 课题的主要研究目的和意义 (1)第2章 DDS简介 (3)2.1 DDS结构 (3)2.2 频率预置与调节电路 (4)2.3 累加器 (4)2.4 控制相位和控制波形的加法器 (5)2.5 波形存储器 (5)2.6 D/A转换器 (5)2.7 低通滤波器 (6)第3章系统整体设计方案 (7)3.1 系统设计原理 (7)3.2 总体设计框图 (7)第4章系统各模块组成 (8)4.1 单片机控制模块 (8)4.1.1 AT89S52单片机介绍 (8)4.1.2 AT89S52功能特性描述 (8)4.1.3 时钟电路 (11)4.1.4 复位电路 (11)4.2 按键控制模块 (12)4.3 LCD显示模块 (13)4.4 AD9850 与单片机连接模块 (13)4.4.1 AD9850简介 (13)4.4.2 AD9850的控制字与控制时序 (16)4.4.3 单片机与AD9850的接口 (18)第5章软件设计与硬件调试 (20)5.1 程序流程图 (20)5.2 软件测试 (21)5.3 硬件电路制作 (21)5.4 硬件电路调试 (22)第6章结束语 (27)致谢 (28)参考文献 (29)附录1 原理图 (30)附录2 主程序代码 (31)第1章绪论1.1 课题背景信号发生器[1],它是一种悠久的测量仪器,最早出现于十九世纪20年代。

基于DDS技术的信号发生器的设计与实现

基于DDS技术的信号发生器的设计与实现DDS(Direct Digital Synthesis)技术是一种基于数字信号处理的频率合成技术,通过数字方式生成正弦波信号。

DDS信号发生器可以用于科学实验、通信系统中的频率合成、音频处理等应用领域。

通过DDS技术,可以实现高精度、稳定性好、频率范围广的信号发生器。

DDS信号发生器的基本原理是:通过一个相位累加器、一个频率累加器和一个波表,来生成一个时域上的正弦波信号,并将其转换为模拟电压信号输出。

相位累加器用来控制波表中的每个周期的采样点,频率累加器用来控制相位累加器的步进。

波表中存储了一个完整的正弦波周期的数值,波表的长度决定了信号发生器的频率分辨率。

DDS信号发生器的主要模块包括:时钟模块、相位累加器、频率累加器、波表和数模转换器。

时钟模块是DDS信号发生器的产生步进信号的时钟源,可以采用稳定的晶振或者时钟信号源。

时钟信号的频率决定了DDS信号发生器的输出信号的频率精度。

相位累加器是DDS信号发生器的核心模块,它接收时钟信号,并根据频率累加器的输入生成一个相位累加信号。

相位累加器可以采用简化的模数累加器,根据时钟信号的周期计算脉冲个数,每当相位累加信号增加一个固定的脉冲数时,波表就输出一个采样点。

频率累加器实时地改变相位累加器的步进,从而改变信号发生器的输出频率。

频率累加器可以通过输入一个控制信号来改变频率累加器的增加或减少的步进大小,从而实现更精细的频率调节。

波表是DDS信号发生器的存储波形数据的模块。

它包含了一个完整的正弦波周期的采样点的数值,波表的长度决定了信号发生器的输出信号的频率分辨率。

波表的数据可以事先存储在ROM中,也可以动态生成。

数模转换器将生成的波形数据转换为模拟电压信号输出。

数模转换器的位宽决定了输出信号的精度,位宽越大,精度越高。

除了上述基本模块,DDS信号发生器还可以添加比较器、滤波器等模块,以实现输出电平调节、滤波等功能。

基于单片机制作高频DDS信号发生器

基于单片机制作高频DDS信号发生器在现代科学和电子技术的不断进步下,数字信号发生器(DDS)已经成为了频率控制和生成的重要工具。

尤其是高频DDS信号发生器,其在雷达、通信、电子对抗等领域的应用具有不可替代的地位。

本文将介绍如何使用单片机制作高频DDS信号发生器。

一、DDS技术概述DDS,全称Direct Digital Synthesizer,即直接数字合成器,其工作原理是将数字信号通过数模转换器(DAC)转换成模拟信号。

DDS 技术的核心是相位累加器,它将输入的数字信号的相位进行累加,从而生成新的频率信号。

二、硬件设计1、单片机选择:本设计选用具有高速、低功耗、高集成度的单片机,如STM32F4系列。

2、频率控制字:通过设置频率控制字(FCW),可以控制输出信号的频率。

频率控制字由一个16位二进制数组成,表示了相位累加的步进大小。

3、存储器:使用Flash存储器存储预设的频率波形数据。

4、DAC:数模转换器将存储器中的波形数据转换成模拟信号。

本设计选用具有高分辨率、低噪声、低失真的DAC芯片。

5、滤波器:使用LC滤波器对DAC转换后的信号进行滤波,以得到更加纯净的信号。

三、软件设计1、相位累加器:相位累加器是DDS的核心,它将输入的数字信号的相位进行累加,从而生成新的频率信号。

2、波形查找表:将所需的波形数据存储在波形查找表中,通过查表的方式获取波形数据,可以大大提高DDS的工作效率。

3、控制逻辑:控制逻辑负责处理输入的控制信号,如启动、停止、频率控制字等。

4、通信接口:为了方便远程控制,需要设计通信接口,如SPI、I2C 等。

四、性能测试1、频率范围:测试DDS输出信号的频率范围是否满足设计要求。

2、频率分辨率:测试DDS输出信号的频率分辨率是否达到设计要求。

3、信号质量:测试DDS输出信号的信噪比、失真度等指标是否满足设计要求。

4、稳定性:长时间运行后,测试DDS输出信号的频率是否稳定。

5、远程控制:测试通信接口是否正常工作,可以通过计算机或者其他控制器对DDS进行远程控制。

基于单片机制作高频DDS信号发生器

目录1 DDS技术的基本原理 (2)2.1 DDS结构 (2)DDS数学原理 (5)2 总体设计方案 (7)3.1系统设计原理 (7)3.2总体设计框图 (8)3系统的硬件设计 (8)3.2 DDS芯片的选择及与单片机之间的通信 (8)3.3 单片机〔AT89S52〕控制电路 (11)3.4 液晶显示模块 (14)3.5 低通滤波器的设计 (16)4 信号发生器的软件设计 (17)4.1 程序流程图 (17)4.2 键盘扫描流程图 (19)4.3 LCD的显示 (21)5部分系统的仿真和调试 (21)6 系统的程序代码................ 错误!未定义书签。

7设计心的及体会 . (25)8 参考文献 (26)1 DDS技术的基本原理2.1 DDS结构1971年,美国学者等人撰写的“A Digital Frequency Synthesizer”-文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新组成原理。

限于当时的技术和器件产,它的性能指标尚不能与已有的技术相比,故没受到重视。

近几年间,随着微电子技术的迅速发展,直接数字频率合成器〔Direct Digital Frequency Synthesis简称DDS或DDFS〕得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的佼佼者。

具体表达在相对带宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

DDS是直接数字式频率合成器〔Direct Digital Synthesizer〕的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

直接数字频率合成器〔Direct Digital Synthesizer〕是从相位概念出发直接合成所需波形的一种频率合成技术。

DDS信号发生器实验报告含原理图PCB和代码

电子信息技术综合实训报告格式竞赛题名称:《DDS信号发生器的设计》队员名称:评阅人签名:2012年9月15日1、设计思路描述:本设计是一个以AT89C51单片机为核心基于DAC0832芯片的DDS信号发生器。

信号发生器采用数字波形合成技术,通过硬件电路和软件程序相结合,可输出正弦波和三角波,波形的转换可通过软件控制。

本设计通过按键选择波形,经过AT89C51单片机将数据输出到DAC0832,由数字信号转变为模拟信号,再通过运放器稳定地输出到示波器上。

原理框图如下:2、硬件电路图:DAC0832是采样频率为八位的D/A转换器件,芯片内有两级输入寄存器,使DAC0832具备双缓冲、单缓冲和直通三种输入方式,以便适于各种电路的需要(如要求多路D/A异步输入、同步转换等)。

D/A转换结果采用电流形式输出。

要是需要相应的模拟信号,可通过一个高输入阻抗的线性运算放大器实现这个供功能。

运放的反馈电阻可通过RFB端引用片内固有电阻,还可以外接。

该片逻辑输入满足TTL电压电平范围,可直接与TTL电路或微机电路相接。

下面是DAC0832引脚图和内部结构电路图DAC0832引脚功能说明:DI0~DI7:数据输入线,TLL电平。

ILE:数据锁存允许控制信号输入线,高电平有效。

CS:片选信号输入线,低电平有效。

WR1:为输入寄存器的写选通信号。

XFER:数据传送控制信号输入线,低电平有效。

WR2:为DAC寄存器写选通输入线。

Iout1:电流输出线。

当输入全为1时Iout1最大。

Iout2: 电流输出线。

其值与Iout1之和为一常数。

Rfb:反馈信号输入线,芯片内部有反馈电阻。

Vcc:电源输入线 (+5v~+15v)Vref:基准电压输入线 (-10v~+10v)AGND:模拟地,摸拟信号和基准电源的参考地。

DGND:数字地,两种地线在基准电源处共地比较好。

主控电路及数模转换电路分别如下:主控电路数模转换电路3软件流程图:4测试方法描述:运用proteus软件设计好电路图,将程序代码编译好以后载入proteus中的AT89C51芯片进行仿真。

基于单片机DDS信号发生器的硬件设计

基于单片机DDS信号发生器的硬件设计单片机DDS信号发生器是一种利用数字直接频率合成技术(Direct Digital Synthesis, DDS)来生成高精度信号波形的设备。

它通过调用存储在单片机中的频率、幅度和相位数据,实时更新波形,从而实现高速、高分辨率和低失真的信号发生器功能。

在本文中,将简要介绍单片机DDS信号发生器的设计流程以及其硬件实现。

设计流程:1.确定需求和规格:首先需要明确所需信号的频率范围、分辨率、输出幅度和失真要求等基本参数,以确定设计的方向和重点。

2.硬件选型:根据需求确定适合的单片机型号和外围器件,如振荡器、滤波器、放大器等。

3.硬件连接:根据单片机的引脚功能和外部器件的连接方式设计电路图,将各模块连接起来。

4.编程开发:编写单片机控制程序,实现DDS算法和信号波形生成,并将其烧录到单片机中。

5.调试和优化:通过实际调试和测试,不断优化硬件和软件设计,使其符合设计要求。

硬件实现:1.单片机选择:选择一款适合的高性能单片机作为控制核心,如STM32系列、PIC系列等,具有较高的计算性能和丰富的功能模块。

2.时钟源部分:基于晶振或者DDS芯片提供的时钟信号作为主时钟源,保证信号发生器稳定输出。

3.数字与模拟部分:DDS信号发生器的核心是DDS芯片,它与单片机通过SPI接口通信,实现信号波形的生成和调试。

4.输出功率放大器:将DDS芯片输出的信号通过功率放大器放大至所需的幅度,以驱动外部电路工作。

5.滤波器设计:为了消除输出信号中的高次谐波和噪声干扰,需要设计合适的低通滤波器,保证输出信号的纯净度和稳定性。

6.电源管理:为各个模块提供稳定可靠的电源,充分考虑信号发生器的功耗和稳定性要求。

7.外部控制:设计合适的用户接口和控制按钮,方便用户操作和调节信号波形的参数。

总结:单片机DDS信号发生器的硬件设计涉及到信号生成、时钟同步、数字模拟转换、输出功率放大和滤波等多个方面,需要综合考虑各个模块的性能和需求,以实现高质量、高稳定性的信号输出。

基于单片机和FPGA的DDS任意波形信号发生器的设计

基于单片机和FPGA的DDS任意波形信号发生器的设计摘要:本文主要对任意波形信号发生器的软硬件设计进行了相关的研究,并提出了一种新的设计思路,以现场可编程器件FPGA和单片机芯片为核心,设计任意波形信号发生器的硬件连线电路和编写相关软件程序,实现了上位机对硬件模块部分产生任意波形信号的控制。

关键词:信号发生器任意波形AT89C51FPGA1 引言任意波形发生器是电子技术领域应用最为广泛的电子测量仪器,它是信号源发展方向的代表。

由于DDS技术的查找合成波形的方法能够满足产生任意波形的要求,所以,目前大多数生产任意波形发生器的厂家都利用DDS技术来实现任意波形发生器。

本设计采用TMEL公司的单片机芯片和Xilinx公司的Virtex-Ⅱ系列FPGA芯片来实现任意波形信号发生器硬件部分的电路设计,采用美国NI公司的Labwindows/CVI作为开发平台,开发一个任意波形信号发生器的波形编辑软件,从而实现任意波形信号发生器软件模块对硬件模块产生相应波形信号的控制。

2 系统硬件设计在不影响功能的情况下,本设计简化了硬件部分的电路设计,把设计分成了多个实现模块,主要有单片机实现模块和FPGA实现模块。

单片机实现模块主要是由ATMEL公司的AT89C51芯片实现,该模块是用来完成数据传输、通信和控制数据处理电路工作等功能的。

FPGA实现模块是由Xilinx公司的FPGA芯片XC2V3000结合一些其他电路实现的,主要是用来完成DDS数据处理,实现任意波形的输出。

2.1单片机实现模块本设计选用ATMEL公司的单片机芯片AT89C51,AT89C51采用ATMEL技术,与MCS-51指令集和输出管脚相兼容,是一种高效微控制器。

本设计利用AT89C51主要是来控制显示、键盘以及FPGA电路。

单片机芯片AT89C51与液晶显示器的连线图如图1所示,AT89C51与液晶显示器通过P0口和P2口的部分位连接实现,并通过AT89C51芯片的和功能端实现读写控制。

毕业设计(论文)-基于DDS芯片AD9951的信号发生器

基于DDS芯片AD9951的精密信号发生器设计摘要直接数字频率合成(Direct Digital Frequency Synthesis简称DDS)是近年来迅速发展起来的一种新的频率合成方法。

而AD9951是美国模拟器件公司(ADI)最新推出的高集成度DDS芯片。

本设计采用该芯片,以AT89S52单片机为控制,采用AT24C02来存储重要的系统数据,由1602点阵式字符型液晶显示模块作为显示器,并加上一个小键盘构成了精密信号发生器。

要求其输出频率范围为0~160MHz、最小步进为10Hz或者1Hz、输出信号幅度大于0.3Vp-p、杂散小、有掉电数据保持功能。

文中详细介绍了DDS的工作原理以及该信号发生器的软、硬件设计方案,并给出了具体的程序设计。

指标关键词:直接数字频率合成(DDS)、AD9951、AT89S52、信号发生器、频率控制字直接数字频率合成(Direct Digital Frequency Synthesis简称DDS)是近年来迅速发展起来的一种新的频率合成方法,广泛应用于通讯、导航、雷达、遥控遥测、电子对抗以及现代化的仪器仪表工业等领域。

而AD9951是美国模拟器件公司(ADI)最新推出的高品质、高集成度DDS芯片。

本设计采用该DDS芯片作为核心元件,以AT89S52单片机为主控器件、并辅以AT24C02存储重要的系统数据、1602点阵式字符型液晶显示模块作为显示器,构成了一种精密的DDS信号发生器。

文中详细介绍了DDS的工作原理以及该精密信号发生器的软、硬件设计方法,并给出了具体的程序设计方案。

设计出的信号发生器,输出频率范围为0~160MHz、最小步进为10Hz或者1Hz、输出信号幅度大于0.3Vp-p、杂散小。

关键词:直接数字频率合成(DDS)、AD9951、AT89S52、信号发生器、频率控制字该芯片能以早期DDS 1/10的功耗提供速度高达400 MHz 的内部时钟,而合成频率高达160 MHz。

基于单片机的DDS算法的实现

基于单片机的DDS算法的实现【摘要】通常DDS信号发生器设计主要分为两类,一类是采用FPGA设计,另一类采用单片机+DDS专用芯片实现。

本文针对频率及要求较低的应用,提出一种更为简单的解决方案,即通过单片机编程完成DDS算法,从而实现信号发生器功能。

【关键词】单片机;DDS;D/A转换1.引言近年来,直接数字频率合成(DDS)信号发生器,因具有输出信号频率稳定、分辨率高、相位噪声低等优点,逐渐取代了传统的基于LC或RC振荡电路的信号发生器,成为当前信号发生器的主流。

DDS信号发生器的设计核心在于DDS算法的实现,当前主流的设计方案主要有两种:(1)采用FPGA实现DDS算法,即通过HDL语言自行设计DDS算法,产生波形数字序列,FPGA输出驱动D/A转换器,实现信号输出。

(2)采用专用DDS芯片实现,单片机只需改写DDS芯片相关寄存器,即可输出相应频率及波形的模拟信号。

整个芯片的DDS算法及D/A转换都是出厂时已设计好,无需干预。

针对一些非主流的应用,比如对输出频率和设计要求都较低时,有没有更简单的解决方案?本文将讨论如何采用单片机代替FPGA及DDS专用芯片,采用C语言编程完成DDS算法,从而实现单片机完成DDS信号发生器的简单设计方案。

2.DDS基本原理直接数字合成(Direct Digital Synthesis、DDS)是一种从相位出发的新的频率合成技术和信号产生的方法。

DDS主要由:相位累加器、正弦波形存储器(ROM)、数模转换器(D/A转换)、低通滤波器、和时钟五部分组成。

如图1所示。

图1 DDS原理框图相位累加器本质上是一个计数器。

在时钟脉冲的作用下,将频率控制字(FTW)的相位增量M累加一次。

累加器如果溢出,除溢出位外,累加器保留其它的数字位。

相位累加器输出数据作为地址,查询正弦查询表,将取出的正弦数据通过D/A转换器输出模拟信号。

模拟信号再通过一个低通滤波器输出纯净的正弦波信号[1]。

c8051单片机模拟dds信号发生器

单片机模拟dds信号发生器一、信号发生器原理信号发生器就是能够产生如正弦信号,三角波信号及锯齿波信号的装置。

在模拟电路中可以用运放、电阻和电容来搭建。

数字电路中需要DA转换。

这里主要讨论数字方式产生信号,并且以正弦信号为列来讲解。

首先,需要一个均匀采样一个正弦周期的数据,通常将这个数据表固化在ROM中,网上有这种软件,可以直接生成数据表。

然后,在程序中不断的将这个数据表中的数据顺序送出,就可以产生正弦信号。

如图1所示。

实际单片机送出的数据为红色的圆点,圆点的包络就是一个正弦信号,当然DAC输出后用低通滤波器滤波后效果会更好。

图1 信号发生器原理示意图二、简易信号发生器根据上面叙述的原理,在设计的时候用定时器给DAC送数据,那么DAC输出的数据就是一个正弦信号。

采用定时器2启动DAC0来产生信号。

定时器2初始化产生溢出时间为50us(频率为20kHz),也就是说每隔50us会向DAC写入一个数据。

由此可以计算出频率最小(当256个点都写入到DAC时,程序中变量step 为1)为1/(50us*256)=78.125Hz;最大频率(只有两个点输入DAC中,程序中变量step为127)为10Khz,但是此时输出就是一个方波信号了。

而且频率调整的时候只能是78.125Hz的倍数。

三、简易信号发生器的问题及缺陷上面简易信号发生器有很多不完善的地方:①、频率围比较小(78.125Hz~10kHz);②、频率调整只能是78.125Hz的倍数,不能实现连续调整;③、对于有按键输入的系统,不能实现任意频率信号的输出。

为了能增加频率,只能缩短定时器溢出时间,但是不能太小,要保证能大于中断函数中代码执行的时间。

为了能进一步减小频率,可以有两种方法:一是延长定时器中断溢出时间;二是在向DAC输出数据的时候,将一个数据重复写入DAC中(可以理解为步进值step为负数)。

如果采用第一种方法,那么在频率调整的时候需要调整两个参数,即步进值step和中断初值,这种方法对于精确调整频率是很难实现的,因此,我们需要调整一个参数就能实现频率的精确调整。

单片机模拟dds信号发生器

单片机模拟dds信号发生器刚开始想用单片机做个频率连续可调的信号发生器,后来就联想到了当时用FPGA做的DDS信号发生器了。

然后上网搜资料,哈哈,这个还真有人做过,大概看了一下人家的讲解,就开始干活啦!DDS信号发生器的频率计算公式如下:其中fout为输出频率,M为累加器每次的步进值,N为累加器的位数,我这里采用的是unsigned int 16位的累加器。

在FPGA系统中这个fc为系统时钟,也就是有源晶振经过分频后的频率。

但是在单片机中我们只能用单片机进中断的频率来作为fc。

fc的设置需要注意的是1、进中断的周期要大于中断程序执行的时间 2、进中断的周期也要大于DAC两次写入数据的时间。

我采用的硬件stc12c5a08s2 24m晶振 dac0832上最终效果图几个频率的测试波形10Hz频率测试正弦波方波三角波锯齿波制作经历:昨天用单片机模拟个DDS信号发生器,画了个板子。

从开始做板子就各种不顺。

打印时打印机没墨啦,地线我用的铺铜,悲催的是铺地墨太浅,没法只好拿着油性笔把地线重新描了下。

好吧,做板去,腐蚀顺利。

然后拿到板子测量电源和地没短路,开始焊接,一切顺利。

再次检测电源和地是否短路,万用表讨厌的滴滴声想起来啦。

啊苍天啊,短路啦,我焊接水平没那么差吧,一个小板子竟然焊短路啦!好吧开始检查电路,把电源线从头看到尾看不出来短路啊,好吧再看两遍,还是没短路啊。

没法开始上刀子割电源线,割了两刀短路范围缩小啦,然后就逮着那一小段电源线左看右看上看下看没短路啊,当时就有点崩溃。

然后打开pcb,就沿着这条线对电路,晕死。

问题是我描地线时把复位按键当做独立按键啦,本来接电源的线硬给画到了地上,割开不短路啦。

可是我焊接前测试啦啊,没短路啊亲,怎么突然蹦出来电路缺陷短路啊,见鬼。

上电,电源灯不亮。

赶紧拔下电源,摸摸芯片不热啊,准备好万用表,直接接在单片机的地和vcc上,上电,电压正常,怀疑电源灯电路可能断啦,一摸led焊盘直接翘起来啦,这的归功于那没墨的打印机。

基于单片机和DDS技术的信号发生器的设计

O 引言

AD 8 0相 位 寄 存 器 每 过 2 K 个 外 部 参 考 时 钟 后 返 回到 初 始 状 95

态 一 次 . 应 地 正 弦 查 询 表 每 经 过 一 个 循 环 也 回 到初 始 位 置 , 而 使 相 从 信 号 源 是 现 代 电子 系统 的 重 要 组 成 部 分 , 通 信 系 统 、 子 测 量 整个 D S 系统 输 出一 个 正 弦 波 。输 出 的正 弦 波 频 率 fu =K'c Nf 在 电 D 0t f/ , 2 c 以 及 各 种 科 学 实 验 中 , 常 需 要 一 个 高 精 度 的 频 率 可 变 信 号 源 , 且 为 外部 参 考 时 钟 频 率 ,N 3 常 并 = 2为相 位 累 加 器 位 数 , 为 频 率 控 制 字 , K 也 要 求数 字 可 控 。而 直 接 数 字 频 率 合成 技 术 以 其 能输 出 各 种 波 形 , 且 并 称 为步 进 值 。当 K I时 , 9 5 = AD 8 0输 出最 低 频 率 ( 时 也 称 为 频 率 分 辨 此 具 有 频 率 分 辨 率 高 、 变 速 度快 、 出相 位 连续 、 位 噪声 低 、 编 程 转 输 相 可 率 ) f/ 为 e2 。而 其 最 大频 率 输 出 由 N q i 采 样 定 理 决 定 , f 2 在 yus t 即 c 。 / 和 全数 字 化 、 于 集 成 等 突 出 优 点 成 为信 号 发 生 器 研 究 的 一 个 重 要 方 便 15 2 MHz的 时 钟 下 , 9 5 AD 8 0输 出 频 率 分辨 率 可 达 0 0 9 H ,输 出最 . 2 1z 向。 高 频 率 理 论 上 可 以达 到 6 .MH 。 25 z

v u n c n mi f cs l a ea d eo o cef t. e

基于DDS技术的信号发生器的设计与实现

基于DDS技术的信号发生器的设计与实现DDS(Direct Digital Synthesis,直接数字合成)技术是一种通过数字方式产生任意波形信号的技术。

DDS信号发生器是一种能够产生可控频率、幅度和相位的信号的设备。

本文将介绍基于DDS技术的信号发生器的设计与实现。

首先,信号发生器的核心部件是DDS芯片。

DDS芯片是一种集成电路,能够通过数字方式产生任意波形信号。

它包含一个相位累加器和一个查找表。

相位累加器用于生成连续的相位值,而查找表则用于根据相位值输出相应的幅度值。

通过不断更新相位累加器的数值,就可以产生连续的信号。

然后,需要一个高性能的时钟源来提供DDS芯片所需的时钟信号。

一般使用晶振来提供稳定的时钟信号。

时钟信号的频率决定了DDS芯片所能产生的最高频率。

因此,选择合适的晶振对于信号发生器的性能和稳定性至关重要。

接下来,需要设计一个控制电路来控制DDS芯片的工作模式。

控制电路可以通过按键、旋钮或者电脑串口等方式与用户进行交互。

用户可以通过控制电路设定信号的频率、幅度和相位等参数。

控制电路接收用户输入的数据,并将数据传输给DDS芯片进行处理。

在实现过程中,还需要一块数模转换器(DAC)将DDS芯片输出的数字信号转换为模拟信号。

DAC负责将DDS芯片输出的数字信号转换为与之对应的模拟信号。

数模转换的精度直接影响信号发生器的性能,因此需要选择高性能的DAC。

最后,可以通过一个显示屏显示当前信号的频率、幅度和相位等参数。

显示屏可以直接与控制电路相连,通过控制电路获取当前信号的参数,并将参数显示在屏幕上。

这样用户可以直观地了解当前信号的状态。

总结起来,基于DDS技术的信号发生器的设计与实现包括选择合适的DDS芯片、时钟源和DAC,设计控制电路和显示屏,并将各部件进行连接。

通过这些步骤可以实现一个功能完善的信号发生器,能够产生任意波形信号,并提供简单的用户界面进行参数设置和显示。

基于DDS与单片机的信号发生器的设计_毕业设计

基于DDS与单片机的信号发生器的设计选题:信号源的设计和制作(B题)摘要在信号发生器的设计中,传统的用分立元件或通用数字电路元件设计电子线路的方法设计周期长,花费大,可移植性差。

本设计是用直接数字频率合成器(DDS)。

与传统的频率合成方法相比,DDS合成信号具有频率切换时间短、频率分辨率高、相位变化连续等诸多优点。

使用单片机灵活的控制能力与液晶显示相结合,使得可以直观的控制波形的产生与调整,带来了很大的便利。

关键词:单片机,直接数字频率合成,液晶1、现有元件电源模块7805,STC89C52单片机,DDS直接式数字合成频率计,模数转换器ADC0804,1602液晶显示模块,独立按键等。

2、设计要求一、任务在给定±12V电源电压条件下,设计并制作一个正弦波信号源。

二、要求1、基本要求:(1)输出信号频率:20Hz~300kHz;(2)信号幅度:负载50Ω时,输出电压峰峰值为1~3V可调;(3)信号源输出电阻为50Ω;(4)显示信号的频率和幅度。

2、发挥部分:(1)提高信号的输出频率至1MHz;(2)提高信号的输出电压峰峰值至1~10V可调(带50Ω负载);(3)自行扩展信号源功能。

3、可以达到的效果本设计可以将输出频率调整到1~30 MHz,而由于在超高频条件下,一般运放的带宽不足以满足放大波幅的设计要求,但是我们通过负电压增加电流的方式,使得信号输出电压峰峰值为0.7v~2.4v可调。

本设计可以通过按键进入设置模式,左右按键移动光标,上下按键加减频率,再通过旋钮调节幅值,然后按键结束设置模式,就可以从输出口输出我们在设置模式下给定的波形。

4、硬件设计4.1、总体设计通过STC89c52给定DDS频率,短接DDS上J3口,使DDS可以输出稳定频率和幅值的波形,同时通过液晶显示出幅值与频率。

通过按键中断进入波形设置模式,可以通过按键增减与移位调整液晶屏上的频率显示,通过调整LM348设置新的幅值,在跳出波形设置模式时,DDS会按照设置好的波形参数产生一个新的波形,用以输出。

基于单片机的信号发生器设计

基于单片机的信号发生器设计一、本文概述随着现代电子技术的飞速发展,单片机因其高集成度、低成本和易于编程等特点,在信号处理和控制领域得到了广泛应用。

本文旨在探讨基于单片机的信号发生器设计,该设计在电子工程、自动化控制、信号处理等领域具有重要的应用价值。

本文将首先介绍单片机的基本概念、特点及其在信号发生器设计中的应用优势。

随后,将详细阐述信号发生器的设计原理、系统架构以及关键模块的设计方法,包括信号生成模块、放大模块、滤波模块等。

本文还将探讨单片机编程技术在信号发生器中的应用,包括程序设计、调试与优化等方面。

通过实验验证所设计信号发生器的性能,并对其在实际应用中的可行性进行评估。

本文的研究成果将为相关领域的研究人员和技术人员提供一定的理论指导和实践参考。

二、单片机概述单片机(Microcontroller Unit,MCU)是一种集成电路芯片,是将中央处理器(CPU)、随机存取存储器(RAM)、只读存储器(ROM)、输入输出(IO)端口、定时计数器以及中断系统等主要计算机功能部件集成在一块芯片上的微型计算机。

单片机以其体积小、功能强、性价比高、可靠性高、控制灵活、易于扩展等优点,被广泛应用于各种控制系统和智能化产品中。

单片机通常按照数据总线宽度、内部程序存储器容量、IO端口数量等参数进行分类。

其内部逻辑电路主要包括CPU、存储器、IO接口电路、定时计数器、中断控制逻辑等模块。

CPU是单片机的核心,负责执行指令、处理数据和进行逻辑运算存储器用于存储程序和数据IO接口电路负责单片机与外部设备的连接和通信定时计数器用于实现定时和计数功能中断控制逻辑则用于响应和处理外部中断事件。

在信号发生器设计中,单片机作为核心控制单元,负责产生和控制各种信号波形,如正弦波、方波、三角波等。

通过编程控制单片机的IO端口,可以产生不同频率、不同幅度的信号,从而实现信号发生器的功能。

同时,单片机还可以通过与其他电路模块的配合,实现信号调理、功率放大、显示输出等功能,使信号发生器具有更高的性能和更广泛的应用范围。

毕业设计(论文)-基于单片机的dds信号发生器设计[管理资料]

![毕业设计(论文)-基于单片机的dds信号发生器设计[管理资料]](https://img.taocdn.com/s3/m/ac8d8dc60b4c2e3f56276387.png)

前言频率源在现代电子系统中占有十分重要的地位 ,通信、雷达、制导等电子系统功能的实现及性能指标的好坏都直接依赖于频率源的性能。

频率源的性能是伴随着频率合成技术的进步而发展的 ,频率合成技术主要有直接合成、锁相频率合成直接数字合成(DDS)三种方式。

DDS的概念首先由美国学者J .Tierney 等人提出 ,它不同于前两种频率合成方法。

它是把一系列数字量形式的信号通过 DAC 转换成模拟信号的合成技术。

与其他频率合成方法相比 ,DDS 具有频率转换时间极短、频率分辨率高、输出相位连续、可编程、全数字化易于集成等突出优点。

因此 ,它得到越来越广泛的应用 ,成为现代频率合成技术中的佼佼者。

本文通过STM32来实现对DDS芯片AD9852控制,来产生10 MHz 频率内的正弦信号、调幅信号、调频信号、ASK及 PSK信号。

并通过使用AD8370及AD811来实现对幅度的控制。

第1章绪论在工业自动化系统中,经常要用一些信号作为测量基准信号或输出信号。

随着科学技术的发展,现代电子测量对信号源频率准确度和稳定度的要求越来越高。

例如在无线电通信系统中,蜂窝通信频段在912MHz并以30kHz步进。

为此,信号频率稳定度的要求必须优于10−6。

作为电子系统必不可少的信号源,在很大程度上决定了系统的性能,因而常称之为电子系统的“心脏”。

传统的信号源采用振荡器,只能产生少数几种波形,自动化程度较低,且仪器体积大,灵活性与准确度差。

而现在要求信号源能产生波形的种类多、频率高,而且还要体积小、可靠性高、操作灵活、使用方便及可由计算机控制。

为此可采用直接数字频率合成( Direct Digital Synthesis ,简称DDS)技术,把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。

采用这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形。

频率合成技术的理论形成于二十世纪三十年代左右,如今已有七十多年的发展史。

基于DDS的信号发生器设计

基于DDS的信号发生器设计基于DDS(Direct Digital Synthesis,直接数字合成)的信号发生器是一种数字技术信号发生器,利用计算机和高速数字转换器(DAC)以及DDS芯片来合成各种频率和幅度的信号。

DDS信号发生器具有频率精度高、频率调谐范围宽、频率稳定性好、相位噪声低等优点,被广泛应用于通信、电子测试、音频设备等领域。

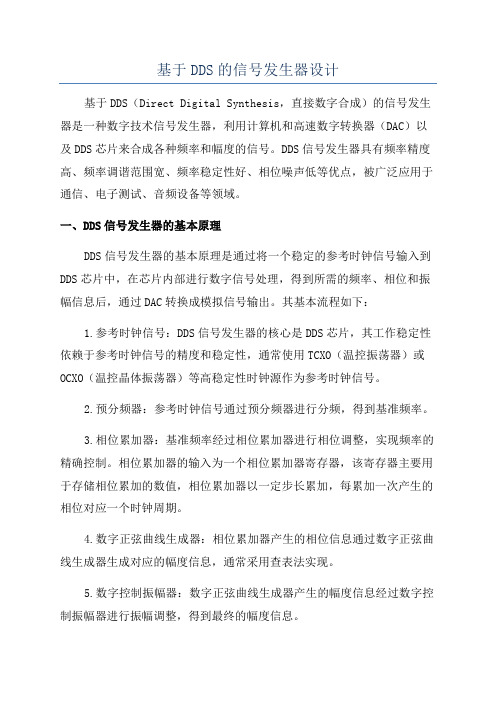

一、DDS信号发生器的基本原理DDS信号发生器的基本原理是通过将一个稳定的参考时钟信号输入到DDS芯片中,在芯片内部进行数字信号处理,得到所需的频率、相位和振幅信息后,通过DAC转换成模拟信号输出。

其基本流程如下:1.参考时钟信号:DDS信号发生器的核心是DDS芯片,其工作稳定性依赖于参考时钟信号的精度和稳定性,通常使用TCXO(温控振荡器)或OCXO(温控晶体振荡器)等高稳定性时钟源作为参考时钟信号。

2.预分频器:参考时钟信号通过预分频器进行分频,得到基准频率。

3.相位累加器:基准频率经过相位累加器进行相位调整,实现频率的精确控制。

相位累加器的输入为一个相位累加器寄存器,该寄存器主要用于存储相位累加的数值,相位累加器以一定步长累加,每累加一次产生的相位对应一个时钟周期。

4.数字正弦曲线生成器:相位累加器产生的相位信息通过数字正弦曲线生成器生成对应的幅度信息,通常采用查表法实现。

5.数字控制振幅器:数字正弦曲线生成器产生的幅度信息经过数字控制振幅器进行振幅调整,得到最终的幅度信息。

6.高速DAC:数字振幅信息通过高速DAC转换成模拟信号输出,DAC 的速度和分辨率决定了信号发生器的输出品质。

7.滤波器:由于DAC输出是离散的,需要通过滤波器对其进行滤波,以去除高频成分和伪像,得到平滑的连续信号。

二、基于DDS的信号发生器设计思路在设计基于DDS的信号发生器时,需要考虑以下几个关键问题:1.DDS芯片选择:选择合适的DDS芯片作为信号发生器的核心,要考虑芯片的性能、频率范围、精度等因素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

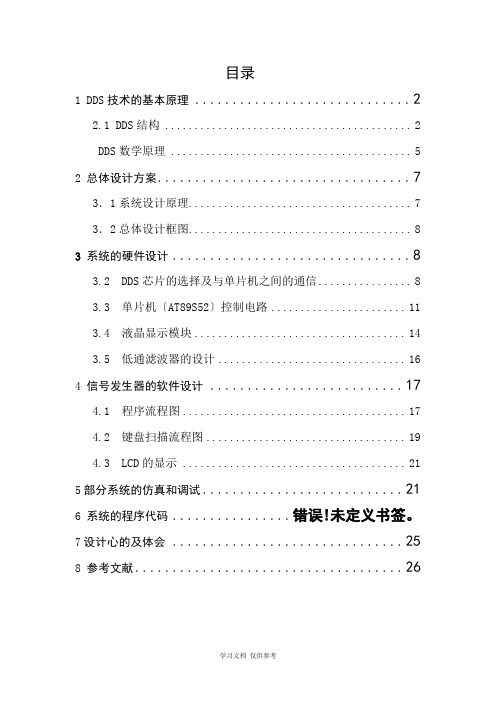

目录1 DDS技术的基本原理 (2)2.1 DDS结构 (2)2.2 DDS数学原理 (5)2 总体设计方案 (7)3.1系统设计原理 (7)3.2总体设计框图 (8)3系统的硬件设计 (8)3.2 DDS芯片的选择及与单片机之间的通信 (8)3.3 单片机(AT89S52)控制电路 (11)3.4 液晶显示模块 (14)3.5 低通滤波器的设计 (16)4 信号发生器的软件设计 (17)4.1 程序流程图 (17)4.2 键盘扫描流程图 (19)4.3 LCD的显示 (21)5部分系统的仿真和调试 (21)6 系统的程序代码................ 错误!未定义书签。

7设计心的及体会 . (25)8 参考文献 (26)1 DDS技术的基本原理2.1 DDS结构1971年,美国学者J.Tierney等人撰写的“A Digital Frequency Synthesizer”-文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新组成原理。

限于当时的技术和器件产,它的性能指标尚不能与已有的技术相比,故没受到重视。

近几年间,随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的佼佼者。

具体体现在相对带宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

直接数字频率合成器(Direct Digital Synthesizer)是从相位概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器(LPF)构成。

DDS的原理框图如下所示:图2.1 DDS原理框图其中K为频率控制字、P为相位控制字、W为波形控制字、fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。

相位累加器在时钟fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P、波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM 输出D位的幅度码S(n)经D/A转换器变成阶梯波S(t),再经过低通滤波器平滑后就可以得到合成的信号波形。

合成的信号波形形状取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。

这里我们用DDS实现正弦波的合成作为说明介绍。

2.1.1 频率预置与调节电路K被称为频率控制字,也叫相位增量。

DDS方程为:f0=f CLK/2n,f0为输出频率,fc为时钟频率。

当K=1时,DDS输出最低频率(也即频率分辨率),为fc/2n,而DDS的最大输出频率由Nyquist采样定理决定,即fc/2,也就是说K的最大值为2N-1。

因此,只要N足够大,DDS可以得到很细的频率间隔。

要改变DDS 的输出频率,只要改变控制字K即可。

2.1.2累加器图2.2 累加器框图相位累加器由N位加法器与N位寄存器级联构成。

每来一个时钟脉冲fc,加法器将频率控制字K与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。

寄存器将加法器在上一个时钟作用下继续与频率控制字进行相加。

这样,相位累加器在时钟的作用下,进行相位累加。

当相位累加器累加满时就会产生一次溢出,完成一个周期性的动作。

2.2.3 控制相位的加法器通过改变相位控制字P可以控制输出信号的相位参数。

令相位加法器的字长为N,当相位控制字由0跃变到P(P≠0)时,波形存储器的输入为相位累加器的输出与相位控制字P之和,因而其输出的幅度编码相位会增加P/2N,从而使最后输出的信号产生相移。

2.2.4 控制波形的加法器通过改变波形控制字W可以控制输出信号的波形。

由于波形存储器中的不同波形是分块存储的,所以当波形控制字改变时,波形存储器的输入为改变相位后的地址与波形控制字W(波形地址)之和,从而使最后输出的信号产和相移。

2.2.5 波形存储器用相位累加器输出的数据作为波形存储器的取样地址,进行波形的相位一幅值转换,即可在给定的时间上确定输出的波形的抽样幅值。

N位的寻址ROM相当于把0°~360°的正弦信号离散成具有2N个采样值的序列,若波形ROM有D位数据位,则2N个样值的幅值D位二进制数值固化在ROM中,按照地址的不同可以输出相应相位的正弦信号的幅值。

相位—幅度变换原理图如下图所示:图2.3 相位—幅度变换原理图2.2.6 D/A 转换器D/A 转换器的作用是把合成的正弦波数字量转换成模拟量。

正弦幅度量化序列S (n)经D/A 转换后变成了包络为正弦波的阶梯波S (t)。

需要注意的是,频率合成器对D/A 转换器的分辨率有一定的要求,D/A 转换器的分辨率越高,合成的正弦波S (t)台阶数就越多,输出的波形的精度也就越高。

2.2.7 低通滤波器对D/A 输出的阶梯波S (t)进行频谱分析,可知S (t)中除主频f o 外,还存在分布在fc,2fc 等等的两边±f o 处的非谐波分量,幅值包络为辛格函数。

因此,为了取出主频f 0,必须在D/A 转换器的输出端接入截止频率为fc/2的低通滤波器。

2.2 DDS 数学原理设有一频率为f 的余弦信号)(t S :)2cos()(ft S t π= 现在以采样频率c f 对)(t S 进行采样,得到的离散序列为:)2cos()(c n fnT S π= 2,1,0=n 其中cc f T 1=为采样周期。

对应的相位序列为c n fnT πφ2)(= ,2,1,0=n从上式可以看出相位序列呈线性,即相邻的样值之间的相位增量是一个常数,而且这个常数仅与信号的频率f 有关,相位增量为:c n fT π2)(=∆Φ因为信号频率f 与采样频率c f 之间有以下关系:M K f f c = 其中K 与M 为两个正整数,所以相位的增量也可以完成:MK n πφ2)(=∆ 由上式可知,若将π2的相位均匀的分为M 等份,那么频率为M K f π2=的余弦信号以频率c f 采样后,它的量化序列的样品之间的量化相位增量为一个不变值K 。

根据上述原理可以构造一个不变量K 为量化相位增量的量化序列:nK n =)(φ 2,1,0=n然后完成从)(n φ到另一个序列)(n S 的映射,由)(n φ构造序列: )2cos(2cos )(2cos )(c fnT KnK M n n S πππφ=== 公式(2—1) 公式(2-1)是连续信号)(t S 经采样频率为c f 采样后的离散时间序列,根据采样定理,当21<=M K f f c 时,)(n S 经过低通滤波器平滑后,可唯一恢复出)(t S 。

可见,通过上述变换不变量K 将唯一的确定一个单频率模拟余弦信号)(t S : M t Kf t S c π2cos)(= 该信号的频率为: MKf f c =0 公式(2—2) 公式(2—2)就是直接数字频率合成(DDS )的方程式,在实际的DDS 中,一般取N M 2=,于是DDS 方程就可以写成:N cKf f 20= 公式(2—3) 根据公式(2—3)可知,要得到不同的频率只要通过改变K 的具体数值就可以了,而且还可以得到DDS 的最小频率分辨率(最小频率间隔)为当1=K 时的输出频率:N c res f f 2=可见当参考频率c f 始终一定是,其分辨率由相位累加器的位数N 决定,若取MHz f c 100=,32=N ,则Hz f res 024.0=,即分辨率可以达到Hz 024.0,这也是最低的合成频率,输出频率的高精度DDS 的一大优点。

由奈奎斯特准则可知,允许输出的最高频率2max c o f f =,即12-≤N K ,但实际上在应用中受到低通滤波器的限制,通常2max c o f f <,以便于滤波镜像频率,一般: c o f f ⨯=%40max由此可见DDS 的工作频率带较宽,可以合成从直流到c f 4.0的频率信号,同时它的输出相位连续,频率稳定度高。

2 总体设计方案3.1系统设计原理本文提出的采用DDS 作为信号发生核心器件的全数控函数信号发生器设计方案, 根据输出信号波形类型可设置、输出信号幅度和频率可数控、输出频率宽等要求,选用了美国A/D 公司的AD9850 芯片,并通过单片机程序控制和处理AD9850的32位频率控制字,再经放大后加至以数字电位器为核心的数字衰减网络,从而实现了信号幅度、频率、类型以及输出等选项的全数字控制。

本系统主要由单片机、DDS直接频率信号合成器、数字衰减电路、真有效值转换模块、A/D转换模块、数字积分选择电路等部分组成。

单片机AT89S52是整个系统关键部分,通过对键盘进行扫描读入相位信息,经转换后输出到芯片AD9850,输出波形。

键盘输入的数字信息经AT89S52控制的LCD1602显示3.2总体设计框图系统构成如下图3.1所示。

图3.1 系统框图3系统的硬件设计因为本课题的功能电路与相关部件较多,为了便于研制期间的调试与最终成品的产业化,所以系统的最后实现采用了模块化的思想,即先把各个相关的电路与部件做成相互独立的分离模块,而系统的功能则是通过各模块间的级联来完成的。

下面将分别叙述各功能模块及其中所用到的器件、电路以及在系统设计、调试过程中应该注意的问题。

3.2 DDS芯片的选择及与单片机之间的通信信号的产生与控制部分电路由DDS片AD9851与单片机AT89S52组成,用户通过键盘输入的信号要求被AT89S52接收,并经其处理后将计算出的控制字传送给AD9851,由AD9851产生频率幅度可控的信号。

下面以AD9851芯片为中心加以讨论。

3.2.1 DDS芯片选择及引脚图本系统采用了美国模拟器件公司生产的高集成度产品 AD9851 芯片。

AD9851 是在 AD9850 的基础上,做了一些改进以后生成的具有新功能的 DDS 芯片。

AD9851 相对于 AD9850 的内部结构,只是多了一个 6 倍参考时钟倍乘器,当系统时钟为 180MHz 时,在参考时钟输入端,只需输入 30MHz 的参考时钟即可。

AD9851 是由数据输入寄存器、频率/相位寄存器、具有 6 倍参考时钟倍乘器的DDS 芯片、10位的模/数转换器、内部高速比较器这几个部分组成。