基于DSP的视频编解码系统设计

基于DSP的视频编解码器的控制

0机械 与电子o

21 0 0年

第1 7期

基于 D P的视频编解码器的控制 S

张廷 华 唐 黎 明 ( 中国人 民解 放军装 备指挥 技 术学 院光 电装备 系 中国 北京 1 1 1 ) 0 4 6

【 摘 要 】 以TMS 2C6 1 3 0 4 6为核心, 实现视频 图像的 实时采集与处理 。利 用DS P的 G I 口模拟 IC总线 实现对视 频编解码器的寄存 器 PO 2

控 制 。 系统 具 有 结 构 简 单 、 置 灵活 、 配 实时 性 高 、 用性 强 的优 点 。 通

【 关键词 】AA 1 5S AT0 ; P S 7 1 ;A 1 5DS

很 多 应 用 场 合 要求 所 设 计 的 图像 处 理 系 统 必 须 能 够 满 足 图像 处 理 中大 数 据 量 、 复杂 运 算 、 时 性 强 、 传输 率 、 定 可 靠 等 要 求 。 性 实 高 稳 高 能 D P的发 展 为 实 时 的 图像 处 理 提 供 了一 个 解 决 方法 。 S 高 速 D P不 仅 可 以满 足 在 运 算 性 能 方 面 的需 要 .而且 由于 D P S S 的可编程性 , 可以在硬件配置上获得 系统设计 的极大灵活性 。视频 还 采 集 与 显示 功 能是 图像 处 理 系 统 的关 键 技 术 , 由于 专 用 的视 频 编 码 芯 片 工 作 频 率 比 较 高 , 输 出 模 式 可 选 择 , 设 计 中 采 用 视 频 解 码 器

且 配 置灵 活 。

1 硬 件 系统 设计

图 2 视 频 解码 器 的原 理 图

视 频 编 解 码 芯 片 S A 15和 S A 1 E 的 工 作 运 行 通 过 主 控 芯 A 71 A 70 5 根 据 目前 算 法 的运 算 复 杂 度 和 器 件 水 平 , 于 F G 基 P A和 D P设 计 S 2 S PO模 拟 1C 总线 对 视 2 的 图像 处 理 系 统 , 统结 构框 图如 图 1 系 。系 统 的 构 成 主要 包 括 : 频 采 片 的 IC 总线 配 置 寄 存 器来 完 成 。D P通 过 G I 视 GI 集与显示、 视频 预 处理 、 频 图 像 处 理 、 频 图 像 缓 存 与 存 储 等 模 块 。 频 编 解 码 芯 片 的寄 存 器 进 行 初 始 化 。通 用 目的 输 入 输 出 外 设 ( PO) 视 视 可 当配 置 为 输 出 时 . 以 可 D P是 整 个 图像 处 理 系 统 的 核 心 , 采 集 到 的 信 号 进 行 处 理 、 缩 等 提 供 了 通 用 目的 引脚 . 以配 置 位 输 入 或 输 出 。 S 对 压 当配 置 为 输 人 过程 都 由 D P编 程 实 现 。 D P可 对 视 频 采 样所 得 数据 进 行 实 时 处 理 。 通 过 写 一 个 内 部 寄存 器 以控 制 输 出 引 脚上 驱 动 的状 态 ; S S 可 由 于 实 时 性 的 要 求 , 选 用 , 公 司 的 D P 处 理 器 T 3 0 6 1 。 引 脚 时 , 通 过读 内部 寄 存 器 的 状 态检 测 到输 入 的状 态 。 因此 可 以利 n S MS 2 C 4 6 2 C coeI F G 是 基 于 9 n 工 艺 推 出 的 低 成 本 高 性 能 的 F G 其 用 GH0模 拟 IC总 线 实 现 对 视 频 编解 码 器 的控 制 。 视 频编 解 码 芯 片 yln P A I 0m P A. D C S P0 内部 的 R AM可以实现图像数据的缓存 , 内嵌的硬的 D P模块使其 具 的 串行 数 据 输 入 端 S A 和 串行 时 钟 S K 和 D P的 G 1 连 接 在 一 S 其 0K i 。 有 一 定 的 信 号 处理 能 力 ,可 以 实 现 图像 的预 处 理 。 除 了上 述 特 点 外 , 起 。 读 写数 据速 率 可 以 达 到 4 0 b ̄s 应 用 8位 子 地 址 自动 增 加 的 功 能 , 了 只读 位 外 所 有 的 寄存 器 可写 可 读 。每 一 个 器 件 都 有 专 门 的 除 C coeI F G yl I P A还 具 有 高 速 存储 器 接 口和 高 速 差 分 接 口 , 便 与 D P n 方 S 辅助地址 , 时为了区别输入( 入) 同 写 和输 出( 出)在其 辅 助 地 址 上 也 读 , 的高 速 互 联 。

基于多DSP的MPEG-2高速视频压缩系统设计与实现

( I 6 1 ) h esedo u ei a eu 5fs(2 5 6ge iue . T 4 6 .T pe f r s ncnb pt 7 C o d g o p 70× 7 rypc r) t

Ke r y wo ds: MPEG一 2; DSP;c c p i z to a he o tmiain

比 MP G 1 E 一 清晰度更 高的动态图像 。除 了作 为 D D的指定 标 V 准外 , E 一 可用 于为数字有线 电视 分配 、 过 A M 的网 MP G 2还 通 T

读取 D P板上 压缩 后的数据存人硬盘 。 S

式, 通过 C C 的 J P I 4总线 ( : 注 J 4在 C C 协议 中是可 以 自定 义 PI

A b tac : T s p pe s rbe t e i n a d i e n ain o g — p e PEG一 o e y t m n d ti. T i y tm sr t hi a rde c i d he d sg n mplme tto fa hih s e d M 2 c d e s se i e al h s s se c ul p u ev d o sg a n fr a fc m ea ln rPAL,a d e c dei nt P o d ca t r i e i n li o m to a r ik o n n o ti o M EG一 i o sr a i e —i t Ps 2 vde te m n r a tme wih 4 DS l

维普资讯

第2 4卷 第 8期

20 年 8月 07

计 算 机 应 用 研 究

Ap l ai n Re e r h o o u e s p i t s a c fC mp t r c o

基于DSP和FPGA的视频采集实时处理系统设计

后 经过 图像处 理模 块 进 行 处理 , 处 理 后 的 数据 通 将

作者简介 : 常奇峰 (9 4 ) 男, 18 一 , 河南省周 口市人 , 南京航 空航 天大学硕 士研 究生, 主要研 究方向为数 字图像 处理.

郑 州 轻 工 业 学 院 学 报 (自 然 科 学 版 )

本文 拟 以 T 公 司 的 T 30 6 1 核 心 , I MS2 C 73为 结

合大 规 模 逻 辑 器 件 F G , 及 视 频 采 集 芯 片 PA 以

S A A 7 11 1A设计 实时 f 的视频 采集处 理 系统. 生好

1 系统原理及硬件结构设计

系统原 理框 图如 图 1 所示 .

21 00拄

过双 口送 给 D\ A进行 转换 , 将数 字信 号 转换 为模 拟 信号 , 送往 显示器 显示 .

工作时 , 一块 缓存用 于存放 当前采集 到 的图像数 据, 另一块用 于保存前一 帧数 据, 实现 了高速采集 的数据存储 与读取并行 , 简化 了系统设计 , 提高 了 系统的可靠性.

的效率降低 , 响应 速度 变差. 但是采 用可编程逻辑

器件设计 视 频 采 集 处 理 系统 , 有 开 发 周 期 短 , 具 功 耗 低 , 作频率 高 , 工 编程 配置灵 活等一 系列 优点 .

收 稿 日期 :0 9—1 2 20 2— 6

该系统首先对 由 C D摄像头输出的模拟视频 C

性能实 , 明该系统可以完成常用算法的实时处理. 证

关键 词 : 视频 采 集 ;P A; F G 图像 处理 中 图分 类号 :P 7 . T 242 文 献标 志码 : A

一种基于DSP的实时视频跟踪系统设计

耗低 ( O  ̄O mW) 。 川

DP S 芯片 T 30 C 3 I MS2V 3 的 / O工作电压是 3 , .y 其它模块 3

工作电压为 5 视频解码 T P15 V 54 数字部分也为 3 V , . )通过 3 该款 D P S 将浮点运算与定点运算结合起来, 具有更高的运 仔细查看各芯片资料的电气性能说明 , 可知各芯片接1电路 电 : 3 算精度和较 高的运算速度 , 性价比高 , 尤其适用于信号处理 、 图 平都兼容于 3 V, L电 褂 可直接与 T 30 C 3 . I 3 1 隹, MS2V 3 相联 。

1T 3 0 C 3的特点 MS 2 V 3

T 30 3 MS 2 VC 3是 T 推 出的 3 位 高性能浮点 D P中最新 I 2 S 的一款数字信号处理器 。 指令周期分 1 n 和 1 n 两种 , 3s 7s 单周期

完成 3 位整数 、( 2 4 位浮点乘法运算 ,S 工作在 7MH 主频 ) DP 5 z

维普资讯

・9 ・

Co u e a No 4 2 0 mp tr Er . 0 6

一

种基于 D P的实时视频跟踪 系统设计 S

-

刘 望军 。张可 为 ,陈军根

( 湖南工程 学院电气与信息工程 系,湖南 湘潭 4 10) 111

像处理等领域 。

222 接 口 时序 匹配 设 计 ..

2 基于 T 3 0 C 3的实 时视频 跟踪 系统硬 件设计 M¥ 2 V 3

21 系统 硬 件 总体 结 构 .

()D P与视频解码芯 片接口设计 1 S

基于DSP的G.729语音编解码器设计

基于DSP的G.729语音编解码器设计作者:聂伟,何心莹,白天石来源:《现代电子技术》2011年第09期摘要:设计了基于DSP的G.729语音编解码器,并针对G.729算法标准源码代码效率低、执行时间长的不足,从算法精简、代码优化等方面进行了优化。

优化后的算法在保证了高质量语音输出的同时,提高了编码效率,实现了对语音信号的实时处理。

最后对系统性能进行了测试,结果满足设计要求。

关键词:G.729; DSP;语音编码;算法优化中图分类号:TN764-34文献标识码:A文章编号:1004-373X(2011)09-0093-04Design of G.729 Speech Codec Based on DSPNIE Wei,HE Xin-ying,BAI Tian-shi(Computer System and Communication Laboratory, Beijing University of Chemical Technology, Beijing 100029, China)Abstract: An optimized ITU-T G.729 speech codec based on DSP is designed. The algorithm and code adopted in the source code which overcame the low efficiency and long executive time on a DSP. The optimized algorithm provided a high quality of the speech output and improved the code executive efficiency, realized the real-time processing of the speech signal. The codec system performance is tested and the result satisfies the design requirements.Keywords: G.729; DSP; speech codec; algorithm optimization0 引言语音信号处理是现代通信研究的重要内容之一,语音压缩编码作为其关键技术,如今已得到了极大的发展。

教学用数字视频编解码系统的设计

图3接口内部结构 终止、响应。

sIDAT寄存器是数据发送接收移位寄存器。 sIADR寄存器是P80C3lB的从地址寄存器。 在使用中,P80C31B是一个主发送者,它不接收 数据。学生可按上述思路编写初始化程序、中断程序、 状态服务程序以及对编解码电路控制程序。 状态服务程序可分成26种,这些程序是分别对总 线的26种状态进行处理,比如。若是主发送模式的 sTART状态,则对应的服务程序就是往sIDAT中装 载要寻址器件的从地址及读写位,然后由sIO】口自 动发送。若从地址发完并且从器件响应,则又进入另外 地服务程序。 在对编解码电路编程时,可按图4所示顺序写人 控制数据。

视频 输出

图1系统框图

视频输入端口加入模拟的视频全电视信号后,经 sAA7110模数转换后,对其数字化的全电视信号进行 数字解码,分离出数字Y、Uv分量,该电路的控制接 口是只有两根线的12C总线,通过12c编程可提供8bit 的4:2:2的视频采样格式,Y、uV的数据速率为 13.5MHz,将此信号存在帧存储器pPD42880中, sAA7184在读写控制模块EPM7128的作用下.从帧 存储里按一定要求读出数字视频数据,并将其编码成 NTsc制或PAL制的复合全电视信号。

3.学位论文 杨遂军 基于FPGA的高速图像采集技术研究 2004

在现代测量和检测领域,基于图像法的自动检测系统得到了越来越广泛的应用.图像采集卡作为图像法获取信息的重要手段和基础器件,能够实现图像 信息的采集、处理和视觉功能的扩展,是图像法测量和图像信息获取系统中的关键技术单元之一.该文在对国内外图像采集和处理技术的应用现状和发展 趋势进行了系统分析的基础上,针对高速图像采集时存在的模数转换速率高、数据量大、运算复杂等问题,采用了现场可编程门阵列器件(Field Programmable Gate Array,FPGA)和数字信号处理器(Digital Signal Processor,DSP),实现了图像的高速采集和处理.具体研究内容和方法如下:首先,对 标准视频信号格式进行深入分析,设计了基于高速A/D和FPGA的图像采集卡,其中,模数转换器速率为40MSPS,FPGA的工作频率为70MHz,并针对影响高速图像 采集的若干因素,提出了改善措施和方法;其次,设计了视频放大电路和视频分离电路,对视频信号进行预处理,运用锁相环设计了同步信号发生器电路,解 决了系统的同步问题;在行、场同步信号、A/D转换器和帧存储体之间的固有逻辑关系的基础上,采用硬件描述语言编制了图像采样、存储控制程序;再次 ,选用了5000系列的低功耗数字信号处理器,设计了图像处理电路;并以图像的边缘检测为例,采用Sobel算子实现了图像的边缘检测;最后,对高速电路板的 布局和抗干扰技术进行了详尽的分析,讨论了高速电路板设计应遵循的一些基本要求;并对整个系统进行调试、实验,对硬件电路和图像处理的结果予以验 证;综上所述,该课题采用FPGA和DSP完成了高速图像采集卡的研制,对相关的图像采集技术进行了有益的探索,并为高速图像采集卡各项功能的进一步扩展 奠定了基础.

基于ADI DSP-BF533的H.264视频采集编码系统设计

2 0 年第3 08 期

中图分 类号 :N 1 T 91 文献标识码 : A 文章编 号 :09 52 20 )3— 0 1 3 10 —25 (0 80 0 0 —0

基 于 A I S —F3 D PB 53的 H. 4视频 采集编码 系统设计 D 2 6

席道 光 ,孟 利 民

( 江 工 业 大 学 信 息 工 程 学 院 ,杭 州 303 ) 浙 10 2

摘 要 :设 计 了一种 嵌 入 式H.6 2 4视 频 流 采 集 编码 传 输 系统 。方 案 基 于 A I 司的视 频 处 理 器 D公

A S-F 3 ,通 过摄 像 头采集 视频 图像 并 存 储 ,在 D P内采 用软 编 码 的方 式 对 采 集 的视 频 图像 D PB 53 S 进行 H.6 2 4压 缩处理 。通过 以太 网接 口实现 压 缩 的数据 流传 输 以太 网传输 。 关键 词 :A S—F3 ;H.6 ;远程 视频 监 控 ;以太 网 D PB 53 2 4

后的数据存 入 分数据存储或通过网络接 口发送到远程主机进行监

收稿 日期 :2o —0 2 o 7 9— 6

处理 。 随着 数字 信号 处 理 器 的高 速发 展 , 实 现 高 为

模块 ] A5 I 1 B3 、 F 3 n

l 1 系统 组 成 框 l 到 到

模 块

系统 通 过 摄 像 头 采 集 数 据 从 并 行 外 设 接 口 (P) 过 D A方 式 直 接 存 入 S R M。视 频 采 集 P I通 M DA 单元 可 以是 C SSno 或 C D摄 像 头 ( 过视 频 MO esr C 经 A D变 换 ) 当 采 集 完 一 帧 数 据 之 后 , D PB 53 / 。 A S-F3 从 S R M 中读 人 数 据 进 行 H.6 视 频 编 码 , D A 2 4 编码

基于DSP的音频信号处理系统设计

基于DSP的音频信号处理系统设计一、导言随着数字信号处理(DSP)技术的不断发展和成熟,其在音频信号处理领域的应用也越来越广泛。

基于DSP的音频信号处理系统不仅可以实现高质量的音频处理和增强,也可以满足不同应用场景下的需求,如音频通信、娱乐、音频分析等。

本文将针对基于DSP的音频信号处理系统进行设计,从系统结构、信号处理算法、硬件平台等方面进行介绍和分析。

二、系统结构设计基于DSP的音频信号处理系统的设计首先需要确定系统的结构框架。

一般来说,这个结构包括了输入模块、DSP处理模块、输出模块和控制模块。

输入模块用于接收音频信号,可以是来自麦克风、音乐播放器、电视等各种音频设备。

DSP处理模块是音频信号处理的核心部分,其中包括了各种信号处理算法和算法的实现。

输出模块用于将处理后的音频信号输出到扬声器、耳机等输出设备中,以供用户听取。

控制模块可以用来控制和调节系统参数、算法选择、音频效果等。

三、信号处理算法音频信号处理系统的设计离不开各种信号处理算法的选择和实现。

常见的音频信号处理算法包括了滤波、均衡器、混响、压缩、编码解码等。

滤波算法用于去除音频信号中的杂音和干扰,使音频信号更加清晰;均衡器算法可以调节音频信号的频谱特性,使音频输出更加平衡;混响算法用于模拟不同的音频环境和效果;压缩算法可以调节音频信号的动态范围,使音频输出更加均衡;编码解码算法用于音频信号的数字化和解码处理。

在实际应用中,根据不同场景和需求,可以选择不同的信号处理算法,并通过DSP处理模块进行实现和调节。

四、硬件平台设计在基于DSP的音频信号处理系统的设计中,硬件平台的选择和设计也是非常重要的一部分。

常见的DSP芯片有TI的TMS320系列、ADI的Blackfin系列、Freescale的i.MX系列等。

在选择DSP芯片的还需要考虑到外围设备的选择和接口设计,如ADC(模数转换器)、DAC(数模转换器)、存储器、通信接口等。

为了提高系统的性能和稳定性,还需要考虑到功耗、体积、散热等方面的问题。

基于TMDSP开发平台的实时视频编码系统设计与实现

在 h 2 3算 法实现 中, C 与运 动补偿 是最耗时 的 两 .6 D T 者的计算量几乎 占去整个系统 的 9 , o 因此本人在系统实现 中克分利用 T S MD P提供 的并行汇缩语 言对这两个模块进行 汇编化 , 让其 中非相关语句充分并行 , 太大减少了编解码的时

同 , 测试 , 经 同时 在一 块芯 片 上 进 行 QC F图 像 格 式 的 编 解 码 I

台, 实现 了一种 视 额 鳊解 码 系统 , 经过 测试 谊 系统 在 对 qi 或 囤像 阿 时煽 码 解 码 时 , 达 到 每 秒 2 上 , e f格 能 5帧 平均 码 率 能控 制 在 4 k p 咀下 , 压 缩卡 能 广迁 应 用 于 可视 电话 、 0 bs 谊 围像监 控 、 精会 议 等 多蝶 俸 应 用 中. 视 关 键 词 : 23 D T H. 6 C DS ; S N;运动 朴 偿 P PT

着 可 视 电话 的通 信 质 量 . 在 现 有 的 视 频 缩 解 码 系 统 中 , 们 一 般 采 用 三 种 方 式 来 人 实 现 压缩 算 法 . 一 是 用 纯 硬 件 方 式 来 实 现 图 像 的 编 码解 码 , 其 即 采 用 专 用 苎 片 来 完 成 , 种 方 式 实 现 的 编 解 码 系 统 实 时 性 此 好, 压缩 率 高 , 图 像 质量 也 好 , 般 能 达 到 编 码 2 且 一 5帧 / 每秽 以上 ( I QC F格 式 图 像 ) 缺 点 是 一 旦 编解 码 方 案 固 定 , 无 法 , 就

运 动 朴 偿 技 术 的结 台 . 和 h 2 1 比 , 较 高码 率 时 ,. 6 视 频 质 量稍 超 过 h .6 相 在 h 23 .

21 而在低码 率时 , 6 6, h 2 3的 图像 质量明显高 于 h 2 1 6 图像

基于DSP的网络视频传输系统设计

视 频 采 集 驱 动 采 用 F I 视 频 I 开 发 包 ,V D模 块 1 为 基 于 VD / O F I 3 1 D PBO S /I S的应用 程序 提 供 A I P 函数 。 该 模 块 以芯 片 支 持 库 C L和设 S

1 系统 的硬件设 计

后 续 处 理作 准备 。 22 X A S及参 考 框 架 R 5 . DJ F X A S ̄e rs P Al r h tn ad 是 T 针 对 T 3 0 D P D I t Xpes ' ( DS g i m Sa d r ) ot I M¥ 2 S

O 引 言

视 频通 信是 多媒 体 通 信 的 重要 组 成 部 分 , 关 键 是 要 求鞍 低 的数 其 备 驱 动 为 基 础 ,实 现 帧 图 像 的 获 取 和 显 示 。模 块 集 中 完成 了 C L中 S 据量 和 实 时性 。采 用成 熟 的 视 频编 码 算 法 可 大 大减 少 传 输 的 数据 量 , E MA、P、 Q 和 1C 四个 模 块 的配 置 和 控 制 , 现 了 V 口与 L D V I R 2 实 P 2问 进 而 降 低 对 网络 带 宽 的要 求 ; 两通 信的 实 对 性可 用 软 件 或 硬 件 方 法解 固定 周 期 的 E MA 传 输 、D D E MA 中 断 及 V P口 中 断 这 些 固 定 操 作 , 极 决 , 用 纯 软件 实 现 的系 统 虽 易 于升 级 和 移植 , 实 时 性 较 差 ; 使 但 而采 用 大 地 简 化 了编 程 工 作 。 专用 的编 解码 芯 片 虽 能保 证 实 时性 . 不 利 于算 法 升级 。而 1 司专 但 1公 模 块 使 用 时 首 先 用 F I_ ra VD eet 建 并 初 始 化 一 个 F I 通 道 , e创 VD 为 多 媒 体 应 用 而 设 计 的 芯 片 T 30 M6 2 简 称 DM 2 则 解 决 了 之 后 通 过 F I cnrl 送 控 制 命 令 到 设 备 驱 动 以配 置 相 应 的视 频 M¥ 2 D 4 ( 4 6 ) V D ot 发 o 以上 问题 . 其丰 富 的 外 围接 1 其近 乎 是 一 个 多媒 体 嵌 入 式 系 统 的单 3使 解 码 器 (V 5 5 并 启 动 视 频 帧 图 像 的 采 集 , 备 驱 动 工 作 后 , T P 10) 设 利用 芯 片硬 件平 台 , 完 全可 编 程性 又使 其 能 兼容 正 在 发 展 的 各 种 多 媒体 F D a lc 为 应 用 程序 分 配 视 频 帧 缓 冲 区 , 当应 用 程 序 处理 完成 后 , 其 Vl lo 信号 处 理 标准 , 而 构成 通 用 的 软件 平 台 。 系 统 即 和用 D 4 进 本 j M6 2并结 再 用 F I_xh ne完 成 应 用 程 序 与设 备 驱 动 问 缓 冲 区 的 交 换 以 为 VD eca g 合 T 公 司 的 X A S编 码算 法 实 现 的 网络 视频 服务 器 。 l DI

基于DSP的视频编码的优化和实现

测 ( 低 图 像 的 时 间 冗 余 度 ) 离 散 余 弦 变 换 降 和

( T) 降 低 图像 的空 间冗 余 度 ) 一体 的混 合 编 DC ( 于

码 结构 , 码过 程 如 图 1所示 。 编 从 H. 6 2 3视 频 编 码 器 的 编码 流 程 可 以看 出 .

编码 方 法 的选 择 不但 要考 虑 到压 缩 比、 噪 比 , 信 还要 考 虑 到算 法 的复 杂性 。太复 杂 的编 码算 法 可 能会 产生 较 高 的压 缩 比 , 也 会带 来 较 大 的计算 开 销 , 而 影 响通 但 从 信 的实 时性 。 由于早 期 D P芯片 速度 和 性能 的限制 以 S

K e wor y ds: . 3,e c de,TM ¥ 0 00 H 26 n o 32 C6 0,c d ptm iato o e o i z in

l 引 言

近 年来 , 多媒 体 技 术迅 猛发 展 , 人们 对 视频 编码 技

术 及 其 在 网络 中 的应 用 如 : 可视 电话 、 议 电视 、 程 会 远

维普资讯

基 于 DS 的 视 频 编 码 的 优 化 和 实 现 P

I pl m e a i n a p i i a i n o d o Enc de Ba e n DSP m e nt t o nd O t m z to f An Vi e o sd o

特性 消除 视 觉冗 余 , 动补 偿 用 以降 低 图 像 信 息 的 时 运 间冗 余 。 C 变 换 用 于 降 低 图像 信 息 的空 间冗 余 , D T 变

字 长 编码 通 过 对 出现 概 率 大 的信 息 符 号 赋予 短 码 字 , 而对 于 概率 小 的信 息符 号 赋予 长码 字 来 降低 信源 内 部 的代 码优 化 及实 现 方 法 。

基于DSP的网络安全视频监视系统的设计

目录摘要 .............................................................................................................. 错误!未定义书签。

一、设计目的 ................................................................................................ 错误!未定义书签。

二、设计要求 (2)三、设计内容 (3)3.1系统需求分析 (3)3.2系统方案设计 (3)3.3视频部分电路模块 (3)3.4音频部分电路模块 (5)3.5网络部分电路接口模块 (6)3.7存储器系统部分电路模块 (7)总结与致谢 (8)参考文献 (9)摘要嵌入式网络视频监控系统作为新一代的视频监控设备,集先进的视频压缩处理和以太网通信与一体。

通过Internet远程用户可以在任意时间、任意地点访问监控系统,进行实时视音频监控,接收报警信息,同时还可以对摄像机进行控制操作,对图像的质量进行调节。

系统以嵌入式系统技术为基础,具有高度的稳定性和可靠性,在道路交通、银行、电信、智能家居等众多领域具有广泛的应用前景。

多媒体处理器集成了通用DSP芯片的特点,具有高速的运行速度、极强的处理能力和灵活性。

同时,由于是面向多媒体应用,多媒体处理器对内核结构进行了优化,同时扩充了接口功能,添加了视频接口、音频接口、网络接口等,可以实现与视频解码芯片、音频解码芯片和以太网物理层芯片的无缝连接,整个芯片非常设和与网络视频监控系统的应用,比较有代表性的又TI公司的TMS320DM64x系列。

采用多媒体处理器进行网络视频监控系统的设计,系统外围电路简单、体积小、灵活性高,可升级性和可扩展性强,所以是一种非常好的解决方案。

系统主要功能模块包括:视频解码、视频处理、存储器系统、音频接口、网络接口几个部分的硬件设计。

基于DSP平台HEVC编解码算法研究及优化

基于DSP平台HEVC编解码算法研究及优化随着多媒体技术深入人们的日常生活,有关于高分辨率视频的存储传输需求逐渐增加,因此高清视频编解码和大数据传输问题已经成为研究的焦点。

于2013推出新一代视频编码国际标准HEVC(High Efficiency Video Coding)。

同时近年来嵌入式多核处理器和高性能计算机的高速发展为并行处理系统提供了条件。

本文首先基于DSP平台进行HEVC编解码算法研究,最终设计并实现了基于TI TMS320C6678多核硬件平台的高清实时并行解码系统。

本文首先对HEVC中的关键技术进行深入理解,同时研究多核DSP平台的性能,多级内存架构。

对HM16.0解码软件框架进行C代码改写,然后优化解码流程架构,针对CCS编译平台进行数据类型,自带实时库等代码改写。

将PC端实现的HEVC解码系统成功移植到硬件单核平台中,针对不同分辨率视频对解码各个模块进行复杂度和耗时分析。

从分析结果中决定主要结合硬件平台指令集和熵解码算法对单核解码系统进行优化。

为了达到高清实时的效果,需要将解码系统部署至多核平台。

结合HEVC原理和C6678多核特点设计多核高清解码并行方案。

完成多核中内存分配以及多核间数据传输标志位的控制。

将解码系统移植到C6678的6个核中,完成熵解码,反变换,插值重构,滤波等处理。

同时利用CACHE原理,EDMA原理进一步优化数据流,减少数据访问和传输时间,提高解码效率。

本文最终实现基于硬件多核平台的高清实时解码系统。

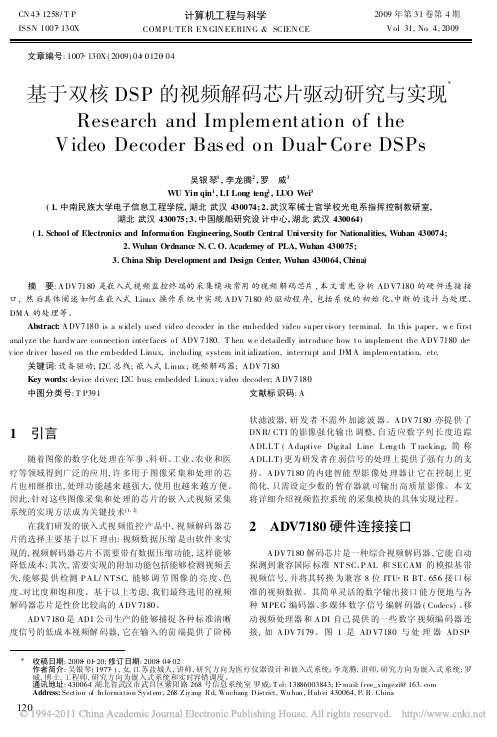

基于双核DSP的视频解码芯片驱动研究与实现

v ice dr iver based on the embedded L inux, including system init ialization, inter rupt and DM A implementatio n, etc.

关键词: 设备驱动; I2C 总线; 嵌入式 L inux ; 视频解码器; A DV 7180

在我们研发的嵌入式视 频监控 产品中, 视 频解码 器芯 片的选择主要基于以下 理由: 视频数 据压缩 是由软件 来实 现的, 视频解码器芯片不需要带有数据压缩功能, 这样能够 降低成本; 其次, 需要实现的附加功能包括能够检测视频丢 失, 能够提 供 检测 P A L/ N T SC, 能够 调 节 图像 的 亮 度、色 度、对比度和饱和度。基于以上考虑, 我们最终选用的视频 解码器芯片是性价比较高的 A DV 7180。

基于DSP的视频图象处理系统实验研究

第30卷 第2期2007年4月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.2Ap r.2007Research f or the Video Image Pr ocessing System Exper iment B a sed on DSP 3GU A N Yon g ,L U O L i 2mi n g ,L I Zhi 2p i ng ,W U Mi n 2hu a(Col lege of Inf or mat i on En gi neeri ng ,Cap it al Normal Uni versi t y ,Bei j i ng 100037,Chi na)Abstract :In t he video i mage processing syst em experi ment ,it i s cr ucial to be familiar wi t h archi tect ure of DSP and integra ted develop me nt experi ment envi ronment.In or der to hold t he met hod of vi deo image pro 2ce ssing and t echnology of DS P video i mage proce ssing ,and t he abilit y of engi neeri ng applicat io n ,education of st udent s f rom t heir different l evel s i s very i mporta nt.To fit t he st udy needs of t heir diff erent level s ,t hi s paper divides experi ment i nto four t ype s as ba sic verification t ype ,design t ype ,i nt egrated t ype and i n 2novation t ype ba sed on t he anal ysis of experi ment cont ent s and effect s.K ey w or ds :vi deo image processi ng syst em ;DSP ;int egrat ed t ype ;design type ;innovat io n type EEACC :6140C基于DSP 的视频图象处理系统实验研究3关 永,骆力明,李志平,吴敏华(首都师范大学信息工程学院,北京100037)收稿日期522基金项目北京市自然科学基金项目资助(6);北京市教委科技发展计划项目资助(K M 683);北京市高等学校5年度教育改革主项项目资助(55)作者简介关 永(662),男,博士,研究方向为智能信息处理与嵌入式系统设计,xy 6@摘 要:在DSP 视频处理系统实验中,了解DSP 的体系结构、熟悉集成开发实验环境是关键.为了掌握常用视频图象处理方法和DSP 视频图象处理技术,培养学生的工程应用能力,以实现对学生的分层次培养.本文在认真分析实验内容和实验效果的基础上,提出将实验划分为基础验证型、设计型、综合型和创新型四类,以适应不同层次学习者的需要.关键词:视频图象处理系统;DSP ;综合型;设计型;创新型中图分类号:TP391 文献标识码:A 文章编号:100529490(2007)022******* 数字信号处理器(DSP )自20世纪80年代问世以来,以其独特的哈佛结构和流水线技术以及快速实现各种数字信号处理算法的突出优点[1],在图像处理、语音合成、数字通讯、仪器仪表、医疗设备、家用电器等众多领域获得了广泛的应用[2].近几年来,DSP 技术在国内发展异常迅速,社会对这一领域人才的需求逐年增多,为适应人才市场的需求,目前,大部分的工科院校的都建设了自己的DSP 实验室,但这些实验室的主要实验内容大多都集中在通用数字信号处理方面,针对视频图象压缩编解码、图象信号识别与分析等DSP 应用较为集中的内容太少;另一方面,《数字图象处理》、《图形学》等与DSP 应用联系十分紧密的课程实验仍然在PC 机上进行[3].为了解决这些问题,提高工科学生的工程应用能力,我们进行了一些尝试与探索,针对有一定基础的信息、电子和计算机类的学生开设了基于DSP 的视频图象处理的实践课程.1 硬件平台TMS320DM642[4](以下简称DM642)是TI (美国德州仪器)公司2002年推出的高性能32位定点数字信号处理器(DSP ),工作主频最高可达720M Hz ,处理性能可达5760MIPS.它是TI 公司专为媒体处理设计的一种新型的DSP 芯片,用以实现便携式、高性能多媒体处理,如:实时MP EG 22、MP EG 24、H263、H264编码、DV R 、VOD 、DVB 、DSS:2000919:402009200100201200200007:19g 19sina.co m.等高速音视频处理系统[5].DM642采用Veloci TI 体系结构,有8个并行运算单元,采用二级缓存结构,具有64位外接存储器接口,兼容IEEE 21149.1(J TAG)边界扫描,为了面向多媒体体应用,还集成了3个可配置的视频端口、面向音频应用的McASP (Multi Channel Audio Serial Port)、10/100Mbit/s 的以太网MAC 等外设.该DSP 为548脚B G A 封装,其基本结构如图1所示.图1 TI DM642硬件组成2 实验环境一个完整的DSP 处理系统一般由DSP 及相关接口芯片、实时操作系统、应用软件组成[6].在实时操作系统和DSP 的共同支持下,DSP 处理系统能够实现大规模、高复杂度、高速数字信号处理工作.2.1 DSP DM642实验平台DSP 实验环境一般由三个部分组成:运行于PC 机端的集成开发环境CCS 、仿真器和用户的实验板或开发用的目标板[7].DM642实验系统的基本结构与连接形式如图2所示.图2 DM642实验系统的基本结构DM642实验系统硬件平台包括:DSP :TMS320DM642,720MHz SDSR M M ×6F M ×8V 路L N TS 标准模拟视频输入1路PAL/N TSC 标准模拟视频输出Audio :4路立体声输入/输出数字I/O :8入8出,用于状态和报警信号的输入/输出;UA R T :2路R S232/RS422/RS485R TC :实时时钟硬件加密:预留PCI 接口:32位、33MHz ,PC I 2.2标准以太网接口:10M/100M/s 标准以太网接口A TA 接口:直接挂接硬盘.在DSP 实验环境中,实验准备工作需要如下三个步骤:①在PC 中搭建CCS (Code Composer St udio )集成开发环境.②将仿真器、DM642实验系统、电源、音频、视频设备连接好.③经过编译调试过程后,将.out 文件装入DSP 目标板运行.2.2 集成开发环境CCSCCS 是TI 开发的一个完整的DSP 集成开发环境,也是目前使用得最为广泛的DSP 开发软件之一.CCS 代码调试器是针对标准TMS320调试接口的集成开发环境IDE ,由TI 公司在1999年推出[8].CCS 目前有CCS1.1、CCS1.2、CCS2.0、CCS2.2和CC S3.1等版本,有CCS2000(针对C2XX 系列芯片)、CCS5000(针对C54XX 、CCS55XX 系列芯片)、CCS6000(针对C6X 系列芯片)等几个不同的型号.各个不同的版本和型号之间的差别并不大.在TI 公司的网站上还可以下载免费使用期限为30d 的试用版本.CCS 提供了环境配置、源文件编辑、程序调试、跟踪和分析等工具,可以帮助用户在一个软件环境下完成编辑、编译链接、调试和数据分析等工作,支持设计和开发的整个流程,如图3所示.与TI 提供的早期软件开发工具相比,利用CCS 能够加快软件开发进程,提高工作效率.图3 使用CCS 的开发流程CCS 一般工作在两种模式下:软件仿真器和与硬件开发板相结合的在线编程前者可以脱离DS 芯片,在机上模拟DS 的指令集与工作机制,主要用于前期算法实现、调试和仿真分析后者实时运行在DS 316第2期关 永,骆力明等:基于DSP 的视频图象处理系统实验研究A :44b itlash :4bitideo :4PA /C .P PC P .P芯片上,可以在线编制和调试应用程序,如图4所示.图4 使用CCS进行在线调试3 实验内容目前,在DSP实验系统上已经验证的主要实验如表1所示,这些实验大体上可分为基本验证型实验、综合设计型实验和创新应用型实验几个层次,可以根据教学的具体需要进行组合和选择.表1 四种类型DSP实验对比分析一览表实验名称实验内容实验效果基础验证型实验实验1PAL格式图像实时采集并显示将第二通道(V1)作为视频输入,第一通道(V0)作为视频输出,视频循环显示.控制输入视频的制式及分辨率和输出视频的制式.掌握Code Compose r Studio2.2的安装和配置;了解DSP开发系统和计算机与目标系统的连接方法;了解CCS集成开发环境的操作环境和基本功能;了解视频编码的相关基本知识;熟悉视频显示程序的运行过程、控制过程,搞清数据处理、传输途径.实验2图像的反色将图像按象素进行求反,取得类似照相底片效果.熟悉视频显示程序的运行过程、控制过程,搞清数据处理、传输途径;结合实例学习如何在视频显示程序中增加图像处理算法;了解图像反色的算法和用途.实验3灰度图显示去掉色度信号(C r、C b色差信号),仅保留亮度信号Y.在视频显示任务的循环处理.结合实例学习如何在视频显示程序中增加图像处理算法;了解灰度图的概念和用途.实验4图像的阈值分割灰度的阈值变换可以将一幅灰度图像转换成黑白二值图像.按照用户指定的阈值进行处理熟悉视频显示程序的运行过程、控制过程;结合实例学习如何在视频显示程序中增加图像处理算法;理解和掌握图像的域值分割的原理和应用.实验5灰度图的线性变换将图像中所有的点的灰度按照线性灰度变换函数进行变换.该线性灰度变换函数是一个一维线性函数.理解和掌握图像的线性变换的原理和应用;结合实例学习如何在视频显示程序中增加图像处理算法.实验6灰度的窗口变换灰度的窗口变换也是一种点运算.它限定一个窗口,该窗口中灰度值保持不变;小于该下限的灰度值直接设置为0;大于该窗口上限的灰度值直接设置为255.理解和掌握图像的窗口变换的原理和应用.结合实例学习如何在视频显示程序中增加图像处理算法.实验灰度拉伸灰度拉伸可以更加灵活的控制输出灰度直方图的分布,它可以有选择的拉伸某段灰度区间以改善输出图像了解和掌握灰度拉伸的原理和应用结合实例学习如何在视频显示程序中增加图像处理算法〗416电 子 器 件第30卷7.. .实验名称实验内容实验效果基础验证型实验实验8灰度均衡灰度均衡也称直方图均衡,程序首先将视频数据从输入缓冲区读入自己开设的临时图像处理缓冲区,再在临时图像处理缓冲区上进行处理.理解和掌握灰度均衡的原理和应用.掌握在临时图像缓冲区处理图像的方法实验9图像平移分别设置图像水平和垂直平移.改变水平和垂直偏移量,观察显示.理解和掌握图像平移的方法和应用.掌握图像几何变换的处理方法.实验10图像的垂直镜像变换分别设置显示屏上的左半部分和右半部分垂直镜像变换.然后,将整个屏幕进行垂直镜像变换,观察显示结果.理解和掌握图像的水平镜像变换的方法和应用.掌握图像几何变换的处理方法.实验11图像的水平镜像变换分别设置显示屏上的左半部分和右半部分垂直镜像变换.然后,将整个屏幕进行垂直镜像变换,观察显示结果.理解和掌握图像的水平镜像变换的方法和应用.掌握图像几何变换的处理方法.实验12图像的缩放改变水平缩放比率和垂直缩放比率,观察显示效果.理解和掌握图像缩放的方法和应用.实验13图像的旋转旋转是绕坐标轴原点(0,0)进行的,如果是绕一个指定点(a,b)旋转,则先要将坐标系平移到该点,进行旋转,然后再平移回到新的坐标原点.理解和掌握图像旋转的方法和应用.设计型实验实验14CIF格式的图像采集与播放通过视频数据进行CIF算法编解码,学习会议视频格式CIF的基本协议.了解DSP/BIOS程序的结构、运行顺序和注意事项.学习使用DSP/BIOS程序设计环境.了解CIF格式的图像采集与播放.实验15图像的增强实验15.1图像的平滑(平均模板)实验15.2图像的平滑(高斯模板)实验15.3333均值滤波实验15.4333中值滤波实验15.5图像的锐化(梯度锐化)实验15.6图像的锐化(拉普拉斯锐化)了解平滑处理的算法和用途,学习利用各种模板进行图像平滑处理的程序设计方法.熟悉视频显示程序的运行过程、控制过程,搞清数据处理、传输途径.熟悉CCS集成开发环境的使用.结合实例学习如何在视频显示程序中增加图像处理算法.图像的平滑是一种实用的数字图像处理技术,主要目的是为了减少图像的噪声.一般情况下,在空间域内可以用领域平均来减少噪声;在频率域,由于噪声频谱通常多在高频段,因此可以采用各种形式的低通滤波的办法来减少噪声.实验16图像的边缘检测实验16.1边缘检测(Sobel边缘算子)实验16.2边缘检测(Prewitt边缘算子)实验16.3边缘检测(Laplacian边缘算子)实验6边缘检测(G2L边缘算子)学习边缘检测的算法和用途,学习利用Sobel算子、Pre2witt算子、Laplacia n算子、Gauss2Laplacian算子进行边缘检测的设计方法.经典的边缘提取方法是考察图像的每个象素在某个邻域内灰度的变化516第2期关 永,骆力明等:基于DSP的视频图象处理系统实验研究1.4a ussaplacian.实验名称实验内容实验效果综合型试验实验17H263编解码实验程序在目标板上实现D1格式的H.263编码和解码.程序将摄入的视频图像首先进行编码,产生H.263码流,再由解码程序处理此码流,生成目标视频送显示设备显示.了解DSP/BIOS程序的结构、运行顺序和注意事项.学习使用DSP/BIOS程序设计环境.学习使用RF25(Ref er2ence Framewor k5)设计框架构造应用程序.了解在RF25平台上调用H.263编码、解码库.实验18J P EG编解码实验程序在目标板上实现D1格式的J P EG2编码和解码.程序将摄入的视频图像首先进行编码,产生J P EG压缩图,再由解码程序处理此压缩图,生成解压缩图像送显示设备显示.学习使用DSP/B IOS程序设计环境.学习使用R F25设计框架构造应用程序.了解在R F25平台上调用J P EG编码、解码库实现可编程控制的压缩质量和帧率的视频采集、显示功能.实验19M P EG2编解码将每一帧的图像编码,然后解码输出.根据视频数据在进行M PEG2算法编解码后的运行情况观察输出结果.学习使用RF25设计框架构造应用程序.了解在R F25平台上调用MP EG22编码、解码库.了解使用XDIAS接口实现MP EG22编码、解码库的协调工作.创新型实验课程设计或课外活动设计基于模式识别的应用程序根据图形学基本原理设计相应的处理程序;学生自定义开发题目.综合理解和应用视频图象处理理论,在前面实验的基础上进行扩展,掌握独立运用DSP进行各种视频图象处理的方法与技术,将人工智能领域中的神经网络、模式识别等热点理论、手段与DSP处理技术相结合,实现软硬件协同设计与开发,提高学习者的工程应用能力. 在表1中,实验1213属于基础验证型实验,主要目的是让学生熟悉集成开发环境CCS和DSP实验系统的基本外设接口,掌握Code Composer St udio 的安装和配置,了解DSP开发系统和计算机与目标系统的连接方法,了解CCS集成开发环境的操作环境和基本功能,了解视频编码的相关基本知识,熟悉视频显示程序的运行过程、控制过程,弄清数据处理、传输途径,学习视频图象处理的基本方法;实验14216涉及到C IF格式的图像采集与播放,常用的图象平滑处理算法和用途,学习图象边缘检测算法和用途,了解利用各种模板进行图像平滑处理和边缘检测的程序设计方法,属于设计型实验;实验172 19是一些综合型实验,主要涉及到DSP/B IOS程序的结构,了解使用DSP/B IOS程序设计环境,学习使用RF25(Ref erence Framework5)设计框架构造应用程序,掌握在RF25平台上调用各种编码、解码库的开发等内容;对一些能力强的学生,可以充分调动他们的积极性和创新意识,鼓励他们自主进行实验内容设计和开发工作[9].例如我们提出的作为课程设计的几个实验,不但综合性较强,而且与实际应用结合紧密,既需要学生查阅大量相关资料,又要求学生进行硬件、软件的协同设计.安排上述实验内容时,学生可以分为项目小组,在教师的指导下,按照软件工程的原则,分工协作,从分析、设计,直至最终完成实验项目这样既有利于学生实践能力的锻炼,又可以培养他们的合作精神[]4 结束语通过上述实验课程的学习,学生对DSP处理器和集成开发环境CCS有了深刻的了解,学习了DSP 数字图象处理的基本方法,包括图像的点运算、图像的几何变换、图像的增强、图像的边缘检测、视频编解码算法等内容.培养了学生的硬件、软件协同设计技能,提高了他们的工程实践能力.参考文献:[1] 谢平,刘彬,李宇波.基于MA TL AB的数字信号处理ICA I系统[J].电化教育研究,2002,(3):33235.[2] 王友仁,姚睿,储剑波等.探索研究型课程教学模式,培养学生工程实践与科技创新能力[J].南京航空航天大学学报,2004,6(2):77280.[3] 柳春锋.数字信号处理实验软件系统的开发[J].齐齐哈尔大学学报,2002,18(3):55257.[4] Texas Inst ru m ent s(www.t i.co m).TMS320DM642DSPR e f erence Set,Vol ume1:CPU and Perip heral s.2002.[5] Texas In st rument s(www.ti.co m).TMS320DM642DSPR e f erence Set,Vol ume4:Applicat ion G ui de.2002.[6] 北京合众达电子技术有限公司.双DSP教学实验系统[M].北京:合众达电子技术有限公司.2005.[7] 彭启琮,管庆等.DSP集成开发环境-CCS及DSP/BIOS的原理与应用[M].北京:电子工业出版社.2004.[8] 尹勇,欧光军,关荣锋.DSP集成开发环境C CS开发指南[M].北京:北京航空航天大学出版社.2003.[9] 徐盛,胡剑凌,耿相铭等.面向研究生的课程设计-DSP开放式教学[J].实验室研究与探索,2004,23(2):47250.[10] 关永,王雪立,刘维民等.基于AR M的嵌入式系统实验研究[]电子器件,58(3)68263616电 子 器 件第30卷.10.J.200.2:2 2.。

基于DSP的通信电子系统设计与开发

基于DSP的通信电子系统设计与开发随着现代通信技术的不断发展,人们对通信电子系统的需求也越来越高。

作为通信电子系统的核心,数字信号处理(DSP)技术的应用越来越广泛。

本文将就基于DSP的通信电子系统设计与开发进行探讨。

一、DSP技术在通信电子系统中的应用DSP技术是数字信号处理领域的一项重要技术,可以实现数字信号的滤波、变换、编码、解码、压缩等各种操作。

在通信电子系统中,DSP技术主要应用于数字信号处理和通信调制等方面。

数字信号处理是一种将模拟信号转换为数字信号,并对数字信号进行滤波、降噪、去除干扰等处理的过程。

DSP芯片的高速运算和强大的数据处理能力可以实现对数字信号的高效处理和优化,提高通信质量和稳定性。

通信调制是一种将数字信号转换为模拟信号的过程。

DSP芯片可以通过数学运算和算法实现对数字信号的调制、解调和误码纠正等操作,将数字信号转换为可以传输的模拟信号,从而实现通信功能。

二、DSP电子系统的设计要点在设计基于DSP的通信电子系统时,需要考虑以下几个方面。

1.芯片选择首先要选择适合自己设计要求的DSP芯片。

常用的DSP芯片有TI的TMS320系列、ADI的SHARC系列、Freescale的StarCore系列等。

在选择芯片时,要考虑处理能力、功耗、芯片成本和开发环境等因素。

2.系统架构设计在系统架构设计上,要将系统模块化,并根据不同的功能要求进行分析和设计。

通信电子系统一般由前端收发模块、数字处理模块和后端存储模块组成。

在设计时,需要考虑各模块之间的数据流程和通信方式,确保系统的可靠性和高效性。

3.软件开发DSP电子系统的软件开发是整个设计过程中最为复杂的部分,也是最为关键的环节。

软件开发一般分为DSP程序和控制程序两部分。

DSP程序用于对数字信号进行处理和优化,控制程序则用于控制系统的启动、运行和关闭等过程。

4.测试与调试在系统设计完成后,需要进行测试与调试。

先进行硬件调试,检验各硬件模块的功能是否正常。

基于DSP的音频信号处理与放大系统设计(毕业设计)

基于DSP的音频信号处理与放大系统设计一、前言数字信号处理(DSP)技术在音频处理中得到了广泛的应用。

本文旨在设计一个基于DSP的音频信号处理与放大系统,实现对音频信号的处理、调节和放大。

该系统采用了TMS320C6713 DSP芯片作为核心处理器,能够实现高效率、高精度的数字信号处理。

本文将从系统设计的需求出发,分析系统架构、设计参数、算法实现和系统性能等方面进行详细阐述。

二、系统需求分析输入/输出该系统的输入为音频信号,一般来自音频采集器、CD、MP3等设备。

输出为音频放大信号,一般连接至功放、扬声器等设备。

为保证音频信号质量,系统应具有输入阻抗高、噪声低、失真小的特点。

放大输出信号应具有高保真度、低失真度、大输出功率等特点。

系统性能该系统应满足以下要求:(1)输入阻抗:> 10kΩ(2)噪声:< 0.1mV(3)失真:< 0.1%(4)输出功率:> 50W(5)频率响应:20Hz-20kHz(6)信噪比:> 90dB(7)总谐波失真:< 0.5%系统算法系统应支持以下算法:(1)音频采集(2)滤波处理(3)音量调节(4)均衡器(5)混响效果三、系统设计系统架构该系统采用了TMS320C6713 DSP芯片作为核心处理器,外围连接音频采集器、音频处理器、音频放大器等模块。

系统框图如下所示:+--------+ +--------+ +--------+|音频采集器|------->| DSP芯片|------->| 音频放大器|+--------+ +--------+ +--------+|+--------+| 音频处理器|+--------+系统参数(1)输入阻抗:系统采用运放作为输入级,输入阻抗可达到10MΩ以上。

(2)噪声:系统采用低噪声运放,噪声可控制在0.1mV以下。

(3)失真:系统采用高精度ADC/DAC芯片和高质量音频放大器,失真可控制在0.1%以下。

基于双DSP的实时高清H_264视频编码器实现(1)

1引言H.264作为新一代的视频压缩标准,编码性能远优于以往的任何标准。

在同等画质下,H.264比MPEG-2平均节约64%的传输码流,比MPEG-4平均节约39%的传输码流[1]。

但是由于H.264编码过程较为复杂,基于这一标准的实时编解码技术面临着巨大的挑战,特别是高分辨力视频更是很难做到实时处理,因此如何提高H.264编码的实时性是目前国内外学者研究的热点。

DSP芯片具有易扩展和可继承性,针对特殊应用更改也较为方便,已经被广泛应用在各种图像处理领域,在视频压缩上也得到了广泛使用。

由于高清实时视频处理计算的复杂性,多处理器架构的系统被越来越多的采用。

目前应用较为广泛的是FPGA+DSP框架的嵌入式系统结构,基于这种结构的视频压缩具有较强的处理能力,但是对开发人员有较高要求,开发人员需同时具有较高的DSP和FPGA的技能,开发周期相对较长。

针对以上问题,本文提出了一种使用2片DSP来实现H.264高清实时视频压缩的方案。

在DSP芯片选型上,本文采用了具有C64x+内核的TMS320C6455[2],不仅具备了C64内核的优势,同时由于结构上的改进,提高了处理能力,特别是对流媒体数据的处理能力有了很大的提高,且TMS320C6455内嵌的SRIO总线接口具有较高的数据传输速度,支持点对点的数据通信,使多DSP系统互联通信结构具有了高效的性能[3]。

2H.264简介H.264编码算法总体上分为网络适配层(Network Abstraction Layer,NAL)和视频编码层(Video Coding Layer,VCL)。

NAL主要是实现在不同网络应用中的数据打包。

VCL是视频处理的核心,完成对有效视频数据的描述,其结构框图[4]如图1所示。

尽管H.264和其他视频压缩标准的主要结构相似,但是由于它使用了许多特殊的数据处理方法,编码效率文章编号:1002-8692(2010)05-0033-03基于双DSP的实时高清H.264视频编码器实现*韩文俊1,2,张艳艳1,2,任国强1,吴钦章1(1.中国科学院光电技术研究所,四川成都610209;2.中国科学院研究生院,北京100039)【摘要】针对H.264标准的高清视频编码在实现时对硬件有较高要求,提出了一种使用双DSP处理的方案。

基于DSP的音频信号处理系统设计

基于DSP的音频信号处理系统设计【摘要】本文介绍了基于DSP的音频信号处理系统设计。

在文章概述了背景介绍、研究目的和研究意义。

在详细讨论了DSP在音频信号处理中的应用、音频信号处理系统设计原理、DSP系统设计流程、DSP系统硬件设计和DSP系统软件设计。

在总结了基于DSP的音频信号处理系统设计的优势,并探讨了未来研究方向。

通过本文的研究,读者可以更加深入地了解基于DSP的音频信号处理系统设计,并了解其在实际应用中的优势和未来发展方向。

【关键词】关键词:DSP、音频信号处理、系统设计、应用、原理、流程、硬件设计、软件设计、优势、未来研究方向、总结1. 引言1.1 背景介绍音频信号处理是数字信号处理领域的一个重要应用方向,随着数字信号处理技术的不断发展,其在音频领域的应用越来越广泛。

传统的音频信号处理系统往往采用模拟信号处理技术,但是由于模拟处理存在精度不足、易受干扰等问题,随着数字信号处理技术的不断改进和发展,基于DSP的音频信号处理系统逐渐成为主流。

DSP技术具有处理速度快、精度高、灵活性强等优点,能够实现复杂的音频信号处理功能,如滤波、时域变换、频谱分析等。

基于DSP的音频信号处理系统设计可以满足不同应用场景对音频处理的要求,如音乐录制、语音识别、音频增强等。

本文旨在探讨基于DSP的音频信号处理系统设计原理和流程,从硬件设计到软件设计进行详细介绍,希望能够为大家对音频信号处理技术有一个更深入的了解,并为未来的研究和应用提供一定的参考。

1.2 研究目的本文旨在通过对基于DSP的音频信号处理系统设计进行深入研究,探讨其在音频领域的应用和发展趋势。

具体来说,研究目的主要包括以下几点:1. 探究DSP在音频信号处理中的优势和特点,分析其在音频处理中的具体应用和效果。

通过深入了解DSP技术在音频信号处理中的作用,可以为音频领域的技术发展提供更深入的理解。

2. 研究音频信号处理系统设计原理,探讨DSP系统在音频处理中的工作原理和设计思路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MPEG-2 Video/H.262:MPEG2(ISO/IEC 13818-2),也被称为ITU-T H.262,是目前消费类电子视频设备中使用最广泛的视频编码标准。MPE2视频用于数字电视广播:包括地面、电缆和直接卫星广播。它能在25fps (Pal)或者30fps(NTSC)的固定帧率下达到720x576象素成像。此外,它也是DVD视频中必需的编解码器。

应用方案

特定的目标应用决定了系统要求,因而带动了系统设计的选择。

个人媒体播放器(PMP):个人媒体播放器是带大容量存储器的便携式设备,通过对存储的文件进行解码,可以观看视频、听音乐或者浏览数码照片。由于是便携式播 放器,因此功耗至关重要。既然编码和流处理功能都不需要,并且屏幕尺寸通常是比较小的QVGA或者CIF格式,其可通过基于DSP的 方案很好的解决。采用DSP的优势还在于可轻松支持多种视频和音频标准。例如:LSI针对高性能嵌入式系统的可授权DSP核ZSP500,可为此类应用提 供充足的视频处理能力。此外,ZSP500还可以提供杰出的音频解码能力,使DSP可在较低的频率下运行;从而使音频/视频子系统功耗很低。而存储器、键 盘、显示和文件系统可通过微控制器执行。

当然,某些PMP具备把播放器连接到普通电视机的视频输出功能。虽然PMP集成的显示屏幕相对较小,但现在的视频解码尺寸通常达到D1格式。依据播放器的功 能列表要求,设备需要集成1个或者多个视频解码标准;对于在电视帧率(25-30帧/秒)下D1格式视频解码,硬件视频解码器是最佳选择。多个视频解码标 准可能需要多个硬件模块。实行多个解码标准会提高系统成本,但不会提高功耗,因为同一时间只有一个模块会被激活。多标准音频解码可在小而高效的嵌入式 DSP核中实现,而无需增加额外的硬件成本(存储解码器的空间除外)。而微控制器将用于控制DSP和视频硬件解码器。

MPEG-4-SP/ASP: ISO/IEC 14496-2描述了 MPEG4简单类(Simple Profile, SP)/高级简单类(Advanced Simple Profile, ASP)。其中,SP用于下一代便携式终端和窄带互联网。而ASP增加若干工具,编码效率提高了1.5到2倍。他们两个均在市场上获得越来越多的接受

MPEG-4-AVC/ITU-T H.264:先进视频编码(AVC)是由ISO/MPEG和ITU-T联合技术委员会开发的多媒体标准。AVC提供更高的压缩率,更好的视频质量和比MPEG2更高的容错性,有望用于互联网广播和移动通讯。

Windows Media Video(WVM)/SMPTE VC-1:WMV9是微软的多媒体标准,其特性包括支持流处理,可变比特率,以及与MPEG-4-AVC/H.264相媲美的容错工具。除了用于家庭电 脑,WMV9目前也在电影院用于数字投影。电影中使用的编码可以是7~12Mbps的恒定比特率CBR或可变比特率VBR,并达到DVE解析度 (720x480)。

当仅用于播放音频时— 如典型的MP3播放器,也可使用单DSP解决方案。此系统中DSP进行音频解码、文件/流数据处理,还同时控制键盘、显示屏和存储器等。由于DSP处理音 频解码更为高效,因此使用如ZSP400 DSP而非微控制器可以显著降低功耗。此外,基于DSP的解决方案可进行软件升级,以支持运算更为密集的音频标准(比如aac Plus),此时微控制器可能无法处理额外增加的负荷。

通用视频标准和编解码器

联合视频组(Joint Video Team, JVT)由 ITU的视频编码专家组(Video Coding Experts Group, VCEG)和ISO/IEC运动图像专家组(Moving Picture Experts Group, MPEG)组成。VCEG开发自愿性标准,用于会话和非会话类音/视频应用的先进移动图像编码。 MPEG开发国际标准,用于移动图像、音频及两者组合的压 缩、编码、解压缩、处理等,以满足各种PEG-4 AVC在内的最流行的视频标准。

基于DSP的视频编解码系统设计

随着数字多媒体的应用日渐广泛,视频解码 在嵌入式系统设计中变成一个基本要素。视频标准有多种,依赖于产品可实施其中的一个或者多个标准。当然这不是全部,视频仅仅是多媒体码流的一部分,另外还 有音频或者语音需要并行处理。因此,一个精确的处理存储或数据流的同步层是必需的。此外,视频解码本身对性能要求较高,需要不同于先前基于语音和信息应用 的系统架构;这就对便携系统提出了特殊挑战,而桌面应用同样面临这些问题。