运算放大器常见参数解析

运算放大器常见指标及重要特性

运算放大器常见指标及重要特性运算放大器是一种电子放大器,用于放大微弱电信号。

它是现代电子系统中的关键组件之一,广泛应用于各种电路中,如音频放大器、通信电路、仪器仪表、运算放大电路等。

了解运算放大器的常见指标和重要特性对于正确选择和应用运算放大器至关重要。

下面是关于运算放大器常见指标和重要特性的详细介绍。

1.常见指标(1)增益:运算放大器的增益是指输入信号和输出信号之间的放大倍数。

运算放大器的增益通常用电压增益来表示,即输出电压与输入电压之比。

(2)输入阻抗:运算放大器的输入阻抗是指输入端对外界电路的负载特性,也就是输入电路对外界电路之间的阻抗。

输入阻抗越大,对外界电路的负载影响越小。

(3)输出阻抗:运算放大器的输出阻抗是指输出端对外界电路的负载特性,也就是输出电路对外界电路之间的阻抗。

输出阻抗越小,对外界电路的阻抗匹配越好。

(4)带宽:运算放大器的带宽是指在指定的增益范围内,能够传递的频率范围。

带宽越大,运算放大器能够传递的高频信号越多。

(5)零点抵消:运算放大器的零点抵消是指在输出电压为零时,输入电压不为零的情况下,输出电压的漂移量。

零点抵消越好,运算放大器的精度越高。

2.重要特性(1)运算精度:运算放大器的运算精度是指在给定的测量条件下,输出结果与实际值之间的偏差大小。

运算精度越高,运算放大器输出的信号越准确。

(2)稳定性:运算放大器的稳定性是指在不同工作条件下,输出信号的稳定程度。

稳定性越好,运算放大器的输出信号波动越小。

(3)噪声:运算放大器的噪声是指在运放输入端产生的不可避免的电压或电流波动。

噪声越小,运算放大器的信噪比越高。

(4)温度漂移:运算放大器的温度漂移是指在温度变化的情况下,输出信号的稳定程度。

温度漂移越小,运算放大器的性能越稳定。

(5)电源电压范围:运算放大器的电源电压范围是指能够正常工作的电源电压范围。

电源电压范围越大,运算放大器的适用范围越广。

(6)输入偏置电流:运算放大器的输入偏置电流是指在没有输入信号的情况下,输入端电流的大小。

运算放大器参数详解

运算放大器参数详解运算放大器(通常简称为运放)是一种广泛应用于模拟信号处理领域的电子器件。

它被广泛应用于各种不同的电子设备中,包括音频放大器、模拟电路、数字电路等。

以下是对运算放大器参数的详细解释:1. 带宽增益乘积:这是运算放大器的一个重要指标,它等于开环带宽与开环增益的乘积。

这个参数可以用来估算运放在高频应用中的性能。

2. 开环增益:开环增益是运算放大器在没有反馈的情况下,输入电压与输出电压之比。

这是一个衡量运放放大能力的参数。

3. 最大差模输入电压:这是指运放可以接受的最大差分输入电压。

超过这个电压,运放可能会被损坏。

4. 最大共模输入电压:这是指运放可以接受的最大共模输入电压。

超过这个电压,运放可能会被损坏。

5. 最大输出电压:这是指运放在安全工作范围内可以输出的最大电压。

超过这个电压,运放可能会被损坏。

6. 电源电压范围:这是指运放正常工作所需的最小和最大电源电压。

低于最小电压,运放可能无法正常工作;高于最大电压,运放可能会被损坏。

7. 功耗:这是指运放在正常工作条件下消耗的功率。

这是一个重要的环保指标,因为电子设备的功耗直接影响到其热量产生和能源消耗。

8. 输入阻抗:这是指运放在没有反馈的情况下,输入端的电阻抗。

这个参数可以影响运放在特定应用中的性能。

9. 输出阻抗:这是指运放在没有反馈的情况下,输出端的电阻抗。

这个参数可以影响运放在特定应用中的性能。

10. 带宽增益乘积与最大带宽:带宽增益乘积是指运算放大器在特定频率下达到特定增益所需的带宽,通常以Hz为单位表示。

最大带宽是指运放在不失真的情况下可以处理的最高频率信号。

这两个参数共同决定了运算放大器处理高频信号的能力。

11. 建立时间:这是指运算放大器从启动到达到最终输出值所需的时间。

这个参数对于需要快速响应的电路设计来说非常重要。

12. 失调电压:这是指运算放大器在没有输入信号的情况下,输出端的直流偏置电压。

这个参数可能会对电路的直流性能产生影响。

运算放大器15个常见指标介绍

运算放大器15个常见指标介绍在运放开环使用时,加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。

优劣范围:1µV 以下,属于极优秀的。

100µV 以下的属于较好的。

最大的有几十mV。

对策:1 选择 VOS远小于被测直流量的放大器,2 过运放的调零措施消除这个影响3 如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。

如果 IB1=IB2,那么选择 R1=R2//RF,可以使电流形成的失调电压会消失。

但实际中IB1=IB2很难满足失调电压漂移(Offset Voltage Drift)定义:当温度变化(µV/°C)、时间持续(µV/MO)、供电电压(µV/V)等自变量变化时,输入失调电压会发生变化。

后果:很严重。

因为它不能被调零端调零,即便调零完成,它还会带来新的失调。

对策:第一,就是选择高稳定性,也就是上述漂移系数较小的运放。

第二,有些运放具有自归零技术,它能不断地测量失调并在处理信号过程中把当前失调电压减掉。

输入偏置电流(Input bias current, IB)定义:当输出维持在规定的电平时,两个输入端流进电流的平均值。

Ib=(Ib1+Ib2)/2优劣范围:60fA~100µA。

后果:第一,当用放大器接成跨阻放大测量外部微小电流时,过大的输入偏置电流会分掉被测电流,使测量失准。

第二,当放大器输入端通过一个电阻接地时,这个电流将在电阻上产生不期望的输入电压。

对策:为避免输入偏置电流对放大电路的影响,最主要的措施是选择 IB较小的放大器。

输入失调电流(Input offset current, IOS)定义:当输出维持在规定的电平时,两个输入端流进电流的差值。

优劣范围:20fA~100µA。

Ib=Ib1-Ib2后果:失调电流的存在,说明两个输入端客观存在的电流有差异,无法用外部电阻实现匹配抵消偏置电流的影响。

运放 参数

运放参数运放(Operational Amplifier,简称Op Amp)是一种有着特殊符号的集成电路元件,其具有高放大增益、宽带、高输入阻抗、低输出阻抗等特点,被广泛应用于模拟电路和数字电路中。

以下是一些常用的运放参数:1. 常模增益:表示运放输出信号与输入信号共同变化的增益,常用符号为Acm。

2. 差模增益:表示运放输出信号与两输入信号差值之间的关系,常用符号为Adm。

3. 常模输入阻抗:表示运放两输入端之间对于共模信号的阻抗,常用符号为Ricm。

4. 差模输入阻抗:表示运放两输入端之间对于差模信号的阻抗,常用符号为Ridm。

5. 输出阻抗:表示运放输出端的阻抗,常用符号为Rout。

6. 带宽:表示运放能够放大信号的最高频率,常用符号为Bw(Bandwidth)。

7. 偏置电压:表示运放两输入端之间的电压差,常用符号为Vos(Offset Voltage)。

8. 共模抑制比:表示运放输出信号与共模信号的比值,常用符号为CMRR (Common Mode Rejection Ratio)。

9. 输入偏置电流:表示运放两输入端的电流偏置,常用符号为Ib(Input Bias Current)。

10. 输入偏置电流温度漂移:表示运放输入偏置电流随温度变化的比值,常用符号为Ib/T。

(其中’T’为温度变化量)。

11. 噪声:表示运放输入信号中的噪声电压,常用符号为En。

12. 失调电流:表示运放输出信号与输入信号之间的失调电流,常用符号为Ioff。

13. 失调电压:与失调电流类似,表示运放输出信号与输入信号之间的失调电压,常用符号为Voff。

以上几个参数是运放设计与选择时需要考虑的重要因素,通常应根据实际需要进行综合考虑。

运算放大器常见参数解析

运算放大器常见参数解析运算放大器是一种功率放大器,可以将输入电压放大到更大的输出电压,同时保持输入电压与输出电压之间的线性关系。

在电子设备与电路中广泛应用,例如音频放大器、通信系统等。

下面将对运算放大器的常见参数进行解析。

1.增益(Av):运算放大器的增益即输出电压与输入电压之间的比值,通常用一个数字表示。

增益越大,输出信号放大倍数就越高。

运算放大器通常有固定增益和可调增益两种类型。

2. 输入偏置电压(Vos):运算放大器的输入端有一个微小的直流偏置电压,即输入电压接近于零时实际电压。

输入偏置电压可以引起输出偏置电压,影响放大器的性能。

常见解决方法是使用一个偏置调零电路来降低输入偏置电压。

3.输入偏置电流(Ib):运算放大器的输入端也有一个微小的直流偏置电流。

输入偏置电流过大会引起伪输出电压,并对信号放大造成影响。

输入偏置电流可以通过使用PN结和电流源进行补偿。

4. 输入电阻(Rin):输入电阻是指运算放大器输入端对外部电路的等效电阻。

输入电阻越大,输入电压的损失就越小,维持输入信号的原始性。

输入电阻对应于差模模式和共模模式。

5.带宽(BW):运算放大器的带宽是指输出信号能够跟随输入信号的频率范围。

带宽越高,放大器能够处理更高频率的信号。

带宽可以通过增加放大器的带宽限制元件来提高。

6. 输出电阻(Rout):输出电阻是指运算放大器输出端对外部电路的等效电阻。

输出电阻影响着输出电压的稳定性和与外部电路的匹配性。

输出电阻越小,输出电压与负载电阻的影响就越小。

7.摆幅(Av):摆幅是指运算放大器能够提供的最大输出电压幅值。

摆幅取决于供电电源电压和运算放大器内部极限电压。

摆幅越大,放大器能够输出的电压范围就越广。

8.直流增益(Ao):直流增益是指运算放大器在输入信号频率为零时的增益。

直流增益可以决定运算放大器的静态精度,即输出电压与输入电压之间的比值。

9.共模抑制比(CMRR):共模抑制比是指运算放大器对共模信号的压制能力。

运算放大器参数说明及选型指南

运算放大器参数说明及选型指南一、运放的参数说明:1.增益:运算放大器的增益是指输出信号与输入信号之间的比值,通常用V/V表示。

增益可以是固定的,也可以是可调的。

增益决定了输出信号相对于输入信号的放大程度。

2.带宽:运算放大器的带宽是指在其增益达到-3dB时的频率范围。

带宽决定了运放的工作频率范围,对于高频应用,需要选择具有宽带宽的运放。

3.输入偏置电压:输入偏置电压是指在无输入信号时,运放输入端的直流偏置电压。

输入偏置电压可能会引入偏置误差,对于精密测量电路,需要选择输入偏置电压尽可能小的运放。

4.输入偏置电流:输入偏置电流是指在无输入信号时,运放输入端的直流偏置电流。

输入偏置电流可能会引起输入端的电平漂移,对于高精度应用,需要选择输入偏置电流尽可能小的运放。

5.输入偏置电流温漂:输入偏置电流温漂是指输入偏置电流随温度变化的比例。

输入偏置电流温漂可能会导致运放的工作点发生变化,对于温度变化较大的应用,需要选择输入偏置电流温漂较小的运放。

6.输入噪声:输入噪声是指在无输入信号时,运放输入端产生的噪声。

输入噪声可能会影响信号的纯净度,对于低噪声应用,需要选择输入噪声较低的运放。

7.输出电流:输出电流是指运放输出端提供的最大电流。

输出电流决定了运放的输出能力,在驱动负载电流较大的应用中,需要选择输出电流较大的运放。

8.输出电压:输出电压是指运放输出端能够提供的最大电压。

输出电压决定了运放的输出范围,在需要大幅度信号放大的应用中,需要选择输出电压较大的运放。

二、选型指南:1.确定应用需求:根据实际应用需求确定所需的放大倍数、带宽、输入/输出电压等参数。

例如,对于音频放大器,需要考虑音频频率范围、输出功率等因素。

2.选择性能指标:根据应用需求选择合适的性能指标。

不同应用对各个参数的要求可能会有所差异,需根据实际情况进行权衡与选择。

3.查询产品手册:查询供应商的产品手册或网站,获取相关产品的详细参数信息。

产品手册通常会提供各项参数的典型值和极限值,可以用于评估是否满足需求。

运放NE一些参数的讲解

运放NE一些参数的讲解运放NE(Nonetheless Effect)是一种常用于音频放大器中的运放类型。

它是指一种具有高增益、低噪声、低失真、宽带宽和快速响应的放大器。

NE运放常见的参数有:1. 增益(Gain):增益是指输入信号经过放大器放大后的输出信号的倍数。

NE运放通常具有高增益,一般在几十到几百倍不等。

2. 带宽(Bandwidth):带宽是指放大器能够放大的频率范围。

NE 运放的带宽通常很宽,一般在几十千赫到几百千赫之间。

3. 输入偏置电压(Input Offset Voltage):输入偏置电压是指输入端电压与输出端电压之间的差值。

NE运放的输入偏置电压很小,一般在几微伏到几毫伏之间。

4. 输入偏置电流(Input Offset Current):输入偏置电流是指输入端电流与输出端电流之间的差值。

NE运放的输入偏置电流很小,一般在几纳安到几微安之间。

5. 输入噪声电压(Input Noise Voltage):输入噪声电压是指输入端的噪声电压。

NE运放的输入噪声电压很低,一般在几微伏到几毫伏之间。

6. 输出电压摆幅(Output Voltage Swing):输出电压摆幅是指放大器能够输出的最大电压范围。

NE运放的输出电压摆幅通常较大,一般在几伏到几十伏之间。

7. 输入电阻(Input Impedance):输入电阻是指输入端对输入信号的阻抗。

NE运放的输入电阻通常很高,一般在几十千欧到几百千欧之间。

8. 输出电阻(Output Impedance):输出电阻是指输出端对负载的阻抗。

NE运放的输出电阻通常很低,一般在几欧到几十欧之间。

NE运放具有以上参数的优点,使其成为广泛应用于音频放大器、测量仪器、通信设备等领域的重要器件。

其高增益、低噪声和低失真的特性使它能够准确地放大输入信号而不引入额外的噪声和失真。

同时,其宽带宽和快速响应的特性使其能够处理宽频谱的信号,并能够快速地响应输入信号的变化。

超强总结:25个运放参数详解(收藏)

超强总结:25个运放参数详解(收藏)1、输入偏置电流和输入失调电流一般运放的datasheet中会列出众多的运放参数,有些易于理解,我们常关注,有些可能会被忽略了。

在接下来的一些主题里,将对每一个参数进行详细地说明和分析。

力求在原理和对应用的影响上把运放参数阐述清楚。

由于本人的水平有限,写的博文中难免有些疏漏,希望大家批评指正。

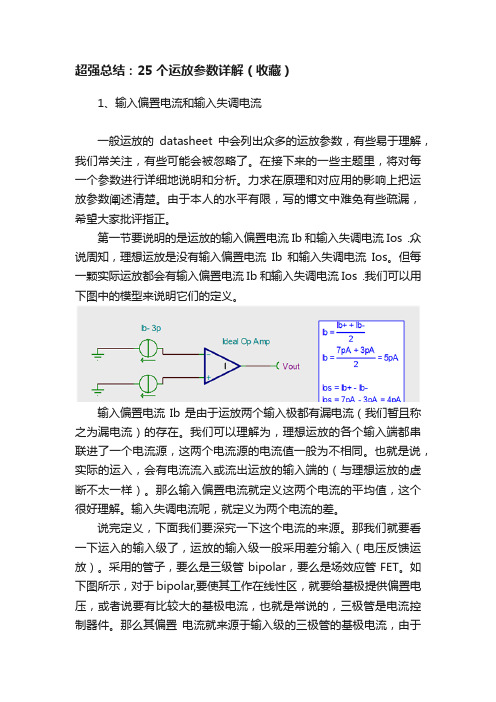

第一节要说明的是运放的输入偏置电流Ib和输入失调电流Ios .众说周知,理想运放是没有输入偏置电流Ib和输入失调电流Ios。

但每一颗实际运放都会有输入偏置电流Ib和输入失调电流Ios .我们可以用下图中的模型来说明它们的定义。

输入偏置电流Ib是由于运放两个输入极都有漏电流(我们暂且称之为漏电流)的存在。

我们可以理解为,理想运放的各个输入端都串联进了一个电流源,这两个电流源的电流值一般为不相同。

也就是说,实际的运入,会有电流流入或流出运放的输入端的(与理想运放的虚断不太一样)。

那么输入偏置电流就定义这两个电流的平均值,这个很好理解。

输入失调电流呢,就定义为两个电流的差。

说完定义,下面我们要深究一下这个电流的来源。

那我们就要看一下运入的输入级了,运放的输入级一般采用差分输入(电压反馈运放)。

采用的管子,要么是三级管bipolar,要么是场效应管FET。

如下图所示,对于bipolar,要使其工作在线性区,就要给基极提供偏置电压,或者说要有比较大的基极电流,也就是常说的,三极管是电流控制器件。

那么其偏置电流就来源于输入级的三极管的基极电流,由于工艺上很难做到两个管子的完全匹配,所以这两个管子Q1和Q2的基极电流总是有这么点差别,也就是输入的失调电流。

Bipolar输入的运放这两个值还是很可观的,也就是说是比较大的,进行电路设计时,不得不考虑的。

而对于FET输入的运放,由于其是电压控制电流器件,可以说它的栅极电流是很小很小的,一般会在fA级,但不幸的是,它的每个输入引脚都有一对ESD保护二极管。

运放参数详解超详细

运放参数详解超详细运放,全称为运算放大器,是一种主要用于电子设备中的放大电路。

它能够接收输入信号并在输出端放大,以达到放大信号的效果。

运放广泛应用于放大、滤波、积分、微分、求和、差分等电路中,是现代电子电路中不可或缺的元件之一在使用运放时,需要了解一些重要的参数,这些参数将影响到运放的性能和应用。

下面将详细介绍一些常见的运放参数:1.增益:增益指的是输入信号经过运放放大后的输出信号与输入信号之间的比例关系。

增益可以是小信号增益,即输入信号幅度相对较小的情况下的增益;也可以是大信号增益,即输入信号幅度较大的情况下的增益。

通常使用dB(分贝)来表示增益大小。

2.带宽:带宽是指运放能够正确放大的频率范围。

在带宽之外的信号将会被放大产生失真。

带宽通常以Hz(赫兹)表示,常见的运放带宽为几百kHz到几GHz。

3.输入电阻:输入电阻指的是运放输入端的电阻阻抗。

输入电阻越大,表示输入信号的损耗越小,输出信号与输入信号之间的电压差会更小。

输入电阻一般以欧姆(Ω)表示。

4.输出电阻:输出电阻指的是运放输出端的电阻阻抗。

输出电阻越小,表示运放输出信号的能力越强,能够驱动更大的负载。

输出电阻一般以欧姆(Ω)表示。

5.失调电流:失调电流是指运放输入端的两个输入电流之间的差异。

失调电流越小,表示运放的两个输入端能够更好地匹配,从而减小了对输入信号的失真。

失调电流一般以安培(A)表示。

6.偏置电压:偏置电压是指运放两个输入端相对于公共模式电压的偏差。

偏置电压越小,表示运放能够更好地接近理想运算放大器模型,减小了对输入信号的失真。

偏置电压一般以伏特(V)表示。

7.输出偏置电压:输出偏置电压是指运放输出端相对于公共模式电压的偏差。

输出偏置电压越小,表示运放输出信号更加准确,能够更好地匹配输入信号。

输出偏置电压一般以伏特(V)表示。

8.运放噪声:运放噪声是指运放输出信号中存在的由运放本身引起的随机噪声。

运放噪声分为输入噪声和输出噪声,通常以nV/√Hz(纳伏特/根赫兹)表示。

运算放大器的主要参数

02

输出参数

输出阻抗

总结词

输出阻抗是运算放大器的一个重要参数,它决定了放大器输出信号的损失程度。

详细描述

输出阻抗定义为运算放大器输出端的电阻抗,它反映了放大器对输出信号的阻碍作用。输出阻抗越大 ,信号在输出端的损失越大,信号保真度越低。因此,在选择运算放大器时,应尽量选择具有较低输 出阻抗的型号,以减小信号损失。

03

直流参数

直流增益

总结词

直流增益是运算放大器的重要参数,表示放大器对直流信号的放大能力。

详细描述

直流增益是指在直流条件下,输出电压与输入电压的比值,通常用分贝或倍数表 示。它是衡量运算放大器放大能力的重要指标,一般要求具有较高的增益值。

输入失调电压

总结词

输入失调电压是运算放大器的静态参数,表 示输入端在没有输入信号时,由于内部晶体 管的不对称性所产生的电压差。

详细描述

电源电流是衡量运算放大器功耗的重要参数,它反映了 运算放大器在正常工作状态下对电源的负载能力。较小 的电源电流意味着较低的功耗和发热,有助于提高运算 放大器的可靠性。在选择运算放大器时,应考虑其电源 电流与系统电源的负载能力相匹配。

功耗

总结词

功耗是运算放大器在工作过程中消耗的能量,通常以瓦特(W)为单位表示。

运算放大器的主要参数

目录

• 输入参数 • 输出参数 • 直流参数 • 交流参数 • 电源参数

01

输入参数

输入偏置电流

总结词

输入偏置电流是运算放大器在无输入信号时,输入端的直流 电流。

详细描述

输入偏置电流表示运算放大器在静态时,输入端的直流电流 大小。它反映了运算放大器输入级的直流状态。输入偏置电 流的大小会影响运算放大器的精度和线性度,因此在实际应 用中需要对其进行精确控制。

运算放大器常见参数解析

运算放大器常见参数解析1. 增益(Gain):运算放大器的增益是指输入信号经过放大器后的输出信号相对于输入信号的放大倍数。

增益通常以分贝(dB)为单位表示。

放大器的增益决定了输出信号的大小,所以选择适当的增益对于系统的设计非常重要。

2. 带宽(Bandwidth):运算放大器的带宽是指放大器能够处理的频率范围。

带宽通常以赫兹(Hz)为单位表示。

带宽决定了放大器能够处理的输入信号频率范围,对于高频应用来说,需要选择具有较宽带宽的放大器。

3. 偏置电流(Bias Current):运算放大器的偏置电流是指放大器输入端和输出端之间的电流,它对于放大器的性能和稳定性都十分重要。

较低的偏置电流通常可以提高放大器的性能和增益,但过低的偏置电流可能会导致放大器不稳定。

4. 偏置电压(Bias Voltage):运算放大器的偏置电压是指放大器输入端和输出端之间的电压,它对于放大器的性能和稳定性也非常重要。

与偏置电流类似,适当的偏置电压可以提高放大器的性能,但过高或过低的偏置电压都可能会导致放大器的不稳定。

5. 输入电阻(Input Impedance):运算放大器的输入电阻是指放大器输入端的阻抗,它决定了放大器输入端的电压和电流关系。

较高的输入电阻可以减少信号源和放大器之间的干扰和电流泄漏,从而提高放大器的性能。

6. 输出电阻(Output Impedance):运算放大器的输出电阻是指放大器输出端的阻抗,它决定了输出信号的负载能力。

较低的输出电阻可以提高放大器的驱动能力和信号传输质量。

通常在设计中,会选择与负载匹配的输出电阻。

7. 输入偏置电压(Input Offset Voltage):运算放大器的输入偏置电压是指放大器输入电压与基准电压之间的差值。

较小的输入偏置电压可以减少对输入信号的失真和干扰,提高放大器的性能。

8. 温度漂移(Temperature Drift):运算放大器的温度漂移是指增益和偏置随温度变化的程度。

运放参数的详细解释和分析

运放参数的详细解释和分析运放(Operational Amplifier,简称Op Amp)是一种主要用于放大和处理电信号的电子器件。

它是非常重要的集成电路之一,广泛应用于各种电子设备和系统中,如放大电路、滤波电路、模拟计算器、比较器等。

本文将详细解释并分析运放的参数。

1. 增益(Gain):增益是运放最重要的特性之一,用于描述输入信号与输出信号之间的放大比例。

它通常以电压倍数(Voltage Gain)表示,即输出电压与输入电压的比值。

增益可以是正值或负值,表示了放大器是否进行了相位反转。

增益通常以dB(分贝)为单位,即20log(Vout/Vin)。

增益可以由外部电阻和内部电路元件决定,可以通过选择合适电路参数来调整增益。

2. 输入阻抗(Input Impedance):输入阻抗是指运放输入端对外部电路的电阻。

对于传感器等输出电阻较高的装置,输入阻抗要足够大,以保持输入信号的精确度,防止干扰信号被负载吸收。

通过增加并联电阻或引入晶体管等组件可以提高输入阻抗。

3. 输出阻抗(Output Impedance):输出阻抗是指运放输出端对外部电路的电阻。

输出阻抗应尽可能小,以便输出信号能够真实地传递到负载电路。

较小的输出阻抗也能提高运放的线性性能和频率响应特性。

4. 带宽(Bandwidth):带宽表示运放能够放大的频率范围。

运放作为一个激励放大器,其输出信号随着频率的增加而衰减,当频率超出了带宽时,输出信号的幅度会显著降低,甚至无法放大。

带宽可以通过增加增益带宽积来提高。

增益带宽积是增益和带宽的乘积,其值越大表示运放能够放大更高的频率。

6. 运放的失调电流(Input Offset Current):失调电流是指两个输入端之间的电流差异。

输入端的电压差异产生失调电流,这会导致输出信号与输入信号之间存在误差。

失调电流的大小取决于运放本身的结构和设计,并可以通过外部电路进行校准。

7. 噪声(Noise):噪声是指运放输出端的不想要的信号,通常表现为随机应变,被称为随机噪声。

运算放大器的22个主要参数都在这了!

运算放大器的22个主要参数都在这了!参数一:共模输入电阻(RINCM):该参数表示运算放大器工作在线性区时,输入共模电压范围与该范围内偏置电流的变化量之比。

参数二:直流共模抑制(CMRDC):该参数用于衡量运算放大器对作用在两个输入端的相同直流信号的抑制能力。

参数三:交流共模抑制(CMRAC):CMRAC用于衡量运算放大器对作用在两个输入端的相同交流信号的抑制能力,是差模开环增益除以共模开环增益的函数。

参数四:增益带宽积(GBW):增益带宽积是一个常量,定义在开环增益随频率变化的特性曲线中以-20dB/十倍频程滚降的区域。

参数五:输入偏置电流(IB):该参数指运算放大器工作在线性区时流入输入端的平均电流。

参数六:输入偏置电流温漂(TCIB):该参数代表输入偏置电流在温度变化时产生的变化量。

TCIB通常以pA/℃为单位表示。

参数七:输入失调电流(IOS):该参数是指流入两个输入端的电流之差。

参数八:输入失调电流温漂(TCIOS):该参数代表输入失调电流在温度变化时产生的变化量。

TCIOS通常以pA/℃为单位表示。

参数九:差模输入电阻(RIN):该参数表示输入电压的变化量与相应的输入电流变化量之比,电压的变化导致电流的变化。

在一个输入端测量时,另一输入端接固定的共模电压。

参数十:输出阻抗(ZO):该参数是指运算放大器工作在线性区时,输出端的内部等效小信号阻抗。

参数十一:输出电压摆幅(VO):该参数是指输出信号不发生钳位的条件下能够达到的最大电压摆幅的峰-峰值,VO一般定义在特定的负载电阻和电源电压下。

参数十二:功耗(Pd):表示器件在给定电源电压下所消耗的静态功率,Pd通常定义在空载情况下。

参数十三:电源抑制比(PSRR):该参数用来衡量在电源电压变化时运算放大器保持其输出不变的能力,PSRR通常用电源电压变化时所导致的输入失调电压的变化量表示。

参数十四:转换速率/压摆率(SR):该参数是指输出电压的变化量与发生这个变化所需时间之比的最大值。

运算放大器的相关参数及测法

运算放大器的相关参数及测法一、运算放大器的相关参数:1.增益:运算放大器的增益是指输出信号和输入信号间的比例关系。

一般来说,增益被分为电压增益、电流增益和功率增益。

增益的计算要根据具体电路的需求和设计目标进行确定。

2.带宽:运算放大器的带宽是指其输出信号在频率上的可用范围。

在一般情况下,带宽要大于信号的最高频率才能保证较好的信号放大效果。

带宽的测量方法通常是通过输入一个特定频率的正弦波信号,对输出信号进行测量,观察输出信号的衰减情况,从而确定带宽。

3.输入偏置电流:运算放大器在正常工作情况下,输入信号为零时,输出信号应该为零。

但实际上,由于器件的不对称性和不完美性等因素,输入信号为零时,输出信号往往不为零,这就是输入偏置电流。

输入偏置电流的大小影响着运算放大器的工作稳定性和精度。

测量输入偏置电流可以通过将输入端直接接地,然后测量输出电压。

4.输入偏置电压:输入偏置电压是指运算放大器的输入端电位差,当输入信号为零时,输出信号为零需要的输入电压。

输入偏置电压的大小也会对运算放大器的工作稳定性和精度产生影响。

测量输入偏置电压可以通过将输入端短接,然后测量输出电压。

5.输入阻抗:输入阻抗是指运算放大器输入端的电阻特性,即输入端电流和电压间的比例关系。

输入阻抗的大小决定了运算放大器对输入信号的影响程度,输入阻抗越大,说明输入信号被放大器吸收的越少。

测量输入阻抗的方法可以通过接入一个标准电阻,然后测量输入端的电压和电流,计算得到。

二、运算放大器的测量方法:1.增益测量:增益可以通过输入一个特定幅值的正弦波信号,然后测量输出信号的幅值,通过两者的比值来计算增益。

可以通过示波器来观察输入和输出信号的波形,然后进行幅值测量。

2.带宽测量:带宽的测量可以通过输入不同频率的正弦波信号,然后测量输出信号的衰减程度,通过找到输出信号衰减到一半的频率,确定带宽的上限。

可以使用频谱分析仪或者示波器进行测量。

3.输入偏置电流和输入偏置电压测量:输入偏置电流的测量可以通过将输入端直接接地,然后测量输出电压来确定。

运算放大器常见参数解析

运算放大器常见参数解析运放常见参数总结1.输入阻抗和输出阻抗(Input Impedance And Output Impedance)一、输入阻抗输入阻抗是指一个电路输入端的等效阻抗。

在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗Rin就是U/I。

你可以把输入端想象成一个电阻的两端,这个电阻的阻值,就是输入阻抗。

输入阻抗跟一个普通的电抗元件没什么两样,它反映了对电流阻碍作用的大小。

对于电压驱动的电路,输入阻抗越大,则对电压源的负载就越轻,因而就越容易驱动,也不会对信号源有影响;而对于电流驱动型的电路,输入阻抗越小,则对电流源的负载就越轻。

因此,我们可以这样认为:如果是用电压源来驱动的,则输入阻抗越大越好;如果是用电流源来驱动的,则阻抗越小越好(注:只适合于低频电路,在高频电路中,还要考虑阻抗匹配问题。

另外如果要获取最大输出功率时,也要考虑阻抗匹配问题二、输出阻抗无论信号源或放大器还有电源,都有输出阻抗的问题。

输出阻抗就是一个信号源的内阻。

本来,对于一个理想的电压源(包括电源),内阻应该为0,或理想电流源的阻抗应当为无穷大。

输出阻抗在电路设计最特别需要注意但现实中的电压源,则不能做到这一点。

我们常用一个理想电压源串联一个电阻r的方式来等效一个实际的电压源。

这个跟理想电压源串联的电阻r,就是(信号源/放大器输出/电源)的内阻了。

当这个电压源给负载供电时,就会有电流I从这个负载上流过,并在这个电阻上产生I×r 的电压降。

这将导致电源输出电压的下降,从而限制了最大输出功率(关于为什么会限制最大输出功率,请看后面的“阻抗匹配”一问)。

同样的,一个理想的电流源,输出阻抗应该是无穷大,但实际的电路是不可能的三、阻抗匹配阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。

阻抗匹配分为低频和高频两种情况讨论。

我们先从直流电压源驱动一个负载入手。

由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。

运算放大器参数

运算放大器参数

运算放大器是一种电子电路元件,它可以对输入信号进行放大、滤波、求和等运算。

运算放大器的参数对于电路设计和性能优化非常重要,以下是常见的运算放大器参数:

1. 增益:运算放大器的放大倍数,一般用电压增益表示,可以通过放大器的输出电压与输入电压的比值来计算。

2. 带宽:运算放大器的频率响应范围,即在该范围内放大器能够保持稳定的放大倍数。

3. 偏置电压:运算放大器输入端需要添加一个偏置电压才能正常工作,该电压会影响放大器的输入电平范围和输出电平范围。

4. 输入阻抗:运算放大器的输入端电阻,它会影响信号输入的负载能力和信号失真。

5. 输出阻抗:运算放大器的输出端电阻,它会影响输出信号的负载能力和信号失真。

6. 偏置电流:运算放大器的输入端需要一定的偏置电流来保持稳定的工作状态,该电流会影响输入端的输入电平范围和信号失真。

7. 跨导:运算放大器的输入端电压变化与输出电流变化的比值,也称为转移电导。

它会影响运算放大器的放大倍数和带宽。

以上是常见的运算放大器参数,不同的运算放大器型号和用途需要考虑不同的参数,以满足电路设计的要求和性能优化。

- 1 -。

运算放大器常见参数解析

运放常见参数总结1.输入阻抗和输出阻抗(Input Impedance And Output Impedance)一、输入阻抗输入阻抗是指一个电路输入端的等效阻抗。

在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗Rin就是U/I。

你可以把输入端想象成一个电阻的两端,这个电阻的阻值,就是输入阻抗。

输入阻抗跟一个普通的电抗元件没什么两样,它反映了对电流阻碍作用的大小。

对于电压驱动的电路,输入阻抗越大,则对电压源的负载就越轻,因而就越容易驱动,也不会对信号源有影响;而对于电流驱动型的电路,输入阻抗越小,则对电流源的负载就越轻。

因此,我们可以这样认为:如果是用电压源来驱动的,则输入阻抗越大越好;如果是用电流源来驱动的,则阻抗越小越好(注:只适合于低频电路,在高频电路中,还要考虑阻抗匹配问题。

另外如果要获取最大输出功率时,也要考虑阻抗匹配问题二、输出阻抗无论信号源或放大器还有电源,都有输出阻抗的问题。

输出阻抗就是一个信号源的内阻。

本来,对于一个理想的电压源(包括电源),内阻应该为0,或理想电流源的阻抗应当为无穷大。

输出阻抗在电路设计最特别需要注意但现实中的电压源,则不能做到这一点。

我们常用一个理想电压源串联一个电阻r的方式来等效一个实际的电压源。

这个跟理想电压源串联的电阻r,就是(信号源/放大器输出/电源)的内阻了。

当这个电压源给负载供电时,就会有电流I从这个负载上流过,并在这个电阻上产生I×r的电压降。

这将导致电源输出电压的下降,从而限制了最大输出功率(关于为什么会限制最大输出功率,请看后面的“阻抗匹配”一问)。

同样的,一个理想的电流源,输出阻抗应该是无穷大,但实际的电路是不可能的三、阻抗匹配阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。

阻抗匹配分为低频和高频两种情况讨论。

我们先从直流电压源驱动一个负载入手。

由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。

运算放大器主要参数

运算放大器主要参数运算放大器(Operational Amplifier,简称Op-Amp)是电子电路中的一个重要部件,广泛应用于模拟电路电路中。

它具有输入阻抗高、增益大、输出阻抗低等特点,可以起到信号放大、滤波、求积分、求微分、比较等作用。

在使用运算放大器时,需要了解其主要参数,以便选择合适的运算放大器并设计出稳定可靠的电路。

下面介绍几个常见的主要参数。

1. 增益(Gain)增益是运算放大器的一个重要指标,表示运算放大器输入和输出之间的电压增值比。

具体地,电压增益为输出电压与输入电压之比。

通常用dB(分贝)表示,公式为:voltage gain = 20*log (Vout / Vin)。

增益越大,表示放大器的输出电压变化更灵敏,适合要求精度高的应用。

但是,增益不能过大,否则容易产生噪声、漂移等问题。

2. 输入阻抗(Input Impedance)输入阻抗指运算放大器对输入信号的电阻抵抗,也就是输入端电路的电阻。

输入阻抗越高,说明输入信号被放大器“欢迎”,放大器可以提供更好的输入信号放大效果。

一般而言,输入阻抗越高,保证了信号的高噪声性,但是会降低放大器的带宽。

3. 输出阻抗(Output Impedance)输出阻抗是指运算放大器的输出端对外部电路所带来的等效电阻抗。

输出阻抗越低,说明输出信号更能维持所需的电压波形,应用范围更广。

一般而言,输出阻抗越低意味着输出信号更稳定,功率损耗更小等优点。

4. 偏置电流(Bias Current)偏置电流是指运算放大器内部存在的无输入信号时流经输入端的电流。

这种电流流过时序电阻等元器件,它们产生的电压陡度呈指数增长,这种电流有可能影响放大器和被测电路的稳定性和性能。

因此,它的大小要求越小越好。

5. 限幅电流(Slew Rate)当运算放大器输出电压变化速度很快时,就会出现斜率限制(Slew Rate)现象。

限幅电流是输出电压的变化率,量纲为伏特/微秒(V/μs),表示放大器输出端电压的变化速率。

运算放大器的参数选型与应用

运算放大器的参数选型与应用一、运算放大器的参数1.基本参数:(1)增益(A):运算放大器的放大能力,通常以电压增益或电流增益表示。

(2)输入阻抗(Rin):运算放大器对输入信号源的接收能力,一般较高,以保持输入信号源的电路完整性。

(3)输出阻抗(Rout):运算放大器提供给负载的输出能力,一般较低,以最大限度地传递放大的信号。

(4)带宽(B):运算放大器能够放大信号的频率范围。

(5)共模抑制比(CMRR):运算放大器对共模信号的抑制能力。

2.典型参数:(1)输入偏置电压(Vio):运算放大器非平衡输入端的直流电压差异。

(2)输入偏置电流(Iio):运算放大器非平衡输入端的直流电流差异。

(3)输入偏置电流温漂(Iio TC):运算放大器输入偏置电流随温度变化的程度。

(4)输入失调电压(Vos):漏电流通过输出端电阻引起的电压差。

(5)输出失调电压(Vos):输出电压与期望输出电压之间的差异。

二、运算放大器的选型1.输入信号要求:根据要放大的信号类型,确定所需的运算放大器是单电源还是双电源,是直流耦合还是交流耦合。

2.增益和带宽需求:根据系统设计的需求,选择具有足够放大增益和带宽的运算放大器。

3.供电电源需求:选择适合实际供电电源范围的运算放大器。

4.共模抑制比要求:根据具体应用的共模干扰程度确定所需的共模抑制比。

5.工作温度和封装要求:根据实际工作温度和应用环境,选择适合的运算放大器封装。

三、运算放大器的应用1.模拟电路放大:2.滤波器设计:3.比较器设计:4.阻容电路设计:5.仪器放大器设计:总结:运算放大器作为一种重要的电子元件,具有广泛的应用领域。

在使用运算放大器时,需要根据具体应用的需求来选择合适的运算放大器型号,并根据参数来进行电路设计和调试。

运算放大器的应用非常灵活,可以用于模拟电路放大、滤波器设计、比较器设计、阻容电路设计和仪器放大器设计等。

运算放大器参数详解

运算放大器参数详解运算放大器是一种电子设备,用于放大电压,实现信号处理和放大。

它具有以下参数:1. 增益(Gain):增益是运算放大器输出电压与输入电压之比。

它表示运算放大器在输入信号上的放大倍数。

2. 带宽(Bandwidth):带宽是指运算放大器能够放大的频率范围。

在带宽之外的信号将被减弱或屏蔽。

3. 输入阻抗(Input Impedance):输入阻抗是运算放大器输入端的电阻。

它影响信号源与运算放大器之间的匹配。

4. 输出阻抗(Output Impedance):输出阻抗是运算放大器输出端的电阻。

它影响运算放大器输出信号的传输质量和负载匹配。

5. 输入偏置电流(Input Bias Current):输入偏置电流是指进入运算放大器输入端的电流。

它对输入信号的准确性和稳定性有影响。

6. 温度漂移(Temperature Drift):温度漂移是指运算放大器参数随温度变化的变化。

它会导致运算放大器的性能随环境温度变化而变化。

7. 共模抑制比(Common Mode Rejection Ratio,CMRR):CMRR是运算放大器对共模信号抑制的能力。

较高的CMRR意味着运算放大器对共模信号的抑制能力更强。

8. 噪声(Noise):噪声是运算放大器输出信号中的非期望信号,通常由电子器件的不完美性和环境干扰引起。

在某些应用中,噪声是一个重要的参数,需要尽量降低。

以上是一些常见的运算放大器参数,它们决定了运算放大器在特定应用中的性能。

不同的应用需要不同的参数要求,因此在选择运算放大器时,我们需要仔细考虑这些参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

运放常见参数总结1.输入阻抗和输出阻抗(Input Impedance And Output Impedance)一、输入阻抗输入阻抗是指一个电路输入端的等效阻抗。

在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗Rin就是U/I。

你可以把输入端想象成一个电阻的两端,这个电阻的阻值,就是输入阻抗。

输入阻抗跟一个普通的电抗元件没什么两样,它反映了对电流阻碍作用的大小。

对于电压驱动的电路,输入阻抗越大,则对电压源的负载就越轻,因而就越容易驱动,也不会对信号源有影响;而对于电流驱动型的电路,输入阻抗越小,则对电流源的负载就越轻。

因此,我们可以这样认为:如果是用电压源来驱动的,则输入阻抗越大越好;如果是用电流源来驱动的,则阻抗越小越好(注:只适合于低频电路,在高频电路中,还要考虑阻抗匹配问题。

另外如果要获取最大输出功率时,也要考虑 阻抗匹配问题二、输出阻抗无论信号源或放大器还有电源,都有输出阻抗的问题。

输出阻抗就是一个信号源的内阻。

本来,对于一个理想的电压源(包括电源),内阻应该为0,或理想电流源的阻抗应当为无穷大。

输出阻抗在电路设计最特别需要注意但现实中的电压源,则不能做到这一点。

我们常用一个理想电压源串联一个电阻r的方式来等效一个实际的电压源。

这个跟理想电压源串联的电阻r,就是(信号源/放大器输出/电源)的内阻了。

当这个电压源给负载供电时,就会有电流I从这个负载上流过,并在这个电阻上产生I×r 的电压降。

这将导致电源输出电压的下降,从而限制了最大输出功率(关于为什么会限制最大输出功率,请看后面的“阻抗匹配”一问)。

同样的,一个理想的电流源,输出阻抗应该是无穷大,但实际的电路是不可能的三、阻抗匹配阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。

阻抗匹配分为低频和高频两种情况讨论。

我们先从直流电压源驱动一个负载入手。

由于实际的电压源,总是有内阻的(请参看输出阻抗一问),我们可以把一个实际电压源,等效成一个理想的电压源跟一个电阻r串联的模型。

假设负载电阻为R,电源电动势为U,内阻为r,那么我们可以计算出流过电阻R的电流为:I=U/(R+r),可以看出,负载电阻R 越小,则输出电流越大。

负载R上的电压为:Uo=IR=U/[1+(r/R)],可以看出,负载电阻R越大,则输出电压Uo越高。

再来计算一下电阻R消耗的功率为:P=I2×R=[U/(R+r)]2×R=U2×R/(R2+2×R×r+r2)=U2×R/[(R-r)2+4×R×r]=U2/{[(R-r)2/R]+4×r}对于一个给定的信号源,其内阻r是固定的,而负载电阻R则是由我们来选择的。

注意式中[(R-r)2/R],当R=r时,[(R-r)2/R]可取得最小值0,这时负载电阻R上可获得最大输出功率Pmax=U2/(4×r)。

即,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一。

对于纯电阻电路,此结论同样适用于低频电路及高频电路。

当交流电路中含有容性或感性阻抗时,结论有所改变,就是需要信号源与负载阻抗的的实部相等,虚部互为相反数,这叫做共扼匹配。

在低频电路中,我们一般不考虑传输线的匹配问题,只考虑信号源跟负载之间的情况,因为低频信号的波长相对于传输线来说很长,传输线可以看成是“短线”,反射可以不考虑(可以这么理解:因为线短,即使反射回来,跟原信号还是一样的)。

从以上分析我们可以得出结论:如果我们需要输出电流大,则选择小的负载R;如果我们需要输出电压大,则选择大的负载R;如果我们需要输出功率最大,则选择跟信号源内阻匹配的电阻R。

有时阻抗不匹配还有另外一层意思,例如一些仪器输出端是在特定的负载条件下设计的,如果负载条件改变了,则可能达不到原来的性能,这时我们也会叫做阻抗失配。

在高频电路中,我们还必须考虑反射的问题。

当信号的频率很高时,则信号的波长就很短,当波长短得跟传输线长度可以比拟时,反射信号叠加在原信号上将会改变原信号的形状。

如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射。

为什么阻抗不匹配时会产生反射以及特征阻抗的求解方法,牵涉到二阶偏微分方程的求解,在这里我们不细说了,有兴趣的可参看电磁场与微波方面书籍中的传输线理论。

传输线的特征阻抗(也叫做特性阻抗)是由传输线的结构以及材料决定的,而与传输线的长度,以及信号的幅度、频率等均无关。

例如,常用的闭路电视同轴电缆特性阻抗为75Ω,而一些射频设备上则常用特征阻抗为50Ω的同轴电缆。

另外还有一种常见的传输线是特性阻抗为300Ω的扁平平行线,这在农村使用的电视天线架上比较常见,用来做八木天线的馈线。

因为电视机的射频输入端输入阻抗为75Ω,所以300Ω的馈线将与其不能匹配。

实际中是如何解决这个问题的呢?不知道大家有没有留意到,电视机的附件中,有一个300Ω到75Ω的阻抗转换器(一个塑料封装的,一端有一个圆形的插头的那个东东,大概有两个大拇指那么大)。

它里面其实就是一个传输线变压器,将300Ω的阻抗,变换成75Ω的,这样就可以匹配起来了。

这里需要强调一点的是,特性阻抗跟我们通常理解的电阻不是一个概念,它与传输线的长度无关,也不能通过使用欧姆表来测量。

为了不产生反射,负载阻抗跟传输线的特征阻抗应该相等,这就是传输线的阻抗匹配,如果阻抗不匹配会有什么不良后果呢?如果不匹配,则会形成反射,能量传递不过去,降低效率;会在传输线上形成驻波(简单的理解,就是有些地方信号强,有些地方信号弱),导致传输线的有效功率容量降低;功率发射不出去,甚至会损坏发射设备。

如果是电路板上的高速信号线与负载阻抗不匹配时,会产生震荡,辐射干扰等。

当阻抗不匹配时,有哪些办法让它匹配呢?第一,可以考虑使用变压器来做阻抗转换,就像上面所说的电视机中的那个例子那样。

第二,可以考虑使用串联/并联电容或电感的办法,这在调试射频电路时常使用。

第三,可以考虑使用串联/并联电阻的办法。

一些驱动器的阻抗比较低,可以串联一个合适的电阻来跟传输线匹配,例如高速信号线,有时会串联一个几十欧的电阻。

而一些接收器的输入阻抗则比较高,可以使用并联电阻的方法,来跟传输线匹配,例如,485总线接收器,常在数据线终端并联120欧的匹配电阻。

为了帮助大家理解阻抗不匹配时的反射问题,我来举两个例子:假设你在练习拳击——打沙包。

如果是一个重量合适的、硬度合适的沙包,你打上去会感觉很舒服。

但是,如果哪一天我把沙包做了手脚,例如,里面换成了铁沙,你还是用以前的力打上去,你的手可能就会受不了了——这就是负载过重的情况,会产生很大的反弹力。

相反,如果我把里面换成了很轻很轻的东西,你一出拳,则可能会扑空,手也可能会受不了——这就是负载过轻的情况。

另一个例子,不知道大家有没有过这样的经历:就是看不清楼梯时上/下楼梯,当你以为还有楼梯时,就会出现“负载不匹配”这样的感觉了。

当然,也许这样的例子不太恰当,但我们可以拿它来理解负载不匹配时的反射情况2.稳定时间(Stable Time)稳定时间t s被定义为在输入端阶跃信号的作用下,输出电压稳定在规定的终值误差带以内所需的时间。

也被称为总响应时间。

一个信号在通过运放内部的电路时,总要花费一定的时间。

因此,输出端要花费一定的时间来对输入端的阶跃信号进行响应。

此外,输出端一般会超调,然后经历一段时间的震荡后才稳定在终值上。

在采集系统中,信号变化快速时,稳定时间是设计过程中的重要问题。

例如当用运放对一个集线器输出的信号进行缓冲时,然后将信号给AD,在集线器切换通道时,输入端就会感受到一个阶跃变化。

只有当运放的输出稳定在某个值后,AD才能进行采样。

3.与频率相关的参数(Parameter Relate to Frequency)在运放的参数中,有5个参数与频率特性有关系,它们是:单位增益带宽、增益带宽积、单位增益时的相位裕度、增益裕度、最大输出摆幅带宽。

单位增益带宽和增益带宽积很相似,单位增益带宽是运放增益为1时的频率。

增益带宽积是开环增益与该点频率乘积。

对于电压反馈运放,增益带宽积是一个常数,而对于电流反馈运放,该参数无意义。

因为增益与频率不是线性关系。

在选择运放时要考虑增益带宽积和摆率。

相位裕度是信号180度时的相移与单位增益处相移之差的绝对值。

相位裕度是开环测量的。

增益裕度是单位增益与180度相移时增益之差。

相位裕度和增益裕度是确定电路稳定性的两种方法。

由于轨到轨输出的运放有较大的输出阻抗,所以再驱动容性负载时会产生很大的相移。

这个额外的相移会使相位裕度变坏。

由于这个原因,大多数轨到轨输出的CMOS运放在驱动容性负载时,只有有限的驱动能力。

最大输出摆幅带宽B OM是输出摆幅超出某个规定值或者输出仍处于运放线性区内的那个最高频率。

最大输出摆幅带宽受到摆率限制。

当频率越来越高时,输出受限于摆率,就不能以足够快的响应来维持指定的输出电压摆幅。

为了使运放稳定,在运放的内部第二级上,通过加补偿电容来实现频率补偿,被称为主极点补偿。

这种方法使运放在相移到180前,增益降为1.4.输入噪声(Input Noise)每个运放都有内部寄生噪声,运放的噪声是通过在输出端测量然后换算到输入端的。

1.Spot Noise在噪声的频谱密度中,可以看出噪声主要有粉噪声和白噪声构成,粉噪声与频率成反比,在低频时有意义。

白噪声的频谱密度是平滑曲线。

在运放的参数中一般给出10Hz和1KHz频率时的噪声密度。

10Hz时主要是粉噪声,而1KHz时为白噪声。

两者之间有转折频率来区分。

2.宽带噪声宽带噪声被定义为在一个指定频带内的峰峰电压,典型的频带值有0.1Hz-1Hz或0.1Hz到10Hz。

当运放的内部结构保持不变时,增加偏置电流会降低噪声(同时会增加SR,GBW和功耗)。

从运放输入端想运放看进去的电阻值也会增加噪声。

对同相和反相端进行电阻平衡时,虽然有助于对输入偏流引起的失调进行调零,但却增加了电路噪声。

5.摆率(Swing rate)摆率SR是由阶跃变化引起的输出电压的变化速率。

它的单位是V/S。

如下图生动展示了摆率。

运放的摆率等于它可以传递的信号的摆率的最大值,这时增益一般规定为1,因此有时摆率又称单位增益摆率。

当运放在传递信号时,如果要求不会因SR太慢而使信号失真,那么,放大器的摆率必须至少要等于信号的最大摆率。

一个正弦波的最大摆率出现在过零点时,SR=2*pi*f*V.f为信号频率,V为信号的峰值电压。

因此,SR/(2*pi*f)可以求出最大不失真输出电压。

SR有时被表示为SR+和SR-。

其中SR+表示正向转移的摆率,SR-表示负向转移时的摆率。