片上网络关键技术研究

片上共面波导关键技术及其应用研究

片上共面波导关键技术及其应用研究一、本文概述随着微电子技术的快速发展,片上互连技术成为了制约高性能集成电路性能进一步提升的关键因素之一。

片上共面波导(Coplanar Waveguide,CPW)作为一种重要的微波传输线结构,在微波毫米波集成电路、高速数字电路以及微波单片集成电路等领域具有广泛的应用前景。

本文旨在深入探讨片上共面波导的关键技术及其在相关领域的应用研究,以期为高性能集成电路的设计和制造提供有益的参考和启示。

本文首先介绍了片上共面波导的基本结构和传输特性,包括其电磁场分布、传输损耗、色散特性等方面。

在此基础上,重点分析了片上共面波导的设计优化技术,包括介质材料选择、导体材料优化、线宽线距调整等方面,以提高其传输性能和集成度。

同时,本文还关注了片上共面波导的加工制造技术,包括光刻、刻蚀、金属化等工艺流程的优化和改进,以提高其制造精度和可靠性。

在应用研究方面,本文重点探讨了片上共面波导在微波毫米波集成电路、高速数字电路以及微波单片集成电路等领域的应用。

通过实例分析,展示了片上共面波导在提高电路性能、减小电路尺寸、降低制造成本等方面的优势。

本文还展望了片上共面波导在未来集成电路设计中的潜在应用和发展趋势,为相关领域的研究人员提供了有益的参考和借鉴。

本文旨在全面系统地探讨片上共面波导的关键技术及其应用研究,以期推动高性能集成电路技术的不断发展和创新。

二、片上共面波导的基本理论片上共面波导(Coplanar Waveguide, CPW)是一种广泛应用于微波和毫米波集成电路中的传输线结构。

其基本理论涉及电磁波在导体与介质分界面上的传播行为,以及导体结构对电磁波传输特性的影响。

CPW结构由中央导带和两侧的地带组成,所有导体均位于同一平面上,因此得名共面波导。

电磁波在CPW中的传播遵循麦克斯韦方程组,特别是在时谐场下,可以简化为亥姆霍兹方程。

通过求解该方程,可以得到电磁波在CPW 中的传播常数、相位常数、衰减常数等关键参数。

电脑芯片分析中的片上网络设计与实现

电脑芯片分析中的片上网络设计与实现电脑芯片是现代科技的重要组成部分,它们在计算机领域的发展起到了举足轻重的作用。

而在电脑芯片的制造过程中,片上网络的设计与实现是一个关键环节。

本文将深入探讨片上网络的设计原理、实现方式以及相关技术的发展。

一、片上网络的设计原理片上网络是指在一个芯片上实现的网络结构,它由一系列的逻辑电路和通信结点组成,可以用来连接芯片上的不同功能模块。

片上网络的设计原理主要包括以下几个方面:1.1 芯片组成和模块划分在设计片上网络之前,首先需要对芯片进行整体的组成和模块划分。

芯片通常由处理器核心、存储器、输入输出接口等功能模块组成。

通过对芯片功能的分析和划分,可以确定片上网络需要连接的模块以及通信的需求。

1.2 网络拓扑结构的选择在设计片上网络时,需要选择合适的网络拓扑结构。

常见的网络拓扑结构包括总线结构、网络结构和集成结构等。

每种拓扑结构都有其自身的特点和适用范围,根据芯片的功能需求和性能要求,选择合适的拓扑结构对于片上网络的设计非常重要。

1.3 路由算法的设计片上网络的设计离不开路由算法的选择和设计。

路由算法决定了数据在网络中的传输路径,直接影响网络的性能和吞吐量。

在选择路由算法时,需要考虑网络的拓扑结构、数据通信的可靠性和效率等因素,以及芯片本身的资源和功耗限制。

二、片上网络的实现方式片上网络的实现方式多种多样,主要包括硬件实现和软硬件结合实现两种方式。

2.1 硬件实现硬件实现是指将片上网络的功能直接实现在芯片硬件中。

这种实现方式具有低时延、高并发和高可靠性的特点,但相对而言比较复杂和耗费资源。

硬件实现可以采用专用电路的方式,例如使用交换网络来实现。

另外,硬件实现还可以使用配置逻辑单元(FPGA)等可编程硬件设备来实现。

2.2 软硬件结合实现软硬件结合实现是指将片上网络的部分功能通过软件来实现,而将主要的数据通信等关键功能实现在硬件中。

这种实现方式兼顾了硬件实现的性能优势和软件实现的灵活性。

片上网络

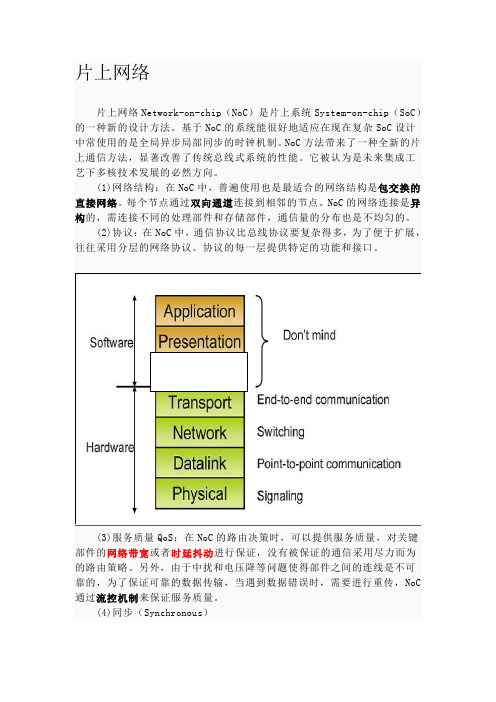

片上网络片上网络Network-on-chip(NoC)是片上系统System-on-chip(SoC)的一种新的设计方法。

基于NoC的系统能很好地适应在现在复杂SoC设计中常使用的是全局异步局部同步的时钟机制。

NoC方法带来了一种全新的片上通信方法,显著改善了传统总线式系统的性能。

它被认为是未来集成工艺下多核技术发展的必然方向。

(1)网络结构:在NoC中,普遍使用也是最适合的网络结构是包交换的直接网络。

每个节点通过双向通道连接到相邻的节点。

NoC的网络连接是异构的,需连接不同的处理部件和存储部件,通信量的分布也是不均匀的。

(2)协议:在NoC中,通信协议比总线协议要复杂得多,为了便于扩展,往往采用分层的网络协议。

协议的每一层提供特定的功能和接口。

(3)服务质量QoS:在NoC的路由决策时,可以提供服务质量,对关键部件的网络带宽或者时延抖动进行保证,没有被保证的通信采用尽力而为的路由策略。

另外,由于中扰和电压降等问题使得部件之间的连线是不可靠的,为了保证可靠的数据传输,当遇到数据错误时,需要进行重传,NoC 通过流控机制来保证服务质量。

(4)同步(Synchronous)优点 通过并发和非阻塞交换获得更高的带宽通过分层协议获得可靠的传输通过分组交换获得更高的链路利用率 通过点对点传输获得低功耗全局异步或准同步的、模块化、可升级的结构缺点交换电路和接口增加了电路面积数据打包、缓冲、同步和接口增加了延迟缓冲和增加的逻辑造成了功耗增加与原有IP 核接口和协议的兼容问题Noc 提供的服务分为两种基本类型:尽力而为服务(Best-Effort,BE)和有保障服务(Guaranteed-Services,GS)。

GS 的实现方法有两种:(1)面向无连接的数据包优先级方式(2)面向连接的虚电路方式前者是通过对数据包设定不同的优先级来保障需要的服务质量,其保障服务质量具有统计特性,属于软保障;后者是指通过预留资源使GS 数据流在逻辑上与网络中其他数据流隔离,从而避免阻塞,以此保障服务质量,属于应保障。

片上网络拓扑结构的研究

(. c olf o ue Xi a nvri , i a hn 10 1 Sh o o mp t d nU iesy X ’ nC ia 7 ; C r i t 70 1

2 Sae e bo NX da nv r t X ’ nC ia 0 . t yl I iinU i s y i a hn 1 7 ) t k a fS e i 70 1

I t s ae fs w t d cd h cn a caa e sc i N Cadt e t ho g ia a T e e n h pr i t en oue e ehi r c rts n o n e y e nl y n h e; hn ip , r , i r t t c h t ii l h k c o its r w

系统 , 以及应用等各个层面。 目前 ,o N C的概念很宽

其核心思想是将计算机网络技术移植到芯片设计中

了缩短各种应用的设计和验证时间 , 各大研究机构

速发展 , 研究就涉及到从物理设计到体系结构 、 操作 来 , 从体系结构上彻底解决总线结构带来的问题。 为

基金项 目: 中兴通讯基金 Z J 2 0 0 1 0 5 X S 0 6 9 2 1 9国家 自 然科学基金项 目 N . 0 3 0 0 o 6 5 2 6

Absr c : W ih t e c mp e i fd sg i o r h tcur n r a i g ta iin lb - a e c t cu e h s ta t t h o lx t o e in ng S C a c i t e i c e sn . r d to a us b s d a hi t r a y e r e b c met e b t e e k o o e o h ot n c fc mmun c t n a n P lc . I r e ome tt e r q ie n so c lbi t , e e g l ia i mo g I b o ks o n o d rt e h e u r me t fs a a l y i n ry

5G网络切片关键技术综述与应用展望

网络切片技术是5G 区别2G/3G/4G 的主要功能之一。

5G 网络切片提供了一种比较灵活的机制,使得运营商可以充分利用网络资源来为各种不同的应用提供差异化服务,是一种比较理想的5G 行业专网部署方式,具有较好的发展前景。

1 5G网络切片主要考虑因素在5G 网络中,建立有效的网络子切片需要考虑四个关键因素:时延、负载均衡、异构性和功率效率。

(1)时延。

不同的应用对于时延的要求是不一样的,在5G 切片网络中,物联网和人工智能的相关应用,如自动驾驶和远程手术等应用,对于网络时延十分敏感。

而一个应用端到端的时延由多条路径上的时延加和而成,仅依靠单独优化某一局部的时延无法满足应用要求,因此时延是构建有效的网络切片中的关键因素之一。

(2)负载均衡。

5G 切片网络支持多样化的多媒体应用,各种应用的控制和管理都是通过动态网络切片来处理,为保障运营效率和服务质量,通过网络功能和协议定制,为不通的业务场景匹配相应的网络功能[1],将所需的资源在全网中进行动态的分配和释放,并进一步动态优化网络连接[2]。

(3)异构性。

5G 网络为了承载移动终端增长带来的海量移动数据流量以及需求多样化的新兴业务,运营商不断增加基站数量和类型,密集化组网提升容量。

因此,5G 切片网络的异构性不仅仅是指不同类网络融合形成异构网络,同时,也指网络中需要兼容不同制造商生产的网络设备和相关应用系统。

(4)功率效率。

数据显示,一个5G 基站平均功耗在3.8 kW 左右,是4G 基站的3倍以上,单个5G 基站电费大约2.3~3万元/年。

5G 是未来数字社会的基础设施,需要长期稳定发展,因此需要更多的绿色技术和创新,以进一步降低5G 基站的功率,提高效率,实现可持续发展。

2 5G网络切片典型业务场景国际标准化组织3GPP 已经定义了5G 的三大应用场景:增强移动宽带、大规模机器通信以及超高可靠超低时延通信[3],这三大应用场景对应着“快”“稳”“密”三个特点,对网络的速率、容量、时延、可靠性、安全性、移动性、服务成本等有不同的需求。

片上网络体系结构的研究与进展

( . co lcr nc si t, da iest, ’n7 0 7 ; . mp tr c o lXiin ie s y Xi n7 0 7 ) 1 Mir e t is n t ue XiinUnv ri Xi 1 0 1 2 Co ue h o, da v ri , ’ 1 0 1 e o I t y a S Un t a

维普资讯

第 3 卷 第2 期 3 4

V1 3 o. 3

No. 4 2

计

算

机

工

程

20 年 l 07 2月

De e be 0 cm r 2 07

Co p t rEn i e rn m u e gn eig

・工程应 用 技术 与 实现 ・

文章编号:1o_32( 0)-o3.0 文献标识码: oo_48 074-29_3 2 2 _ A

中圈分类号: N0 T 42

片上 网络体 系结构 的研 究 与进展

朱樟 明 ,周 靖 ,杨银 堂

(. 1 西安 电子科技大学微 电子研究所,西安 7 0 7 ;2 西安 电子科技大学计 算机 学院,西 安 70 7 ) 10 l . 10 1

s f co , o o tma r s c mmunc t n ac i cue , n e in meh d lgy Low o rp ro ma c dc mp t/o iai r ht tr s OS a dd sg to oo . o e p we e r n e a o uec mmu iain a ii et e . f n nc t blt a o y r hek ys Th sp p rds u s sf u C c ie trs Con ieig te p ro ma c , e n we ,i fn h tte 2 me h i e wo s,a d wo mhoe i a e ic se o rNo a htcu e . r sd rn h ef r n e a aa dpo r t idsta D s st rt n r r h h l

片上网络

0! 9&$ 分层的设计方法

我们提出一种垂直的设计流程。这个微型网络 层次结构中的每一层都针对特定的应用域进行了优 化, 功能专一, 如图 + 所示。这种针对特定应用的片

向: 软件工程与网络软件。

D K 期

杨敏华等:拟的优点, 它代表 了技术发展的一个趋势。当然功能的专一并不意味 着复杂性的丧失。网络自配置功能中的核心一点就 是支持组件的即插即用, 这就需要组件间通过具体 可配置协议相互作用, 因此微型网络层次结构中的 每一层都具有相当的复杂性。

/ ! 引! 言

随着半导体技术的发展, 门长度将会进一步减 小到 7, Y +,,<H 的范围。电子元器件尺寸的减小, 使得人们完全可以在单个芯片上构造一个系统, 即 ).$/ ( )W/GFH .< L=;N ) , 被称为芯片系统。在未来的 +, 年中 #<GFJ<FG 将是最大的超级系统。随着 #<GFJ<FG 访问量的增长, 对基础设施的需求将进一步加大, 许 多基础设施将变为硅结构。随着 #<GFJ<FG 和联网技 术不断成为 ).$/ 发展的动力, #0%) ( G=F ;<GFJ<?G;.<?V GFL=<.V.EW J.?KH?N O.J /FH;L.<K>LG.J/) 预计在接下来 的十年中全球将设计包含上十亿晶体管的芯片, 目 标尺寸是 7,<H, 并且具有 +,:=Z 的时钟频率。在微 小的芯片上包含上十亿支晶体管, 对它的设计将会 非常复杂。当前的设计工具和方法已经不能适应这 种新的设计需求, 因此设计工具和方法学需要进行 一次彻底的变革。 ).$ 设计具有挑战性的一面是在有限的能量预 算下, 保证充分的服务质量。最基本的 [.) 需求包 括: 性能和可靠性。应用要求部署在便携式设备上

片上系统设计中的高性能片上网络优化研究

片上系统设计中的高性能片上网络优化研究片上系统设计中的高性能片上网络优化研究随着集成电路技术的不断发展,片上系统设计中的高性能片上网络优化成为了一个重要的研究领域。

片上网络是连接芯片上各个功能模块的网络,其性能优化对于提高整个芯片的性能具有重要意义。

本文将探讨高性能片上网络优化的研究内容和方法,并分析其在片上系统设计中的应用。

首先,高性能片上网络优化需要考虑多个因素。

首先是网络拓扑的设计。

合理的网络拓扑可以减少延迟、提高吞吐量和降低功耗。

常用的网络拓扑包括多级交叉开关网络、栅栏网络和环形网络等。

其次是路由算法的设计。

路由算法决定了数据在网络中的传输路径,合理的路由算法可以减少网络拥塞和延迟。

最后是流量控制和拥塞控制。

流量控制和拥塞控制可以保证网络的稳定性和可靠性,防止数据丢失和延迟增加。

在高性能片上网络优化的研究中,有许多方法和技术被提出。

首先是利用虚拟通道技术。

虚拟通道技术可以将网络划分为多个虚拟通道,每个虚拟通道可以独立地传输数据,从而提高网络的带宽利用率和吞吐量。

其次是使用自适应路由算法。

自适应路由算法可以根据网络状况动态地选择最优的传输路径,从而减少网络拥塞和延迟。

另外,还可以使用队列调度算法来优化数据的传输顺序,以减少延迟和提高吞吐量。

此外,还可以使用流量控制和拥塞控制算法来保证网络的稳定性和可靠性。

高性能片上网络优化的研究在片上系统设计中有着广泛的应用。

首先,在多核处理器中,高性能的片上网络可以提高各个核之间的通信效率,从而提高整个系统的性能和并行计算能力。

其次,在图像处理器和视频处理器中,高性能的片上网络可以实现快速的数据传输和处理,从而提高图像和视频的处理速度和质量。

另外,在通信芯片中,高性能的片上网络可以提高通信速率和可靠性,从而提高通信系统的性能和稳定性。

总之,高性能片上网络优化是片上系统设计中的重要研究领域。

通过合理的网络拓扑设计、优化的路由算法和流量控制算法,可以提高片上网络的性能,降低延迟和功耗,从而提高整个芯片的性能和功能。

基于多级网络的片上光互连系统的研究的开题报告

基于多级网络的片上光互连系统的研究的开题报告一、研究背景与意义随着芯片规模越来越大,互连成为限制芯片性能的瓶颈之一。

为了解决这个问题,光互连技术被提出。

相比于电互连,光互连具有高速、低能耗、低延迟等优点。

然而,传统的片上光互连架构中存在一些问题,比如成本高、复杂度大、稳定性差等。

因此,研究基于多级网络的片上光互连系统,具有重要的研究意义。

二、研究内容和方法本研究将基于多级网络的片上光互连系统作为研究对象,针对现有的片上光互连架构中存在的问题,提出了一种新的解决方案。

具体的研究内容如下:1. 多级网络的构建。

根据芯片中不同功能单元之间的互连需求,设计出一种多级网络的结构,并建立相应的数学模型。

2. 光互连的实现。

针对多级网络的结构,设计出一种高效的光互连方案,实现芯片中不同功能单元之间的快速互连。

3. 系统的实现和测试。

基于开源EDA软件,实现设计的多级网络和光互连方案,并进行性能测试。

三、预期研究成果及创新点本研究预期可以获得以下成果:1. 提出一种新的基于多级网络的片上光互连架构方案,解决传统光互连架构的成本高、复杂度大、稳定性差等问题。

2. 建立了相关的数学模型,分析了多级网络的性能及光互连方案的实现效果。

3. 实现了设计的多级网络和光互连方案,并进行了性能测试,展示了其高速、低能耗、低延迟等优点。

四、研究进度安排第一年:1. 调研现有的片上光互连架构,并分析其存在的问题及未来的发展方向。

2. 设计多级网络结构,并建立相关的数学模型,对其性能进行分析和优化。

3. 开始光互连的实现,并进行初步实验验证。

第二年:1. 优化多级网络结构,并对光互连方案进行优化。

2. 完善并测试实现的多级网络和光互连方案,并进行性能测试。

3. 撰写论文及相关文章。

第三年:1. 完成论文及相关文章的撰写和修改。

2. 准备相关的学术报告,并参加相关学术会议。

3. 对研究成果进行总结和展示。

五、参考文献1. C. Chen, et al., “Energy-efficient system design with silicon photonic interconnects,” in Proc. IEEE Int. Symp. on Power and Energy Systems, 2016, pp. 1-5.2. K. Yoshida, et al., “Optical interconnects for future many-core processors,” Optics Express, vol. 24, no. 5, pp. 5016-5030, 2016.3. Z. Zheng, et al., “Silicon photonics for on-chip and inter-chip optical interconnects,” J. Semicond., vol. 38, no. 5, 2017.4. J. Van Campenhout, et al., “Towards optical multi-chip modules using 3D integration of silicon photonics and microelectronics,”in Proc. IEEE Int. Electron Devices Meeting, 2016, pp. 20.25.1-4.。

无缓存片上网络的研究

2 4 2基于 金色分 组算 法 的仲裁 策略 ..

为 了避免全 排 列导致 的 较长关 键路 径 和各微 片 端 口分 配 的依 赖性 , 献 [】 出金 色 分 组 ( o e 文 6提 Gl n d Pce, P) 法 : 择 一个 分 组 , 它 的 优 先 级 高 aktG 算 选 使 于 网络 中所有 其他 分组 ,且 该分 组 的优先 级要 持续 足 够长 的时 间 ,以保证 它能 够 到达 目的节 点 。这个 分 组称 为金 色分组 ,组 成该 分组 的微 片称 为金 色微 片。 该算 法 通过遍 历所 有 可能 的分组 , 每个 分组 最 使 终 都 能成为 金色 分组 , 而保证 无活 锁 。 从 基于 G P算法 , 献 [】 偏 转 路 由映 射 到 一 个 文 6将 置 换 网络 ,来 代 替 B E S中 的仲 裁 逻 辑 和 交 叉 开 LS

T e e o e b f re sN C, whc l n t si - o trb f r n o e t o tn i n b r p i g o e e t g h r fr , u f l s o e ih e i ae n r u e u f sa d c p swi c n e t y d o p n rd f c i mi e h o l n

偏转 。

功耗减小 2 ~ 0 路 由器面积减少 7 %, 0 4 %, 5 并降低 实现复杂度l。这种完全消除路 由器内缓存的片上 1 . 6 ]

网络 , 为无 缓存 片上 网络 。在无 缓存 片上 网络 中 , 称 当微 片 ( i) 对 输 出端 口 的竞 争 中失 败 时 , 微 l ft 在 该 片会 被 偏 转 到 其 他 未 分 配 的 输 出 端 口l 或 被 丢 弃 1 l , 并 由源 节点 重新发 送[1 繁 的微 片偏 转或 重传 可 2。频 , 3 能会 降低 性 能 , 然而 在 中低 负荷 下 , 口竞 争 较少 , 端

片上网络性能及功耗仿真实验研究

收 稿 日期 :2 1 0 0 1— 3—1 6

创新 研 究 的通用 性 和灵 活性 等 特 点 , 合 定 制 芯 片 综 原 型元 助于 由浅 人 深地 理 解 片上 网络 的 体 系结 构 ,

且 因其 特性 固定 故 不适 合 进 行 灵 活 地 实 验 , 再者 原

p af r b s d o y t mC.c mp ee r e t a h n x e i n st k n e s a a l RGAM i lt r l t m a e n S s o e o lt st e e c i g e p r h me t i g t c b e NI a h l s mu ao

功能 , 现 网络 的上行 与下行 。 实

12 处 理 单元 .

Ss m y e C是 由 O C 开发的统一建模平 台, t SI 为系 统设计 提供 了统 一 的语言 以便更 好地 进行 软硬 件协 同设 计 和 验 证 。它 在 C ++基 础 上 添 加 一 个 S s y— t C类库。类库是采用 c+ 编写 的各种 函数 和数 e m + 据类型等的程序库 , 将并发 、 时钟和特殊数据类型等

个 片上 网络 由路 由器 、 络接 口和 处 理单 元 网

这三 种基 本要 素组成 。

片上 网络像计算机网络可分通信子网和资源子 网。通信子网由网络接 口一边的所有路由器和其间 的链路构成 , 负责各个节点间数据 的传递及路 由功 能 。而资 源子 网 由网络接 口另 一边 的所有 处理 单元 构成 , 负责处理数据 , 完成 目标应用的功能 。 网络接 口是处在 资源子 网与通信子 网间 的装 置 , 到数 据连 接 和转 换 的 功 能 。它通 常具 有 双 向 起

基于交叉开关结构的片上光互连网络研究

图 2给 出 了传 统 的光 交叉 开关所 使用 的基本 的

l 2光 交换 单元 .它包括 两条 光波 导 和一个 微环 谐 x

振 器 。当微环 谐振 器处 于打 开状态 ( N) , O 时 光信 号

耦 合进微 环谐 振器 , 传输 方 向转 变 9 。 当微环谐 振 0。 器 处 于关 闭状 态 ( F ) , 信 号 直 线 传 输 , 向 O F时 光 方

器和 1 0根 波导 .5个 波 导 交叉 点 , 2 5个 光输 人 端 口

和 5个光 输 出端 口。 任 意两个 输 入 和输 出端 口之 在 间都 能够 通 过 在 特 定 的 波 导交 叉 点 处 打 开 一 个 微

+

c os 态 r s状

环谐 振器 来 建立 一条 单 独 的传 输 通道 , 条 数据 传 每 输通 道都 要 经过 一次 微 环谐 振 器 的耦 合 。 向偏 转 方

也 会影 响光 功率 、 热调 制功率 和 面积 。此外 , 收 消 接 息 时 要 通 过 向滤 波 器 环 中 注人 电 荷使 其 调谐 到合 适 的波 长 , 这会 引起 每个 被调 谐 的环 5 W 的 固定 0I x 消耗。

24 传统 光 交叉开 关与 新光 交叉 开关 的对 比 .

一

本节将 先介 绍传 统 的光 交叉 开关结 构 .然 后再

介 绍 两 种 较 新 的 光 交 叉 开 关 结 构 ( MXbr和 D a

列 的各个 开关 的横 向输 人 ,输 出是 位于 最下一 行

的各个 开 关 的纵 向输 出 。2 2开关 有 2个 状 态 :a x br 和 cos rs。如 图 1 示 . 谓 b r 所 所 a 状态 , 指横 向输 入 是

支持内嵌IP芯核测试的片上网络路由器技术研究

第 3期

电子 测量与仪器学报

J oURNAL oF EL ECT RoNl C 伍 As URE^ E NT AND Ns i TRU NT 伍

2 No 3 4 .

・

21 O O年 3月

25 ・ 0

DOI 037Байду номын сангаас4 S J 1 8 2 0.0 5 :l . 2 / P.. 1 7-0l 0 20

电 路集 IC0 T ’ 2巾的 微 系统 芯 片基 准 电路 d 9 行 了实验 验证 65进

关键词:微系统芯片;片上网络 ;路由器 :路 由算法 ;测试存取链配置

中 图分 类 号: N 0 T 47 文 献标 识码 : A 国 家标 准 学科 分 类代 码: 1. 3 5 01 5 0

络测试 内嵌 I P芯核,提 出了支持 内嵌 I 芯核测试的片上 网络路由器结构,分析讨沦丁测 斌模 式下的无拥塞路 由算法,片上网 P 络路 由器分析模型以及在片上网络平台 上的测试存取链配置方法 使用 VH L硬件描述语言实现了在 F G D P A芯 片中可综 合 的二维 Meh片上网络,建立 了片上网络测试平 台,可用 于分析被测芯核 的测试时间和路 E/ s f 交换算法 :最后,使用测试基 准 f

i g ag r h , n lssm o e fr u e n h e t c e sc an o fg rto eh di n l o i m a ay i d l tra dt ets c s h isc n u ai nm t o nNoC w eed s u s d Th D t o o a i r ic s e . e2

m e t l e u t r h 6 5o TC’ 2So Te t n h akswe ep e e td u ig aN o e t lto m . n a s lsf ed 9 fl r o t 0 C s Be c m r r r s n e sn C t s af r p

片上网络

三NoC路由策略3.1 NoC 路由技术3.1.1 虚拟直通技术3.1.2 存储转发技术3.2 NoC 路由算法3.2.1 确定性路由3.2.2 自适应路由3.3 本章小结存储转发是一种最简单、最直接的交换方式。

数据包到达网络节点时,需要首先被完整地暂存于接收缓冲区中,在确定了去向后,数据包再被投递到相应的端口,发送给邻接节点。

存储转发交换机制并不适合NoC网络。

首先,该机制决定了每个节点处的缓冲区大小至少要和网络支持的最大数据包一致,这将极大消耗片上资源以用于缓冲区的设计。

另外,采用存储转发机制时,数据包必须完全到达某中间节点后才能被发送到下一个节点,因此会带来极大的通信延迟。

虚拟直通交换是将数据包进行分片传输。

一个较大数据包被分割为较小的片段,传输过程中只要中间节点收到了一个片段就可以将其转发到下一个节点,而无需等待完整数据包的到来。

该交换方式克服了存储转发机制下表现出较大网络延时的问题。

然而,和存储转发类似,当网络发生拥塞时,整个数据包必须被完整地保存在阻塞时包头所在节点的缓冲区中,因此同样会占用大量网络存储资源。

虚拟直通也不适用于NoC系统。

-7-2.2 NOC的关键技术――路由技术本文所介绍的常用路由技术主要包括以下内容,包交换技术、虚拟通道技术[6]和死锁[7]避免技术。

包交换技术关注的是数据包是怎样从输入通道交换到输出通道的。

采用的包交换技术不同,所产生的延迟就不同,网络的延迟与包交换技术直接相关。

虚拟通道技术主要是结合虫洞路由一起使用,可以大大的降低阻塞发生的概率。

死锁避免技术,主要介绍了死锁的原理,在路由算法设计中也有所涉及。

2.2.1包交换技术常用的包交换技术主要有四种:存储转发(Store-and-Forward)、虚拟直通(Virtual Cut-Though)、虫洞路由(Wormhole Routing)和偏转路由(Deflection Routing)。

下面分别介绍它们的概念和一些相关问题。

片上互连网络多核众核处理器关键技术

精彩摘录

《片上互连网络多核众核处理器关键技术》精彩摘录

在当今高度信息化的时代,处理器技术作为信息技术的核心,其发展速度和趋 势一直备受。这本《片上互连网络多核众核处理器关键技术》一书,详细解析 了当前处理器技术的热点和未来发展方向,为读者揭示了多核众核处理器技术 的奥秘。

书中首先介绍了片上网络的基本概念和设计理念,深入阐述了其与传统的总线 式互连相比的优势和特点。片上网络的出现,使得处理器内部的通信变得更加 灵活、高效,为多核众核处理器的并行处理能力提供了有力的支持。

阅读感受

《片上互连网络多核众核处理器关键技术》读后感

在当今这个信息爆炸的时代,多核处理器已经成为了计算机技术的重要发展方 向。而在这一领域中,《片上互连网络多核众核处理器关键技术》一书为我们 提供了一个深入而全面的视角。这本书不仅介绍了多核处理器的基本概念和原 理,更进一步探讨了片上互连网络的关键技术,以及这些技术如何在实际应用 中发挥作用。

在阅读过程中,我深受启发。书中首先介绍了多核架构环境下的片上网络,详 细解释了片上网络如何适应多核设计的整体系统架构。在多核处理器日益普及 的今天,如何确保各个核心之间的通信效率成为了关键问题。片上网络的出现, 为这一问题提供了有效的解决方案。

书中还深入探讨了各种拓扑结构、成本及性能的权衡、路由算法、网络中使用 的流控制机制以及路由器微体系结构等细节问题。这些内容让我深刻体会到了 多核处理器设计的复杂性,以及片上网络在其中的重要性。

更令人印象深刻的是,书中还介绍了一系列基于片上互连网络技术的计算架构 设计案例。这些案例不仅展示了片上网络在实际应用中的优势,也让我明白了 如何在实际部署中进行取舍和融合各种技术。

在书的结尾部分,作者展望了未来几年在推动片上网络研究探索中将面临的关 键技术和新领域。这一部分内容让我对未来的技术发展有了更清晰的认识,也 为我未来的学习和研究指明了方向。

低功耗片上网络(noc)差错控制方法研究与设计

低功耗片上网络(noc)差错控制方法研究与设计

低功耗片上网络(NOC)差错控制是近年来电子设计自动化技术发展的重要方向。

它是一种基于分布式的网络架构,采用多节点的结构实现网络的系统控制,可有效控制系统的延时和拥塞,提高系统性能。

虽然封装NOC系统提供了更多的优势,但它仍存在一定的差错控制问题。

因此,在NOC系统中设计差错控制机制是必不可少的。

本文旨在研究和设计低功耗片上网络(NOC)的差错控制机制,以提高NOC系统的可靠性和安全性,满足用户的需求。

首先,本文分析了NOC系统的差错控制的挑战和机制,包括信道异常检测、定位和恢复、系统可靠性和安全性评估等。

其次,本文提出了一种基于可靠性和安全性指标的低功耗片上网络(NOC)差错控制机制,涉及信道异常检测、定位和恢复机制构建、系统可靠性分析和安全性评估等方面,以满足用户的需求。

最后本文在中国的电子设计自动化(EDA)实验环境中实施了实验,通过实验可以证明本文提出的方法可以有效控制NOC系统的差错。

综上所述,本文提出了一种基于可靠性和安全性指标的低功耗片上网络(NOC)差错控制机制,通过实验验证可以有效地控制NOC系统的差错,以满足用户的需求。

本文的研究为NOC系统设计提供了借鉴,也为EDA技术的进一步发展提供了参考。

浅谈5G关键技术

浅谈5G关键技术随着信息技术的快速发展,人们对无线通信的需求越来越高。

5G技术作为下一代无线通信技术,具有更高的速度、更低的延迟和更强的稳定性。

5G技术的发展离不开一些关键技术的支持。

本文将对5G技术的若干关键技术进行浅谈。

首先是毫米波技术。

毫米波也称作毫米波段,是指300GHz到3000GHz的频段。

由于毫米波具有高频、大带宽、小波长等特性,因此可以支持更高的数据传输速率。

在5G技术中,毫米波技术被广泛应用于高速数据传输和超高清视频等应用中。

毫米波技术的应用需要解决的一个难题是,信号的传输距离较短,易受障碍物干扰。

因此,在毫米波信号的传输过程中,需要使用波束成形和MIMO等技术来提高信号的传输质量。

其次是多输入多输出(MIMO)技术。

MIMO技术利用多个天线进行数据传输,可以在同一频带上传输更多的数据。

在5G技术中,由于频谱资源的有限性,需要通过提高频带利用效率来提高传输速率。

MIMO技术可以通过空间复用的方式,在同一频带上并行传输多个数据流,从而提高频带利用效率和传输速率。

目前,5G技术中的MIMO技术通常采用基于波束成形的空间复用技术,将信号发送到特定的用户。

第三是新型天线技术。

5G技术中需要使用大量的天线进行信号传输,因此天线技术对5G技术的影响非常大。

当前,5G技术中的新型天线技术主要包括有源天线和微型天线技术。

有源天线可以实现上下行频段的共存,从而避免了频段资源的浪费,可以提高频带利用效率。

微型天线可以实现数字化控制和集成化,可以精细的控制天线的辐射性能,从而减少信号干扰,提高传输质量。

第四是片上网络技术。

片上网络技术是一种新型集成技术,可以将多个功能单元集成在一个芯片上。

在5G技术中,将多个通信模块集成在同一个芯片上,可以大大减少通信模块之间的耦合,提高通信能力和通信质量。

同时,片上网络技术还可以实现高速和低延迟的数据传输,可以支持更多的智能化应用。

最后是网络切片技术。

网络切片技术是指在一台服务器或网络设备上,按照业务或服务类型将网络资源进行分割,从而实现定制化服务。

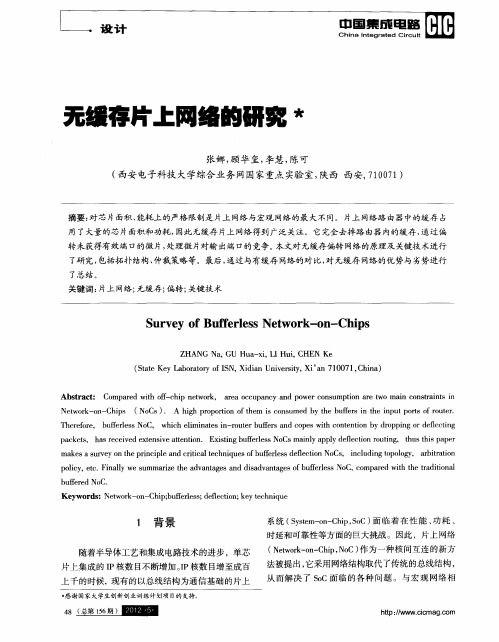

无缓存片上网络的研究

无缓存片上网络的研究张娜;顾华玺;李慧;陈可【期刊名称】《中国集成电路》【年(卷),期】2012(000)005【摘要】对芯片面积、能耗上的严格限制是片上网络与宏观网络的最大不同。

片上网络路由器中的缓存占用了大量的芯片面积和功耗,因此无缓存片上网络得到广泛关注。

它完全去掉路由器内的缓存,通过偏转未获得有效端口的微片,处理微片对输出端口的竞争。

本文对无缓存偏转网络的原理及关键技术进行了研究,包括拓扑结构、仲裁策略等。

最后,通过与有缓存网络的对比,对无缓存网络的优势与劣势进行了总结。

%Compared with off-chip network, area occupancy and power consumption are two main constraints in Network-on-Chips( NoCs ). A high proportion of them is consumed by the buffers in the input ports of router. Therefore, bufferless NoC, which eliminates in-router buffers and copes with contention by dropping or deflecting packets, has received extensive attention. Existing bufferless NoCs mainly apply deflection routing, thus this paper makes a survey on the principle and critical techniques of bufferless deflection NoCs policy, etc. Finally we summarize the advantages and disadvantages of bufferless N . including topology, compared with the arbitration traditional buffered NoC【总页数】7页(P48-53,56)【作者】张娜;顾华玺;李慧;陈可【作者单位】西安电子科技大学综合业务网国家重点实验室,陕西西安710071;西安电子科技大学综合业务网国家重点实验室,陕西西安710071;西安电子科技大学综合业务网国家重点实验室,陕西西安710071;西安电子科技大学综合业务网国家重点实验室,陕西西安710071【正文语种】中文【中图分类】TP303【相关文献】1.一种提高无缓存片上网络性能的方法 [J], 张坤;刘怡俊2.无缓存片上网络中偏转感知的拥塞控制方法 [J], 方娟;姚治成3.基于片上网络的低偏转率微缓存路由器 [J], 汪涟;朱珂;赵博4.一种片上网络缓存与带宽折中算法 [J], 樊利芳;张兴明;董春雷5.基于片上网络互连的多核缓存一致性研究综述 [J], 陈家豪;黄乐天;谢暄;魏敬和因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

片上网络关键技术研究杨晓强1, 2(1.西安电子科技大学微电子学院, 陕西西安 710071 ; 2. 西安科技大学 计算机系, 陕西西安710054)摘要:半导体技术的快速发展以及芯片上系统应用复杂度的不断增长,使得片上互连结构的吞吐量、功耗、延迟以及时钟同步等问题更加复杂,出现了将通信机制与计算资源分离的片上网络。

片上网络设计涉及从物理层到应用层诸多方面的问题,本文给出片上网络设计的一些关键技术:设计流程、拓扑结构、路由技术、交换技术、性能评估;并指出目前研究存在的问题和今后的研究方向。

关键词:片上网络;片上系统;路由;拓扑结构【中图分类号】TN4 【文献标识码】AResearch of Network on Chip TechnologyYANG Xiao-qiang1,2(1.School of Microelectronics,Xi,dian University 710071,China;2.Department of computer,Xi’an University of Science and Technology 710054,china)ABSTRACT:With the development of VLSI technology and increasing complexity of System on Chip application, comunication architecture on chip design encounters some problems,such as,power,latency and clock work on Chip(NoC) was introduced. NoC involves in many problems ranging from physical layer to application layer, the paper provides the key technology for NoC design, such as design flow ,topology, routing, performance evaluation, flow control, resource network interface. In the end,the problems in present research and future research trends are presented..Keywords:Network on Chip System on Chip Routing Topology1 引言片上系统(System on Chip,SoC)将计算资源,即多个处理核和大的可重用的组件集成到一个芯片上,实现了计算资源之间的点到点的连接转向了总线的连接。

相对于点到点的连接,总线的连接降低了设计的难度,减少了芯片的面积成本,有利于计算资源的标准化。

随着硅工艺的进一步发展,总线连接的通信方式面临着许多问题。

1)总线限制了所连接的计算资源的数量。

总线只能实现共享信道的通信,适合连接3到10个计算资源,若再增加计算资源,总线争用就会带来严重的竞争冲突,降低了信道的的吞吐量。

2)深亚微米的物理层带来问题。

长而细的全局总线,电阻大,消耗大量的能量;线间存在较大的偶合电容,对信号的传输造成大的干扰。

3)系统信号同步问题。

随着芯片集成度增加和芯片速度提高,芯片上各部分模块很难实现全局信号同步。

4)芯片的设计效率和计算资源重用问题。

每个片上系统有不同通信结构要求,系统内的每个计算资源也有不同通信结构要求,这就带来了重用的问题,降低了芯片的设计效率[1]。

为了解决设计复杂SoC时的问题,一些研究机构提出了以通信为中心的复杂SoC的计算资源的集成设计方法――片上网络(Network on Chip,NoC)。

NoC实现了计算资源与通信结构(网络)的分离[2,3]。

目前有许多机构在NoC方面做了大量研究,具有重要影响有:意大利Bologna大学和美国Stanford大学联合研发的一个可综合的、高性能NoC的XPipes;荷兰Philips公司研发的具有保证服务并提供尽最大努力服务NoC的ÆTHEREAL。

英国Manchester 大学研发的使用握手信号进行数据交换的自定时NoC的CHAIN,法国Pierre et Marie Curie大学研发的通用可扩展NOC的SPIN。

国内研究刚刚起步,主要有清华大学、西安电子科技大基金项目:国家自然科学基金项目(90607008) 无线通信自重构容错NOC研究学等。

NoC研究涉及到从物理设计到体系结构、应用服务、设计方法和工具等诸多方面。

从系统结构角度看,NoC研究的重点在于NoC的拓扑结构、NoC协议、NoC服务质量、NoC的信号同步和低功耗等问题[4,5]。

2 NoC的组成及设计流程2.1 NoC的组成NoC由计算资源和通信网络两部分组成。

计算资源一般由IP核和本地内存组成,对应应用层上一个独立的应用,是芯片物理层上一个独立的信号同步处理区域。

IP核是一个可以重构的硬件单元,例如处理器、DSP等[6]。

通信网络主要包含路由器、信道和资源网络接口。

图1给出一个3x3 NoC拓扑结构。

计算资源只受到芯片面积和接口的条件限制。

资源网络接口将资源和网络连接,使资源相对网络透明,实现了异构计算资源间的方便、灵活的通信。

NoC结构是一种片上通信基础结构,涉及了OSI的物理层、数据链路层和网络层[4]。

图1 一个3x3 NoC拓扑结构2.2 资源网络接口资源网络接口是计算资源与网络间的接口,目的是:1)让计算资源承担最小的通讯服务任务;2)将计算资源与网络通信部分分离,即计算和通讯间的分离,使计算资源对网络透明,从而实现异构资源间的互连,且能提高设计的重用性。

资源网络接口在计算资源这一侧实现了资源接口,在网络这一侧实现了网络接口。

资源网络接口易于使用分层的方法实现系统。

在分离高层,易于计算资源的重用;在分离的低层使得网络资源的重用优化,提高了实际设计效率[5]。

资源网络接口主要考虑地址信号,数据的打包、解包、编码,同步等问题。

2.3 拓扑结构NOC的拓扑结构定义系统中每个计算资源结点通过信道与其它计算资源结点的连接关系。

拓扑结构通常用图来描述。

结构既可以是规则的也可以是不规则的。

NOC的拓扑结构主要有网格结构、环网格结构、混合结构、非规则结构等,如图2所示。

(a)网格结构(b)环网格结构 (c) 混合结构(d)非规则结构图2 NOC的拓扑结构网络传输信息的能力主要依靠其拓扑结构。

拓扑结构除了对网络延迟、吞吐量、面积、容错以及功耗的极大影响外,还对路由设计策略和计算资源到网络结点的映射起着重要的作用。

目前还没有一个理论方案来确定最优的拓扑结构来实现任何一个给定的应用。

相对于规则拓扑,不规则拓扑构虽然能提高性能、降低功耗、减小面积,但同时可能产生版图设计、不均匀的线长等设计问题。

因此,决定有效的拓扑结构以平衡高层性能与细节的实现方法受到了微米或纳米级工艺的制约。

2.4 设计流程NOC设计分为计算资源结构和NOC结构的设计两部分。

NOC设计流程如图3所示。

首先进行计算资源结构设计,计算资源结构描述了应用系统的行为,计算资源单元实现系统的功能。

计算资源结构设计一般涉及两种模型---行为模型和计算资源结构模型。

行为模型被划分并映射到计算资源结构模型。

NOC结构的设计必须依照计算资源结构的设计。

1)通信的模型化和分析。

分析所有计算资源之间数据信息传输的特点,抽取传输信息的数量,信息单元的尺寸,通信的类型和速率。

在计算资源结构的仿真中,通过跟踪信息流可以获取通信的特点、要求,建立通信的模型。

2)拓扑结构与协议设计。

在建立的通信模型基础上设计拓扑结构和协议,目标是用尽可能少的网络资源实现计算资源之间的通信要求,同时要考虑系统的性能和扩展性。

这一步是NOC设计核心。

3)版图规划评估。

在NOC中,不是逻辑电路,而是互连结构主要影响着系统的功耗和面积。

芯片的版图规划评估是通过评估时钟周期上每个互连的延迟以及分析功耗、面积,为互连获得设计要求。

4)系统性能分析。

在仿真平台上(例如OPENNET),通过对计算资源结构的通信跟踪,仿真NOC 结构。

仿真结果可用于对不同设计的选择和完善系统的设计。

如果设计不能满足性能要求或仅有太小的性能富余,必须返回前2步。

5)NOC 逻辑与电路设计。

逻辑电路的行为由拓扑和协议的设计定义,通过硬件语言描述,并且综合。

图3 NOC 设计流程互连设计要求有好的线路和晶体管模型。

互连设计是分析的重点。

6)功耗、面积分析。

累加每一个活动的功耗,可计算出NOC的最大功耗;累加每一个设计部分,得到总的硅和金属使用的面积。

如果功耗和面积不能满足要求,必须返回选择不同的电路设计或重新进行版图规划,最坏情况下进行拓扑结构和协议的设计。

3 NOC协议3.1交换技术交换技术是按照某种方式动态分配传输线路和接口的资源。

交换技术包括两种主要类型,电路交换、包交换。

1)电路交换在发送数据前源端与目的端之间先建立链路,然后进行数据传输,数据传输结束后必须释放链路。

交换单元可以实现空分交换或时分交换。

典型的空分交换是crossbar。

电路交换的优点是在数据传输过程种不需要交换结点进行路由选择,传输延迟小,并且数据是按序到达目的端。

适合每次批量传输数据且实时性要求高的应用。

缺点是信道利用率低,建立和释放连接浪费额外时间,缺乏灵活性,不适合突发数据的传输。

2)包交换发送数据前后不需要建立和释放链路,每个包既携带数据又携带地址信息,独立地在每个经过的交换结点上进行路由选择。

包交换的优点是不需要建立和释放链路花费附加时间;在数据传输过程中动态分配带宽,信道利用率高,吞吐量高;对结点、链路故障具有容错能力。

适合突发数据的传输。

缺点是,在交换结点中存储整个包需要很大的缓存器,这将会增加NoC的面积成本(NoC交换结点相对于IP核,应该占用较小的面积)。

为了解决大的缓存器的面积问题,将包交换使用存储转发方式改进为虚通道和虫孔路由方式[7]。

3.2 路由策略路由是确定一个信息从源到目的的机制。

依据路由算法是否随网络通信量或拓扑自适应地调整变化,路由算法可以分为静态路由选择算法和动态路由选择算法两类。

NOC主要的静态路由选择算法有源路由算法和X-Y路由算法,源路由算法是由源结点指定包到目的结点的路由,X-Y路由遵循先按行走,再按列走;动态路由涉及动态分布机制,基于局部链路拥塞,能很好地适应网络状态的变化,但算法实现复杂、开销大。

3.3 流量控制在NoC领域,流量控制被特定用于端到端之间的传输协议的业务量。