FPGA课程设计报告

fpga在线课程设计

fpga 在线课程设计一、教学目标本课程旨在通过FPGA(现场可编程门阵列)在线课程设计,让学生掌握FPGA的基本概念、原理及其在数字电路设计中的应用。

通过本课程的学习,学生将能够:1.知识目标:理解FPGA的工作原理、结构及编程方法;掌握FPGA在数字信号处理、通信、嵌入式系统等领域的应用。

2.技能目标:学会使用FPGA设计工具进行电路图绘制和编程;具备分析、解决实际工程问题的能力。

3.情感态度价值观目标:培养学生对电子技术的兴趣,提高创新意识和团队合作能力,使其意识到FPGA技术在现代社会中的重要性。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA基本概念:介绍FPGA的定义、发展历程、特点及应用领域。

2.FPGA结构和工作原理:讲解FPGA的内部结构、工作原理及其与外部电路的接口。

3.FPGA编程方法:介绍FPGA的编程语言、开发工具及编程过程。

4.FPGA应用案例分析:分析FPGA在数字信号处理、通信、嵌入式系统等领域的具体应用。

5.实践环节:安排学生进行FPGA设计实践,巩固所学知识,提高实际操作能力。

三、教学方法为了提高教学效果,本课程将采用以下教学方法:1.讲授法:讲解FPGA的基本概念、原理及其应用,使学生掌握相关理论知识。

2.案例分析法:通过分析实际案例,让学生了解FPGA在各个领域的应用,提高学生的实践能力。

3.实验法:安排实践环节,让学生亲自动手进行FPGA设计,培养学生的动手能力和创新意识。

4.讨论法:学生进行小组讨论,分享学习心得,提高团队合作能力。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:选用权威、实用的FPGA教材,为学生提供系统的理论知识。

2.参考书:提供相关的FPGA技术参考书籍,丰富学生的知识体系。

3.多媒体资料:制作精美的PPT、教学视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:准备FPGA开发板、编程器等实验设备,为学生提供实践操作的机会。

FPGA设计的报告课程设计

FPGA课程设计实验报告实验一:设计一个可控的100进制可逆计数器一、实验要求用DE2-115开发板下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用clr plus minus 功能0 ××复位为01 1 0 递增计数1 0 1 递减计数1 1 1 暂停计数二、关键词可控制、可逆、100进制、复位、暂停、递增、递减三、内容摘要module updown_count(qout,reset,clk,plus,minus);output[7:0] qout;/*定义一个8位的输出,其目的是低四位和高四位分别表示计数器的个位和十位。

*/input clk,plus,minus,reset;//定义四个输入,时钟,加计数,减计数和清零reg[7:0] qout;//qout的数据类型为寄存器型always @(posedge clk)//当clk上升沿到来时执行一遍下列程序beginif(!reset) qout<=0;//当reset为低电平时,计数器执行清零功能,否则跳过elsebegincase({minus,plus})//case语句模块,包含加,减和暂停四个模块2'b10:if (qout[3:0]==0)//判断个位是否为零,若不为零,跳到个位减一beginqout[3:0]<=9;//给个位赋值if(qout[7:4]==0) qout[7:4]<=9;//判断十位是否为零,并且给十位赋值elseqout[7:4]<=qout[7:4]-1;//由于个位赋9,相当于向十位借一,因而十位减一endelseqout[3:0]<=qout[3:0]-1;//个位减一/*这一部分是减计数模块,其思路是:首先判断个位是否为零,若为零,则执行后面的程序,个位直接赋9,并且十位减一;否则个位减一*/ 2'b01:if (qout[3:0]==9)//判断个位是否为9,否则跳到个位加一beginqout[3:0]<=0;//若上面个位为9判断成立,则给个位赋值if(qout[7:4]==9) qout[7:4]<=0;//判断十位是否为9,若为9,则赋0elseqout[7:4]<=qout[7:4]+1;//若十位不为9,十位加一endelseqout[3:0]<=qout[3:0]+1;//个位加一/*这一部分是加计数模块,首先判断个位是否为9,若不为9,个位加1;否侧,再判断十位是否为9,若为9,十位赋0,否侧十位加1。

fpga技术课程设计

fpga技术课程设计一、教学目标本课程的教学目标分为三个维度:知识目标、技能目标和情感态度价值观目标。

1.知识目标:通过本课程的学习,学生将掌握FPGA技术的基本概念、原理和应用,了解FPGA技术的发展趋势及其在电子工程领域的广泛应用。

2.技能目标:学生将能够熟练使用FPGA开发工具,如ISE、Vivado等,掌握FPGA编程语言,如VHDL、Verilog等,并具备一定的FPGA硬件设计和验证能力。

3.情感态度价值观目标:培养学生对FPGA技术的兴趣和热情,使其认识到了解和掌握FPGA技术对于个人职业发展的重要性,树立正确的科学态度和创新精神。

二、教学内容教学内容将根据课程目标进行选择和,确保内容的科学性和系统性。

教学大纲如下:1.FPGA技术概述:介绍FPGA的基本概念、工作原理和分类,以及FPGA技术的发展历程和趋势。

2.FPGA硬件描述语言:讲解VHDL和Verilog两种主流的FPGA硬件描述语言,包括基本语法、语句结构和常用库函数。

3.FPGA设计与验证:介绍FPGA设计的基本流程,包括设计输入、综合、布局布线和仿真验证等环节。

4.FPGA应用案例:分析典型的FPGA应用案例,如数字信号处理、网络通信、嵌入式系统等,使学生了解FPGA技术在实际工程中的应用。

5.FPGA开发工具:介绍FPGA常用的开发工具,如ISE、Vivado等,以及这些工具的使用方法和技巧。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

1.讲授法:教师通过讲解、演示和举例等方式,向学生传授FPGA技术的基本概念、原理和应用。

2.讨论法:学生针对FPGA技术的相关话题进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:分析典型的FPGA应用案例,使学生了解FPGA技术在实际工程中的应用,提高学生的实践能力。

4.实验法:安排学生进行FPGA实验,让学生亲自动手操作,巩固所学知识,提高实际操作能力。

FPGA课程设计报告

FPGA课程设计报告学部:信息科学与技术学部专业:通信工程班级:10级1班学号:姓名:万洁指导老师:祝宏合作伙伴:张紫君一.《任务书》:实验一 100进制的可逆计数器(11——12周)实验二交通灯控制系统(15周)实验三多功能数字钟系统(14-15周)二.实验书写格式:一:题目要求二:程序代码三:操作步骤及运行结果截图四:心得体会三.实验附录:一:老师提供的资源二:关于实验所用EP4CE115F29板的简介实验一 100进制的可逆计数器一、设计一个可控的100进制可逆计数器,要求用实验箱下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用下,计数器具有复位、增或减计数、暂停功能。

二、程序如下:module keni100(CLR,CLK,PLUS,MINUS,OUT);——图在出现的输入界面内输入程序,点击file→save as,在出现的对话框中点击Yes,然后在出现的new project Wizard对话框中点击next,在Family&Device Settings 对话框中选择如下图所示的选项,在选择第三方软件的对话框中的选项选为none后点击next,在随后出现的对话框中,点击finish。

设置完成。

——图2、点击project→Set as Top-Level Entity,指向所输入的文件。

3、点击Processing→Start→Start Analysis & Synthesis。

——图4、点击File→New出现上面第一步时出现的对话框,如图,选择Vector Waveform File。

5、点击View→Utility Windows→Node Finder,在出现的对话框中点击List,如下图所示——图选择所需要的节点,将其拉到后面的Name栏中,并设置输入数据6、选择End Time:点击Edit→End Time,设置参数,如下图所示——图7、输入参数的数据设置完成后,保存,仿真图形如下图所示:——图8.点击Assigment→Settings,在出现的对话框(如图所示)中,选择Simulator Settings,在Simulation mode中选择Functional,进行功能编译。

基于fpga的简单课程设计

基于fpga的简单课程设计一、课程目标知识目标:1. 学生能理解FPGA的基本概念,掌握FPGA的基本结构和原理;2. 学生能描述数字电路的基本组成,了解数字电路在FPGA中的应用;3. 学生能掌握Verilog HDL语言的基本语法和编程方法,并运用其设计简单的数字电路。

技能目标:1. 学生能运用FPGA设计软件进行电路设计和仿真;2. 学生能通过Verilog HDL编程实现基本的数字电路功能;3. 学生能对设计的FPGA电路进行调试和优化,提高电路性能。

情感态度价值观目标:1. 培养学生积极主动探索新知识、新技术,增强其对电子工程领域的兴趣;2. 培养学生具备团队协作精神,学会与他人共同解决问题,提高沟通与表达能力;3. 培养学生具备工程素养,关注工程伦理,认识到科技发展对社会的重要意义。

课程性质:本课程为实践性课程,注重培养学生的动手能力和创新能力。

学生特点:学生具备一定的电子技术基础,对FPGA技术有一定了解,具备基本的计算机操作能力。

教学要求:教师需结合学生特点和课程性质,采用任务驱动、案例教学等方法,引导学生主动参与课堂实践,提高学生的实际操作能力。

同时,注重培养学生的自主学习能力和团队合作精神,提高学生的综合素质。

通过课程目标的分解与实施,使学生在知识、技能和情感态度价值观方面取得具体的学习成果。

二、教学内容1. 数字电路基础- 数字逻辑基础:逻辑门、逻辑函数、逻辑代数;- 组合逻辑电路:编码器、译码器、多路选择器、算术逻辑单元;- 时序逻辑电路:触发器、计数器、寄存器。

2. FPGA基本原理- FPGA结构:逻辑单元、查找表、寄存器、布线资源;- FPGA编程原理:配置、重配置、上电配置;- FPGA设计流程:设计输入、综合、布局布线、仿真、下载。

3. Verilog HDL编程- 基本语法:模块、端口、信号、数据类型;- 语句结构:顺序语句、并行语句;- 基本数字电路设计:组合逻辑电路、时序逻辑电路、状态机。

FPGA课程设计报告

FPG课程设计—256个8位计数器技术规范一、实现功能:用一个8×256的单口RAM完成256个8位计数器,计数器的初值分别为0-255,时钟频率为10MHz,计数器计数频率为5/256MHz。

具体功能描述如下:1、分频模块:时钟频率为10MHz,要实现计数器计数频率为5/256MHz,将其时钟频率进行2分频送入。

每来一个时钟,计数器计一个数。

第一个时钟来时,第一个计数器计1,此时,此计数器中的值变为1,其余的计数器中的值不变,以此类推,直到第256个时钟来时,第256个计数器计1,计数器中的值255变为0,以此类推,完成256个8位计数器,得到计数器计数频率即为5/256MHz。

2、8x256的单口RAM模块:定义一块内存为8x256的单口RAM,只有一条地址线,读写共用一个地址单元,当使能信号we=1时,写有效,可以将数据写入RAM,当使能信号we=0,读有效,可以将RAM中的值输出。

3、写模块:当时能信号we=1时,写有效,当clk的上升沿到来时,可以将数据写入寄存器,在时钟的上升沿和reset的下降沿时,如果reset=0,则地址addr=0,计数器a=0;否则,如果使能信号we=1,地址addr递加,当addr大于255时,addr=0,计数器a=a+1,将addr+a送入数据输入data_in.。

二、系统I/O管脚的描述:三、拟选用的FPGA类型:ep1cq240c8n总体设计方案一、整体设计方案我构想了如下两个总体设计方案:第一个总体设计方案:将10MHz的时钟clk_in通过分频器进行2分频送入系统clk,触发条件是clk的上升沿,这就可以实现计数器计数频率为5/256MHz。

由于是单口RAM,所以只有一条地址线,要么只能写入数据,要么只能读出数据。

因此,我先将所有的寄存器清零,将0—255这256个计数器初值分别送入256个寄存器,此时采用一个加法计数器完成。

然后每来一个时钟clk,计数器中的值计1,同时地址加1,即第一个寄存器的0变成1,地址加到第二个寄存器,以此类推,完成256个8位计数器的计数,并且将计数器的值读出。

fpga课程设计总结

fpga课程设计总结一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理、设计和应用。

具体来说,知识目标包括:了解FPGA的基本结构和工作原理;掌握FPGA的编程语言和设计方法;熟悉FPGA在数字信号处理、嵌入式系统等方面的应用。

技能目标包括:能够使用FPGA设计简单的数字系统;能够使用FPGA进行嵌入式系统设计;能够进行FPGA的编程和调试。

情感态度价值观目标包括:培养学生的创新意识和团队合作精神;使学生认识到FPGA技术在现代科技中的重要地位和应用价值。

二、教学内容根据课程目标,教学内容主要包括FPGA的基本原理、设计和应用。

具体包括以下几个方面:1. FPGA的基本结构和工作原理;2. FPGA的编程语言和设计方法;3. FPGA在数字信号处理、嵌入式系统等方面的应用;4. FPGA的设计工具和实验方法。

三、教学方法为了达到课程目标,我们将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

通过这些方法,我们将引导学生从不同角度理解和掌握FPGA技术和应用。

具体来说:1. 讲授法:通过讲解FPGA的基本原理、设计和应用,使学生掌握相关知识;2. 讨论法:通过分组讨论和课堂讨论,引导学生深入思考和理解FPGA技术;3. 案例分析法:通过分析实际案例,使学生了解FPGA在实际应用中的优势和局限;4. 实验法:通过FPGA实验,使学生掌握FPGA的设计和编程方法,提高实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将选择和准备以下教学资源:1. 教材:选用权威、实用的教材,为学生提供系统、全面的学习材料;2. 参考书:推荐一些与FPGA相关的参考书,拓展学生的知识视野;3. 多媒体资料:制作课件、视频等多媒体资料,提高课堂教学效果;4. 实验设备:准备FPGA实验设备,为学生提供实践操作的机会。

五、教学评估本课程的评估方式包括平时表现、作业和考试等。

平时表现主要评估学生的课堂参与、提问和讨论等情况,占总评的20%。

FPGA课程设计实验报告

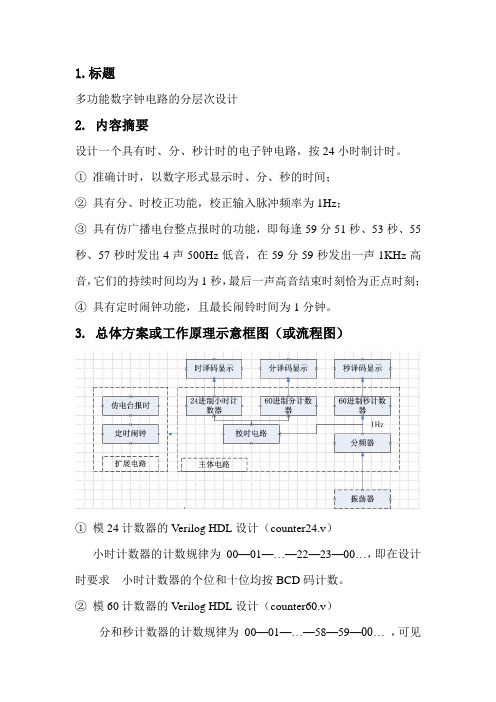

1.标题多功能数字钟电路的分层次设计2. 内容摘要设计一个具有时、分、秒计时的电子钟电路,按24小时制计时。

①准确计时,以数字形式显示时、分、秒的时间;②具有分、时校正功能,校正输入脉冲频率为1Hz;③具有仿广播电台整点报时的功能,即每逢59分51秒、53秒、55秒、57秒时发出4声500Hz低音,在59分59秒发出一声1KHz高音,它们的持续时间均为1秒,最后一声高音结束时刻恰为正点时刻;④具有定时闹钟功能,且最长闹铃时间为1分钟。

3. 总体方案或工作原理示意框图(或流程图)①模24计数器的Verilog HDL设计(counter24.v)小时计数器的计数规律为00—01—…—22—23—00…,即在设计时要求小时计数器的个位和十位均按BCD码计数。

②模60计数器的Verilog HDL设计(counter60.v)分和秒计数器的计数规律为00—01—…—58—59—00… ,可见个位计数器从0~9计数,是一个10进制计数器;十位计数器从0~5计数,是一个六进制计数器。

可以先分别设计一个十进制计数器模块(counter10.v)和一个六进制计数器模块(counter6.v),然后将这两个模块组合起来,构成六十进制计数器。

4. 顶层逻辑电路图组成及原理简单叙述仿真波形如下:分析结论:经仿真波形分析①走时正常;②能〝校时〞〝校分〞;③整点报时;④时段控制到位。

功能完全符合设计要求,可以下载。

5. 对应各模块功能仿真波形(数据分析)分析及结论1、小时计时模块:仿真波形:当小时的高四位为0、1时,小时的低四位为九时,在下一个时钟的上跳延来了之后,高四位加一;当小时的高四位为2,同时低四位为3时,小时的高低四位都清零。

实现从00到23的循环计数。

2、分钟计时模块:仿真波形:当分钟的高四位为0、1、2、3、4时,小时的低四位为九时,在下一个时钟的上跳延来了之后,高四位加一;当分钟的高四位为5时,同时低四位为9时,分钟的高低四位都清零,实现从00到59的循环计数。

fpga课程设计报告

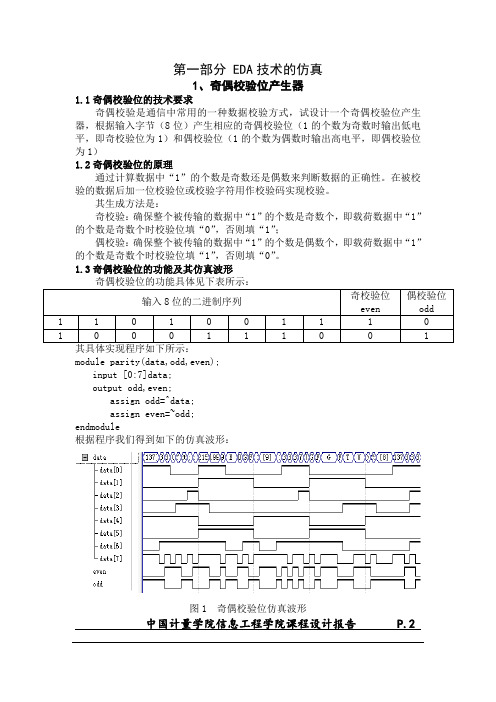

第一部分 EDA技术的仿真1、奇偶校验位产生器1.1奇偶校验位的技术要求奇偶校验是通信中常用的一种数据校验方式,试设计一个奇偶校验位产生器,根据输入字节(8位)产生相应的奇偶校验位(1的个数为奇数时输出低电平,即奇校验位为1)和偶校验位(1的个数为偶数时输出高电平,即偶校验位为1)1.2奇偶校验位的原理通过计算数据中“1”的个数是奇数还是偶数来判断数据的正确性。

在被校验的数据后加一位校验位或校验字符用作校验码实现校验。

其生成方法是:奇校验:确保整个被传输的数据中“1”的个数是奇数个,即载荷数据中“1”的个数是奇数个时校验位填“0”,否则填“1”;偶校验:确保整个被传输的数据中“1”的个数是偶数个,即载荷数据中“1”的个数是奇数个时校验位填“1”,否则填“0”。

1.3奇偶校验位的功能及其仿真波形奇偶校验位的功能具体见下表所示:输入8位的二进制序列奇校验位even偶校验位odd1 1 0 1 0 0 1 1 1 0 1 0 0 0 1 1 1 0 0 1其具体实现程序如下所示:module parity(data,odd,even);input [0:7]data;output odd,even;assign odd=^data;assign even=~odd;endmodule根据程序我们得到如下的仿真波形:图1 奇偶校验位仿真波形中国计量学院信息工程学院课程设计报告P.22、十六位数据选择器2.1数据选择器的原理在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

在数据选择器中,我们设定一个控制输入端ENA ,当ENA=1时,电路不能工作,输出Y=0;而当ENA=0时,电路才处于工作状态。

由于我们设计的是16选1数据选择器,因而其有4个数据控制端,即S0,S1,S2,S3,根据这4个控制端的状态有选择性的输出。

FPGA实验报告5篇

FPGA实验报告5篇第一篇:FPGA实验报告FPGA实验报告专业:XXX 姓名:XXX 学号:XX一:实验目的1.熟悉Modelsim和Quartus II软件的运行环境和使用2.熟练使用Quartus II仿真软件生成网表。

3.熟悉FPGA前仿真和后仿真的整个流程。

二:实验内容编写counter计数器,在Quartus II仿真软件中生成网表,再在Modelsim中进行后仿真。

三: 实验步骤1.在Modelsim编写源程序(counter计数器及激励),编译源文件,确保程序的正确性,并进行前仿真,生成波形图如下:附:源程序如下:module counter(q,clk,reset);input clk,reset;output [3:0] q;reg [3:0] q;always @(posedge reset or negedge clk)if(reset)q <= 4'b0;elseq <= q + 1;endmodule module top;reg CLK,RESET;wire [3:0] Q;counter c1(Q,CLK,RESET);initialCLK=1'b0;always#1 CLK=~CLK;initial$monitor($time,“Q=%d”,Q);initialbeginRESET=1'b1;#5 RESET=1'b0;#180 RESET=1'b1;end endmodule 2.新建文件夹,将源程序counter.v放进去。

然后启动Quartus II仿真软件,生成网表。

1).在【File】下拉菜单中选中New Project Wizard选项,出现对话框。

并指定工程工作目录、工程名称和顶层模块名,如图(a)所示。

2).添加(Add)counter.v文件。

如图(b)所示。

3).选择器件系列4).指定其它EDA工具,如图(d)所示。

FPGA课程设计实验报告

FPGA课程设计实验报告专业年级:学号:姓名:指导教师写:2014 年10 月8日目录1、标题及任务书2、关键词(不少于5个)3、内容摘要4、总体方案或工作原理示意框图(或流程图)5、顶层逻辑电路图组成、信号定义及原理简单叙述6、底层功能模块设计,逻辑抽象(定义input 和output),简述逻辑电路工作原理,并要求附有*.bdf和*.v文件及文件中语句注释7、对应各模块功能仿真波形(数据分析)分析及结论;8、选用芯片型号、定义芯片管脚号(列表格示意)及简述下载过程9、《课程设计》设计项目完成最终结论10、《课程设计》项目的特点和实用性11、心得体会或结束语1、标题及任务书;设计一个具有时、分、秒钟的电子计时器,用DE2-115开发板烧制,并能准确计时。

2、关键词(不少于5个);时、分、秒、调频、译码器3、内容摘要;24进制代码module con24(out,clk,clr,plus,minus);output[7:0] out;input clk,plus,minus,clr;reg [7:0] out;always @(posedge clk)beginif (!clr) out<=0;elsebegincase ({plus,minus})2'b10:beginif (out[7:4]==2&out[3:0]==3) out[7:0]<=0;elseif (out[3:0]==9)beginout[3:0]<=0;out[7:4]<=out[7:4]+1;endelse out[3:0]<=out[3:0]+1;end2'b11: out<=out;default:out<=0;endcaseendendendmodule60进制代码module con60(out,clk,clr,plus,minus); output[7:0] out;input clk,plus,minus,clr;reg [7:0] out;always @(posedge clk)beginif (!clr) out<=0;elsebegincase ({plus,minus})2'b10:beginif (out[3:0]==9)beginout[3:0]<=0;if (out[7:4]==5) out[7:4]<=0;elseout[7:4]<=out[7:4]+1;endelse out[3:0]<=out[3:0]+1;end2'b11: out<=out;default:out<=0;endcaseend分频代码//Divided_Frequency.vmodule divider(f,_500HzOut,_1KHzOut,ncR,CLOCK_50,s);input ncR,CLOCK_50,s;output _500HzOut,_1KHzOut,f;wire _1HzOut,_5HzOut;assign f=s?_5HzOut:_1HzOut;divn #(.WIDTH(26),.N(50000000))u0(.clk(CLOCK_50),.rst_n(ncR),.o_clk(_1HzOut));divn #(.WIDTH(17),.N(100000))u1(.clk(CLOCK_50),.rst_n(ncR),.o_clk(_500HzOut));divn #(.WIDTH(16),.N(50000))u2(.clk(CLOCK_50),.rst_n(ncR),.o_clk(_1KHzOut));divn #(.WIDTH(24),.N(10000000))u3(.clk(CLOCK_50),.rst_n(ncR),.o_clk(_5HzOut));Endmodule4、总体方案或工作原理示意框图(或流程图);5、顶层逻辑电路图组成、信号定义及原理简单叙述;工作原理:振荡器产生的稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准秒脉冲。

FPGA设计的报告课程设计

FPGA课程设计实验报告实验一:设计一个可控的100进制可逆计数器一、实验要求用DE2-115开发板下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用clr plus minus 功能0 ××复位为01 1 0 递增计数1 0 1 递减计数1 1 1 暂停计数二、关键词可控制、可逆、100进制、复位、暂停、递增、递减三、内容摘要module updown_count(qout,reset,clk,plus,minus);output[7:0] qout;/*定义一个8位的输出,其目的是低四位和高四位分别表示计数器的个位和十位。

*/input clk,plus,minus,reset;//定义四个输入,时钟,加计数,减计数和清零reg[7:0] qout;//qout的数据类型为寄存器型always @(posedge clk)//当clk上升沿到来时执行一遍下列程序beginif(!reset) qout<=0;//当reset为低电平时,计数器执行清零功能,否则跳过elsebegincase({minus,plus})//case语句模块,包含加,减和暂停四个模块2'b10:if (qout[3:0]==0)//判断个位是否为零,若不为零,跳到个位减一beginqout[3:0]<=9;//给个位赋值if(qout[7:4]==0) qout[7:4]<=9;//判断十位是否为零,并且给十位赋值elseqout[7:4]<=qout[7:4]-1;//由于个位赋9,相当于向十位借一,因而十位减一endelseqout[3:0]<=qout[3:0]-1;//个位减一/*这一部分是减计数模块,其思路是:首先判断个位是否为零,若为零,则执行后面的程序,个位直接赋9,并且十位减一;否则个位减一*/ 2'b01:if (qout[3:0]==9)//判断个位是否为9,否则跳到个位加一beginqout[3:0]<=0;//若上面个位为9判断成立,则给个位赋值if(qout[7:4]==9) qout[7:4]<=0;//判断十位是否为9,若为9,则赋0elseqout[7:4]<=qout[7:4]+1;//若十位不为9,十位加一endelseqout[3:0]<=qout[3:0]+1;//个位加一/*这一部分是加计数模块,首先判断个位是否为9,若不为9,个位加1;否侧,再判断十位是否为9,若为9,十位赋0,否侧十位加1。

fpga课程设计报告彩灯实验

fpga课程设计报告彩灯实验一、课程目标知识目标:1. 学生能理解FPGA的基本原理和结构,掌握彩灯实验相关的硬件描述语言(HDL)基础;2. 学生能描述数字电路设计的基本流程,并运用FPGA设计简单的数字电路;3. 学生掌握彩灯实验的原理,能够解释彩灯显示背后的逻辑控制过程。

技能目标:4. 学生能够运用所学知识,设计并实现一个基于FPGA的彩灯控制电路;5. 学生通过实际操作,提高问题解决能力和实验操作技能,包括电路调试和故障排查;6. 学生能够利用FPGA设计软件进行电路设计和仿真,并完成硬件的实现和测试。

情感态度价值观目标:7. 学生通过实验探究,培养对电子工程领域的兴趣,增强创新意识和实践能力;8. 学生在小组合作中,提升团队协作能力和沟通技巧,理解集体智慧的重要性;9. 学生能够在实验过程中,形成良好的工程伦理观念,认识到技术对社会发展的积极影响和责任。

二、教学内容本课程教学内容围绕FPGA的原理与应用,结合彩灯实验项目,进行以下组织和安排:1. FPGA基础知识:- 数字电路设计基础;- FPGA原理与结构;- 硬件描述语言(HDL)入门。

2. 彩灯实验原理与设计:- 彩灯显示原理;- FPGA在彩灯控制中的应用;- 彩灯控制电路设计流程。

3. 教学大纲与进度安排:- 第一周:FPGA基本原理学习,了解硬件描述语言;- 第二周:数字电路设计基础,学习彩灯显示原理;- 第三周:彩灯控制电路设计,进行FPGA编程与仿真;- 第四周:电路调试与测试,优化设计方案。

4. 教材关联内容:- 教材第3章:“数字电路设计基础”;- 教材第4章:“FPGA原理与结构”;- 教材第5章:“硬件描述语言(HDL)应用”;- 教材第6章:“数字电路设计实例”。

5. 实践环节:- 彩灯控制电路设计实践;- FPGA编程与仿真;- 电路调试与故障排查。

三、教学方法针对FPGA课程设计报告彩灯实验,采用以下多样化的教学方法,以激发学生的学习兴趣和主动性:1. 讲授法:- 对FPGA基本原理、数字电路设计基础和硬件描述语言(HDL)等理论知识进行系统讲解,为学生奠定扎实的理论基础。

FPGAverilog课程设计报告

FPGA verilog课程设计报告一、教学目标本课程旨在通过FPGA Verilog的学习,让学生掌握数字电路设计的基本原理和方法,学会使用Verilog硬件描述语言进行数字电路设计和仿真。

具体目标如下:1.理解FPGA的基本原理和结构。

2.掌握Verilog语言的基本语法和编程技巧。

3.熟悉数字电路的设计方法和流程。

4.能够使用Verilog语言编写简单的数字电路模块。

5.能够进行FPGA的配置和编程。

6.能够使用FPGA开发工具进行数字电路的仿真和测试。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.增强学生对新技术的敏感性和学习兴趣。

3.培养学生对工程实践的热爱和责任感。

二、教学内容本课程的教学内容主要包括FPGA的基本原理和结构、Verilog语言的基本语法和编程技巧、数字电路的设计方法和流程。

具体安排如下:第1-2课时:FPGA的基本原理和结构1.FPGA的定义和发展历程。

2.FPGA的内部结构和组成。

3.FPGA的配置和编程方法。

第3-4课时:Verilog语言的基本语法和编程技巧1.Verilog语言的基本数据类型和操作符。

2.Verilog语言的逻辑表达式和语句。

3.Verilog语言的模块结构和参数传递。

第5-6课时:数字电路的设计方法和流程1.数字电路的设计原则和技巧。

2.数字电路的设计流程和步骤。

3.数字电路的仿真和测试方法。

三、教学方法本课程采用讲授法、案例分析法和实验法相结合的教学方法。

1.讲授法:通过讲解和演示,让学生掌握FPGA和Verilog的基本知识和技巧。

2.案例分析法:通过分析具体的数字电路设计案例,让学生熟悉设计方法和流程。

3.实验法:通过动手实验,让学生亲手配置FPGA、编写Verilog代码并进行仿真测试,提高学生的实际操作能力。

四、教学资源1.教材:《FPGA Verilog设计与实践》。

2.参考书:《数字电路与FPGA设计入门》、《Verilog HDL入门与提高》。

FPGA课程设计报告

课程设计开课学期: 2014年—2015年下学期课程名称:FPGA课程设计学院:信息科学与工程学院专业:集成电路设计与集成系统班级:集成1201班学号:20121221077姓名:蔚任课教师:涛2015 年 7 月 21 日基于FPGA的数字钟设计摘要本文介绍一种利用现场可编程逻辑器件FPGA产生多功能数字钟的设计方案。

数字钟是采用数字电路实现对时、分、秒数字显示的计时装置,是人们日常生活中不可少的必需品。

本设计采用EDA技术,以硬件描述语言Verilog为系统逻辑描述手段设计文件,在Quartus II工具软件环境下,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统由时钟模块、控制模块、计时模块、数据译码模块、显示以及报时模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证。

开发板采用5CSEMA5F31C6N。

本次设计的多功能数字钟,具有时、分、秒的数码管显示功能,以24小时循环计数,具有整点报时功能,并有由按键输入进行数字钟的校时、清零、启停功能。

关键词:可编程逻辑器件 FPGA Verilog 数字钟 EDA技术AbstractThis paper introduces a kind of based on field programmable logic device FPGA design of multi-function digital clock, the digital clock is used in digital circuits, and seconds digital display timing device is in people's daily life necessities.This design using EDA technology, hardware description language Verilog logic system description method of design documents, in the Quartus II software environment, by all the basic modules together to build a a FPGA based digital clock.System consists of the clock module, control module, time module, data decoding module, display and broadcast module composition. Program after compilation and simulation design, programmable logic device to download verification. Development board using the multi-function digital clock 5CSEMA5F31C6N. this design, with time, points, the second digital tube display, to a 24-hour cycle count, with the whole point timekeeping function and input by the key of the school of digital clock, clear, open and stop function.Key words: programmable logic device FPGA Verilog Digital cloc EDA Technology目录前言 (1)第一章多功能数字钟概述 (2)1.1 数字钟的构成 (2)1.3 计时电路 (3)1.4 异步清零电路 (4)1.5 校时、校分功能电路 (4)第二章 FPGA简介 (5)2.1 现场可编程逻辑门阵列FPGA (5)2.2 FPGA简介 (6)2.3 Quartus II软件简介 (6)第三章设计方案 (7)第四章设计实现 (9)4.1 顶层模块 (9)4.2 新建工程项目 (9)4.3 选择芯片 (10)4.4 子模块 (12)4.4.1 分频器 (12)4.4.2 控制器和计数器 (13)4.4.3 显示器 (16)4.5 元件封装 (21)4.6 引脚的绑定和设置 (21)4.7 之后再进行一次编译运行。

FPGA课程设计课程设计报告

《CPLD/FPGA课程设计》课程设计报告系别:信息科学与技术系专业班级:通信工程08XX班学生姓名:XXXX指导教师:**(课程设计时间:2011年9月5日——2011年9月16日)华中科技大学武昌分校目录1 课程设计目的 (3)2课程设计题目描述和要求 (3)3课程设计报告内容 (4)3.1 硬件设计 (4)3.1.1 EP1C6Q240C8管脚结构图 (4)3.1.2 液晶屏的硬件连接电路设计 (4)3.1.3 外围电路的设计 (5)3.2 软件设计 (6)3.2.1 功能需求分析 (6)3.2.2 模块划分 (6)3.2.4 模块之间连接组成系统 (11)3.2.5 管教绑定 (11)3.2.6 下载 (11)4总结 (12)参考文献 (12)1 课程设计目的本课程属专业课程设计。

EDA课程设计是继“数字电路技术基础”课之后开出的实践教学环节。

其目的是训练学生综合运用学过的数字电路的基本知识,独立设计比较复杂的数字电路的能力。

设计建立在硬件和软件两个平台的基础上。

硬件平台是FPGA综合实验箱,根据不同题目设计的数字电路下载到一片可编程逻辑器件上,实验结果可在实验仪上实现。

软件平台是ALTERA公司的QUARTUSII。

通过课程设计,学生要掌握使用EDA工具设计数字电路的方法,包括图形设计输入、编译、软件仿真、下载和硬件仿真等全过程。

2课程设计题目描述和要求设计题目:综合数字钟的设计与实现;设计内容:用ALTERA公司的QUARTUSII软件和FPGA综合实验平台设计一个数字时钟,能进行正常的时,分,秒计时功能,用1块液晶屏显示24小时,60分,60秒;能利用按键实现“校时”“校分”“闹钟”功能。

3课程设计报告内容3.1 硬件设计3.1.1 EP1C6Q240C8管脚结构图3.1.2 液晶屏的硬件连接电路设计管脚号管脚名称管脚功能描述FPGA接口1VSS电源地GND 2VDD电源正+5V 3NC空脚不接4RS(CS)RS=“H”, 表示DB7~DB0 为显示数据。

fpga实训课程设计

fpga实训课程设计一、课程目标知识目标:1. 掌握FPGA的基本原理与结构,理解数字电路设计的基本流程;2. 学习并运用硬件描述语言(如VHDL/Verilog)进行数字电路设计与仿真;3. 理解FPGA实训项目中涉及的算法与逻辑设计,如计数器、状态机、数字信号处理等。

技能目标:1. 能够独立完成FPGA开发环境的搭建与基本操作;2. 培养学生利用硬件描述语言进行数字电路设计的能力,能够对设计进行调试与优化;3. 培养学生团队协作能力,通过项目实践,学会分析问题、解决问题,提高创新能力。

情感态度价值观目标:1. 激发学生对数字电路设计及FPGA技术的兴趣,培养良好的学习习惯;2. 培养学生面对困难与挑战时,具备积极的心态和坚持不懈的精神;3. 强化学生的工程意识,培养严谨、求实的科学态度,提高学生的职业素养。

课程性质:本课程为实践性较强的课程,注重培养学生动手能力与创新能力。

学生特点:学生具备一定的电子技术基础和编程能力,对新技术充满好奇。

教学要求:结合课程特点和学生特点,通过理论教学与实践操作相结合的方式,使学生在掌握基本知识的基础上,提高实际应用能力。

将课程目标分解为具体的学习成果,以便在教学过程中进行有效的设计与评估。

二、教学内容1. FPGA基本原理与结构:介绍FPGA的发展历程、基本组成、工作原理,以及FPGA在设计中的优势与应用领域。

教材章节:第一章 FPGA概述2. 硬件描述语言基础:学习Verilog/VHDL基本语法,掌握数字电路设计的基本描述方法。

教材章节:第二章 硬件描述语言基础3. FPGA开发环境搭建:学习FPGA开发工具(如ISE、Quartus等)的使用,掌握FPGA设计流程。

教材章节:第三章 FPGA开发环境与工具4. 数字电路设计与仿真:学习并实践简单的数字电路设计,如门电路、组合逻辑电路、时序逻辑电路等。

教材章节:第四章 数字电路设计与仿真5. 实践项目:开展FPGA实践项目,涵盖计数器、状态机、数字信号处理等应用。

大学生fpga课程设计

大学生fpga课程设计一、课程目标知识目标:1. 掌握FPGA的基本原理、结构及其在设计中的应用;2. 学习数字电路设计的基本流程,理解硬件描述语言(HDL)的编程规范;3. 熟悉FPGA开发环境及相关软件工具的使用;4. 了解FPGA在信号处理、通信等领域的应用案例。

技能目标:1. 能够运用HDL语言进行数字电路设计和仿真;2. 掌握FPGA硬件编程和配置方法,具备基本的FPGA调试能力;3. 能够根据实际需求,设计并实现简单的FPGA应用系统;4. 提高团队协作和项目实践能力,具备分析和解决实际问题的能力。

情感态度价值观目标:1. 培养学生对FPGA技术及其应用的兴趣,激发学生的学习热情和探索精神;2. 培养学生严谨的科学态度,养成良好的实验习惯和工程素养;3. 增强学生的创新意识,鼓励学生积极参与科技竞赛和实践活动;4. 培养学生的团队合作精神,提高沟通与交流能力。

本课程针对大学生FPGA课程设计,结合课程性质、学生特点和教学要求,明确了具体、可衡量的课程目标。

通过本课程的学习,使学生能够掌握FPGA技术的基本知识和技能,培养创新意识和实践能力,为今后从事相关领域的研究和工作打下坚实基础。

二、教学内容1. FPGA基本原理与结构:介绍FPGA的发展历程、基本组成、工作原理及其优势特点,结合教材第一章内容,使学生建立FPGA的基本概念。

2. 硬件描述语言(HDL):讲解VHDL和Verilog HDL的基本语法、编程规范以及设计流程,结合教材第二章内容,使学生掌握HDL语言的使用方法。

3. FPGA开发环境及工具:学习FPGA开发环境(如ISE、Quartus等)的安装与配置,介绍常用软件工具的功能和操作方法,结合教材第三章内容,使学生熟悉FPGA开发流程。

4. 数字电路设计实例:分析并实践简单的数字电路设计实例,如组合逻辑电路、时序逻辑电路等,结合教材第四章内容,提高学生的实际设计能力。

5. FPGA应用系统设计:学习FPGA在信号处理、通信等领域的应用案例,结合教材第五章内容,使学生了解FPGA在实际工程中的应用。

FPGA课程设计实验报告

FPGA课程设计实验报告1. 引言本报告是针对FPGA课程设计实验的实验结果进行总结和分析。

该实验旨在通过设计一个FPGA应用电路,加深对FPGA的理论知识的理解,并提高对FPGA设计流程的掌握能力。

本实验采用Verilog硬件描述语言进行FPGA设计。

2. 实验目的本实验的主要目的有以下几点: - 通过设计一个FPGA应用电路,提高对FPGA的理论知识的理解。

- 熟悉FPGA设计流程,掌握使用Verilog语言进行FPGA设计的方法。

- 掌握FPGA设计的仿真、综合和下载的流程。

- 提高对FPGA设计中时序约束的理解和处理能力。

3. 实验环境和工具本实验的实验环境和工具如下: - FPGA开发板:Xilinx Spartan-6 - FPGA设计工具:Xilinx ISE Design Suite - 仿真工具:Xilinx ISIM4. 实验设计本实验设计了一个简单的FPGA应用电路,实现了一个4位计数器。

该计数器能够从0递增到15,然后重新从0开始计数。

计数器的递增频率可通过外部开关调节,同时采用七段数码管显示当前计数器的值。

4.1 电路结构实验设计的电路结构如下所示:电路结构图电路结构图该电路包含以下模块: - 时钟模块:用于提供递增计数器的时钟信号。

- 计数器模块:实现了一个4位计数器,并能够从0递增到15。

- 控制模块:用于控制外部开关的输入,并将结果输出到七段数码管的控制端口。

- 七段数码管模块:用于将计数器的值以七段数码管的形式显示出来。

4.2 Verilog代码根据电路结构图,我们编写了如下的Verilog代码:module counter(input wire clk,input wire reset,output wire [6:0] seg,output wire seg_en);reg [3:0] count;always @(posedge clk or posedge reset)beginif (reset)count <= 4'b0000;else if (count == 4'b1111)count <= 4'b0000;elsecount <= count + 1;endassign seg = count;assign seg_en = 1'b1;endmodule5. 实验过程5.1 仿真在进行实际FPGA设计之前,我们首先对设计的Verilog代码进行仿真,以验证其功能的正确性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Shenyang Agricuttural UniversityFPGA课程设计报告题目:基于CPLD的1602字符液晶显示系统设计院系: _________ 信息与电气工程学院___________ 班级: __________________ 电子信息工程_________ 学号:____________________________________________ 学生姓名:_________________________________________ 指导教师:_________________________________________ 成绩:____________________________________________2011年7月基于CPLD勺1602字符液晶显示系统设计一.设计题目:基于CPLD勺1602字符液晶显示系统设计二•设计要求技术指标:要求用1602液晶显示字符;显示内容:学号+英文姓名;显示方式:流动显示,开关控制字符流动速度及方向;具有暂停和清屏的功能;三•设计平台:QUARTUSII 6.0软件MARS-1270 CPLD 1602 液晶四•设计思路与设计步骤:1.1602液晶指令介绍:要想控制1602液晶显示字符,首先需要弄清楚1602有那些可控管脚,有哪些控制命令,如何控制其显示,如何控制其移动及如何控制其移动速度及方向等,下面首先介绍一下我所要用的指令及管脚等。

(1)接口说明:(2)基本操作时序:A. 读状态:输入:RS=L RW=H,E=H,输出:DB0--DB7= 犬态字B. 写指令:输入:RS=L RW=L,E下降沿脉冲,DBO--DB7指令码,输出:无C. 读数据:输入:RS=H RW=H,E=H俞出: DB0--DB7教据D. 写数据:输入:RS=H RW=L,E下降沿脉冲,DBO--DB7数据,输出:无(3)指令集及其设置说明:A.清屏指令:功能:<1>清除液晶显示器即将DDRAM勺内容全部填入"空白"的ASCII码20H; <2> 光标归位,即将光标撤回液晶显示屏的左上方;<3> 将地址计数器(AC)的值设为0。

B.进入设置模式指令:功能:设定每次定入1位数据后光标的移位方向,并且设定每次写入的一个字符是否移动。

参数设定的情况如下所示:位名设置I/D 0= 写入新数据后光标左移1= 写入新数据后光标右移S 0= 写入新数据后显示屏不移1=写入新数据后显示屏整体右移1字符C.显示开关控制指令:位名设置D 0= 显示功能关1=显示功能开C 0= 无光标 1= 有光标B0=光标闪烁 1= 光标不闪烁D.设定显示屏或光标移动方向指令:功能: 使光标移位或使整个显示屏幕移位。

参数设定的情况如S/C R/L 设定情况0 0光标左移1格,且AC 值减1 0 1光标右移1格,且AC 值加11 0显示器上字付全部左移一格, 但光标不动 1 1 显示器上字符全部右移一格, 但光标不动 E.功能设定指令:功能:设定数据总线位数、显示的行数及字型。

参数设定的情况如下: 位名设置DL 0=数据总线为4位 1= 数据总线为8位 N 0= 显示1行1=显示2行F 0=5 X 7点阵/每字符 仁5 X 10点阵/每字符F.设定CGRA 地址指令:功能:设定下一个要存入数据的CGRA 的地址。

DB5DB4DB3为字符号,也就是你将来要显示该字符时要用到的字符地址。

(000~111)(能定义八个字符) DB2DB1DB0 为行号。

(000~111)(八行)G.设定DDRAM地址指令;功能:设定下一个要存入数据的DDRA的地址H.数据写入DDRA或CGRAI指令:功能:<1>将字符码写入DDRAM以使液晶显示屏显示出相对应的字符; <2> 将使用者自己设计的图形存入CGRA。

DB7DB6DB5 可为任何数据,一般取“ 000”DB4DB3DB2DB1DB0对应于每行5点的字模数据。

2.设计流程:弄懂1602中各种管脚及其控制方法以及各种指令的指令码后,就可以进行程序的编写了,首先整理一下编写流程::初始化3.设计源程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; en tity lcd_1602 isPort ( clk : in std_logic;reset:i n std_logic; lcdrs : out std_logic; lcdrw : out std_logic; lcde n :buffer std_logic;-- data : out std 」o gic_vector(7 dow nto 0); key1: in std_logic;-- 拨码开关控制移动与不动;key2: in std 」o gic);end lcd_1602;Architecture Behavioral of lcd_1602 isType state is(set_ qingpin g,set_ no busy,set_cursor,set_switch,set_ddram,write_data,s et_ddram1,write_data1,set_ddram2,write_data2,set_ddram3,write_data3,s et_ddram4,write_data4,set_ddram5,write_data5, set_ddram6,write_data6, set_ddram7,write_data7,set_ddram8,write_data8,set_ddram9,write_data9, set_ddram10,write_data10,set_ddram11,write_data11,set_ddram12,write_d ata12,set_ddram13,write_data13,set_ddram14,write_data14,set_ddram15,write_data15,set_ddram17,write_data17,set_ddram16,write_data16,set_ddr am18, write_data18,set_ddram19,write_data19,set_ddram20,write_data20,set_ddram21,write_data21,set_ddram22,write_data22,set_ddram23,write_d ata23,set_cgram,write_cgram,set_ddram24,write_data24,set_ddram25,writ e_data25,shift_cur,shift_display);-- 定义各种状态 type ram2 is array(0 to 7) of std_logic_vector(7 dow nto 0);con sta nt cgram:ram2:=(("00011111"),("00000100"),("00000100"),("00011111"),("00000100"),("00000100"),("00000100"),("00011111")); --把“王”字字模写入数组;sig nal curre nt_state:state;sig nal clkc nt: std_logic_vector(18 dow nto 0);Con sta nt divcnt:std_logic_vector(18 dow nto 0):="1111001110001000000"; sig nal clkdiv: std_logic; sig nal tc_clkc nt: std_logic; sig nal clk_int: std_logic; sig nal clkdiv2: std_logic; sig nal clkdiv3: std_logic; sig nal clkdiv6: std_logic ;beg in--读或写指令|数据控制端--读|写控制端 使能端ledrw <= 'O';-- 读写控制端设为写有效process(clk,reset)Beg inif(reset='O')the nclkcnt<="OOOOOOOOOOOOOOOOOOO";elsif(clk'eve nt and clk='1')the nif(clkc nt=divc nt)the nclkcnt<="OOOOOOOOOOOOOOOOOOO";elseclkcnt<=clkc nt+1;-- 对系统时钟进行分频使其工作周期为12.5msend if;end if;end process ;tc_clkcnt<='1' whe n clkc nt=divcnt else 'O'; --tc_clkcnt 为12.5msprocess(tc_clkc nt,reset)begi nif(reset='O')the nclkdiv<='O';elsif(tc_clkc nt'eve nt and tc_clkcnt='1')the nclkdiv<=not clkdiv;-- 进一步分频使clkdiv=2*12.5ms;end if;end process;process(clkdiv,reset)begi nif(reset='O')the nclk_i nt<='O';elsif(clkdiv'eve nt and clkdiv='1')the nclk_int<= not clk_int;-- 再进一步分频使clk_int=4*12.5msend if;end process;process(clk_i nt,reset)begi nif(reset='O')the nclkdiv2<='0';-- 再进一步分频使clkdiv2=8*12.5mselsif(clk_i nt'eve nt and clk_i nt='1')the nclkdiv2<= not clkdiv2;end if;end process;process(clkdiv2,reset)beg inif(reset='O')the n clkdiv3<='0';-- 再进一步分频使clkdiv3=16*12.5mselsif(clkdiv2'eve nt and clkdiv2='1')the nclkdiv3<= no t clkdiv3;end if;end process;process(clkdiv3,reset)begi nif(reset='0')the n clkdiv6<='0';-- 还是进一步分频使clkdiv6=32*12.5mselsif(clkdiv3'eve nt and clkdiv3='1')the nclkdiv6<= n ot clkdiv6;end if;end process;process(clkdiv3,reset)begi nif(reset='0')the nlcde n<='0';elsif(clkdiv3'eve nt and clkdiv3='0')the nlcde n<= not lcde n;-- 设置使能信号频率end if;end process;附注:进行多次分频的目地是为了使字符显示速度及移动速度等合适,便于观察。