《 数字系统设计 》试卷含答案

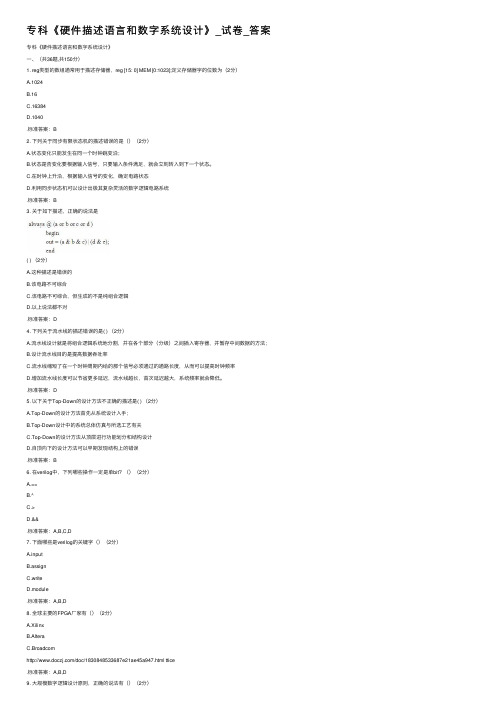

专科《硬件描述语言和数字系统设计》_试卷_答案

专科《硬件描述语⾔和数字系统设计》_试卷_答案专科《硬件描述语⾔和数字系统设计》⼀、(共36题,共150分)1. reg类型的数组通常⽤于描述存储器,reg [15: 0] MEM [0:1023];定义存储器字的位数为(2分)A.1024B.16C.16384D.1040.标准答案:B2. 下列关于同步有限状态机的描述错误的是()(2分)A.状态变化只能发⽣在同⼀个时钟跳变沿;B.状态是否变化要根据输⼊信号,只要输⼊条件满⾜,就会⽴刻转⼊到下⼀个状态。

C.在时钟上升沿,根据输⼊信号的变化,确定电路状态D.利⽤同步状态机可以设计出极其复杂灵活的数字逻辑电路系统.标准答案:B3. 关于如下描述,正确的说法是( ) (2分)A.这种描述是错误的B.该电路不可综合C.该电路不可综合,但⽣成的不是纯组合逻辑D.以上说法都不对.标准答案:D4. 下列关于流⽔线的描述错误的是( ) (2分)A.流⽔线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插⼊寄存器,并暂存中间数据的⽅法;B.设计流⽔线⽬的是提⾼数据吞吐率C.流⽔线缩短了在⼀个时钟周期内给的那个信号必须通过的通路长度,从⽽可以提⾼时钟频率D.增加流⽔线长度可以节省更多延迟,流⽔线越长,⾸次延迟越⼤,系统频率就会降低。

.标准答案:D5. 以下关于Top-Down的设计⽅法不正确的描述是( ) (2分)A.Top-Down的设计⽅法⾸先从系统设计⼊⼿;B.Top-Down设计中的系统总体仿真与所选⼯艺有关C.Top-Down的设计⽅法从顶层进⾏功能划分和结构设计D.⾃顶向下的设计⽅法可以早期发现结构上的错误.标准答案:B6. 在verilog中,下列哪些操作⼀定是单bit?()(2分)A.==B.^C.>D.&&.标准答案:A,B,C,D7. 下⾯哪些是verilog的关键字()(2分)A.inputB.assignC.writeD.module.标准答案:A,B,D8. 全球主要的FPGA⼚家有()(2分)A.XilinxB.AlteraC.Broadcom/doc/1830848533687e21ae45a947.html ttice.标准答案:A,B,D9. ⼤规模数字逻辑设计原则,正确的说法有()(2分)A.异步设计原则B.组合时序电路分开原则C.⾯向RTL的原则D.先电路后代码的原则.标准答案:B,C10. 下⾯有关SRAM,DRAM的叙述,正确的有()(2分)A.DRAM存储单元的结构⽐SRAM简单B.DRAM⽐SRAM成本⾼C.DRAM⽐SRAM速度快D.DRAM要刷新,SRAM不刷新.标准答案:A,D11. 阻塞赋值与⾮阻塞赋值的差别及其各⾃的使⽤环境。

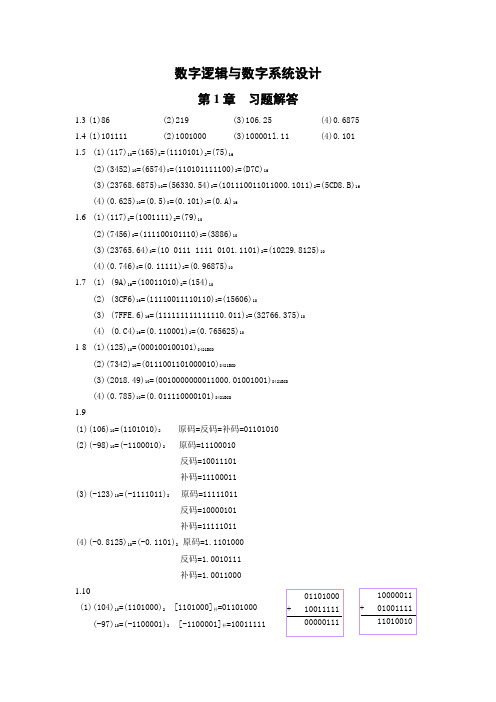

数字逻辑与数字系统设计习题参考答案

(4)(0.785)10=(0.011110000101)8421BCD

1.9

(1)(106)10=(1101010)2原码=反码=补码=01101010

(2)(-98)10=(-1100010)2原码=11100010

不考虑无关项,化简后的表达式:

F=

按考虑无关项化简结果绘制的逻辑电路习题4.10图(a)所示:

习题4.10图(a)

按不考虑无关项化简结果绘制的逻辑电路如习题4.10图(b)所示

习题4.10图(b)

4.11解:这是一个优先编码器的问题,设特快为A,直快为B,慢车为C,没有开车要求,输出为0,若A要求开车则输出,1,B要求开车输出为2,C要求开车输出3,根据A-B-C的优先顺序列功能表如下:

4.6解:根据题意:F= ,所以,可绘制电路如习题4.6图所示

习题4.6图

4.7解:根据题意:F= ,所以,可绘制电路如习题4.7图所示

习题4.7图

4.8解:

习题4.8图

4.9解:根据题意,三个变量有两个为1的卡诺图如习题4.9图(a)所示:

习题4.9图(a)

由此可列出逻辑表达式为:F= ,根据逻辑表达式可绘制逻辑电路习题4.9图(b)所示:

输入

输出

A

B

C

T1

T0

0

0

0

0

0

0

0

1

1

1

0

1

0

1

0

0

1

1

1

0

1

0

0

0

1

1

0

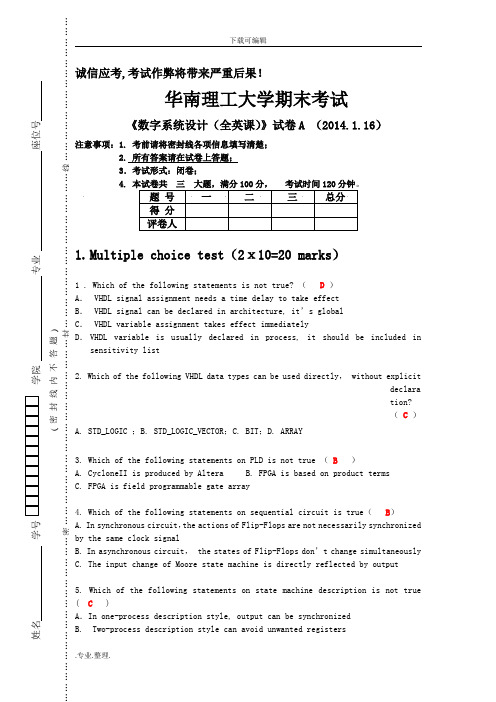

华南理工大学_2013年_数字系统设计(全英)试题_A卷

C. Two-process description style consumes more resources than one-process description6. Which of the following statements on metastability is true ( B )A. In sequential circuit, metastability doesn’t occur if either the set-up time requirement or the holding time requirement is met.B. Metastability doesn’t negatively impact the system if the metastable output resolves to the normal state before it is captured by the next register.C. Metastability usually occurs in synchronous circuit.7. Which of the following statements on VHDL signal is not true(C)A . VHDL signal is usually synthesized as node or wire.B. In VHDL entity, port is considered as signal by defaultC. Assignment to the same signal in different processes can be synthesized, but only one signal assignment takes effect.8. For state encoding in state machine, which of the following scheme is more simple for decoding at the prices of more Flip-Flops in encoding: ( A)A. one hot codeB. Natural binary codeC.Gray code9. Which of the following statements on VHDL case statement is not true( B )A. Each branch of case statement should be corresponding to one or several possible values of the evaluated expression.B. Statement “WHEN OTHERS=>NULL” must be included in case statementC. In execution of case statement,only one branch is selected10. Which of the following statements is not concurrent ?( B )A. process statementB.CASE statementC. component instantiationD.WHEN…ELSE…statement2. Short answer questions( 5ⅹ4=20 marks)1、Please specify the basic components of ASM chart, particularly, explain what a state is.Basic components of ASM chart: state box, decision box, and conditional output box.One state is more than a state box, conditional output box, or decision box can also be a part of the state. A state represents the system state during one clock cycle, indicating the operations to be done in the state.2、What is the difference between sequential logic circuit and combinational logic circuit?Combinational circuit: changes in inputs are immediately reflected by changes in output. The stable output depends on the current input only.The outputs of a system depend on past values of its inputs as well as the present state values.(depend on both present state and history state)3、Please specify the basic structure of sequential logic circuitStructure: it is composed of combinational logic gates, and memory components such as Flip-flop, registers.4、Please describe the concept of set-up time and holding time.Set up time:To ensure reliable operation, the input to a register must be stable for a minimum time before the clock edge (register setup time or tSU). if the time is not long enough, reliable operation can not be guaranteed.Hold time:To ensure reliable operation, the input to a register must be stable for a minimum time after the clock edge (register hold time or tH). if the time is not long enough, reliable operation can not be guaranteed.3、Comprehension & design ( 60 marks)1、Using VHDL, Please describe a tri-state multiplexer (MUX) according to theinput outputLIBRARY IEEE;USE IEEE.std_logic_1164.ALL;ENTITY MUX ISPORT(oe, a, b, sel: in std_logic; y: out std_logic); END MUX;ARCHITECTURE BEHAV OF MUX IS BEGINPROCESS(oe,a,b,sel)BEGINIf oe=’1’ thenif sel=’0’ theny<=a;elsey<=b;end if;elsey<=’Z’;end if;END PROCESS:END ARCHITECTURE;2、As a part of testbench, please describe the following stimuli (6 marks)…Signal S1:std_logic;Signal S2:std_logic;…ProcessBeginS1<=’0’;Wait for 10 ns;S1<=’1’;Wait for 5 ns;S1<=’0’;Wait for 10 ns;End process;ProcessBeginS1<=’0’;Wait for 5 ns;S1<=’1’;Wait for 15 ns;S1<=’0’;Wait for 5 ns;End process;3、Please draw the RTL diagram for the following VHDL codes(5 marks)entity var_sig isport(data : in bit_vector (1 downto 0) ; clk : in bit; z : out bit);constant k1 : bit_vector := “01”;constant k2 : bit_vector := “10”;end var_sig;architecture A of var_sig isbeginvar : processvariable a1 , a2 :bit_vector (1 downto 0);variable a3 : bit;beginwait until clk = ‘1’ and clk’ event ;a1 := data and k1;a2 := data and k2;a3 := a1(0) or a2(1);z <= a3;end process var;end A4、Please complete the waveforms according to the following VHDL codes(6 marks)Library ieee;Use ieee.std_logic_1164.all;Entity D_latch isport ( D, Enable: in std_logic ;Q1,Q2: out std_logic );End D_latch;Architecture behav of D_latch isBeginprocess(D, Enable)beginif (Enable=‘1’) then Q1<=D;end if;end process;process(Enable)beginif (Enable=‘1’) then Q2<=D;end if;end process;End behav;5、Design a 4-bit ALU (Arithmetic Logic Unit), which can complete the following operations on 4-bit inputs a and b:1)Mode 1: Addition (a +b)Mode 2: OR (a or b)Mode 3: AND (a and b)Mode 4: XOR (a xor b)3) The addition operation should have carried-in bit and carried-out bitQuestions: (13 marks)1.Please indicate the inputs and outputs of the ALUInputs: a, b, M0,M1,ciOuput: s, co2.Please finish VHDL design of ALU,including entity and architecturedescription.library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity ALU isport ( a, b :in std_logic_vector(3 downto 0);m0, m1, ci: in std_logic;s: out std_logic_vector(3 downto 0);co: in std_logic;);end ALU;architecture behav of ALU issignal mode : std_logic_vector(1 downto 0);beginmode<=m1&m0;processvariable temp1, temp2, temp3: std_logic_vector(4 downto 0);beginif mode=”00” thentemp1:=0&a;temp2:=0&b;temp3:= temp1+ temp2+ci;co=temp3(4);s<=temp3(3 downto 0);elsif mode=”01” thens<=a or b;elsif mode=”10” thens<=a and b;elsif mode=” 11” thens<=a xor b;elses<=”ZZZZ”;co<=’Z’;end if;end process;end architecture;6. Please read each piece of the following codes carefully. Does each of them have the same circuit behavior like the following circuit diagram? If no, please give the reasons. (9 marks)(a)processbeginwait until rising_edge(clk);d <= not c;c <= a and b;end process;(b)processbeginwait until rising_edge(clk);c1 <= a and b;c2 <= not c1;d <= c2;end process;(c)processbeginwait until rising_edge(clk);c1 <= a and b;d <= c2;end process;process (c1)beginc2 <= not c1;end process;(a)yes:(b)no: extra register is introduced.(c) yes7、Design a serial data transmitter (串行数据发送器)。

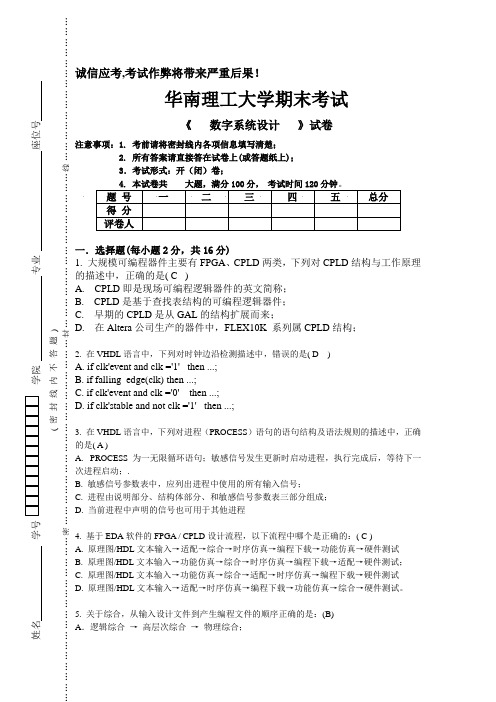

《 数字系统设计 》试卷含答案

,考试作弊将带来严重后果!华南理工大学期末考试《数字系统设计》试卷1. 考前请将密封线内各项信息填写清楚;所有答案请直接答在试卷上(或答题纸上);.考试形式:开(闭)卷;(每小题2分,共16分)大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理( C )CPLD即是现场可编程逻辑器件的英文简称;CPLD是基于查找表结构的可编程逻辑器件;早期的CPLD是从GAL的结构扩展而来;在Altera公司生产的器件中,FLEX10K 系列属CPLD结构;在VHDL语言中,下列对时钟边沿检测描述中,错误的是( D )then ...;then ...;then ...;在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确( A )PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一.敏感信号参数表中,应列出进程中使用的所有输入信号;进程由说明部分、结构体部分、和敏感信号参数表三部分组成;当前进程中声明的信号也可用于其他进程基于EDA软件的FPGA / CPLD设计流程,以下流程中哪个是正确的:( C )原理图/HDL文本输入→适配→综合→时序仿真→编程下载→功能仿真→硬件测试原理图/HDL文本输入→功能仿真→综合→时序仿真→编程下载→适配→硬件测试;原理图/HDL文本输入→功能仿真→综合→适配→时序仿真→编程下载→硬件测试原理图/HDL文本输入→适配→时序仿真→编程下载→功能仿真→综合→硬件测试。

关于综合,从输入设计文件到产生编程文件的顺序正确的是:(B).逻辑综合→高层次综合→物理综合;B. 高层次综合→逻辑综合→物理综合;C. 物理综合→逻辑综合→高层次综合;D. 高层次综合→逻辑综合→时序综合;6. 进程中的信号赋值语句,其信号更新是( C )A. 按顺序完成;B. 比变量更快完成;C. 在进程的挂起时完成;D. 都不对。

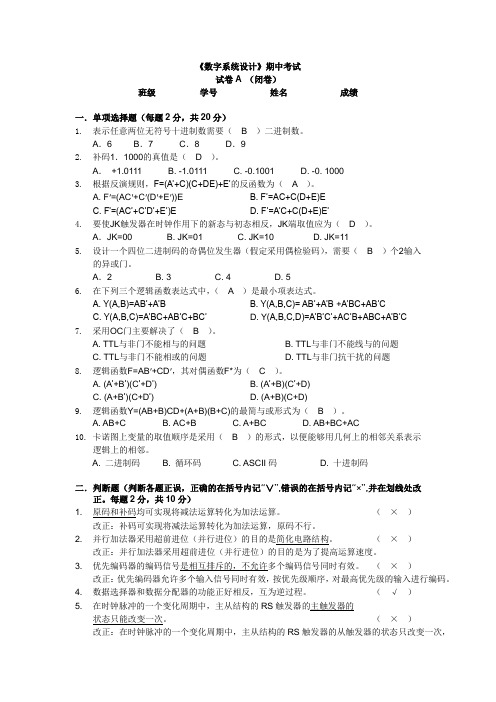

数字系统设计 期中考试试卷 及答案

《数字系统设计》期中考试试卷A (闭卷)班级学号姓名成绩一.单项选择题(每题2分,共20分)1.表示任意两位无符号十进制数需要( B )二进制数。

A.6 B.7 C.8 D.92.补码1.1000的真值是( D )。

A.+1.0111 B. -1.0111 C. -0.1001 D. -0. 10003.根据反演规则,F=(A’+C)(C+DE)+E’的反函数为( A )。

A. F'=(AC'+C'(D'+E'))EB. F’=AC+C(D+E)EC. F'=(AC’+C’D’+E’)ED. F’=A’C+C(D+E)E’4.要使JK触发器在时钟作用下的新态与初态相反,JK端取值应为( D )。

A.JK=00 B. JK=01 C. JK=10 D. JK=115.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要( B )个2输入的异或门。

A.2 B. 3 C. 4 D. 56.在下列三个逻辑函数表达式中,( A )是最小项表达式。

A. Y(A,B)=AB’+A’BB. Y(A,B,C)= AB’+A’B +A’BC+AB’CC. Y(A,B,C)=A’BC+AB’C+BC’D. Y(A,B,C,D)=A’B’C’+AC’B+ABC+A’B’C7.采用OC门主要解决了( B )。

A. TTL与非门不能相与的问题B. TTL与非门不能线与的问题C. TTL与非门不能相或的问题D. TTL与非门抗干扰的问题8.逻辑函数F=AB'+CD',其对偶函数F*为( C )。

A. (A’+B’)(C’+D’)B. (A’+B)(C’+D)C. (A+B’)(C+D’)D. (A+B)(C+D)9.逻辑函数Y=(AB+B)CD+(A+B)(B+C)的最简与或形式为( B )。

A. AB+CB. AC+BC. A+BCD. AB+BC+AC10.卡诺图上变量的取值顺序是采用( B )的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

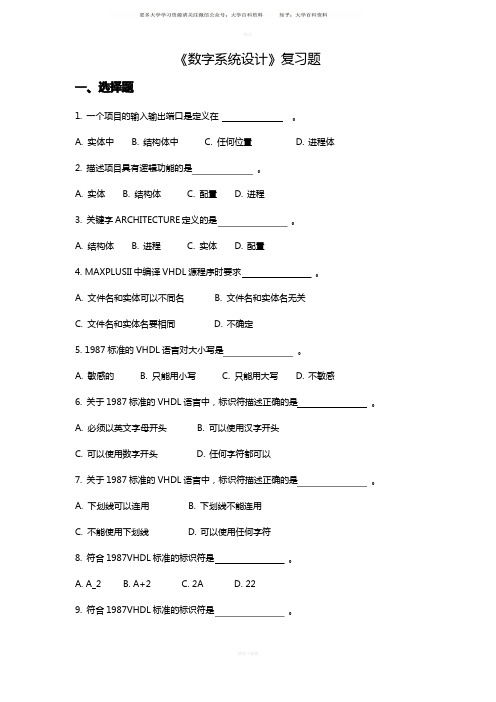

《数字系统设计》总复习题

《数字系统设计》复习题一、选择题1.一个项目的输入输出端口是定义在。

A.实体中B.结构体中C.任何位置D.进程体2.描述项目具有逻辑功能的是。

A.实体B.结构体C.配置D.进程3.关键字ARCHITECTURE定义的是。

A.结构体B.进程C.实体D.配置4. MAXPLUSII中编译VHDL源程序时要求。

A.文件名和实体可以不同名B.文件名和实体名无关C.文件名和实体名要相同D.不确定5. 1987标准的VHDL语言对大小写是。

A.敏感的B.只能用小写C.只能用大写D.不敏感6.关于1987标准的VHDL语言中,标识符描述正确的是。

A.必须以英文字母开头B.可以使用汉字开头C.可以使用数字开头D.任何字符都可以7.关于1987标准的VHDL语言中,标识符描述正确的是。

A.下划线可以连用B.下划线不能连用C.不能使用下划线D.可以使用任何字符8.符合1987VHDL标准的标识符是。

A. A_2B. A+2C. 2AD. 229.符合1987VHDL标准的标识符是。

A. a_2_3B. a_2C. 2_2_aD. 2a10.不符合1987VHDL标准的标识符是。

A. a_1_inB. a_in_2C. 2_aD. asd_111.不符合1987VHDL标准的标识符是。

A. a2b2B. a1b1C. ad12D. %5012. VHDL语言中变量定义的位置是。

A.实体中中任何位置B.实体中特定位置C.结构体中任何位置D.结构体中特定位置13. VHDL语言中信号定义的位置是。

A.实体中任何位置B.实体中特定位置C.结构体中任何位置D.结构体中特定位置14.变量是局部量可以写在。

A.实体中B.进程中C.线粒体D.种子体中15.变量和信号的描述正确的是。

A.变量赋值号是:=B.信号赋值号是:=C.变量赋值号是<=D.二者没有区别16.变量和信号的描述正确的是。

A.变量可以带出进程B.信号可以带出进程C.信号不能带出进程别17.关于VHDL数据类型,正确的是。

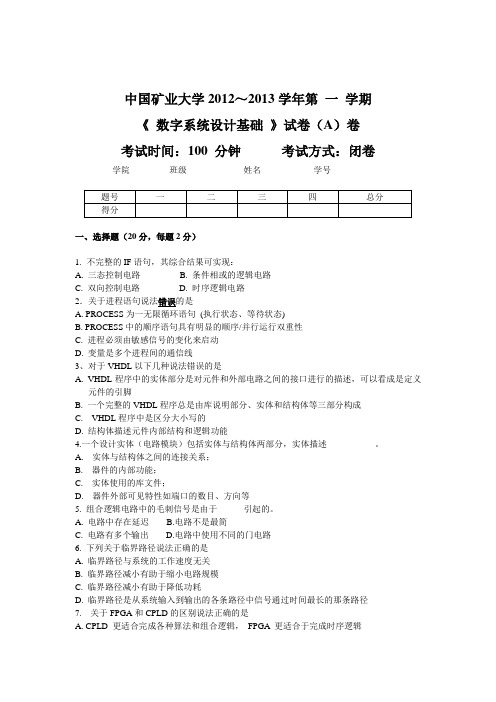

(完整word版)数字系统设计试卷2012A卷(word文档良心出品)

中国矿业大学2012~2013学年第一学期《数字系统设计基础》试卷(A)卷考试时间:100 分钟考试方式:闭卷学院_________班级_____________姓名___________学号____________一、选择题(20分,每题2分)1.不完整的IF语句,其综合结果可实现:_________A. 三态控制电路B. 条件相或的逻辑电路C. 双向控制电路D. 时序逻辑电路2.关于进程语句说法错误的是_________A. PROCESS为一无限循环语句(执行状态、等待状态)B. PROCESS中的顺序语句具有明显的顺序/并行运行双重性C. 进程必须由敏感信号的变化来启动D. 变量是多个进程间的通信线3、对于VHDL以下几种说法错误的是___________A. VHDL程序中的实体部分是对元件和外部电路之间的接口进行的描述,可以看成是定义元件的引脚B. 一个完整的VHDL程序总是由库说明部分、实体和结构体等三部分构成C. VHDL程序中是区分大小写的D.结构体描述元件内部结构和逻辑功能4.一个设计实体(电路模块)包括实体与结构体两部分,实体描述___________。

A. 实体与结构体之间的连接关系;B. 器件的内部功能;C. 实体使用的库文件;D. 器件外部可见特性如端口的数目、方向等5. 组合逻辑电路中的毛刺信号是由于______引起的。

A. 电路中存在延迟B.电路不是最简C. 电路有多个输出D.电路中使用不同的门电路6. 下列关于临界路径说法正确的是___________A. 临界路径与系统的工作速度无关B. 临界路径减小有助于缩小电路规模C. 临界路径减小有助于降低功耗D. 临界路径是从系统输入到输出的各条路径中信号通过时间最长的那条路径7. 关于FPGA和CPLD的区别说法正确的是___________A. CPLD 更适合完成各种算法和组合逻辑,FPGA 更适合于完成时序逻辑B. FPGA 的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而CPLD的分段式布线结构决定了其延迟的不可预测性C. 在编程上CPLD 比FPGA具有更大的灵活性D. CPLD的集成度比FPGA高,具有更复杂的布线结构和逻辑实现。

数字系统(EDA)样卷

)。

C. AHDL和Verilog HDL

D. 只有Verilog HDL

4.本课程实验开发系统上的下载板所配置的目标芯片的型号

是( )。

A. FLEX10K系列 EPF10K10LC84-3 B. FLEX10KE系列 EPF10K30EFC484-1 C. FLEX10K系列 EPF10K10LC84-4 D. MAX7000系列 EPM7096LC84-7

重置

4 课程自测-《数字系统设计》样卷 课程自测—样卷1

4.写出下图所示电路的Verilog 结构描述程序。(5分)

答 : m o d u le D F F (D ,C P ,Q ,N Q ); in p u t D ,C P ; o u tp u t Q ,N Q ; w ire N D ,R ,S ; n o t (N D ,D ); n a n d N 1 (R ,D ,C P ), N 2 (S ,N D ,C P ); n a n d N 3 (Q ,N Q ,R ), N 4 (N Q ,Q ,S ); en d m o d u le

4 课程自测-《数字系统设计》样卷 课程自测—样卷1

3.什么是Top_down设计?

重置

答 : Top_down设 计 , 即 自 顶 向 下 的 设 计 。 这 种 设 计 方 法 首 先 从 系 统 入手,在顶层进行功能方框图的划分和结构设计。在功能级进行仿 真、纠错,并用硬件描述语言对高层次的系统行为进行描述,然后 用综合工具将设计转化为具体门电路网表,其对应的物理实现可以 是 P L D 器 件 或 专 用 的 集 成 电 路 (A S IC )。

sel a b 1 0

F

答 : a ,b ,s e l,F (1 分 ) a ,b ,s e l (1 分 ) F (1 分 ) F = s e l? a :b ; (2 分 )

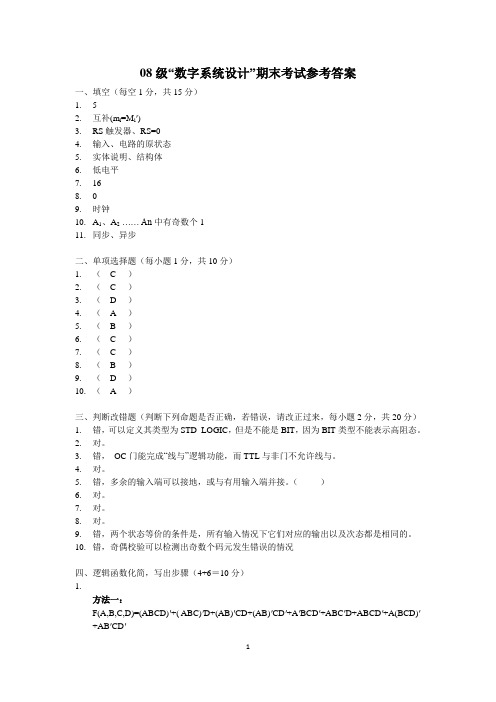

数字系统设计期末试卷参考答案(08级)

08级“数字系统设计”期末考试参考答案一、填空(每空1分,共15分)1. 52.互补(m i=M i')3.RS触发器、RS=04.输入、电路的原状态5.实体说明、结构体6.低电平7.168.09.时钟10.A1、A2…… An中有奇数个111.同步、异步二、单项选择题(每小题1分,共10分)1.( C )2.( C )3.( D )4.( A )5.( B )6.( C )7.( C )8.( B )9.( D )10.( A )三、判断改错题(判断下列命题是否正确,若错误,请改正过来,每小题2分,共20分)1.错,可以定义其类型为STD_LOGIC,但是不能是BIT,因为BIT类型不能表示高阻态。

2.对。

3.错,OC门能完成“线与”逻辑功能,而TTL与非门不允许线与。

4.对。

5.错,多余的输入端可以接地,或与有用输入端并接。

()6.对。

7.对。

8.对。

9.错,两个状态等价的条件是,所有输入情况下它们对应的输出以及次态都是相同的。

10.错,奇偶校验可以检测出奇数个码元发生错误的情况四、逻辑函数化简,写出步骤(4+6=10分)1.方法一:F(A,B,C,D)=(ABCD)'+( ABC)'D+(AB)'CD+(AB)'CD'+A'BCD'+ABC'D+ABCD'+A(BCD)' +AB'CD'=A'+B'+C'+D'+(A'+B'+C')D+( A'+B')CD+( A'+B')CD'+A'BCD'+ABC'D+ABCD'+A(B'+C '+D')+ AB'CD'= A'+B'+C'+D'方法二:由函数式可画出卡诺图如下:由卡诺图化简得:F= A'+B'+C'+D'2.输入ABCD为8421BCD码,故取值为0000~1001,当取值为0000、0011、0110、1001时,F=1,取其他的8421BCD码时,输出为0;1010~1111为无关项,由此可画出卡诺图如下:F=A'B'C'D'+AD+B'CD+BCD'五、按要求完成下列各题,并写出分析步骤(5+6+6=17分)1.(5分)分析下面的电路是否存在竞争-冒险现象?由逻辑电路图可写出函数表达式:F=AC+A'C'+A'B,当B=C=1时,F=A+A',故该电路存在竞争-冒险现象2.(6分)方法一:74283的输出S= A4A3A2A1+ B4B3B2B1+C0= ABCD+A'A'0A'输入ABCD是余3码,即取值范围为:0011~1100当ABCD=0011~0111时,A=0,74283的输出S=ABCD+1101=0000~0100当ABCD=1000~1100时,A=1,74283的输出S=ABCD+0000=ABCD即:对于十进制数0~4的余3码,该电路输出0000~0100;对于十进制5~9的余3码,该电路输出为1000~1100——5421码输出故该电路的功能是将余3码转换成5421码输出方法二:74283的输出S= A4A3A2A1+ B4B3B2B1+C0= ABCD+A'A'0A'输入ABCD是余3码,即取值范围为:0011~1100,列出真值表如下:由真值表可知,该电路的功能是将余3码转换成5421码。

现代数字系统设计_习题集(含答案)

14.任Verilog HDL的端口声明语句中,用()关键字声明端口为双向端口

A:inout B:INOUT C:BUFFER D:buffer

15.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为()。

A:8´b1111_1110 B:3´o276 C:3´d170 D:2´h3E

31.将设计的系统按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程,称为()。

A:设计的输入B:设计的输出C:仿真D:综合

32.不属于PLD基本结构部分的是()。

A:与门阵列B:输入缓存C:与非门阵列D:或门阵列

C:原理图输入设计方法一般是一种自底向上的设计方法;

D:原理图输入设计方法也可进行层次化设计。

35.一般把EDA技术的发展分为()个阶段。

A:2 B:3 C:4 D:5

36.设a = 4´b1010,b=4´b0001,c= 4´b1xz0则下列式子的值为1的是()

A:a > b B:a <= c C:13 - a < b d:13 – (a>b)

A:查找表(LUT)C:PAL可编程B:ROM可编程D:与或阵列可编程

25.设计输入完成之后,应立即对文件进行()。

A:编译B:编辑C:功能仿真D:时序仿真

26.VHDL是在()年正式推出的。

A:1983 B:1985 C:1987 D:1989

27.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→()→综合→适配→()→编程下载→硬件测试。①功能仿真②时序仿真③逻辑综合④配置⑤引脚锁定

现代数字系统设计

现代数字系统设计——在线考试复习资料2022版一、单选题1. SOPC的中文意思是( )。

A. 电子设计自动化B.硬件描述语言C.片上可编程系统D.片上系统答案:C2.XPS是Xilinx公司提供的( )。

A.嵌入式系统的集成硬件设计和仿真工具B.编辑FPGA的I/O引脚和面积约束相关的用户约束文件的工具C.实现FPGA/CPLD的配置和通信的工具D.实现FPGA的时序分析工具答案:A3.CLB的中文意思是( )。

A.有限状态机B.复杂可编程逻辑器件C.可编程逻辑块D.硬件描述语言答案:C4.LUT 的中文意思是( )。

A.可编程门阵列B.查找表C.集成电路D.知识产权答案:B5.根据配置数据线数, 串行配置是以什么方式将配置数据载入可编程器件?A. 比特(bit)B.字节(Byte)C.帧结构D.通用IP方式答案:A6.从互连结构上可将PLD分为确定型和统计型两类。

统计型结构代表是( )。

A.FPGAB.CPLDC.PLAD.GAL答案:A7.IP核在EDA技术和开辟中具有十分重要的地位,IP核是指( )。

B.互联网协议C. 网络地址D.智能外设答案:A8. 基于Xilinx FPGA的IP 核开辟工具是( )。

A.Core GeneratorB.XSTC.FloorplannerD.iMPACT答案:A9.关于Verilog HDL中的数字,请找出以下数字中最大的一个是( )。

A.8´b1111_1110B.9´o276C.8´d170D.8´h3E答案:A10.用Verilog HDL的assign语句建模的方法普通称为( )方法。

A.连续赋值B.并行赋值C. 串行赋值D.函数赋值答案:A11.Verilog HDL的标识符使用字母的规则是( )。

A.大小写相同含义B.大小写不同含义C.只允许大写字母D.只允许小写字母答案:B12.Verilog HDL的端口声明语句中,声明端口为输入端口的关键字是( )。

最新pld习题集(含参考答案)数字系统设计

p l d习题集(含参考答案)数字系统设计------------------------------------------作者xxxx------------------------------------------日期xxxx第1章习题1.1名词解释PROM CPLD FPGA ASICJTAG边界扫描 FPGA/CPLD编程与配置逻辑综合PAL EDA GAL IP-CORE ISP ASIC RTL FPGA SOPC CPLDIP—CORE SOC和SOPCEDA/CAD1.2 现代EDA技术的特点有哪些?采用HDL描述、自顶向下、开放标准、具有完备设计库1.3 什么是Top—down设计方式?(P4)1.4 数字系统的实现方式有哪些?各有什么优缺点?74LS系列/4000系列常规逻辑门设计:设计难度大、调试复杂采用CPLD/FPGA等可编程器件来设计:用HDL描述、设计难度小、调试仿真方便,开发费用低,但单位成本较高,适合小批量应用专用集成电路设计:设计掩模成本高,适合大批量应用1.5什么是IP复用技术?IP核对EDA技术的应用和发展有什么意义?(P5)IP可重复使用的一种功能设计,可节省设计时间、缩短开发周期,避免重复劳动为大规模SOC设计提供开发基础、和开发平台。

1。

6 用硬件描述语言设计数字电路有什么优势?优势:可进行行为级、RTL级、门级多层面对电路进行描述、可功能仿真时序分析,与工艺无关.1.8 基于FPGA/CPLD的数字系统设计流程包括哪些步骤?(P8 图1。

7)1。

9 什么是综合?常用的综合工具有哪些?HDL RTL门级网表的描述转换过程ALTERA:MAX—PLUSII,Quartus, Xilinx:ISE ,Lattice: ispLERVER1.10功能仿真与时序仿真有什么区别?功能仿真不考虑器件延时,而时序分析必须考虑在不同器件中的物理信号的延时1。

11 数字逻辑设计描述分哪几个层级,各有什么特点.1。

现代数字系统设计_习题集(含答案)

一、单选题

1.IP核在EDA技术和开发中具有十分重要的地位,IP是指()。

A:知识产权B:互联网协议C:网络地址D:都不是

2.在verilog HDL的always块本身是()语句

A:顺序B:并行C:顺序或并行D:串行

3.设a = 1´b1,b = 3´b101,c = 4´b1010则X= {a,b,c}的值的等于()

C:综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的;

D:为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;

23.不完整的IF语句,其综合结果可实现()。

A:时序逻辑电路B:组合逻辑电路C:双向电路D:三态控制电路

24.CPLD的可编程是主要基于什么结构()。

A:瘦IP B:固IP C:胖IP D:都不是

16.FPGA可编程逻辑基于的可编程结构基于()。

A:LUT结构B:乘积项结构C:PLD D:都不对

17.操作符是Verilog HDL预定义的函数命名,操作符是由()字符组成的。

A:1 B:2 C:3 D:1~3

18.在EDA工具中,能将硬件描述语言转化为硬件电路的重要工具软件为()。

A:③①B:⑤②C:④⑤D:①②

28.设a=2,b=0,则下列式子中等于X的是()。

A:a && b B:a || b C:!a D:x && a

29.在EDA工具中,能完成在目标系统器件上布局布线的软件称为()。

A:仿真器B:综合器C:适配器D:下载器

30.关于Verilog HDL中的数字,请找出以下数字中最大的一个:()。

第8章 数字系统设计基础-习题答案

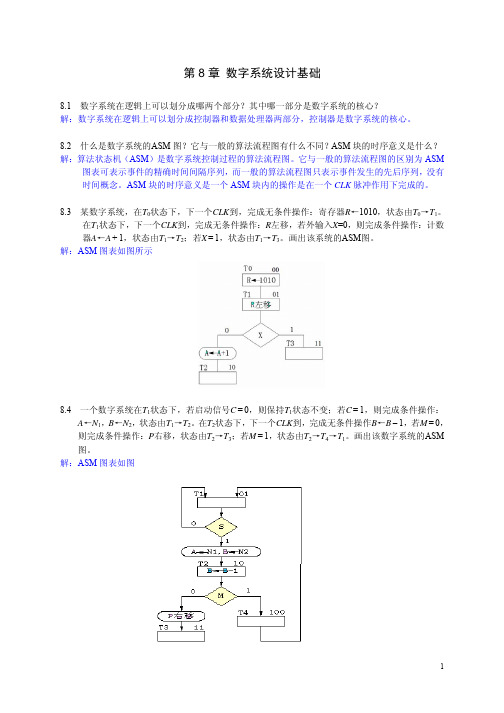

第8章数字系统设计基础8.1 数字系统在逻辑上可以划分成哪两个部分?其中哪一部分是数字系统的核心?解:数字系统在逻辑上可以划分成控制器和数据处理器两部分,控制器是数字系统的核心。

8.2 什么是数字系统的ASM图?它与一般的算法流程图有什么不同?ASM块的时序意义是什么?解:算法状态机(ASM)是数字系统控制过程的算法流程图。

它与一般的算法流程图的区别为ASM 图表可表示事件的精确时间间隔序列,而一般的算法流程图只表示事件发生的先后序列,没有时间概念。

ASM块的时序意义是一个ASM块内的操作是在一个CLK脉冲作用下完成的。

8.3 某数字系统,在T0状态下,下一个CLK到,完成无条件操作:寄存器R←1010,状态由T0→T1。

在T1状态下,下一个CLK到,完成无条件操作:R左移,若外输入X=0,则完成条件操作:计数器A←A+1,状态由T1→T2;若X=1,状态由T1→T3。

画出该系统的ASM图。

解:ASM图表如图所示8.4 一个数字系统在T1状态下,若启动信号C=0,则保持T1状态不变;若C=1,则完成条件操作:A←N1,B←N2,状态由T1→T2。

在T2状态下,下一个CLK到,完成无条件操作B←B−1,若M=0,则完成条件操作:P右移,状态由T2→T3;若M=1,状态由T2→T4→T1。

画出该数字系统的ASM 图。

解:ASM图表如图8.5 控制器状态图如题图8.5所示,画出其等效的ASM图。

题图8.5解:ASM图8.6 设计一个数字系统,它有三个4位的寄存器X、Y、Z,并实现下列操作:①启动信号S出现,传送两个4位二进制数N1、N2分别给寄存器X、Y;② 如果X>Y,左移X的内容,并把结果传送给Z;③如果X<Y,右移Y的内容,并把结果传送给Z;④如果X=Y,把X或Y传送给Z。

画出满足以上要求的ASM图。

解:ASM图如下图8.7 某数字系统的ASM图如题图8.7所示,试完成下列要求:(1)画出其等效的状态图;(2)用每态一个触发器的方法设计控制器。

数字系统设计答案 (2)

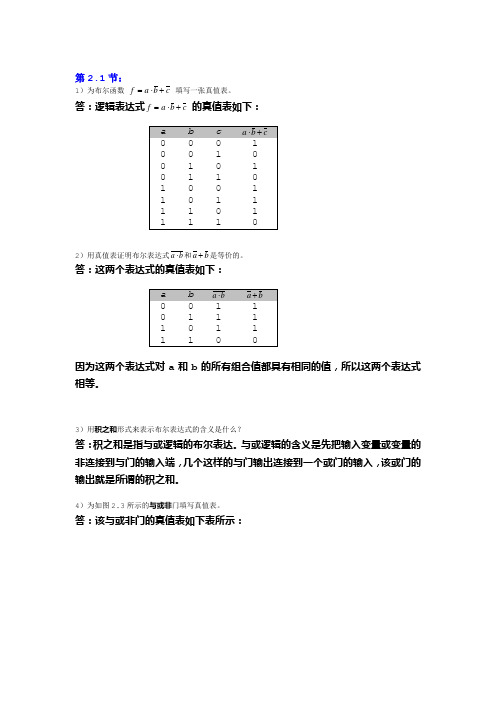

第 2.1 节:1)为布尔函数 f = a ⋅ b + c 填写一张真值表。

的真值表如下: 答:逻辑表达式 f = a ⋅ b + c 的真值表如下: a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1a ⋅b + c1 0 1 0 1 1 1 02)用真值表证明布尔表达式 a ⋅ b 和 a + b 是等价的。

答:这两个表达式的真值表如下: 这两个表达式的真值表如下: a 0 0 1 1 b 0 1 0 1a ⋅ba+b1 1 1 01 1 1 0的所有组合值都具有相同的值, 因为这两个表达式对 a 和 b 的所有组合值都具有相同的值,所以这两个表达式 相等。

相等。

3)用积之和 积之和形式来表示布尔表达式的含义是什么? 积之和积之和是指与或逻辑的布尔表达。

答:积之和是指与或逻辑的布尔表达。

与或逻辑的含义是先把输入变量或变量 的非连接到与门的输入端 几个这样的与门输出连接到一个或门的输入, 的输入端, 连接到一个或门的输入 的非连接到与门的输入端,几个这样的与门输出连接到一个或门的输入,该或 门的输出就是所谓的积之和 积之和。

门的输出就是所谓的积之和。

4)为如图 2.3 所示的与或非 与或非门填写真值表。

与或非答:该与或非门的真值表如下表所示: 该与或非门的真值表如下表所示:a 0 0 0b 0 0 0c 0 0 1d 0 1 0a ⋅b + c ⋅d1 1 10 0 0 0 0 1 1 1 1 1 1 1 10 1 1 1 1 0 0 0 0 1 1 1 11 0 0 1 1 0 0 1 1 0 0 1 11 0 1 0 1 0 1 0 1 0 1 0 10 1 1 1 0 1 1 1 0 0 0 0 05)在数字电路中,为什么要用缓冲器?缓冲器可以用来降低输出的负载, 答:缓冲器可以用来降低输出的负载,当输出必须驱动下一级逻辑门的很多个输 缓冲器可以用来降低输出的负载 入时,其负载是很重的。

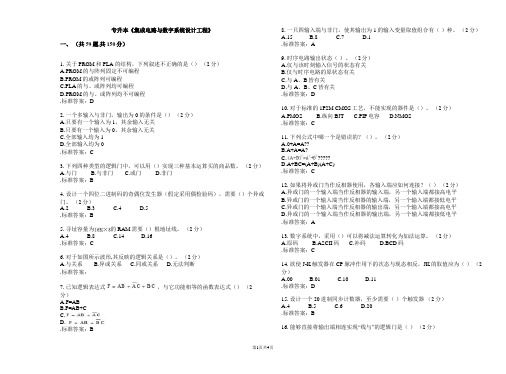

专升本《集成电路与数字系统设计工程》_试卷_答案

专升本《集成电路与数字系统设计工程》一、(共59题,共150分)1. 关于PROM和PLA的结构,下列叙述不正确的是()(2分)A.PROM的与阵列固定不可编程B.PROM的或阵列可编程C.PLA的与、或阵列均可编程D.PROM的与、或阵列均不可编程.标准答案:D2. 一个多输入与非门,输出为0的条件是()(2分)A.只要有一个输入为1,其余输入无关B.只要有一个输入为0,其余输入无关C.全部输入均为1D.全部输入均为0.标准答案:C3. 下列四种类型的逻辑门中,可以用()实现三种基本运算买的商品数。

(2分)A.与门B.与非门C.或门D.非门.标准答案:B4. 设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要()个异或门。

(2分)A.2B.3C.4D.5.标准答案:B5. 寻址容量为的RAM需要()根地址线。

(2分)A.4B.8C.14D.16.标准答案:C6. 对于如图所示波形,其反映的逻辑关系是()。

(2分)A.与关系B.异或关系C.同或关系D.无法判断.标准答案:7. 已知逻辑表达式,与它功能相等的函数表达式()(2分)A.F=ABB.F=AB+CC.D..标准答案:B 8. 一只四输入端与非门,使其输出为1的输入变量取值组合有()种。

(2分)A.15B.8C.7D.1.标准答案:A9. 时序电路输出状态()。

(2分)A.仅与该时刻输入信号的状态有关B.仅与时序电路的原状态有关C.与A、B皆有关D.与A、B、C皆有关.标准答案:D10. 对于标准的1P2M CMOS工艺,不能实现的器件是()。

(2分)A.PMOSB.纵向BJTC.PIP电容D.NMOS.标准答案:C11. 下列公式中哪一个是错误的?()。

(2分)A.0+A=A??B.A+A=A?C.?????D.A+BC=(A+B)(A+C).标准答案:C12. 如果将异或门当作反相器使用,各输入端应如何连接?()(2分)A.异或门的一个输入端当作反相器的输入端,另一个输入端都接高电平B.异或门的一个输入端当作反相器的输入端,另一个输入端都接低电平C.异或门的一个输入端当作反相器的输出端,另一个输入端都接高电平D.异或门的一个输入端当作反相器的输出端,另一个输入端都接低电平.标准答案:A13. 数字系统中,采用()可以将减法运算转化为加法运算。

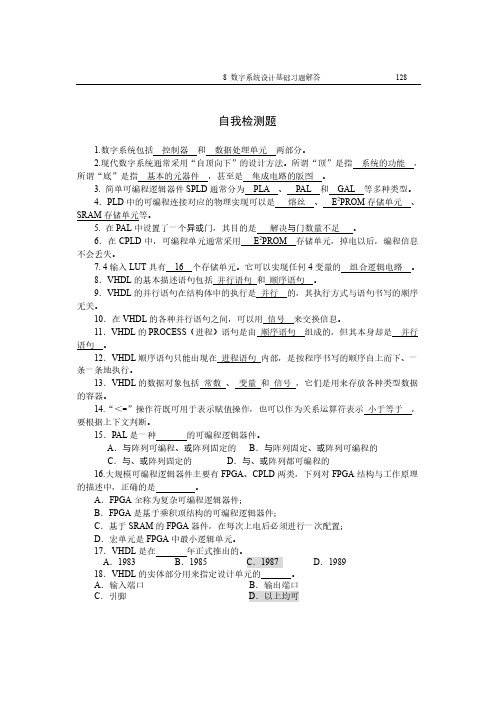

8数字系统设计习题解答

A.字母

B.数字

C.字母或数字

D.下划线

23. 在 VHDL 中,目标信号的赋值符号是

。

A. =:

B.=

C. :=

D.<=

习题

1.说明自顶向下的设计方法及步骤。 首先从系统设计入手,在顶层将整个系统划分成几个子系统,然后逐级向下,再将每 个子系统分为若干功能模块,每个功能模块还可以继续向下划分成子模块,直至分成许多 最基本模块实现。 2.说明 CPLD I/O 控制块的功能。 I/O 控制块允许每个 I/O 引脚单独地配置为输入、输出和双向工作方式。所有 I/O 引脚 有一个三态缓冲器,它控制的信号来自一个多路选择器,可以选择全局输出使能信号中的 一个或者直接连接到地(GND)或电源(Vcc)上。当三态缓冲器的控制端接地时,输出 为高阻态,此时 I/O 引脚可用作专用输入引脚。当三态缓冲器的控制端接高电平(Vcc)时, 输出被使能 3.以 Cyclone IV 系列 FPGA 为例,逻辑单元 LE 能否同时实现组合逻辑电路和时序逻 辑电路? 从图 8.2-18 可知,LUT 输入除了来自互连阵列,也来自触发器的输出,也就是说触发 器的输出反馈到 LUT 的输入端,便于构成计数器、状态机等时序电路。LUT 的输出可以 直接送到互连阵列,触发器的输入也可以不来自 LUT 的输出,而来自触发器链输入。LUT 和触发器可以独立工作,这意味着一个逻辑单元可以同时实现组合电路和时序电路。 4.CPLD 和 FPGA 有什么不同? FPGA 可以达到比 CPLD 更高的集成度,同时也具有更复杂的布线结构和逻辑实现。 FPGA 更适合于触发器丰富的结构,而 CPLD 更适合于触发器有限而积项丰富的结构。 在编程上 FPGA 比 CPLD 具有更大的灵活性;CPLD 功耗要比 FPGA 大;且集成度越高 越明显;CPLD 比 FPGA 有较高的速度和较大的时间可预测性,产品可以给出引脚到引脚 的最大延迟时间。CPLD 的编程工艺采用 E2 CPLD 的编程工艺,无需外部存储器芯片,使 用简单,保密性好。而基于 SRAM 编程的 FPGA,其编程信息需存放在外部存储器上,需

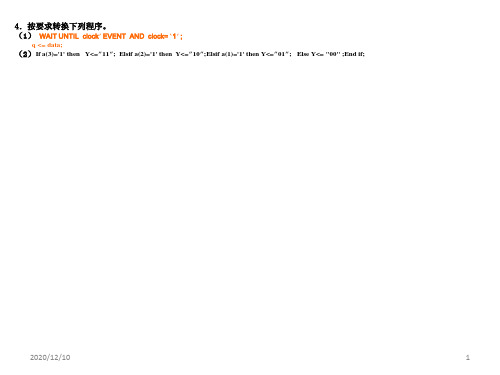

《数字系统设计》试卷A部分答案PPT教学课件

2

(1)

idle

1

r1

0 g1

1

r2

0 g2

0

1

r3

g3

1

r1

0

1

0

r2

1 0

r3

2020/12/10

(2)

idle

r3='1' and

Y

k1k2="11"

N

Y

r1='1'

N

r2='1'

N

r3='1'

Y

Y N

S3 g3='1' k1='0' k2='0'

S1 k1='1' g1='1'

S2 k2='1' g2='1'

each clock cycle in steady-state simulation(ignore any irregularities in the first few clock cycles) • 2)for full marks, if the code does not match, you must explain why. • 3) assume that all signals, constrants, variables, types, etc are properly defined and declared. • 4) all of the codes are leagal, synthesizable VHDL code.

Architecture a of q is Begin

process begin a <= ‘1’; loop wait until rising_edge(clk); a <= NOT a; end loop;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

,考试作弊将带来严重后果!

华南理工大学期末考试

《数字系统设计》试卷

1. 考前请将密封线内各项信息填写清楚;

所有答案请直接答在试卷上(或答题纸上);

.考试形式:开(闭)卷;

(每小题2分,共16分)

大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理( C )

CPLD即是现场可编程逻辑器件的英文简称;

CPLD是基于查找表结构的可编程逻辑器件;

早期的CPLD是从GAL的结构扩展而来;

在Altera公司生产的器件中,FLEX10K 系列属CPLD结构;

在VHDL语言中,下列对时钟边沿检测描述中,错误的是( D )

then ...;

then ...;

then ...;

在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确( A )

PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一.

敏感信号参数表中,应列出进程中使用的所有输入信号;

进程由说明部分、结构体部分、和敏感信号参数表三部分组成;

当前进程中声明的信号也可用于其他进程

基于EDA软件的FPGA / CPLD设计流程,以下流程中哪个是正确的:( C )

原理图/HDL文本输入→适配→综合→时序仿真→编程下载→功能仿真→硬件测试

原理图/HDL文本输入→功能仿真→综合→时序仿真→编程下载→适配→硬件测试;

原理图/HDL文本输入→功能仿真→综合→适配→时序仿真→编程下载→硬件测试

原理图/HDL文本输入→适配→时序仿真→编程下载→功能仿真→综合→硬件测试。

关于综合,从输入设计文件到产生编程文件的顺序正确的是:(B)

.逻辑综合→高层次综合→物理综合;

B. 高层次综合→逻辑综合→物理综合;

C. 物理综合→逻辑综合→高层次综合;

D. 高层次综合→逻辑综合→时序综合;

6. 进程中的信号赋值语句,其信号更新是( C )

A. 按顺序完成;

B. 比变量更快完成;

C. 在进程的挂起时完成;

D. 都不对。

7. 下列不属于VHDL基本程序结构是(A)

A..CONFIGURATION定义区

B..ARCHITECTURE定义区

C.USE定义区

D.ENTITY定义区

8.下面对利用原理图输入设计方法进行数字电路系统设计,那一种说法是不正确的_(C)。

A.原理图输入设计方法直观便捷,但不适合完成较大规模的电路系统设计;

B.原理图输入设计方法一般是一种自底向上的设计方法;

C.原理图输入设计方法无法对电路进行功能描述;

D.原理图输入设计方法也可进行层次化设计。

二.简答题(22分)

1. 简述利用EDA技术设计数字系统的特点。

(4分)

2. 什么是信号建立时间?(2分)什么是信号保持时间?(2分)

3. 仿真分为哪几个层次的仿真?(3分)

4. 实验中,对某程序进行编译时出现错误提示:“VHDL Design File “aaa.vhd”must contain an entity of the same name.”(4分)

这是什么原因?如何修改?

5.实验中,如果编译时出现“Can’t open VHDL “WORK””这样的错误提示。

这又是什么原因,如何修改?(4分)

6.用图示法描述一般时序系统的模型,并作简要说明。

(3分)

三.根据下述VHDL程序段,画出相应的逻辑示意图,并加以简单说明(共10分,每题5分)。

1、Process(clk)

Begin

If (clk =‘1’) then Q<=data; End if;

End process;

2、ENTITY example IS

PORT ( a, b , c, g1, g2a, g2b: IN std_logic;

y: OUT std_logic_vector (7 DOWNTO 0) );

END ENTITY;

ARCHITECTURE behav OF example IS

SIGNAL indata : std_logic_vector(2 DOWNTO 0);

BEGIN

indata<=c & b & a ;

PROCESS( indata, g1, g2a, g2b)

BEGIN

IF (g1='1'and g2a='0' AND g2b='0') THEN

CASE indata IS

WHEN "000"=> y<="11111110";

WHEN "001"=> y<="11111101";

WHEN "010"=> y<="11111011";

WHEN "011"=> y<="11110111";

WHEN "100"=> y<="11101111";

WHEN "101"=> y<="11011111";

WHEN "110"=> y<="10111111";

WHEN "111"=> y<="01111111";

WHEN OTHERS => y<="XXXXXXXX";

END CASE;

ELSE

y<="11111111";

END IF;

END PROCESS;

END behav;

四.综合题(52分)

1. 根据原理图写出相应的VHDL程序:(10分)

2. 有一个传输门,根据下述赋值语句和给定的波形,画出对应Z1,Z2,Z3和Z4的波形图。

(4分)

(1)Z1<=Vi ,惯性延时时间为4ns

(2)Z2 <=Vi after 4 ns ,惯性延时时间为4ns

(3)Z3 <= TRANSPORT Vi AFTER 3 ns ,惯性延时时间为4ns (4)Z4<=Vi ,传输门的T r =4ns,T f =2ns

3. 根据ASM 图画出时序图。

(4分)

Z

C Y

W

1

4.下面的ASM图含有多少个状态单元,用虚线框加以表示(2分)。

并用双进程状态机描述,请在空白处填入合适语句, 使程序完整正确。

(8分)

Entity traffic is

Port ( reset, clk: in std_logic;

car,timed: in std_logic;

major_green, minor_green:out

std_logic);

end entity;

Architecture asm of traffic is

Begin

seq: process(reset, clk)

begin

end process;

com: process (present_state, car, timed)

begin

start_timer<=‘0’;

case pressent_state is

when G =>

when R=>

major_green<=‘0’;

minor_green<=‘1’;

if (timed=‘1’) then

next_state<=G;

else next_state<=R;

end if ;

end case;

end process ;

End asm;

5.下图所示电路是某数字系统的控制器。

其中Z是系统数据处理器的状态信号;

C1和C2是控制器输出的控作信号。

试画出该控制器的ASM图。

(10分)

6.试编程实现以下功能。

(14分)

如下图所示,某数字系统有三条输入线分别为CLK、CONTROL和DATA。

有一条输出应答线READY和8位输出总线Z。

从DATA数据线上输入的是8位串行数据。

串行输入数据从低位到高位依次输入。

当系统准备接受新的数据时READY信号置1,并监视输入信号CONTROL。

当CONTROL线在连续二个时钟周期为1时,系统将READY信号恢复为0。

随后的8个时钟由DATA线依次输入8位数据。

之后一个时钟,再次将READY 信号置1,并将8为数据并行输出到数据总线Z。

《》试卷第 8 页共 8 页。