集成电路课程设计模三计数器设计

项目三 模3计数器的原理图输入设计

教师评价+自评

能正确使用Quartus II软件综 合、编译、仿真并下载程序到 学习板,能正确调试电路,达 到项目要求。

4.项目总结报 告(10%)

5.职业素养 (25%)

教师评价

格式符合标准、内容完整、有 详细过程记录和分析,并能提 出一些新的建议。

教师评价+自评+ 互评

安全、文明工作,具有良好的 职业操守,学习积极性高,遵 守纪律,虚心好学,具有良好 的团队合作精神,热心帮助同 学,能用专业语言准确、流利 地进行交流

(3) 项目编译

分析综合

点击Quartus Ⅱ软件工具条上的快捷按钮 进行分析综合。

,对计数器工程

引脚分配

完成计数器的分析综合过程,得到工程的数据库文件以后, 需要给计数器的输入输出引脚进行引脚分配。

全编译

选择Processing→Start Compilation启动全编译过程。

四、项目实施——1. Quartus Ⅱ原理图设计

五、项目评价与总结提高

1.项目评价标准

考核点及占项目 分值比

1.根据项目要 求完成资讯并制 订行动方案

(15%)

2.详细设计 (20%)

建议考核方式 教师评价+互评 教师评价+互评

优

能根据项目要求很好地完成资 讯及学习,能制订合理的行动 计划,计划详细。

计数器软硬件设计正确,项目 方案可实施。

3.操作实施 (30%)

该设计可以利用JK触发器来完成。

三、项目分析

2.硬件电路设计

模3计数器完全由CPLD内部电路实现 CP连接到外部时钟,clr连接到按键开关、3位输出连接

到LED上。 硬件电路:

三、项目分析

数字集成电路-电路系统与设计第二版课程设计

数字集成电路-电路系统与设计第二版课程设计

一、课程设计介绍

数字集成电路是现代电路设计中的重要组成部分,也是计算机科学与工程的重要分支。

本课程设计旨在通过对数字集成电路的系统与设计进行探究,并结合具体的案例来设计和实现数字集成电路,使学生能够熟悉数字集成电路的基本原理、设计方法和实现技术。

本课程设计主要包含以下内容:

1.数值系统和编码

2.逻辑功能设计:组合逻辑电路和时序逻辑电路

3.集成电路设计方法和流程

4.VHDL和FPGA实现数字逻辑电路

5.数字信号处理器

通过本次课程设计,学生将掌握数字集成电路的系统性设计思路和实现方法,具备数字电路设计的基本能力和实际操作技术,能够针对具体应用场景提出解决方案,实现数字电路的设计、验证和调试。

二、课程设计要求

1. 课程设计题目

本次课程设计的题目为“4位计数器设计”。

2. 软件工具

VHDL编程软件和EDA工具

1。

数字集成电路设计 pdf

数字集成电路设计一、引言数字集成电路设计是一个广泛且深入的领域,它涉及到多种基本元素和复杂系统的设计。

本文将深入探讨数字集成电路设计的主要方面,包括逻辑门设计、触发器设计、寄存器设计、计数器设计、移位器设计、比较器设计、译码器设计、编码器设计、存储器设计和数字系统集成。

二、逻辑门设计逻辑门是数字电路的基本组成单元,用于实现逻辑运算。

常见的逻辑门包括与门、或门、非门、与非门和或非门等。

在设计逻辑门时,需要考虑门的输入和输出电压阈值,以确保其正常工作和避免误操作。

三、触发器设计触发器是数字电路中用于存储二进制数的元件。

它有两个稳定状态,可以存储一位二进制数。

常见的触发器包括RS触发器、D触发器和JK触发器等。

在设计触发器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

四、寄存器设计寄存器是数字电路中用于存储多位二进制数的元件。

它由多个触发器组成,可以存储一组二进制数。

常见的寄存器包括移位寄存器和同步寄存器等。

在设计寄存器时,需要考虑其结构和时序特性,以确保其正常工作和实现预期的功能。

五、计数器设计计数器是数字电路中用于对事件进行计数的元件。

它可以对输入信号的脉冲个数进行计数,并输出计数值。

常见的计数器包括二进制计数器和十进制计数器等。

在设计计数器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

六、移位器设计移位器是数字电路中用于对二进制数进行移位的元件。

它可以对输入信号进行位移操作,并输出移位后的结果。

常见的移位器包括循环移位器和算术移位器等。

在设计移位器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

七、比较器设计比较器是数字电路中用于比较两个二进制数的元件。

它可以比较两个数的值,并输出比较结果。

常见的比较器包括并行比较器和串行比较器等。

在设计比较器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

八、译码器设计译码器是数字电路中用于将二进制数转换为另一种形式的元件。

模拟集成电路十进制异步计数器设计及仿真课程设计报告

模拟集成电路十进制异步计数器设计及仿真课程设计报告“模拟集成电路十进制异步计数器设计及仿真课程设计报告”第一节:引言作为现代电子技术的重要组成部分,模拟集成电路在各种领域中发挥着重要作用。

其中,十进制异步计数器作为模拟集成电路中的一个重要组成部分,具有着广泛的应用前景。

本篇文章将围绕着模拟集成电路十进制异步计数器的设计和仿真展开,探讨其在电子技术中的重要性和应用价值。

第二节:理论基础在深入探讨模拟集成电路十进制异步计数器的设计前,有必要首先了解其理论基础。

十进制异步计数器是一种能够按照十进制计数规律进行计数的电路,并能够在输入脉冲信号的触发下进行递增。

其设计原理涉及到逻辑门的连接和状态转换等内容,需要深入理解和把握。

第三节:设计流程在进行模拟集成电路十进制异步计数器的设计时,需要遵循一定的设计流程。

首先是对其工作原理进行深入理解,并根据要求进行逻辑电路图的绘制。

接着是选择适当的集成电路器件,并进行电路连接和布线设计。

最后则是进行仿真验证和性能测试,以确保其符合设计要求。

第四节:实践应用模拟集成电路十进制异步计数器在实际应用中有着广泛的应用价值。

比如在数字显示系统、计数器系统和数字控制系统中都能够发挥作用。

其设计与实践能够帮助学生更好地理解电子技术的原理,并为日后的工程设计工作打下良好的基础。

第五节:个人观点从我个人的角度来看,模拟集成电路十进制异步计数器的设计和仿真课程设计报告是十分有价值的。

通过深入学习和理解其原理和应用,不仅能够提高我们对电子技术的认识,还能够培养我们的动手能力和实践能力。

这对于我们未来的工程技术学习和研究工作是十分有益的。

总结与回顾通过本文的介绍,我们深入了解了模拟集成电路十进制异步计数器的设计和仿真课程设计报告的重要性和应用价值。

也对其在理论基础、设计流程和实际应用方面有了深入的认识。

这将为我们今后的学习和工程设计工作提供重要的借鉴和指导。

在本篇文章中,我们深入探讨了模拟集成电路十进制异步计数器的设计和仿真课程设计报告,介绍了其在电子技术中的重要性和应用价值。

数字电子技术项目3计数器电路的设计与测试

项目3 计数器电路的设计与测试

任务3-1 触发器逻辑功能测试 3-1-2 边沿D触发器逻辑功能测试

【知识扫描】边沿D触发器逻辑功能及描述方式

项目3 计数器电路的设计与测试

任务3-1 触发器逻辑功能测试 3-1-2 边沿D触发器逻辑功能测试

【知识扫描】边沿D触发器逻辑功能及描述方式

项目3 计数器电路的设计与测试

3-1-1 RS触发器逻辑功能测试 【工作任务3-1-1】基本RS触发器功能测试

测试步骤:

任务3-1 触发器逻辑功能测试

项目3 计数器电路的设计与测试

3-1-1 RS触发器逻辑功能测试 【工作任务3-1-1】基本RS触发器功能测试

测试步骤:

任务3-1 触发器逻辑功能测试 3-1-1 RS触发器逻辑功能测试

项目3 计数器电路的设计与测试

【知识扫描】基本RS触发器逻辑功能

Qn1 S R Qn

RS 1

约束条件

任、 务3-1 触发器逻辑功能测试 3-1-2 边沿D触发器逻辑功能测试

项目3 计数器电路的设计与测试

【器件认知】边沿D触发器逻辑符号和集成D触发器74LS74管脚排列

1 边沿D触发器逻辑符号

【工作任务3-1-2】边沿D触发器逻辑功能测试

项目3 计数器电路的设计与测试

任务3-1 触发器逻辑功能测试 3-1-2 边沿D触发器逻辑功能测试

【工作任务3-试

任务3-1 触发器逻辑功能测试 3-1-2 边沿D触发器逻辑功能测试

【工作任务3-1-2】边沿D触发器逻辑功能测试

按照【工作任务3-1-3】 测试步骤进行测试。

任务3-1 触发器逻辑功能测试 3-1-3 边沿JK触发器逻辑功能测试

【工作任务3-1-3】边沿JK触发器功能测试

计数器的原理图绘制与设计

任务分解

1

编辑元件

2

绘制复杂电路图

任务一 编辑元件

一、新建元件库 二、编辑元件

在原理图编辑前,常常要加载一些元件库, protel自带的元件库内尽管元件已经很齐全,但是在 实际设计过程中也往往会出现一些找不到元件或找到 的元件不理想的情况,比如某些很特殊的元件或新开 发出来的元件元件库内就找不到,或者元件符号尺寸 偏大,引脚过长,占用图纸面积多,不符合用户心意, 或者一些元件符号和GB4728—85标准不一致,需要修 改等等。这些情况下,就需要用户自己创建元件库并 进行元件编辑。一般情况下,用户不要去擅自修改程

模式列表窗内有三种模式可选,Normal、De-Morgan和IEEE,如 图3-6中的SN74LS00三种模式下都有图,很多元件只有Normal下才有 图。原理图绘制中取元件时默认的是Normal模式,如果需要显示其他 模式,必须双击打开其属性对话框。在“Graphical Attrs”选项卡内的 Mode下拉箭头中选择其他模式,如图3-9所示。

一、新建元件库

单 击 “ Description” 按 钮 , 弹 出 如 图 3-8 所 示 “ Component Text Fields”(元件参数文本)对话框。其中 “Designator”标签中是常用的设 置,如Default是缺省序号,如芯片缺省序号是U?,电阻是R?,电容是 C?,只有在此处设置了合适的缺省序号,原理图里取用该元件的时候 就会自动跟上该序号。“Footprint”后面可以填写元件的封装形式。 “description”是元件描述栏,一般描述了元件的功能等基本特性。

首先进入原理图编辑环境,加载TI Databooks.ddb。然后在元件 库列表中找出TI TTL Logic(Commercial).lib,找出SN74LS00元件, 如图3-5,然后单击“Edit”按钮,即打开如图3-6所示的元件编辑环 境。

(VHDL实验报告)模值12计数器、分频器的设计

电子科技大学成都学院学院指导教师模值12计数器,分频器设计二、实验目的1、了解二进制计数器的工作原理。

2、时钟在编程过程中的作用。

3、学习数控分频器的设计、分析和测试方法。

4、了解和掌握分频电路实现的方法。

5、掌握EDA技术的层次化设计方法。

三、实验原理(1)二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(定义使能端高电平有效)则开始计数,否则一直检测使能端信号。

在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数值清零,继续进行检测和计数。

其工作时序如下图所示:(2)数控分频器的功能就是当输入端给定不同的输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器来设计完成的,方法是将计数溢出位与预置数加载输入信号相接得到。

(1)“模值12计数器的设计”的实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。

实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED4来表示计数的二进制结果。

实验L ED 亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。

通过输入不同的值模拟计数器的工作时序,观察计数的结果。

实验箱中的拨动开关、与FPGA 的接口电路,LED 灯与FPGA 的接口电路以及拨动开关、LED 与F PGA 的管脚连接在实验一中都做了详细说明,这里不在赘述。

数字时钟信号模块的电路原理如下图所示,其时钟输出与F PGA 的管脚连接表如下图所示:信号名称对应FPGA 管脚名说明DIGITAL-CLK C13 数字时钟信号送至FPGA 的C13按键开关模块的电路原理如下图所示:按键开关的输出与F PGA 的管脚连接表如下图所示:五、实验步骤(一)模值12计数器的设计1、建立工程文件1)运行QUARTUSII 软件。

模电、数电课程设计

1 数字电子设计部分1.1 课程设计的目的与作用数字逻辑电路是实践性很强的一门学科,通过实践可以大大提高学生的理论水平和实际动手能力。

通过本次课程设计,使学生能够巩固已学专业基础课的理论知识,锻炼学生的实践动手能力,培养学生对电子电路的设计能力,加强学生在分析问题、解决问题能力上的训练和培养,为启发学生的创新意识和培养创新能力起到重要的作用,为其专业学习研究打下良好的基础。

同时培养学生科学实验研究的认真精神,使之明白理论与实践的紧密联系,使其养成良好的作业习惯,为其以后的工作研究打下良好的基础。

时序电路,触发器,序列发生器,是数电技术的基础,熟练掌握其工作特性才能为其以后在数电上的发展打下基础。

1.2设计任务1.利用在理论课上所学到的知识,结合对数字电子器件的认识,利用JK触发器,各种逻辑门电路设计出以010、001为无效态的三位二进制同步减法计数器。

并检查能否自启动,检查完毕,搭接电路,进行验证。

2. 利用JK触发器,各种逻辑门电路设计出串行序列发生电路,使其发生100111序列,并检查能否自启动,检查完毕,搭接电路,进行验证。

1.3 三位同步二进制减法计数器电路设计1.3.1抽象状态图获得驱动方程1.已知三位同步二进制减法计数器的无效状态为010、001,则抽象出状态图为1.3.1三位二进制减法计数器状态图2.根据三位同步二进制减法计数器状态图可得输出状Y的次态卡诺图。

1.3.2输出状态Y的卡诺图3.将输出状Y的次态卡诺图分解可得Q2n+1Q1n+1Qn+1的次态卡诺图。

1.3.3输出状态Q2n+1次态图1.3.4输出状态Q1n+1次态图1.3.5输出状态Q0n+1次态图4.根据图1.3.2、1.3.3、1.3.4、1.3.5中的输出状态Y及Q2n+1Q1n+1 Qn+1的次态卡诺图,可分别得到三位同步二进制减法计数器的输出状态Y的状态方程和三个JK触发器的驱动驱动方程。

状态方程 Q2n+1=nQnQ2+nQnQ1nQ2Q 1n+1=nQnQ1+nQnQ2nQ1Q 0n+1=nQ2nQ1nQ则驱动方程为J 2 =nQJ1=nQJ=nQ2nQ1K 2=nQnQ1K1=nQnQ2K0=11.3.2根据驱动方程画出电路图由于我们做的是三位同步二进制减法计数器,所以设计的电路所需的脉冲CP1=CP2=CP3=CP,所以选用一个就可以了。

数字电路实验3 计数器

实验八计数器一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理。

2.熟悉掌握常用中规模集成电路计数器及其应用方法。

二、实验原理和电路所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路。

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等。

计数器种类繁多。

根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器。

根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的。

根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端。

1.异步二进制加法计数器异步二进制加法计数器是比较简单的。

图 1.8.1(a)是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图1.8.1(b)和(c)分别为其状态图和波形图。

对于所得状态图和波形图可以这样理解:触发器FF O(最低位)在每个计数沿(CP)的下降沿(1 → 0)翻转,触发器FF1的CP端接FF0的Q0端,因而当FF O(Q O)由1→ 0时,FF1翻转。

类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转。

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)。

从波形图可看到,Q0 的周期是CP周期的二倍;Q1 是Q0的二倍,CP的四倍;Q2是Q1 的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0的八倍,CP的十六倍。

所以Q0 、Q1、Q2、Q3分别实现了二、四、八、十六分频,这就是计数器的分频作用。

计数器的设计实验报告

计数器的设计实验报告一、实验目的本次实验的目的是设计并实现一个简单的计数器,通过对计数器的设计和调试,深入理解数字电路的基本原理和逻辑设计方法,掌握计数器的工作原理、功能和应用,提高自己的电路设计和调试能力。

二、实验原理计数器是一种能够对输入脉冲进行计数,并在达到设定计数值时产生输出信号的数字电路。

计数器按照计数方式可以分为加法计数器、减法计数器和可逆计数器;按照计数进制可以分为二进制计数器、十进制计数器和任意进制计数器。

本次实验设计的是一个简单的十进制加法计数器,采用同步时序逻辑电路设计方法。

计数器由触发器、门电路等组成,通过对触发器的时钟信号和输入信号的控制,实现计数功能。

三、实验设备与器材1、数字电路实验箱2、集成电路芯片:74LS160(十进制同步加法计数器)、74LS00(二输入与非门)、74LS04(六反相器)3、示波器4、直流电源5、导线若干四、实验内容与步骤1、设计电路根据实验要求,选择合适的计数器芯片 74LS160,并确定其引脚功能。

设计计数器的清零、置数和计数控制电路,使用与非门和反相器实现。

画出完整的电路原理图。

2、连接电路在数字电路实验箱上,按照电路原理图连接芯片和导线。

仔细检查电路连接是否正确,确保无短路和断路现象。

3、调试电路接通直流电源,观察计数器的初始状态。

输入计数脉冲,用示波器观察计数器的输出波形,检查计数是否正确。

若计数不正确,逐步排查故障,如检查芯片引脚连接、电源电压等,直至计数器正常工作。

4、功能测试测试计数器的清零功能,观察计数器是否能在清零信号作用下回到初始状态。

测试计数器的置数功能,设置不同的预置数,观察计数器是否能按照预置数开始计数。

五、实验结果与分析1、实验结果成功实现了十进制加法计数器的设计,计数器能够在输入脉冲的作用下进行正确计数。

清零和置数功能正常,能够满足实验要求。

2、结果分析通过对计数器输出波形的观察和分析,验证了计数器的工作原理和逻辑功能。

三位二进制模5计数器 课程设计

课程设计任务书学生姓名专业班级指导教师学院名称一、题目:三位二进制模5计数器。

当外部输入X = 1时,计数器加2计数;外部输入X = 0时,计数器加1计数。

“模5”为逢“5”进1计数。

原始条件:使用D触发器( 74 LS 74 )、“与”门( 74 LS 08 )、“或”门( 74 LS 32 )、非门( 74 LS 04 ),设计三位二进制模5计数器。

二、要求完成设计的主要任务如下:1.能够运用数字逻辑的理论和方法,把时序逻辑电路设计和组合逻辑电路设计相结合,设计一个有实际应用的数字逻辑电路。

2.使用同步时序逻辑电路的设计方法,设计三位二进制模5计数器。

写出设计中的三个过程。

画出课程设计图。

3.根据74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路引脚号,在设计好的三位二进制模5计数器电路图中标上引脚号。

4.在试验设备上,使用74 LS 74、74 LS 08、74 LS 32、74 LS 04集成电路连接、调试和测试三位二进制模5计数器电路。

三、课程设计进度安排:序号课程设计内容所用时间1 设计三位二进制模5计数器电路 1天2 电路连接、调试和测试 3天3 分析总结设计,撰写课程设计 1天合计 5天指导教师签名:年月日系主任(责任教师)签名:年月日三位二进制模5计数器课程设计一.课程设计内容:1.三位二进制模5计数器逻辑结构Y2 Y1 Y0 计数器输出三位二进制模5计数器时钟输入( 手工)2.三位二进制模5计数器设计1)第一步:建立状态转移真值表(状态图)真值表x y2 y1yD2D1D0y2(n+1)y1(n+1)y0(n+1)0 0 0 0 0 0 1 0 0 10 0 0 1 0 1 0 0 1 00 0 1 0 0 1 1 0 1 10 0 1 1 1 0 0 1 0 00 1 0 0 0 0 0 0 0 0 0 1 0 1 d d d d d d 0 1 1 0 d d d d d d0 1 1 1 d d d d d d1 0 0 0 0 1 0 0 1 01 0 0 1 0 1 1 0 1 11 0 1 0 1 0 0 1 0 01 0 1 1 0 0 0 0 0 01 1 0 0 0 0 1 0 0 11 1 0 1 d d d d d d1 1 1 0 d d d d d d1 1 1 1 d d d d d d2)第二步:激励函数卡诺图和激励函数表达式激励函数卡诺图:D2:D1:D0:激励函数表达式:D2=y1(x⊕y0);D1=x(y1⊕y0)+x1y2y;D0=0x+x1y(y2+y0);y2yy2(n+1)=D2;y1(n+1)=D1;y0(n+1) =D03) 第三步:画出三位二进制模5计数器的逻辑电路图,同时标出电路引脚。

数字集成电路课程设计

摘要Verilog HDL是一种硬件描述语言,是EDA技术的重要组成部分。

使用HDL 进行数字系统设计是电子设计技术的发展趋势和方向,因此学好这门知识并能够灵活运用于课程设计是非常有必要也非常有意义的。

本次设计主要实现了一个任意分频器的简单功能。

主要有以下两种方案:(一)对被分频时钟的上升沿和下降沿同时计数,计数到分频系数的一半时,对输出时钟进行电平翻转,从而得到占空比为50%的分频时钟。

(二)对被分频时钟的上升沿和下降沿分别计数,得到一个上升沿分频时钟clk_p 和一个下降沿分频时钟clk_q,最后通过对这两个时钟进行相应的逻辑运算,便可得到占空比为50%的输出时钟。

在仿真过程中,主要遇到的问题是无法综合。

经讨论思考发现对同一时钟的上升沿和下降沿同时进行操作时,Quartus II将无法对这一行为进行综合。

最后,为解决综合的问题,我们对程序进行了必要的修改。

最终,我们经过比较选择了方案(二),实现了预期的目标。

【关键词】Verilog HDL 任意分频器半整数分频综合ABSTRACTVerilog HDL is a hardware description language which is an important part of EDA technology. Nowadays,using HDL to design Digital systems is the development trend of electronic design technologies. So it is very necessary and very meaningful to learn this course and develop the ability to apply the knowledge learned to curriculum design flexibly.This design mainly realized a simple function of frequency divider at any frequency coefficients . Basically,we have the following two schemes:First: counting at the rise and fall of the input clock simultaneously, when arrive at half of the frequency coefficients, overturn the output clock, so a clock whose duty ratio is 50% can be achieved;Second: to get a clk_p at the rise of the input clock and a clk_q at the fall of the input clock respectively, then through the corresponding logic operation of the two clock,the wanted output clock can be easily achieved.In the debugging process, the main problem is unable to be synthesized. After discussion and reflection,we found that operations on one clock’s rise and fall at the same time are unable to be synthesized by Quartus II. Finally, in order to solve the problem, we have the program changed where is necessary and we choose the second scheme to meet the desired goals by comparison.【Key words】Verilog HDL Synthesize Divide at any Frequency Coefficients Frequency Division at Half an Integer第一章系统设计第一节课题目标及总体方案《集成电路设计》是一门专业性、技术性、应用性很强的学科,实验课教学是它的一个极为重要的环节。

三位十进制计数器

长沙学院数电课程设计说明书题目三位十进制计数器系(部) 电子与通信工程系专业(班级) 光电信息工程专业一班姓名***学号**********指导教师***起止日期06.11-06.15010级光电信息工程专业课程设计任务书(课题)系(部):电子与通信工程系专业:光电信息工程长沙学院课程设计鉴定表目录一.课程设计的目的 (6)二.课程设计课题 (6)三.课程设计内容 (7)四、设计步骤: (7)五.设计要点: (7)六.设计原理: (8)1.部分器件介绍: (8)2.+5V直流电源工作原理: (13)3.三位十进制计数器工作原理: (13)七:电路仿真 (14)1.M ULTISIM仿真图 (14)2.P ROTEL原理图: (16)3.PCB板: (18)八:心得体会 (19)九:参考文献 (19)三位十进制计数器的设计摘要本次课程设计的课题是三位十进制计数器,就设计所选用的器材而言,主要用到了3个74LS192,3个CD4511,3个七段数码管,1个555芯片以及一些电阻和电容。

74LS192是双时钟方式的十进制可逆计数器,这使得设计本身简单了许多。

设计中采用555芯片制成一脉冲发生器,为电路提供连续脉冲。

CD4511是7段数码管译码器,将74LS192的输出信号译码成数码管可识别的信号。

然后Multisim仿真软件测试和分析电路性能,并用protel软件绘制原理图,设计pcb板,本次设计的计数器是三位十进制加计数器,由上升沿触发,通过CO输出与其他的芯片级联。

达到进位输出!另外,本设计要求自己设计一个直流+5v电源,故用到了LM7805,以及变压器和整流桥堆!关键词:三位十进制计数器,74LS192芯片,555芯片,脉冲发生器,加计数器,上升沿触发,+5v直流电源,Multisim仿真,Protel原理图,PCB板。

一.课程设计的目的1.激发学生的学习热情,最大限度的发挥学生的潜能。

2.对所学过的知识进行强化加深,了解设计一般数电产品的基本程序,方法及过程。

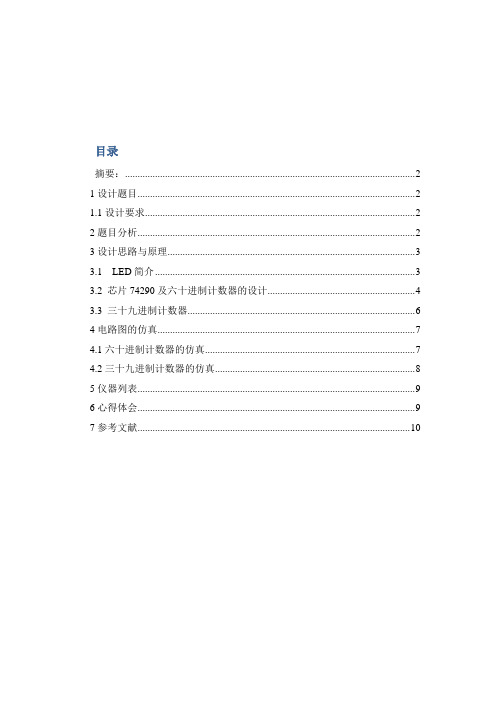

数电课程设计(60进制计数器设计)

目录摘要: (2)1设计题目 (2)1.1设计要求 (2)2题目分析 (2)3设计思路与原理 (3)3.1 LED简介 (3)3.2 芯片74290及六十进制计数器的设计 (4)3.3 三十九进制计数器 (6)4电路图的仿真 (7)4.1六十进制计数器的仿真 (7)4.2三十九进制计数器的仿真 (8)5仪器列表 (9)6心得体会 (9)7参考文献 (10)摘要:要获得N进制计数器,常用的方法有两种:一是用时钟触发器和门电路来设计:二是用集成计数器来构成。

当要得到一些进制数大的计数器时,用时钟触发器和门电路来实现就显的很复杂。

我们就可以用集成计数器来构成,当然集成计数器是厂家已定型的产品,其函数关系已被固化在芯片中,状态分配以及编码我们自己是不可以更改的,而且多为纯自然态序编码,因而利用清零端或置数控制端,让电路跳过某些状态而获得N进制的计数器。

1设计题目60进制计数器的设计1.1设计要求(1)要求学生掌握74系列的芯片和LED的原理和使用方法。

(2)熟悉集成电路的使用方法,能够运用所学的知识设计一规定的电路。

1.2设计任务(1)完成一个60进制的计数器。

(2)LED显示从00开始,各位计数从0—9,逢10 进1,是为计数0—5。

59显示后,又从00重新开始计数。

2题目分析要实现60进制的计数器,单用一片计数器无法实现,我们可以利用级联方式获得大容量的N进制计数器,60进制的计数器就可以由六进制和十进制计数器级联起来构成。

CP 3设计思路与原理 3.1 LED 简介LED 是一种显示字段的显示器件,7个发光二极管构成七笔字形“8”,一个发光二极管构成小数点。

七段发光管分别称为a 、b 、c 、d 、e 、f ,g ,构成字型“8”,如图(a )所示,当在某段发光二极管上施加一定的电压时,某些段被点亮发光。

不加电压则变暗,为了保护各段LED 不被损坏,需外加限流电阻。

信号源 计数器数码显示器十进制计数器(个位)六进制计数器(十位)其真值表如下。

计数器电路的设计与应用技巧

计数器电路的设计与应用技巧计数器是数字系统中常用的电路元件,广泛应用于各种场合,如时钟、计时器以及信号处理等。

设计一个高效可靠的计数器电路需要考虑多个因素,包括电路的类型选择、计数方式和电路的优化等。

本文将探讨计数器电路的设计与应用技巧,帮助读者更好地理解和应用计数器电路。

第一部分:计数器电路的基本原理计数器电路的基本原理是利用触发器或计数芯片实现二进制计数。

触发器是数字电路中的重要组件,具有记忆功能,可根据输入信号的变化切换输出状态。

常用的触发器有RS触发器、JK触发器和D触发器等。

计数芯片是一种具有计数功能的集成电路,常用的计数芯片有74LS90、74LS91和74LS93等。

第二部分:计数器电路的类型选择在实际应用中,计数器电路分为两类:同步计数器和异步计数器。

同步计数器是指所有触发器的时钟输入信号都相同,同步地更新计数状态。

同步计数器的优点是计数稳定,适用于计数频率较高的场合。

异步计数器是指各触发器的时钟输入信号不同,可以独立更新计数状态。

异步计数器适用于计数频率较低,且需要灵活控制计数方式的场合。

第三部分:计数器电路的计数方式计数器电路的计数方式包括二进制计数、十进制计数和BCD码计数等。

其中,二进制计数是最常用的计数方式,每个触发器的输出状态代表一个二进制位,逢二进一。

十进制计数是指在二进制的基础上进行十进展开,常用的十进制计数器电路有74LS90,可通过连接多个74LS90实现大范围的十进制计数。

BCD码计数是一种特殊的计数方式,BCD码是二进制码和十进制码的结合,常用于显示和计数器等应用场合。

第四部分:计数器电路的优化技巧为了提高计数器电路的稳定性和性能,有几点优化技巧值得注意。

首先,选择合适的计数器芯片,根据实际需求选用适当的型号和规格。

其次,合理设计和布局电路,包括电路的连接方式、电源和地线的布置等。

此外,合理选择时钟频率和触发器的工作方式,确保计数器电路的稳定性和可靠性。

最后,进行适当的测试和调试,确保计数器电路的正常运行。

数字集成电路基础课程设计

数字集成电路基础课程设计课程简介数字集成电路基础课程是集成电路工程专业本科生课程中的一门重要基础学科。

该课程涵盖了数字逻辑、集成电路设计、数电实验等多个方面的知识内容。

在该课程中,学生需要通过理论学习和实践操作,掌握数字电路的原理、设计方法和实际应用技能。

本文将以数字集成电路基础课程设计为主题,介绍该课程的教学内容和实践操作,帮助学习者更好地理解和掌握数字集成电路的基础知识。

教学内容数字逻辑基础数字逻辑是数字集成电路的基础,是该课程的核心教学内容。

数字逻辑研究数字信号之间的逻辑关系,包括逻辑与、逻辑或、逻辑非、逻辑异或等基本逻辑运算。

在学习数字逻辑时,需要了解数字信号的二进制表示方法、布尔代数和卡诺图等基础知识。

数字系统设计数字系统设计是将数字逻辑电路进行组合与/或时序逻辑设计的步骤。

基于数字逻辑门电路的基本组合,进行多输入布尔函数模块设计。

时序逻辑设计考虑输出信号与输入信号的时间关系,如系统时钟、触发器、寄存器等。

数字系统设计需要根据实际需求和技术限制,进行逻辑电路的设计和性能分析。

器件及电路实验器件及电路实验是数字集成电路课程教学中的重要部分,通过实验操作,学生可以更直观地了解数字电路实现的基本方法和器件性能。

常见实验项目有数字逻辑门电路实验、复合逻辑电路实验、数码管实验等。

在实验中需要熟悉使用数字集成电路器件和测试设备,同时学习实验数据采集、分析和处理方法。

课程设计数字集成电路基础课程的设计是学生对所学知识的运用实践,在课程结束前,通常需要完成一个综合设计项目。

项目通常包括以下步骤:1.项目选题。

可以从学生已经学习的知识点中选择一个合适的题目,如数字时钟设计、计数器设计等。

2.项目计划。

制定项目计划,明确各个阶段的任务和时间要求,制定检查和控制措施。

3.电路设计。

根据选题确定电路设计方案,包括逻辑设计和电路实现等环节。

4.电路实现。

根据设计方案,使用数字集成电路器件和测试设备完成电路的搭建和调试,并记录相关数据。

集成电路课程设计模三计数器设计

集成电路课程设计题目模三计数器设计姓名学号专业班级湖南大学集成电路课程设计第1页引言计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器可以用来显示产品的工作状态,一般来说主要是用来表示产品已经完成了多少份的折页配页工作。

以电子计数器为代表的计数器于本世纪五十年代初问世,二十多年来发展十分迅速,目前的面貌已焕然一新,性能不断完善,功能不断扩大,自动化程度不断提高,早已冲破了早期只能用于测量频率或计数的概念而渗透到各个测量技术领域中,成为尖端科学研究、通讯、导航以及精密计量不可缺少的设备。

在数字电子技术中应用的最多的时序逻辑电路。

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

但是并无法显示计算结果,一般都是要通过外接LCD或LED屏才能显示。

大部分计数器如电子计数器等都经历了电子管、晶体管、集成电路三个发展阶段。

集成电路的发展和应用,使计数器有可能采用最先进的电路元件和技术,因而电子计数器的性能更臻完美。

随着计数器技术的不断发展与进步,计数器的种类越来越多,应用的范围越来越广,随之而来的竞争也越来越激烈。

过硬的技术也成为众多生产厂商竞争的焦点之一。

厂商为了在竞争中处于不败之地,从而不断地改进技术,增加产品的种类。

现计数器的种类已增加到:电磁计数器、电子计数器、机械计数器(拉动机械计数器、转动机械计数器、按动机械计数器、测长机械计数器)、液晶计数器等,计数器的应用范围也遍布各个行业。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路课程设计题目模三计数器设计姓名学号专业班级引言计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

计数器可以用来显示产品的工作状态,一般来说主要是用来表示产品已经完成了多少份的折页配页工作。

以电子计数器为代表的计数器于本世纪五十年代初问世,二十多年来发展十分迅速,目前的面貌已焕然一新,性能不断完善,功能不断扩大,自动化程度不断提高,早已冲破了早期只能用于测量频率或计数的概念而渗透到各个测量技术领域中,成为尖端科学研究、通讯、导航以及精密计量不可缺少的设备。

在数字电子技术中应用的最多的时序逻辑电路。

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。

但是并无法显示计算结果,一般都是要通过外接LCD或LED屏才能显示。

大部分计数器如电子计数器等都经历了电子管、晶体管、集成电路三个发展阶段。

集成电路的发展和应用,使计数器有可能采用最先进的电路元件和技术,因而电子计数器的性能更臻完美。

随着计数器技术的不断发展与进步,计数器的种类越来越多,应用的范围越来越广,随之而来的竞争也越来越激烈。

过硬的技术也成为众多生产厂商竞争的焦点之一。

厂商为了在竞争中处于不败之地,从而不断地改进技术,增加产品的种类。

现计数器的种类已增加到:电磁计数器、电子计数器、机械计数器(拉动机械计数器、转动机械计数器、按动机械计数器、测长机械计数器) 、液晶计数器等,计数器的应用范围也遍布各个行业。

本次课程设计是在小红帽系统上,利用cadence 软件设计一个钟控模三计数器,实现三个周期的脉冲输出并且进行验证。

主体设计一、实验要求:1、利用cadence 软件制作钟控模三计数器,电源电压V V DD 3.3=, 时钟周期10ns ,输出延迟不超过1ns ;2、自建单元库,并且每个单元输出都有仿真波形。

二、设计思路分析:模三计数器为两位二进制计数,从00,01,10循环计数,在不同的计数状态下分别输出一个周期的脉冲信号.钟控模三计数器有一个用于输入CP 信号的信号输入端,以及三个信号输出端口分别为X 、Y 、Z 。

由于其三个输出端的输出信号是由两位二进制计数控制。

二进制计数从00,01,10循环计数,三个计数状态分别对应三种周期脉冲信号分别由X 、Y 、Z 输出,因此需要设计一个钟控二进制循环计数器,CP 信号上升沿时状态发生转换。

状态转换真值表如下:由A Q 、B Q 输出状态对应的三种状态真值表如下:由此得逻辑表达式如下:A B X Q Q =•B A Q Q Y •=A B Z Q Q =•三、电路设计:根据状态分析和逻辑表达式,可采用与门、非门和D 触发器构成符合要求的计数器,而与门、非门和D 触发器都可以在cadence 下用CMOS 器件构成。

1、反相器(非门)设计首先,进入Cadence ,建立个人工作目录。

在登陆工作站后,于桌面空白处右键,tools-->Terminal ,打开终端。

在终端中输入 mkdir mydir,然后进入自己的工作目录cd mydir 。

启动Cadence ,在终端中输入命令icfb& 出现Cadence 初始界面,打开Cadence 的主控窗口CIW(Command Interpreter Window),随后建立个人工作库。

单击菜单栏Tools-->Library Maneger,打开LM(Library Maneger)窗口,点击File-->New-->Library,打开New Library窗口,在Name一栏输入要新建的库名zhengzhongfeng,然后单击OK确定。

出现Technology File设置窗口,选择第一项Compile a new techfile,单击OK确定。

出现Load Technology File窗口,建立名为zhengzhongfeng的新库。

通过CIW来新建原理图,在CIW窗口File-->New-->CellView,弹出新建对话框,于Library Name栏选择自己的工作库,如mylib,在Cell Name栏输入原理图名字,如invert,于Tool栏选择Composer-Schematic,此时View Name栏自动变为schematic,最后单击OK。

这样就会弹出Composer主界面,新建原理图成功。

点击菜单栏-->Add-->Instance 添加器件,先绘制一个CMOS反相器形成非门单元。

依次点击analogLib--> Actives -->pm-->symbol,再单击close。

刚才的添加器件窗口发生变化。

可以发现Library,Cell,View等都自动填上了相应的信息。

同时多出了一些参数列表(拖动滚动条可以看到更多)。

点击Hide隐藏当前窗口,此时鼠标对应有一个PMOS的symbol,移动PMOS到合适的位置点击鼠标左键将其放下。

继续放置NMOS晶体管、电源与地。

对应的器件名称为nmos4,vdd,gnd。

放完所有器件后进行连线,键入快捷键w,进入连线命令后,于起点单击左键,再于终点单击左键。

画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。

现在设置元件参数,单击PMOS选中它,这样PMOS 会被一个白色方框包围,然后键入快捷键q,会弹出属性编辑对话框。

这里填上model name,以及PMOS的栅长和栅宽。

栅长设为常量550n,而栅宽设为函数pPar(“wp”),模型名填p18,这是因为这里采用的Spice模型是由SMIC提供的,对应PMOS的模型有p18和p33两种,18代表电源电压为1.8V。

同样的方法继续设置NMOS参数,只是模型名为n18,栅长为固定值550n,栅宽设为pPar(“wn”)。

完成以上工作后,还必须放置I/O端口以标明电路的输入输出。

键入快捷键p,执行放置端口命令后,会弹出对话框。

于Pin Names栏输入端口名Vin,于Direction 栏选择input,点击Hide,然后将端口放到反相器的左边输入线上。

同样的方法再放置输出端口,端口方向要改为output,名称为Vout,将其放在反相器右边的输入线上。

最终的完成图如图下图所示:设计完成的电路图需要经过检查方能进行仿真,单击菜单栏->Check and Save或者键入快捷键大写的X,对电路进行检查并存储。

对反相器创建Symbol,CIW窗口菜单栏->Open,弹出打开对话框,选择自己的库,然后选择器件inverter,再于viewname栏选schematic,点击OK打开画好的反相器原理图。

Composer窗口菜栏->Design->Create CellView->From Cellview,弹出Cellview from Cellview窗口,点击OK。

显示出Symbol编辑窗口,选中绿色矩形框,delete之,然后Add->-Shape>Polygon,在刚才矩形框的位置画一个三角形。

鼠标在三个端点点3次即可。

注意在三角形右边留出画圆圈的位置。

再Add->Shape->Circle,先于圆心位置单击左键,再移动鼠标,得到合适的圆的半径后左键确认。

再把图中的输入输出端口以及partname和instanceName 移动到合适位置。

最后再把红色框大小修改合适(框住三角形和端口)。

画好的Symbol后点击Design->check and save保存。

最后对反向器创建仿真电路进行仿真测试。

画出测试电路,如下图所示:得波形图:将波形图放大:从上图可以看出输出延迟不超过1ns,符合设计要求。

至此,反向器即非门单元设计完成。

2、与门设计与门的逻辑关系表达式为Y=AB,在集成电路中用基本的CMOS 单元构成的与非门和非门组合构成与门。

其中,与非门由两个PMOS 管和两个NMOS 管组成。

在candence 软件中的原理图为在A、B 两输入端施以频率不同的方波分别作为时钟脉冲输入和信号输入,输出端接电容作为负载,对与门的仿真电路原理图如下:对与门仿真测试得仿真波形:将波形放大:可以看出输出延迟不超过1ns,符合设计要求。

3、D触发器电路设计触发器有电平触发和边沿触发两种。

低电平触发的主从触发器工作时,必须在上升沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

所以边沿D 触发器也称为维持阻塞边沿D 触发器。

对D触发器的设计电路图如下所示:对D触发器的仿真电路如下图所示:得仿真波形图:将波形图放大:从波形放大图可以看出输出延迟不超过1ns,符合设计要求。

4、下面用非门、与门和D触发器根据真值表制作钟控模三计数器实现电路如下:对计数器仿真:得仿真波形:将波形放大:从波形放大图可以看出输出延迟不超过1ns,符合设计要求。

结论:从非门、与门、D触发器及其构成的计数器的仿真图和波形图可以看出,利用cadence制作的钟控模三计数器,其各个单元都工作正常,且都有满足需要的仿真波形输出,整个模三计数器达到设计要求。

通过这短短的一周课程设计的时间,从打开小红帽系统,到建立个人工作库、添加器件输入电路图、创建Symbol 和电路仿真,我们逐渐熟悉的小红帽系统提以及cadence软件的时候,这次课程设计让我们深深的体会到自己所学的不足之处以及理论知识对于实验的重要性。

参考文献:康华光.电子技术基础(数字部分)[M].北京:高等教育出版社,2009.朱正涌.半导体集成电路[M].北京:清华大学出版社,2011.《Cadence 电路设计案例精解》编写组. Cadence 电路设计案例精解[M].北京:机械工业出版社,2010.。