USB识别及阻抗匹配(二类参照)

阻抗匹配计算理解与方法

(1)差分信号首先来看一下什么是差分信号吧。

1、差分信号差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相同,相位相反。

在这两根线上的传输的信号就是差分信号。

信号接收端比较这两个电压的差值来判断发送端发送的是逻辑0还是逻辑1。

在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

一般类型有:USB、以太网、PCIE、SATA、RS485、RS422、HDMI、LVDS常用对有:+/- PM/PN TXN/TXP2、差分信号与单端走线的比较差分信号与传统的一根信号线一根地线(即单端信号)走线的做法相比,其优缺点分别是:优点:抗干扰能力强。

干扰噪声一般会等值、同时的被加载到两根信号线上,而其差值为0,即,噪声对信号的逻辑意义不产生影响。

能有效抑制电磁干扰(EMI)。

由于两根线靠得很近且信号幅值相等,这两根线与地线之间的耦合电磁场的幅值也相等,同时他们的信号极性相反,其电磁场将相互抵消。

因此对外界的电磁干扰也小。

时序定位准确。

差分信号的接收端是两根线上的信号幅值之差发生正负跳变的点,作为判断逻辑0/1跳变的点的。

而普通单端信号以阈值电压作为信号逻辑0/1的跳变点,受阈值电压与信号幅值电压之比的影响较大,不适合低幅度的信号。

缺点:若电路板的面积非常吃紧,单端信号可以只有一根信号线,地线走地平面,而差分信号一定要走两根等长、等宽、紧密靠近、且在同一层面的线。

这样的情况常常发生在芯片的管脚间距很小,以至于只能穿过一根走线的情况下。

(So,差分信号要优先布线)(2)关于差分的五个常见误区误区一:认为差分信号不需要地平面作为回流路径,或者认为差分走线彼此为对方提供回流途径。

造成这种误区的原因是被表面现象迷惑,或者对高速信号传输的机理认识还不够深入。

虽然差分电路对于类似地弹以及其它可能存在于电源和地平面上的噪音信号是不敏感的。

地平面的部分回流抵消并不代表差分电路就不以参考平面作为信号返回路径,其实在信号回流分析上,差分走线和普通的单端走线的机理是一致的,即高频信号总是沿着电感最小的回路进行回流,最大的区别在于差分线除了有对地的耦合之外,还存在相互之间的耦合,哪一种耦合强,那一种就成为主要的回流通路。

USB 2.0测试规范

Apple数据线, MFI测试此项

90欧+/-15%(76.5-103.5 欧)

Apple数据线, MFI测试此项

30欧+/-30%(39-21欧)

5.2ns/m

1. 信号对绞线绞距; TDR(时域反 2.信号对绞线绝缘材质(介质常 射仪) 数) 1. 信号对绞线对称性和一致性; TDR(时域反 2. 成品长度; 射仪) 3. 信号对绞线裁剥及焊接尺寸 眼图测试是判定 信号质量好坏相 当理想的工具, PG 综以上测试项目有直接或间接影 但对于线材高频 信号发生器 响 特性改善分析无 法提供有效的改 善方向。 1. 线材本身的屏蔽效果(铝 箔,编织,缠绕,外被防电磁材 料); 2. 线材与连接器加工连接处屏 蔽处理工艺(比如铝箔及编织的 破坏程度;连接器铁壳有没有接 地或与马口铁焊接等 3. 是否有磁环 测试Cable连接 终端设备产品一 般测试EMI(电 磁干扰),测试 频率范围: 30MHZ到1GHZ,一 般采用室内测试 (3M或10M暗 室)

100ps

6

眼睛张开程度大小(以波罩 眼图 Eye Mask模块为中心),眼 Eye 图接触到Eye Mask则表示信 Diagram 号质量不好,离Eye Mask越 远,则信号质量越好。

1、电波暗室 2、接收机 3、接收天线 电磁兼容 依客户标准(如0dB,-2dB,- 4、频谱仪 7 3dB,-4dB,-6dB等) EMC 6、转台、升 降台 7、转台、升 降台控制器

USB 2.0 测试规范及影响因素一栏表

No. 测试项目 测试标准 Frequency(MH dB/Cable(Max Z) imum) 0.512 0.13 衰减 Signal 1 Pair attenuat ion 0.772 1 4 8 12 24 48 96 200 400 差模阻抗 Differen 2 tial Impedanc e 同模阻抗 Common 3 Impedanc e 延迟 Propagat 4 ion Delay 延迟差 ew 0.15 0.2 0.39 0.57 0.76 0.95 1.35 1.9 3.2 5.8 测试仪器 影响因素 1. 信号线导体截面积与长度不 匹配 2. 加工信号芯线时伤到芯线导 NA(网络分 体 析仪)或依 EIA364-101 3.信号芯线导体材质 以 Open/Short 4.信号线导体的光泽度及纯度 量测 5. 信号线导体的绝缘材质(介 质常数) 6. 信号线的对绞绞距及包带异 常 1. 信号芯线ID; 2. 信号线的同心度及真圆度; 3. 信号线绝缘材质(介质常 TDR(时域反 数); 射仪) 4. 焊接时锡点饱和度,有无锡 尖,芯线绝缘皮是否后缩 5. 线材与连接器阻抗匹配 备注

USB识别及阻抗匹配

USB识别及阻抗匹配2016/11/22修改记录:目录B传送数率.........................................................................................................................B接口定义.........................................................................................................................B识别.................................................................................................................................2.1.全速和低速识别......................................................................................................................2.2.高速识别..................................................................................................................................B匹配.................................................................................................................................1.概述USB是英文universalserialbus通用串行总线的缩写,是一个外部总线标准,用于规范电脑和外部设备的链接和通信。

关于USB通信阻抗匹配的问题(转载)

关于USB通信阻抗匹配的问题(转载)1.未加终端电阻的波形(还是可以通讯的)2.加上终端电阻的波形(通讯稳定性增强)最近对USB2.0协议进行了研究,也算是略知皮毛了,在这期间也遇到过很多问题,也在网上找过解答,首先我要感谢网络这个强大的东西,为我答疑解惑,其次也想提醒大家网络上的东西一定要持怀疑的态度来看;下面就解说下关于网上所说的USB匹配电阻的问题。

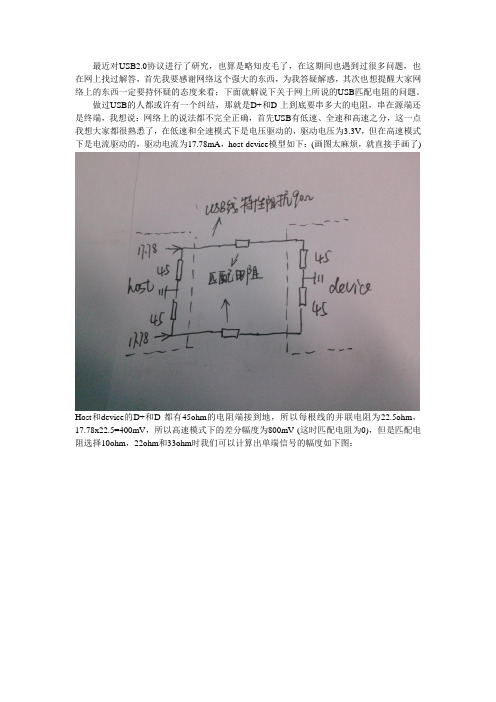

做过USB的人都或许有一个纠结,那就是D+和D-上到底要串多大的电阻,串在源端还是终端,我想说:网络上的说法都不完全正确,首先USB有低速、全速和高速之分,这一点我想大家都很熟悉了,在低速和全速模式下是电压驱动的,驱动电压为3.3V,但在高速模式下是电流驱动的,驱动电流为17.78mA,host-device模型如下:(画图太麻烦,就直接手画了)Host和device的D+和D-都有45ohm的电阻端接到地,所以每根线的并联电阻为22.5ohm,17.78x22.5=400mV,所以高速模式下的差分幅度为800mV (这时匹配电阻为0),但是匹配电阻选择10ohm,22ohm和33ohm时我们可以计算出单端信号的幅度如下图:由此可得高速模式下加入匹配电阻会使信号幅度下降,使信号质量变差,加入匹配电阻后的眼图分别如下:10ohm22ohm那么网上所说的匹配电阻都是错的么?也不是啦!网上所说的匹配电阻都是在全速和低速模式下的,全速模式下为电压驱动的,驱动器具有一定输出阻抗(一般较小),USB线的特性阻抗为90ohm所以要想源端与USB线匹配就需要串电阻,具体阻值是要根据驱动器的输出阻抗来决定的,即要求源端差分阻抗=USB线差分特性阻抗;而要终端匹配的话就需要并联电阻了(终端的阻抗一般很大),在驱动能力不强的情况下根本就没法实现;至于匹配电阻要放在源端还是终端,因为USB是双向的,所以要匹配源端的话则应串在源端,要匹配终端的话则要放在终端。

以上是鄙人通过所学知识对网上的关于USB疑问的一些解释,如有不对还请各位网友斧正!PS:为什么在讨论低速/全速时候,需要考虑USB线的90ohm特性阻抗,而讨论高速模式(电流驱动)的时候,又把USB线的电阻视为0了?22.5=45//45,其中45来自于低速/全速驱动器的内置导通电阻。

USBCAN CANalyst II分析仪 产品说明书

1.5 技术支持与服务

货到15日内无条件退换,5年免费维修、终身维修与升级服务。

技术支持及购买信息请查阅

淘宝官方旗舰店:/

Email: dspstudio@ 技术支持QQ:1877977019

1.6 产品选型

第二章 外形与接口描述 ......................................................................................................... 4 2.1 外观与接口 .................................................................................................................... 4 2.2 信号定义 ........................................................................................................................ 5 2.3 出厂配置 ........................................................................................................................ 6

1.3 典型应用

●通过PC或笔记本的USB接口实现对CAN总线网络的发送和接收; ●快速CAN网络数据采集、数据分析; ●CAN总线-USB网关; ●USB接口转CAN网络接口; ●延长CAN总线的网络通讯长度; ●工业现场 CAN 网络数据监控。

usb 共模电感 差模阻抗

USB共模电感和差模阻抗引言USB(Universal Serial Bus)是一种用于连接计算机和外部设备的通用接口标准。

在USB接口中,共模电感和差模阻抗是两个重要的参数,对于USB的性能和稳定性起着重要作用。

本文将详细介绍USB共模电感和差模阻抗的概念、特性以及其在USB接口中的作用。

USB共模电感共模电感是指在USB接口中用于抑制共模干扰的电感元件。

共模干扰是指通过共模信号线(如地线)传播的电磁干扰。

USB共模电感的作用是通过阻抗匹配和滤波的方式,将共模干扰信号尽可能地抑制在接口内部,以保证USB信号的稳定性和可靠性。

USB共模电感通常采用线圈形式,由绕组和磁芯组成。

绕组中的线圈通过电感耦合的方式,起到阻抗匹配和滤波的作用。

磁芯则用于增加电感的感应效果,提高共模电感的性能。

USB共模电感的特性主要包括电感值、频率响应和直流电阻。

电感值决定了共模电感对共模干扰信号的抑制能力,通常以亨利(H)为单位。

频率响应描述了共模电感在不同频率下的阻抗特性,常用的指标是频率响应曲线。

直流电阻则表示了共模电感在直流电路中的电阻值,对于USB信号的传输没有实质性影响。

USB差模阻抗差模阻抗是指在USB接口中用于匹配差模信号的阻抗。

差模信号是指通过差模信号线(如数据线)传播的电信号,用于传输实际数据。

USB差模阻抗的作用是保证差模信号的传输质量,避免信号的失真和损耗。

USB差模阻抗通常采用传输线的形式,由导体和绝缘层组成。

导体用于传输差模信号,绝缘层则用于隔离和保护导体。

差模阻抗的大小取决于导体的几何形状、材料特性和绝缘层的介电常数等因素。

USB差模阻抗的特性主要包括阻抗值、频率响应和传输损耗。

阻抗值决定了差模阻抗对差模信号的匹配程度,通常以欧姆(Ω)为单位。

频率响应描述了差模阻抗在不同频率下的阻抗特性,常用的指标是频率响应曲线。

传输损耗表示了差模信号在传输过程中的信号衰减程度,对于USB信号的传输质量有重要影响。

usb2a电阻

USB 2.0的A型接口(USB 2.0 Type-A)是USB标准中最为常见的一种接口。

在USB 2.0标准中,对于USB Type-A接口的电阻要求,通常指的是端接电阻(Termination Resistor)或上拉电阻(Pull-up Resistor)。

端接电阻在USB通信中扮演着重要的角色。

它们通常被连接到数据线的两端,用于吸收信号线上的反射和噪声,从而确保信号的质量和稳定性。

在USB 2.0标准中,这些电阻的阻值通常为56欧姆(Ω)。

除了端接电阻外,USB Type-A接口还可能包含其他类型的电阻,例如限流电阻(Current Limiting Resistor)或分压电阻(Voltage Dividing Resistor)等。

这些电阻的阻值和作用会根据具体的电路设计和应用需求而有所不同。

需要注意的是,在设计和使用USB Type-A接口时,必须严格遵循USB标准的规范和要求,以确保接口的正常工作和安全性。

如果您对USB接口的设计和使用有任何疑问或需要进一步的帮助,请咨询相关的专业人士或机构。

USB识别及阻抗匹配

USB识别及阻抗匹配2016/11/22修改记录:目录1.概述 (3)B 传送数率 (3)B接口定义 (3)B识别 (3)2.1.全速和低速识别 (3)2.2.高速识别 (4)B匹配 (8)1.概述USB是英文universal serial bus通用串行总线的缩写,是一个外部总线标准,用于规范电脑和外部设备的链接和通信。

B 传送数率B接口定义B识别我们知道USB2.0向下兼容USB1.x,即高速2.0的hub能支持所有的速度类型的设备,而USB1.x 的hub不能支持高速设备(High Speed Device)。

因此,如果高速设备挂到USB1.x的hub上,那该设备只能工作在全速模式下。

不管是hub还是设备(device),对于速度的区分是非常重要的,否则,后续的通信根本无法进行。

2.1.全速和低速识别根据规范,全速(Full Speed)和低速(Low Speed)很好区分,因为在设备端有一个1.5k的上拉电阻,当设备插入hub或上电(固定线缆的USB设备)时,有上拉电阻的那根数据线就会被拉高,hub根据D+/D-上的电平判断所挂载的是全速设备还是低速设备。

如下两图:USB全速设备上电连接(Full-speed Device Cable and Resistor Connections)USB低速设备上电连接(Low-speed Device Cable and Resistor Connections)2.2.高速识别USB全速/低速识别相当简单,但USB2.0,USB1.x就一对数据线,不能像全速/低速那样仅依靠数据线上拉电阻位置就能识别USB第三种速度:高速。

因此对于高速设备的识别就显得稍微复杂些。

高速设备初始是以一个全速设备的身份出现的,即和全速设备一样,D+线上有一个1.5k的上拉电阻。

USB2.0的hub把它当作一个全速设备之后,hub和设备通过一系列握手信号确认双方的身份。

USB 匹配电阻

最近对USB2.0协议进行了研究,也算是略知皮毛了,在这期间也遇到过很多问题,也在网上找过解答,首先我要感谢网络这个强大的东西,为我答疑解惑,其次也想提醒大家网络上的东西一定要持怀疑的态度来看;下面就解说下关于网上所说的USB匹配电阻的问题。

做过USB的人都或许有一个纠结,那就是D+和D-上到底要串多大的电阻,串在源端还是终端,我想说:网络上的说法都不完全正确,首先USB有低速、全速和高速之分,这一点我想大家都很熟悉了,在低速和全速模式下是电压驱动的,驱动电压为3.3V,但在高速模式下是电流驱动的,驱动电流为17.78mA,host-device模型如下:(画图太麻烦,就直接手画了)Host和device的D+和D-都有45ohm的电阻端接到地,所以每根线的并联电阻为22.5ohm,17.78x22.5=400mV,所以高速模式下的差分幅度为800mV (这时匹配电阻为0),但是匹配电阻选择10ohm,22ohm和33ohm时我们可以计算出单端信号的幅度如下图:眼图分别如下:10ohm22ohm33ohm那么网上所说的匹配电阻都是错的么?也不是啦!网上所说的匹配电阻都是在全速和低速模式下的,全速模式下为电压驱动的,驱动器具有一定输出阻抗(一般较小),USB线的特性阻抗为90ohm所以要想源端与USB线匹配就需要串电阻,具体阻值是要根据驱动器的输出阻抗来决定的,即要求源端差分阻抗=USB线差分特性阻抗;而要终端匹配的话就需要并联电阻了(终端的阻抗一般很大),在驱动能力不强的情况下根本就没法实现;至于匹配电阻要放在源端还是终端,因为USB是双向的,所以要匹配源端的话则应串在源端,要匹配终端的话则要放在终端。

以上是鄙人通过所学知识对网上的关于USB疑问的一些解释,如有不对还请各位网友斧正!网友:二郎神君QQ:865896096转载请注明出处!更多USB、SD卡等精彩内容请到/u/2080044107。

usb接口数据线上的电平标准

USB接口数据线上的电平标准一、 USB接口的电平标准USB(Universal Serial Bus)是一种用于连接计算机和外部设备的串行总线标准。

USB接口数据线上的电平标准对于USB设备的正常连接和通讯起着至关重要的作用。

USB接口的电平标准分为USB 2.0和USB 3.0两种版本,下面将分别介绍它们的电平标准。

1. USB2.0电平标准USB 2.0是一种常见的USB接口标准,其电平标准主要包括数据线电压、数据传输速度、数据线电流和数据线的阻抗。

(1)数据线电压:USB 2.0规定了数据线的高电平和低电平的电压范围,分别为0.0V-0.3V和2.8V-3.6V。

数据线的电压范围对于设备的正常通讯起着至关重要的作用,如果电压超出了规定范围,可能会导致设备无法正常工作。

(2)数据传输速度:USB 2.0标准规定了数据传输速度为最高480Mbps,这一速度已经能够满足大多数外部设备和计算机的数据传输需求。

(3)数据线电流:USB 2.0规定了数据线的电流最大为500mA,这一电流可以满足大部分外部设备的供电需求。

(4)数据线阻抗:USB 2.0标准规定了数据线的阻抗为90ohms,这一阻抗值对于保证数据传输信号质量起着至关重要的作用。

2. USB3.0电平标准USB 3.0是USB接口的下一代标准,其电平标准相比USB 2.0有了很大的提升。

USB 3.0的电平标准主要包括数据线电压、数据传输速度、数据线电流和数据线的阻抗。

(1)数据线电压:USB 3.0规定了数据线的高电平和低电平的电压范围,分别为0.0V-0.3V和2.8V-3.6V。

与USB 2.0相比,USB 3.0的电压范围并没有变化。

(2)数据传输速度:USB 3.0标准规定了数据传输速度为最高5Gbps,这一速度是USB 2.0的10倍,能够更好地满足高速数据传输的需求。

(3)数据线电流:USB 3.0规定了数据线的电流最大为900mA,相比USB 2.0有了一定的提升,可以更好地满足外部设备的供电需求。

usb绝缘阻抗测试标准

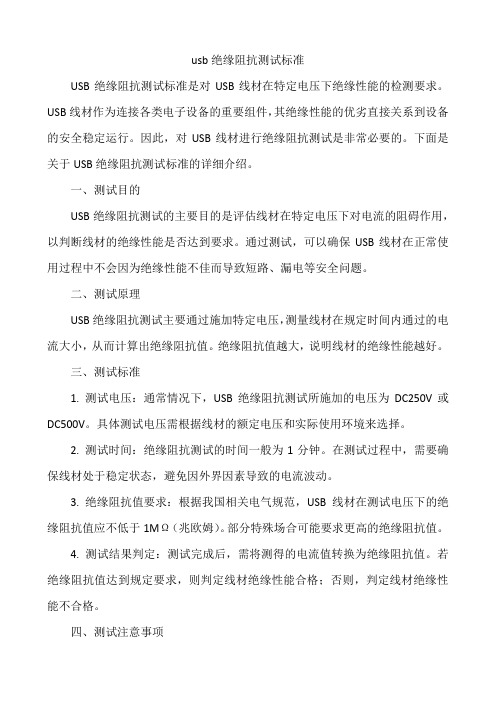

usb绝缘阻抗测试标准USB绝缘阻抗测试标准是对USB线材在特定电压下绝缘性能的检测要求。

USB线材作为连接各类电子设备的重要组件,其绝缘性能的优劣直接关系到设备的安全稳定运行。

因此,对USB线材进行绝缘阻抗测试是非常必要的。

下面是关于USB绝缘阻抗测试标准的详细介绍。

一、测试目的USB绝缘阻抗测试的主要目的是评估线材在特定电压下对电流的阻碍作用,以判断线材的绝缘性能是否达到要求。

通过测试,可以确保USB线材在正常使用过程中不会因为绝缘性能不佳而导致短路、漏电等安全问题。

二、测试原理USB绝缘阻抗测试主要通过施加特定电压,测量线材在规定时间内通过的电流大小,从而计算出绝缘阻抗值。

绝缘阻抗值越大,说明线材的绝缘性能越好。

三、测试标准1. 测试电压:通常情况下,USB绝缘阻抗测试所施加的电压为DC250V或DC500V。

具体测试电压需根据线材的额定电压和实际使用环境来选择。

2. 测试时间:绝缘阻抗测试的时间一般为1分钟。

在测试过程中,需要确保线材处于稳定状态,避免因外界因素导致的电流波动。

3. 绝缘阻抗值要求:根据我国相关电气规范,USB线材在测试电压下的绝缘阻抗值应不低于1MΩ(兆欧姆)。

部分特殊场合可能要求更高的绝缘阻抗值。

4. 测试结果判定:测试完成后,需将测得的电流值转换为绝缘阻抗值。

若绝缘阻抗值达到规定要求,则判定线材绝缘性能合格;否则,判定线材绝缘性能不合格。

四、测试注意事项1. 测试环境:USB绝缘阻抗测试应在干燥、通风的环境中进行,避免高温、高湿等因素对测试结果产生影响。

2. 测试设备:应使用精度高、性能稳定的绝缘电阻测试仪进行测试,确保测试结果的准确性。

3. 测试人员:测试人员需具备一定的电气知识,熟悉测试设备的使用方法,以确保测试过程的顺利进行。

4. 测试样品:测试样品应具有一定的代表性,可从生产过程中的不同批次、不同规格的线材中抽取。

5. 测试记录:测试过程中应详细记录测试条件、测试数据及测试结果,以备后续查验。

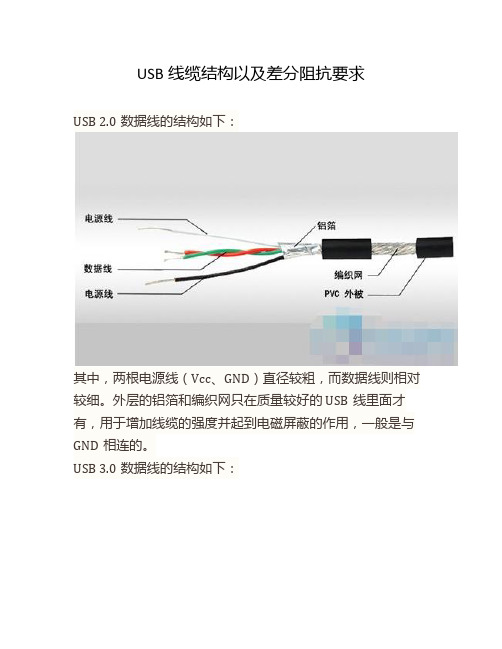

USB线缆结构及差分阻抗要求

USB线缆结构以及差分阻抗要求USB 2.0数据线的结构如下:其中,两根电源线(Vcc、GND)直径较粗,而数据线则相对较细。

外层的铝箔和编织网只在质量较好的USB线里面才有,用于增加线缆的强度并起到电磁屏蔽的作用,一般是与GND相连的。

USB 3.0数据线的结构如下:USB3.0关键信号总共8根,一对兼容USB2.0的差分信号,2对超高速差分信号,分别是发送差分对和接收差分对,如下图。

UTP用于传输USB 2.0信号,另外两对屏蔽双绞线SDP 用于超高速信号。

USB 3.0的导线数量较多,但基本结构与USB 2.0是相同的。

需要注意的是USB 3.0的数据线数量比较多,并且数据线传输的信号也是频率很高的信号,因此很多线缆加强了屏蔽(图中这个就是,可以看到有两组数据线拥有独立的屏蔽层)。

USB3.0的线缆和连接器同样是要做差分阻抗的。

线缆的差分阻抗要求是90Ω±5Ω。

匹配连接器的差分对阻抗要求90Ω±10Ω。

由于USB 3.0的速度达到了5.0Gbps,串行接口的时钟频率已经相当高。

目前只有6Gbps的SATA和SAS硬盘接口以及PCI-E 2.0/3.0总线的频率能够与之匹敌,而这些都是主要用于机箱内部的互连(SAS也可以用在外部,PCI-E则很少),USB 3.0却是连接在主机和外设之间。

为了保证信号的完整性,对控制器和线缆提出了更加严格的要求。

由于USB 3.0和2.0的速度相差10倍以上,再加上还有键盘/鼠标这样的USB 1.x低速外设的拖累,为了保持向下的兼容性USB 3.0采用了双总线架构(如上图)。

即在主机、Hub(集线器)、设备和线缆方面全部保留Non-SuperSpeed(USB 2.0)部分模块,在此基础上增加SuperSpeed(USB 3.0)功能模块。

这样做可以说是一种折中的办法,虽然增加了一部分成本,但是却很好的解决了兼容性的问题。

USB 3.0线缆结构示意图从上表我们看到,USB 3.0除了在数据速度上提升到5Gbps 之外,其传输界面也由USB 2.0的半双工(同一时间只能向一个方向传输数据)改为使用双重单工设计,这一点从上面的线缆图就已经能看出来。

USB 匹配

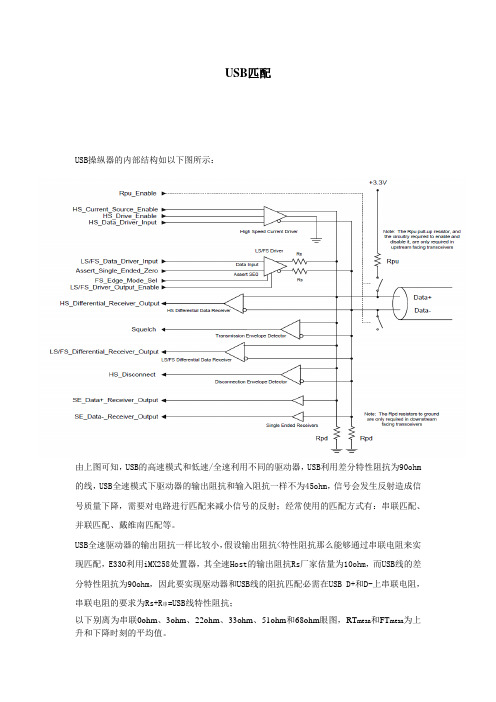

USB匹配USB控制器的内部结构如下图所示:由上图可知,USB的高速模式和低速/全速使用不同的驱动器,USB使用差分特性阻抗为90ohm的线,USB全速模式下驱动器的输出阻抗和输入阻抗一般不为45ohm,信号会发生反射造成信号质量下降,需要对电路进行匹配来减小信号的反射;常用的匹配方式有:串联匹配、并联匹配、戴维南匹配等。

USB全速驱动器的输出阻抗一般比较小,若输出阻抗<特性阻抗则可以通过串联电阻来实现匹配,E330使用iMX258处理器,其全速Host的输出阻抗Rs厂家预计为10ohm,而USB线的差分特性阻抗为90ohm,所以要实现驱动器和USB线的阻抗匹配必须在USB D+和D-上串联电阻,串联电阻的要求为Rs+R串=USB线特性阻抗;以下分别为串联0ohm、3ohm、22ohm、33ohm、51ohm和68ohm眼图,RT mean和FT mean为上升和下降时间的平均值。

R串 = 3ohm,RT mean = 3.30ns;FT mean = 2.80ns;R串 = 22ohm,RT mean = 3.71ns;FT mean = 3.12ns;R串 = 33ohm,RT mean = 4.36ns;FT mean = 3.61ns;R串 = 51ohm,RT mean = 4.88ns;FT mean = 4.50ns;当阻抗>特性阻抗时则要通过并联电阻来实现匹配,而在高速模式下,信号是通过电流源驱动的,以上匹配电阻的存在都将降低信号质量,下面分别举串联10ohm、22ohm和33ohm为例;没有串联电阻时的眼图如下:1、R串 = 10ohmU device = 17.78*45//(10+45) = 440.1mV,U host = 45/(45+10)*440.1 = 360.1mV;2、R串 = 22ohmU device = 17.78*45//(22+45) = 478.6mV,U host = 45/(45+22)*478.6 = 321.5mV;3、R串 = 33ohmU device = 17.78*45//(33+45) = 507.4mV,U host = 45/(45+33)*507.4 = 292.7mV;网友:二郎神君QQ:865896096 转载请注明出处!更多USB、SD卡等精彩内容请到/u/2080044107。

USB 3高频解决方法

USB 3.0 高频不过到底是连接器的原因还是线材的原因??从试验表明,USB 3.0高频测试不过,从报告上显示主要表现为:连接器阻抗,匹配阻抗,skew(A:对内延迟差;B:对间延迟差)。

其它问题都可以解决!一:按以下五个方案做分析!1:从原物料方面着手。

2:从我们的制做方法着手。

3:人员的手法是否正确。

4:制作环境是否影响产品。

5:机器设备是否满足产品的要求。

得出的结果是:1.2.3项对产品的性能有致命性的影响。

二:按以上三顶方案细部分析1:原物料主要是:连接器,线材!是否可以满足3.0产品的高频测试的要求!(这点我们可以从多选物料和切换供应商中解决)!2:制程中对重点工序:脱外被,脱芯线,焊接,成型。

四步重点管控。

其结论A:脱外被如果脱皮机夹线夹太紧,内层芯线压变形。

高频特性线材的阻抗会变化。

B:脱外被脱皮太长会对线材本身绞距和绞线直径有影响,其中最大的是阻抗和电容值(绞线直径影响电容值)。

如果电容值影响了那么高频特性SKEW会直接受到影响。

C:脱芯线,常见的原因1)脱伤芯线,刮伤铜丝,脱断铜丝,这会直接影响我们线材的传输速度,因为信号是在芯线的表面传输。

因此速度的传输和我们线材的载面积成正比。

哎,不要讲远了。

继续。

2)脱芯线太长,芯线太长直接影响最大的就是SKEW(对内延迟差和对间延迟差)1MM约等于2PS!D:焊接---技术工站,具体问题我不讲了,因为这个论谈里有很多对这方面的讲解,不了解的朋友可以去SHOU一下看看。

我只说这个对高频影响部份为:连接器的阻抗,匹配阻抗,SKEW,衰减,串音。

E:成型,成型很多朋友特别是新人,对成型了解到的只是用什么料成型内模,用什么料成型外模,但知其然不知其所以然。

而成型这里比如常用的:PE和PVC 为什么会选择先用PE料成型内模,而后用PVC成型外模。

其主要的原因在于,两者之间的介电系数,介电系数会直接影响我们成型后的:连接器的阻抗和匹配阻抗,如果两项阻抗影响过大,那么还会导致衰减不过。

阻抗匹配基本概念以及高频阻抗匹配

英文名称:impedance matching基本概念信号传输过程中负载阻抗和信源内阻抗之间的特定配合关系。

一件器材的输出阻抗和所连接的负载阻抗之间所应满足的某种关系,以免接上负载后对器材本身的工作状态产生明显的影响。

对电子设备互连来说,例如信号源连放大器,前级连后级,只要后一级的输入阻抗大于前一级的输出阻抗5-10倍以上,就可认为阻抗匹配良好;对于放大器连接音箱来说,电子管机应选用及其输出端标称阻抗相等或接近的音箱,而晶体管放大器则无此限制,可以接任何阻抗的音箱。

匹配条件①负载阻抗等于信源内阻抗,即它们的模及辐角分别相等,这时在负载阻抗上可以得到无失真的电压传输。

②负载阻抗等于信源内阻抗的共轭值,即它们的模相等而辐角之和为零。

这时在负载阻抗上可以得到最大功率。

这种匹配条件称为共轭匹配。

如果信源内阻抗和负载阻抗均为纯阻性,则两种匹配条件是等同的。

阻抗匹配是指负载阻抗及激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗及内阻必须满足共扼关系,即电阻成份相等,电抗成份绝对值相等而符号相反。

这种匹配条件称为共扼匹配。

阻抗匹配(Impedance matching)是微波电子学里的一部分,主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升能源效益。

史密夫图表上。

电容或电感及负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。

如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。

重覆以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。

共轭匹配在信号源给定的情况下,输出功率取决于负载电阻及信号源内阻之比K,当两者相等,即K=1时,输出功率最大。

USB 3.0 线缆和连接器的阻抗和插损测试

USB 3.0线缆和连接器的阻抗和插损测试美国力科公司下一代串行数据标准采用的高速率已经进入到微波领域。

比如,即将到来的SuperSpeedUSB(USB 3.0)通过双绞线对线缆传输速的率就达到了5Gb/s。

通过连接器和线缆传输如此高的速率必须考虑通道的不连续性引起的失真。

为了将失真程度保持在一个可控的水平,标准规定了线缆和连接器对的阻抗和回波损耗。

最新的测量使用S 参数S11表征而且必须归一化到线缆的90欧姆差分阻抗。

当测量USB 3.0通道的S 参数时,可选的仪器是时域反射计或TDR 。

TDR 系统通常往待测器件注入一个阶跃电压信号然后测量是时间函数的反射电压。

差分测量通过产生极性相反可相对定时的阶跃电压对实现。

这篇文章中谈到的都是差分信号。

反射电压与发射器和待测器件之间的阻抗失配成比例,关系如下式:()())()()()()(00t Z Z t Z Z t t V t V L L i r +−==ρ(1)Z 0是源阻抗,Z L (t)是待测器件的阻抗,ρ(t )是反射系数,V r (t)/V i (t)是入射和发射电压的比率。

式(1)假设到待测器件的源,线缆和连接器都是匹配的,但事实上这种情况很少见。

为了补偿线缆和连接器的不理想,参考平面校正(基线校正)通常进行开路,短路,负载校准。

调整式(1)可以得到待测器件的阻抗和时间(或距离)的函数,所以可以使用校准过的TDR 做阻抗测量。

图1展示了USB 3.0带有连接器线缆的的阻抗曲线。

曲线表明了随着TDR 阶跃信号在线缆中的行进阻抗变化是时间的函数。

注意轨迹两头的阻抗变化,那是由于连接器引起的,当使用上升时间100ps (阶跃信号)测试时连接器的阻抗规定是90+/-7欧。

TDR 的上升时间非常重要,因为阻抗变化和TDR 阶跃信号的上升时间成反比,而规范规定的USB 3.0信号的上升时间是100ps ,测量中匹配这个上升时间将给出信号“看到的”阻抗。

usb标准详解

第一章技术背景本章对通用串行总线USB的技术背景作一简单描述,包括设计目标,总线特征和现有技术.1.1USB的目标:结构6.1USB物理结构包括与HUB下游接口连接部分和与另一个HUB或设备上游的连接部分.USB有三种速度:高速(480Mb/s),全速(12Mb/s)(这两种线要求使用遮蔽,其中包括一对电源线和一对绞合信号线),低速推荐但是不要求信号线对绞.端子应设计为热插拔型,USB上的标记使你靠触觉就可以非常容易的找到正确的方位.6.2端子协议为了减少终端使用者的问题,USB采用了端子协议,A端子和B 端子的物理结构不同,A端子直接和主机或HUB的下游接口相连接所有的USB设备都要有A 端子以下是描述插头和插座是如何匹配的1.A插座与A插头相匹配,A插座的功能是主机或HUB 的输出2.A插头与A 插座相匹配,A插头是指向主机系统3.B插座与B插头相匹配,B插座的功能是主机或HUB 的输入4.B插头与B插座相匹配,B插头总是指向HUB或设备6.3电缆USB包括四根线:两根电源线,两根信号线.高速/全速电缆信号线对绞,完全遮蔽,高速/全速电缆应标识出适当的使用方法(见6.6.2),高速/全速电缆可以用于低速,全速和高速的传输设备.当高速/全速电缆应用于低速设备时,电缆一定要满足低速要求.低速电缆建议但是不要求信号线对绞.6.4电缆组合此项规格说明三种USB组合:标准可分离电缆,受制电缆和低速受制电缆.标准可分离电缆是一种一端是A 插头另一端是B插头的高速/全速电缆;受制电缆是一端是A插头,另一端与高速/全速外围设备相连;低速受制电缆是一端连接A插头,另一端与低速外围设备相连接.其它的组合方式是不允许的.电缆组合的颜色由提供者规定,推荐的颜色为白,灰,或黑6.4.1标准可分离电缆组合高速和全速设备可使用B端子,允许设备有一个标准的USB电缆,这就免除了制造设备固定电缆的必要,同时也使换线问题变得容易解决.表6-2列举了标准可分离电缆的组合必须满足以下电气要求(1)一端A插头一端B插头(2)电缆必须规定用于高速/全速(3)电缆阻抗必须满足高速/全速驱动器,驱动器规定了阻抗,参考7.1.1(4)允许的最大电缆长度和信号传播延时.参考7.1.14和7.1.17(5)信号线之间的传播延时偏差应为最小.参考7.1.3(6)电源线中负极是上下游共同的负极,电缆的最大长度受压降的限制.(参考7.2.2)最小可接受的线径由连接设备决定.(7)电源线中的正极为连接设备提供电源6.4.2高速受制电缆组合电缆的一端与外围设备相连就被认为是受制电缆.高速/全速电缆可应用于高速,全速,低速设备.当在低速设备使用一个高速/全速硬联机电缆时,电缆必须满足低速要求高速/全速受制电缆组合应满足以下电气特性:(1)一端有射出后的A端,另一端由供应者规定,如果供应者规定为热插拔,那么应是B端子(2)电缆必须为额定的高速和全速.(3)电缆的阻抗必须与高速和全速驱动器相匹配,驱动器对阻抗有特殊的要求.参考7.1.3(4)由信号的衰减和传播延时决定电缆的最大长度,参考7.1.14和7.1.17(5)信号线间的延时偏差应为最小.参考7.1.3(6)电源线中的负极为上下游接口的共同负极.线的长度受通过地线压降的限制,参考7.2.2,线径由最差电流消耗计算得出.(7)电源线中的正极为与其相连接的设备提供能量,最小线径为提供者规定6.4.3低速受制电缆组合当电缆与外围设备之间采用硬线连接时就被认为是受制组合.低速电缆只可用于低速设备.低速受制电缆应满足以下电气要求:(1)电缆的一端连接射出后的A插头,由供应者规定另一端.若供应者特意设计为热插拔的话,它就应为满足相同参数的USB B 端子.(2)低速驱动器对电容值作出特殊化的要求,这个值包括D+,D-之间的所有介质的电容值而不仅仅是电缆的电容值.电缆的选择必须确保完整的电容值在规定的最大值和最小值之间,若应用的c值不满足最低要求,应增加额外的电容值.参考7.1.1.2(3)低速电缆的最大长度由信号的上升和下降时间决定,这就使低速线明显的比高速线短.参考7.1.1.2(4)信号线之间的传播延时偏差必须最小.参考7.1.3(5)电源线的负极提供给上游和下游一个共同的参数,电缆的最大长度由通过负极的压降决定,参考7.2.2,最小线径由最差电流消耗决定(6)电源线的正极给与其连接的设备提供电源,其最小的线径由供应者规定6.4.4优化USB以便使用,我们期望的是即插即用.依据说明,使USB无效的唯一方法就是切断其电源,或使其缺乏带宽,和过大的布局,这些条件应在软件系统中充分说明.被禁止的电缆组合可以工作在一些情况下,但是不能保证在所有的情况下它都可以使用扩展的电缆组合一种电缆组合由A插头和A插座或B插头和B插座组合,这就允许许多节的线连接在一起,就有可能超过允许的最大电缆长度.违反布局规则的电缆组合一种电缆组合由两个A插头或两个B插座,这就允许两个设备的下游接口直接连接.提示:如果是应用一个USB设备连接2个总线的话是不被禁止的.应用于低速设备的标准可分离电缆标准可分离的电缆被禁止使用在低速设备上,一个标准可分离电缆必须是高速/全速的,既然它额定是高速的,那么应用一个高速电缆将会超过低速的电缆载荷. 6.5.3.1插座的射出热塑性绝缘材料UL-94-V0规定的最小值,30%以上的聚丁烯对苯二盐酸或聚乙烯对苯二盐酸典型颜色: 黑,灰,透明可燃性特性:UL-94-V0规定燃烧延缓外壳必须满足UL,CSA,VDE6.5.3.2插座外壳原料底层材料:0.30+0.05mm磷铜,镍银合金,或其它高强度的铜合金电镀:1.底层:可选择,最小1微米镍,另外,制造者可以在镍之下用铜作底2.外部:最小2.5微米锡6.5.3.3插座连接材料底层材料:0.30+0.05mm最小半硬磷青铜或其它高强度的铜合金电镀:接触点应被电镀A:1.底层:最小1.25微米的镍,也可选择铜合金2. 匹配范围:最小0.05微米的镀金层覆盖在0.70微米的钯上3尾部焊接:最少3.8微米的焊锡覆盖在底座上B1.底层: 最小1.25微米的镍,也可选择铜合金2. 匹配范围:最小0.05微米的镀金层覆盖在0.75微米的钯上3. 尾部焊接:最少3.8微米的焊锡覆盖在底座上C. 1.底层:最小1.25微米的镍,也可选择铜合金2. 匹配范围:最小0.75微米的镀金层覆盖在钯上3. 尾部焊接:最少3.8微米的焊锡覆盖在底座上6.5.4A插头和B插头A插头和B插头的电气和机械特性在表6-9和6-10中有说明6.5.4.1用于插头射出的热塑性材料UL-94-V0规定最小30%聚丁烯对苯二盐酸或聚乙烯对苯二盐酸典型颜色: 黑,灰,透明可燃性特性:UL-94-V0规定外被燃烧延迟必须满足或超过UL,CSA,和VDE的要求氧气指数: 21%,ASTM D28636.5.4.2插头外壳材料底层材料: 0.30±0.05mm磷青铜,镍银合金或其它合适材料.外部:最小2.5微米有光泽的锡6.5.4.3插头连接材料底层材料:0.30±0.05mm半硬磷青铜电镀:接点有选择的电镀A:1.底层:最少1.25微米的镍,也可选择镀铜材料2.匹配范围:最少0.05微米的镀金层覆盖在0.70微米的钯上3.尾部焊接:至少3.8微米的有光泽的锡覆盖在底层上B:1.底层:至少1.25微米的镍,也可选择镀铜材料2.匹配范围:最少0.05微米的镀金层覆盖在0.75微米的钯上3.尾部焊接:至少3.8微米的有光泽的锡覆盖在底层上C:1.底层:至少1.25微米的镍,也可选择镀铜材料2. 匹配范围:最少0.75微米的镀金层3. 尾部焊接:至少3.8微米的有光泽的锡覆盖在底层上6.6电缆机械结构和材质要求高速/全速和低速的资料线和屏蔽是不同的,低速电缆推荐但是不要求资料线对绞.低速电缆推荐但是不要求屏蔽部分带编织.6.6.1说明高速电缆由一对不绞合电源线(28-20AWG)和一对绞合信号线(28AWG)有铝箔麦拉屏蔽(麦拉在内).28AWG的绞合地线.遮蔽率大于65%的镀锡铜外部编织,外被材料是PVC低速电缆由一对不绞合电源线和一对信号线(28AWG,建议对绞)组成,有铝箔麦拉屏蔽(麦拉在内),28AWG的绞合地线,推荐使用遮蔽率大于65%的镀锡铜编织,外被材料PVC.6.6.2结构应用于电缆结构中的原材料必须能够使装配好的线达到或超过当前国内国际安全机构的要求,如UL,CSA,BSA,NEC电源线和资料线的类别表6-2 电源对不绞合电源对A:线径,至少28AWG或对应表6-2中规格B:绝缘部分:半硬式的PVC1.绝缘额定的绝缘厚度0.25mm2.电源线正极: 红色3.负极: 黑色信号对B: 绝缘部分:高密度聚氯乙稀也可用发泡聚乙烯或发泡聚丙烯替换1.额定绝缘厚度0.31mm2.资料线正极: 绿色3.资料线负极: 白色C: 额定绞距(低速不要求)绞距应在60mm到80mm之间.铝箔麦拉A: 底层材料:聚乙稀对苯二盐酸B: 金属部分:真空夹层铝箔C: 组合:1.铝箔的金属部分应与地线充分接触2.铝箔的重叠率应接近25%.地线编织:A: 覆盖面积:至少65%B:组合:外部编织应把铝箔麦拉包裹在内并与地线直接接触.PVC外被:A:结构:PVC外被应包括屏蔽,电源线,信号线在内的所有东西,并与镀锡铜编织直接接触.B:额定厚度:0.64mm标识:电缆应用与线底色反差大的永久性墨水明显的印上标识.A:高速/全速电缆的最少印字信息应包括:USB SHIELDED <GAUGE/2C+GAUGE/2C>UL CM 75℃-UL IDB:低速电缆应标识的信息:没有特殊要求额定电缆的完整外径这是一个标准用于制造者作为导体和绝缘材料的说明6.6.3电气特性所有电气特性必须在20℃条件下被检测额定电压:最大30V rms导体电阻:导体电阻的测量应根据ASTM-D-4566.第13节表6-6导体电阻不平衡:任何线对之间的导体电阻不平衡不超过5%,测试依照ASTM-D-4566第15节.插头外壳任意两点电阻不大于0.6ohms6.6.4电缆对环境的要求温度范围:A:使用温度范围0℃---+50℃B:存储温度:-20℃---+60℃C:标准温度:20℃可燃性:应用于产品中的所有塑料原料都应该满足或超过NEC800(商业用通信电缆)6.6.5产品应满足UL444,CLASS2,商业用电缆要求6.7电气,机械,和环境标准表6-7列举了USB电缆,组合,端子的最低标准364-20B端子,插座和同轴连接的耐压测试2.1.2设备除非有特殊要求,否则我们采用误差5%的伏特表去测量电压,伏特表应连接在第一,第二或第三级是预先决定的,电压的实际值应在允许的范围内.2.1.3一个带有显示表盘的箱子可用于测量气压,除非有特殊要求,否则我们应用误差为5%的仪器用于监视气压的变化.2.1.4错误提示当出现无法用肉眼发现的漏电现象时,我们应采用适当的方法去表示.电压测试,电流泄漏测试,用与其相对应的灯表示,或者用过载保护装置也可以实现这个目的.2.1.5泄漏提示当有泄漏要求说明时,应当有合适的方法去测量泄漏电流,误差±5%,除了特殊要求,否则泄漏电流应小于0.5mA.3.样品说明3.1测试样品应包括一个插头,一个插座,一个相匹配的插头和插座3.2准备当有特殊的条件要求如特殊的测试设备,接地,隔离,浸入水中,这些应在参数文件中说明.4测试过程4.1要点4.1.1方法A应测试空间距离最近的两个接点,端子外壳与导通接触点之间的电压4.1.2方法B在参考文件中描述的相邻接点之间的电压也应测试.4.1.3方法C应测量每个接点之间的电压4.1.4方法D同轴电缆导体的内部外部电压也要测试4.2气压既然气压会对端子或终端隔着空气的同轴接点的抗压性产生很大的影响,那么这个压力应在测试要求中说明.允许通过减小气压而降低其抗压能力,在每个应用于海拔位于海平面的情况会对其抗压特性作出说明.若需要,基于端子或同轴接点的应用要求,为了使气压控制在我们期望的范围内,应该对最小抗压性作出要求. 4.2.1减少气压依照规定端子或同轴接点应固定在测试箱内并且把气压减少到与表1中一致让它们在规定的压力下保持足够长的时间,让残留在箱中的空气散去,端子或同轴接点应遵守测试规定.表1,测试条件注:海拔只是作为参考4.3测试电压测试样品应遵守规定的测试电压4.4应用变化率测试电压应从0℃升到与规定的温度一致,若没有特殊的要求,电压应以500V/s的速率变化,根据制造商的选择,电压测试可以在厂内某一时刻进行.4.5应用持续时间若没有特殊要求,测试电压应维护60s,厂内测试可以减少到5s.在一个完整的测试过程中,测试电压应逐步的减小,避免起伏过大.4.6样品的测量和测试在耐压测试的过程中,如有破裂和泄漏的情况出现,那么这些情况的显示应该被监控.5细节说明以下细节将会在参考文件中说明5.1特殊高电压,若应用参考2.1.15.2最小额定千伏安,若应用参看2.1.15.3电流浪涌,设备限制,参看2.1.15.4伏特表精确度,至少95%,参看2.1.25.5泄漏电流说明2.1.55.6确认测试样品,匹配与否?参看3.15.7特别准备或条件,参看3.25.8样品与测试电压的连接3.25.9测试电压作用点,参看4.15.10气压,参看4.25.10.1处于海平面的绝缘抗压要求参看4.25.10.2减小压强后的绝缘抗压,参看4.25.10.3在减压期间和减压后的测试,参看4.2.15.10.4在测试箱中的安装方法,参看4.35.11测试电压数值,参看4.35.12电压特性(交流或直流)5.13厂内品质保障测试所要求的电压测试和持续时间,参看4.55.14品质保障所要求的电压测试持续时间除了60s之外,还有什么其他的要求参看4.55.15样品的测量和测试细节要求,参看4.65.16需测试样品数量。

USB 2.0测试规范

USB 2.0 测试规范及影响因素一栏表

No. 测试项目 测试标准 Frequency(MH dB/Cable(Max Z) imum) 0.512 0.13 衰减 Signal 1 Pair attenuat ion 0.772 1 4 8 12 24 48 96 200 400 差模阻抗 Differen 2 tial Impedanc e 同模阻抗 Common 3 Impedanc e 延迟 Propagat 4 ion Delay 延迟差 Propagat 5 ion Delay Skew 0.15 0.2 0.39 0.57 0.76 0.95 1.35 1.9 3.2 5.8 测试仪器 影响因素 1. 信号线导体截面积与长度不 匹配 2. 加工信号芯线时伤到芯线导 NA(网络分 体 析仪)或依 EIA364-101 3.信号芯线导体材质 以 Open/Short 4.信号线导体的光泽度及纯度 量测 5. 信号线导体的绝缘材质(介 质常数) 6. 信号线的对绞绞距及包带异 常 1. 信号芯线ID; 2. 信号线的同心度及真圆度; 3. 信号线绝缘材质(介质常 TDR(时域反 数); 射仪) 4. 焊接时锡点饱和度,有无锡 尖,芯线绝缘皮是否后缩 5. 线材与连接器阻抗匹配 备注图 Eye Mask模块为中心),眼 Eye 图接触到Eye Mask则表示信 Diagram 号质量不好,离Eye Mask越 远,则信号质量越好。

1、电波暗室 2、接收机 3、接收天线 电磁兼容 依客户标准(如0dB,-2dB,- 4、频谱仪 7 3dB,-4dB,-6dB等) EMC 6、转台、升 降台 7、转台、升 降台控制器

USB匹配

USB匹配USB操纵器的内部结构如以下图所示:由上图可知,USB的高速模式和低速/全速利用不同的驱动器,USB利用差分特性阻抗为90ohm 的线,USB全速模式下驱动器的输出阻抗和输入阻抗一样不为45ohm,信号会发生反射造成信号质量下降,需要对电路进行匹配来减小信号的反射;经常使用的匹配方式有:串联匹配、并联匹配、戴维南匹配等。

USB全速驱动器的输出阻抗一样比较小,假设输出阻抗<特性阻抗那么能够通过串联电阻来实现匹配,E330利用iMX258处置器,其全速Host的输出阻抗Rs厂家估量为10ohm,而USB线的差分特性阻抗为90ohm,因此要实现驱动器和USB线的阻抗匹配必需在USB D+和D-上串联电阻,串联电阻的要求为Rs+R串=USB线特性阻抗;以下别离为串联0ohm、3ohm、22ohm、33ohm、51ohm和68ohm眼图,RT mean和FT mean为上升和下降时刻的平均值。

R串 = 3ohm,RT mean = ;FT mean = ;R串 = 22ohm,RT mean = ;FT mean = ;R串 = 33ohm,RT mean = ;FT mean = ;R串 = 51ohm,RT mean = ;FT mean = ;R串 = 68ohm,RT mean = ;FT mean = ;当阻抗>特性阻抗时那么要通过并联电阻来实现匹配,而在高速模式下,信号是通过电流源驱动的,以上匹配电阻的存在都将降低信号质量,下面别离举串联10ohm、22ohm和33ohm为例;没有串联电阻时的眼图如下:一、R串 = 10ohmU device = *45//(10+45) = ,U host = 45/(45+10)* = ;2、R串 = 22ohmU device = *45//(22+45) = ,U host = 45/(45+22)* = ;3、R串 = 33ohmU device = *45//(33+45) = ,U host = 45/(45+33)* = ;网友:二郎神君转载请注明出处!更多USB、SD卡等出色内容请到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

USB低速设备上电连接

(Low-speed Device Cable and Resistor Connections)

2.2.

USB全速/低速识别相当简单,但USB2.0,USB1.x就一对数据线,不能像全速/低速那样仅依靠数据线上拉电阻位置就能识别USB第三种速度:高速。因此对于高速设备的识别就显得稍微复杂些。

至此,高速设备与USB2.0 hub握手完毕,进行后续的480Mbps高速信号通信。

最后附上几幅实际USB高速识别的示波器抓图,图中蓝色信号是D+,黄色信号是D-。

1.数据线D+在T点之前挂上1.5K电阻,在T点被host拉成EP0状态。在近2ms后,设备发送第一个Chirp K,向host通知说:我是一个高速设备,如果可能,请用高速方式与我通信。其幅度是800mV(17.78mA * (45Ohm || 1.5kOhm) = 800mV,见上文解释)。在这里,Chirp K的持续时间是2.13ms(a,b两点之间)。

1.2.

USB信号使用分别标记为D+和D-的双绞线传输,它们各自使用半双工的差分信号并协同工作,以抵消长导线的电磁干扰。

触点

功能(主机)

功能(设备)

1

VBUS (4.75-5.25 V)

VBUS (4.4-5.25 V)

2

D-

D-

3

D+

D+

4

接地

接地

2.

我们知道USB2.0向下兼容USB1.x,即高速2.0的hub能支持所有的速度类型的设备,而USB1.x的hub不能支持高速设备(High Speed Device)。因此,如果高速设备挂到USB1.x的hub上,那该设备只能工作在全速模式下。不管是hub还是设备(device),对于速度的区分是非常重要的,否则,后续的通信根本无法进行。

2.1.

根据规范,全速(Full Speed)和低速(Low Speed)很好区分,因为在设备端有一个1.5k的上拉电阻,当设备插入hub或上电(固定线缆的USB设备)时,有上拉电阻的那根数据线就会被拉高,hub根据D+/D-上的电平判断所挂载的是全速设备还是低速设备。如下两图:

USB全速设备上电连接

下图展示了一个高速设备连到USB2.0 hub上的情形:

hub检测到有设备插入/上电时,向主机通报,主机发送Set_Port_Feature请求让hub复位新插入的设备。设备复位操作是hub通过驱动数据线到复位状态SE0(Single-ended 0,即D+和D-全为低电平),并持续至少10ms。

高速设备看到复位信号后,通过内部的电流源向D-线持续灌大小为17.78mA电流。此时高速设备的1.5k上拉电阻还未撤销,在hub端,全速驱动器形成一个阻抗为45欧姆(Ohm)的终端电阻,所以在hub端看到一个约800mV的电压(45欧姆*17.78mA),这就是Chirp K信号。Chirp K信号的持续时间是1ms~7ms。

在hub端,虽然下达了复位信号,并一直驱动着SE0,但USB2.0的高速接收器一直在检测Chirp K信号,如果没有Chirp K信号看到,就继续复位操作,直到复位结束,之后就在全速模式下操作。如果只是一个全速的hub,不支持高速操作,那么该hub不理会设备发送的Chirp K信号,之后设备也不会切换到高速模式。

高速设备初始是以一个全速设备的身份出现的,即和全速设备一样,D+线上有一个1.5k的上拉电阻。USB2.0的hub把它当作一个全速设备之后,hub和设备通过一系列握手信号确认双方的身份。在这里对速度的检测是双向的,比如高速的hub需要检测所挂上来的设备是高速、全速还是低速,高速的设备需要检测所连上的hub是USB2.0的还是1.x的,如果是前者,就进行一系列动作切到高速模式工作,如果是后者,就以全速模式工作。

再回到设备端来。设备检测到6个hub发出的Chirp信号后(3对KJ序列),它必须在500us内切换到高速模式。切换动作有:

1.断开1.5k的上拉电阻。

2.连接D+/D-上的高速终端电阻(high-speed termination),实际上就是全速/低速差分驱动器。

3.进入默认的高速状态。

执行1,2两步后,USB信号线上看到的现象就发生变化了:hub发送出来的Chirp KJ序列幅值降到了原先的一半,400mV。这是因为设备端挂载新的终端电阻后,配上原先hub端的终端电阻,并联后的阻抗是22.5欧姆。400mV就是由17.78mA*22.5Ohm得来。以后高速操作的信号幅值就是400mV而不像全速/低速那样的3V。

2.这幅图显示了host发出的chirp KJ信号的幅度,头几个KJ是800mv(a,b之),随后的是400mV。图中可以看到设备在收到第三个chirp J(蓝色短条)后马上把1.5k电阻取消,导致chirp J的幅值下降到400mV。(17.78mA * (45Ohm || 45Ohm) = 17.78mA * 22.5Ohm = 400mV)

低速(Low-Speed)

5V/500mA

USB1.1

12Mbps(1.5MB/s)

全速(Full-Speed)

5V/500mA

USB2.0

480Mbps(60MB/s)

高速(High-Speed)

5V/500mA

USB3.0

5Gbps(500MB/s)

超高速(Super-Speed)

5V/900mA

设备发送的Chirp K信号结束后100us内,hub必须开始回复一连串的KJKJKJ....序列,向设备表明这是一个USB2.0的hub。这里的KJ序列是连续的,中间不能间断,而且每个K或J的持续时间在40us~60us之间。KJ序列停止后的100~500us内结束复位操作。hub发送Chirp KJ序列的方式和设备一样,通过电流源向差分数据线交替灌17.78mA的电流实现。

USB识别及阻抗匹配

2016/11/22

修改记录:

修订号

作者

日期

简要说明

1.

USB是英文universal serial bus通用串行总线的缩写,是一个外部总线标准,用于规范电脑和外部设备的链接和通信。

1.1.

USB版本

理论最大传输速率

速率称号

最大输出电流

USB1.0

1.5Mbps(192KB/s)