瑞萨电子M16C族系列单片机

HEW自动生成文件介绍

M16C族单片机编程入门作者:快乐水牛M16C族单片机为原三菱电机生产的16位CISC微控制器。

主要特点为:低电压,低功耗,抗干扰性强具备大容量FLASH ROM, SRAM丰富的外设,如定时器,AD,DA,CAN控制器等所有这些特性,使M16C广泛应用汽车,电动车,工业设备及家电产品上。

下面我们讲讲如何在M16C平台下编程。

1. 使用HEW新建一个工程。

打开HEW,选择Create a new project workspace,点OK。

选择CPU family,这里我们选择M16C选项。

工具链Tool chain我们默认选择Renesas M16C Standard。

好了,接下来我们要输入一个工程名字,在workspace name里输入m16c_test。

接下来,注意,也是最重要的一步,在左边的project types下面,我们选择C source startup Application这个选项,该选项的含义是你将建立一个C语言开始的工程。

当然,如果选择第一个Application,则为汇编语言开始的工程。

考虑到大多数朋友对M16C的汇编不是很熟悉,我们这里以C语言工程为参考。

点确定后,继续选择工具链版本5.43.00,CPU Series我选择为M16C/60, CPU Group我选择为6N4,然后点next,继续点next使用默认选项,最后选择targets为M16C E8a SYSTEM,这是是你的CPU要用到的仿真器,我们一般使用瑞萨产的小型ON Chip debugger仿真器E8a. 点next,最后点Finish。

OK,我们的一个C语言工程已经建好了。

2. 工程源文件分析我们发现我们建的m16c_test工程里面有一些源代码文件。

下面我们对这些文件进行分析。

(注意:建立工程时,选择不同的选项可能会产生不同的源代码文件,不过这不影响我们的使用)m16c_test.c源代码:/*****************************/void main(void){}该文件是main()函数。

瑞萨_mcu型号指南

QzROM

PWM

16 8 DA

AD (LVD)

(POR)

/RTC PLL I/O

QzROM

群 型号

(4bits/W) RAM

(10bits/W) QzROM

存储器

)

(

最

/

高 工 最作 大频 范率 围工 作 电 压

最

小

指

令

执

端

行

口

时

间

时钟

电压 检测

SSOP-24

遥控器

7544

M37544G2ASP/GP M37544G2A-XXXSP/GP

8K

256

8MHz/ 1.8~5.5V

0.25us @8MHz

25 - - ○ ○ - - 10位×6

-

2 1 - - - ○ - - ○ ○ ○ - - 8 -20~85

SDIP-32 LQFP-32

OA设备、FA设备、家电、民用设备

M38588GCSP M38588GC-XXXSP

48K

1.5K

12.5MHz/ 2.4~5.5V

0.5us @8MHz

34 - ○ - - - - 8位×9

-

4 2 - - ○ ○ - - ○ ○ ○ - - 8 -20~85

SDIP-42 SSOP-42

OA设备、FA设备、家电、民用设备

M38D24G4FP/HP M38D24G4-XXXFP/HP

M34571G4FP M34571G4-XXXFP

M34571G6FP M34571G6-XXXFP

M34571GDFP M34571GD-XXXFP

瑞萨E8a使用手册(中文)

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

m16

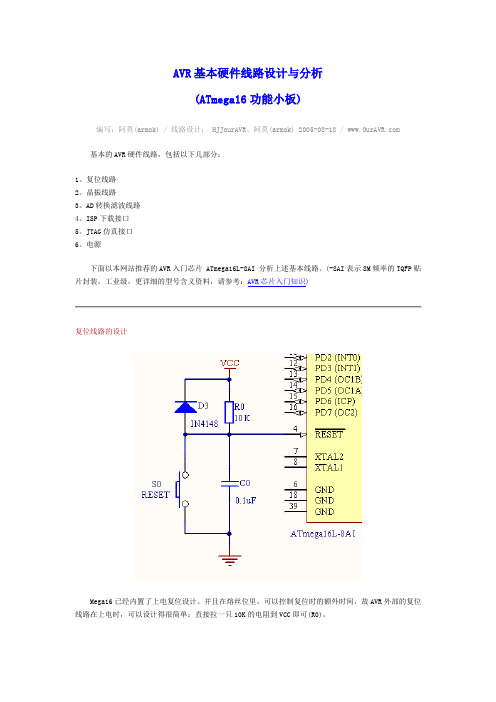

AVR基本硬件线路设计与分析(ATmega16功能小板)编写:阿莫(armok) / 线路设计: HJJourAVR、阿莫(armok) 2005-08-18 / 基本的AVR硬件线路,包括以下几部分:1。

复位线路2。

晶振线路3。

AD转换滤波线路4。

ISP下载接口5。

JTAG仿真接口6。

电源下面以本网站推荐的AVR入门芯片 ATmega16L-8AI 分析上述基本线路。

(-8AI表示8M频率的TQFP贴片封装,工业级,更详细的型号含义资料,请参考:AVR芯片入门知识)复位线路的设计Mega16已经内置了上电复位设计。

并且在熔丝位里,可以控制复位时的额外时间,故AVR外部的复位线路在上电时,可以设计得很简单:直接拉一只10K的电阻到VCC即可(R0)。

为了可靠,再加上一只0.1uF的电容(C0)以消除干扰、杂波。

D3(1N4148)的作用有两个:作用一是将复位输入的最高电压钳在Vcc+0.5V 左右,另一作用是系统断电时,将R0(10K)电阻短路,让C0快速放电,让下一次来电时,能产生有效的复位。

当AVR在工作时,按下S0开关时,复位脚变成低电平,触发AVR芯片复位。

重要说明:实际应用时,如果你不需要复位按钮,复位脚可以不接任何的零件,AVR芯片也能稳定工作。

即这部分不需要任何的外围零件。

晶振电路的设计Mega16已经内置RC振荡线路,可以产生1M、2M、4M、8M的振荡频率。

不过,内置的毕竟是RC振荡,在一些要求较高的场合,比如要与RS232通信需要比较精确的波特率时,建议使用外部的晶振线路。

早期的90S系列,晶振两端均需要接22pF左右的电容。

Mega系列实际使用时,这两只小电容不接也能正常工作。

不过为了线路的规范化,我们仍建议接上。

重要说明:实际应用时,如果你不需要太高精度的频率,可以使用内部RC振荡。

即这部分不需要任何的外围零件。

AD转换滤波线路的设计为减小AD转换的电源干扰,Mega16芯片有独立的AD电源供电。

R8C-18资料

REJ03B0124-0140Rev.1.40Apr 14, 2006R8C/18 Group, R8C/19 GroupSINGLE-CHIP 16-BIT CMOS MCU1.OverviewThese MCUs are fabricated using a high-performance silicon gate CMOS process, embedding the R8C/Tiny Series CPU core, and is packaged in a 20-pin molded-plastic LSSOP, SDIP or a 28-pin plastic molded-HWQFN. It implements sophisticated instructions for a high level of instruction efficiency. With 1Mbyte of address space, they are capable of executing instructions at high speed.Furthermore, the R8C/19 Group has on-chip data flash ROM (1 KB × 2 blocks).The difference between the R8C/18 Group and R8C/19 Group is only the presence or absence of data flash ROM. Their peripheral functions are the same.1.1ApplicationsElectric household appliances, office equipment, housing equipment (sensors, security systems), general industrial equipment, audio equipment, etc.1.2Performance OverviewTable 1.1 outlines the Functions and Specifications for R8C/18 Group and Table 1.2 outlines the Functions and Specifications for R8C/19 Group.Table 1.1Functions and Specifications for R8C/18 GroupItem SpecificationCPU Number of fundamentalinstructions89 instructionsMinimum instruction execution time 50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V) 100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V)Operation mode Single-chipAddress space 1 MbyteMemory capacity Refer to Table 1.3 Product Information for R8C/18GroupPeripheral Functions Ports I/O ports: 13 pins (including LED drive port)Input port: 3 pinsLED drive ports I/O ports: 4 pinsTimers Timer X: 8 bits × 1 channel, timer Z: 8 bits × 1 channel(Each timer equipped with 8-bit prescaler)Timer C: 16 bits × 1 channel(Input capture and output compare circuits)Serial interfaces 1 channelClock synchronous serial I/O, UART1 channelUARTComparator 1-bit comparator: 1 circuit, 4 channelsWatchdog timer15 bits × 1 channel (with prescaler)Reset start selectable, count source protection mode Interrupts Internal: 10 sources, External: 4 sources, Software: 4sources,Priority levels: 7 levelsClock generation circuits 2 circuits•Main clock oscillation circuit (with on-chip feedbackresistor)•On-chip oscillator (high speed, low speed)High-speed on-chip oscillator has frequencyadjustment functionOscillation stop detectionfunctionMain clock oscillation stop detection functionVoltage detection circuit On-chipPower-on reset circuit On-chipElectric Characteristics Supply voltage VCC = 3.0 to 5.5 V (f(XIN) = 20 MHz)VCC = 2.7 to 5.5 V (f(XIN) = 10 MHz)Current consumption Typ. 9 mA (VCC = 5.0 V, f(XIN) = 20 MHz, comparator stopped)Typ. 5 mA (VCC = 3.0V, f(XIN) = 10 MHz, comparator stopped)Typ. 35 µA (VCC = 3.0 V, wait mode, peripheral clock off)Typ. 0.7 µA (VCC = 3.0 V, stop mode)Flash Memory Programming and erasure voltage VCC = 2.7 to 5.5 VProgramming and erasureendurance100 timesOperating Ambient Temperature-20 to 85°C-40 to 85°C (D version) Package20-pin molded-plastic LSSOP20-pin molded-plastic SDIP28-pin molded-plastic HWQFNTable 1.2Functions and Specifications for R8C/19 GroupItem Specification CPU Number of fundamentalinstructions89 instructionsMinimum instruction execution time 50 ns (f(XIN) = 20 MHz, VCC = 3.0 to 5.5 V) 100 ns (f(XIN) = 10 MHz, VCC = 2.7 to 5.5 V)Operation mode Single-chipAddress space 1 MbyteMemory capacity Refer to Table 1.4 Product Information for R8C/19GroupPeripheral Functions Ports I/O ports: 13 pins (including LED drive port)Input port: 3 pinsLED drive ports I/O ports: 4 pinsTimers Timer X: 8 bits × 1 channel, timer Z: 8 bits × 1 channel(Each timer equipped with 8-bit prescaler)Timer C: 16 bits × 1 channel(Input capture and output compare circuits)Serial interfaces 1 channelClock synchronous serial I/O, UART1 channelUARTComparator 1-bit comparator: 1 circuit, 4 channelsWatchdog timer15 bits × 1 channel (with prescaler)Reset start selectable, count source protection mode Interrupts Internal: 10 sources, External: 4 sources, Software: 4sources,Priority levels: 7 levelsClock generation circuits 2 circuits•Main clock generation circuit (with on-chip feedbackresistor)•On-chip oscillator (high speed, low speed)High-speed on-chip oscillator has frequencyadjustment functionOscillation stop detectionfunctionMain clock oscillation stop detection functionVoltage detection circuit On-chipPower-on reset circuit On-chipElectric Characteristics Supply voltage VCC = 3.0 to 5.5 V (f(XIN) = 20 MHz)VCC = 2.7 to 5.5 V (f(XIN) = 10 MHz)Current consumption Typ. 9 mA (VCC = 5.0 V, f(XIN) = 20 MHz, comparator stopped)Typ. 5 mA (VCC = 3.0 V, f(XIN) = 10MHz, comparator stopped)Typ. 35 µA (VCC = 3.0 V, wait mode, peripheral clock off)Typ. 0.7 µA (VCC = 3.0 V, stop mode)Flash Memory Programming and erasure voltage VCC = 2.7 to 5.5 VProgramming and erasure endurance 10,000 times (data flash) 1,000 times (program ROM)Operating Ambient Temperature-20 to 85°C-40 to 85°C (D version) Package20-pin molded-plastic LSSOP20-pin molded-plastic SDIP28-pin molded-plastic HWQFN1.3Block DiagramFigure 1.1 shows a Block Diagram.1.4Product InformationTable 1.3 lists Product Information for R8C/18 Group and Table 1.4 lists Product Information for R8C/19 Group.Table 1.3Product Information for R8C/18 Group Current of Apr. 2006 Type No.ROM Capacity RAM Capacity Package Type RemarksR5F21181SP 4 Kbytes384 bytes PLSP0020JB-A Flash memory versionR5F21182SP 8 Kbytes512 bytes PLSP0020JB-AR5F21183SP 12 Kbytes768 bytes PLSP0020JB-AR5F21184SP 16 Kbytes 1 Kbyte PLSP0020JB-AR5F21181DSP (D) 4 Kbytes384 bytes PLSP0020JB-A D versionR5F21182DSP (D)8 Kbytes512 bytes PLSP0020JB-AR5F21183DSP (D)12 Kbytes768 bytes PLSP0020JB-AR5F21184DSP (D)16 Kbytes 1 Kbyte PLSP0020JB-AR5F21181DD 4 Kbytes384 bytes PRDP0020BA-A Flash memory versionR5F21182DD8 Kbytes512 bytes PRDP0020BA-AR5F21183DD12 Kbytes768 bytes PRDP0020BA-AR5F21184DD16 Kbytes 1 Kbyte PRDP0020BA-AR5F21182NP8 Kbytes512 bytes PWQN0028KA-B Flash memory versionR5F21183NP12 Kbytes768 bytes PWQN0028KA-BR5F21184NP16 Kbytes 1 Kbyte PWQN0028KA-B(D): Under Development(D): Under DevelopmentTable 1.4Product Information for R8C/19 GroupCurrent of Apr. 2006Type No.ROM CapacityRAM Capacity Package Type Remarks Program ROM Data flashR5F21191SP 4 Kbytes 1 Kbyte × 2384 bytes PLSP0020JB-A Flash memory versionR5F21192SP 8 Kbytes 1 Kbyte × 2512 bytes PLSP0020JB-A R5F21193SP 12 Kbytes 1 Kbyte × 2768 bytes PLSP0020JB-A R5F21194SP 16 Kbytes 1 Kbyte × 2 1 Kbyte PLSP0020JB-A R5F21191DSP (D) 4 Kbytes 1 Kbyte × 2384 bytes PLSP0020JB-A D versionR5F21192DSP (D)8 Kbytes 1 Kbyte × 2512 bytes PLSP0020JB-A R5F21193DSP (D)12 Kbytes 1 Kbyte × 2768 bytes PLSP0020JB-A R5F21194DSP (D)16 Kbytes 1 Kbyte × 2 1 Kbyte PLSP0020JB-A R5F21191DD 4 Kbytes 1 Kbyte × 2384 bytes PRDP0020BA-A Flash memory versionR5F21192DD 8 Kbytes 1 Kbyte × 2512 bytes PRDP0020BA-A R5F21193DD 12 Kbytes 1 Kbyte × 2768 bytes PRDP0020BA-A R5F21194DD 16 Kbytes 1 Kbyte × 2 1 Kbyte PRDP0020BA-A R5F21192NP 8 Kbytes 1 Kbyte × 2512 bytes PWQN0028KA-B Flash memory versionR5F21193NP 12 Kbytes 1 Kbyte × 2768 bytes PWQN0028KA-B R5F21194NP 16 Kbytes 1 Kbyte × 21 KbytePWQN0028KA-B1.5Pin AssignmentsFigure 1.4 shows Pin Assignments for PLSP0020JB-A Package (Top View), Figure 1.5 shows Pin Assignments for PRDP0020BA-A Package (Top View) and Figure 1.6 shows Pin Assignments for PWQN0028KA-B Package (Top View).1.6Pin FunctionsTable 1.5 lists Pin Functions, Table 1.6 lists Pin Name Information by Pin Number of PLSP0020JB-A,PRDP0020BA-A packages, and Table 1.7 lists Pin Name Information by Pin Number of PWQN0028KA-B package.I: InputO: OutputI/O: Input and outputTable 1.5Pin FunctionsTypeSymbolI/O TypeDescriptionPower supply input VCCVSS I Apply 2.7 V to 5.5 V to the VCC pin. Apply 0 V to the VSS pin.Analog power supply input AVCC, AVSS I Power supply for the comparatorConnect a capacitor between AVCC and AVSS.Reset input RESET I Input “L” on this pin resets the MCU.MODEMODE I Connect this pin to VCC via a resistor.Main clock input XIN I These pins are provided for main clock generation circuit I/O. Connect a ceramic resonator or a crystal oscillator between the XIN and XOUT pins.To use an external clock, input it to the XIN pin and leave the XOUT pin open.Main clock output XOUTO INT interrupt INT0, INT1, INT3I INT interrupt input pins Key input interrupt KI0 to KI3I Key input interrupt input pins Timer X CNTR0I/O Timer X I/O pin CNTR0O Timer X output pin Timer Z TZOUT O Timer Z output pin Timer CTCINI Timer C input pin CMP0_0 to CMP0_2, CMP1_0 to CMP1_2O Timer C output pins Serial interfaceCLK0I/O Transfer clock I/O pin RXD0, RXD1I Serial data input pins TXD0, TXD1O Serial data output pinsReference voltage input VREF I Reference voltage input pin to comparator Comparator AN8 to AN11I Analog input pins to comparatorI/O portP1_0 to P1_7, P3_3 to P3_5, P3_7, P4_5I/OCMOS I/O ports. Each port has an I/O select direction register, allowing each pin in the port to be directed for input or output individually.Any port set to input can be set to use a pull-up resistor or not by a program.P1_0 to P1_3 also function as LED drive ports.Input port P4_2, P4_6, P4_7IInput-only portsTable 1.6Pin Name Information by Pin Number of PLSP0020JB-A, PRDP0020BA-A packagesPin Number ControlPinPortI/O Pin Functions for Peripheral ModulesInterrupt Timer Serial Interface Comparator1P3_5CMP1_22P3_7CNTR0TXD13RESET4XOUT P4_75VSS/AVSS6XIN P4_67VCC/AVCC8MODE9P4_5INT0RXD110P1_7INT10CNTR0011P1_6CLK012P1_5INT11CNTR01RXD013P1_4TXD014P1_3KI3TZOUT AN11 15P1_2KI2CMP0_2AN10 16VREF P4_217P1_1KI1CMP0_1AN9 18P1_0KI0CMP0_0AN8 19P3_3INT3TCIN/CMP1_020P3_4CMP1_1Table 1.7Pin Name Information by Pin Number of PWQN0028KA-B packagePin Number ControlPinPortI/O Pin of Peripheral FunctionInterrupt Timer Serial Interface Comparator1NC2XOUT P4_73VSS/AVSS4NC5NC6XIN P4_67NC8VCC/AVCC9MODE10P4_5INT0RXD111P1_7INT10CNTR0012P1_6CLK013P1_5INT11CNTR01RXD014P1_4TXD015NC16P1_3KI3TZOUT AN11 17P1_2KI2CMP0_2AN10 18NC19NC20VREF P4_221NC22P1_1KI1CMP0_1AN9 23P1_0KI0CMP0_0AN8 24P3_3INT3TCIN/CMP1_025P3_4CMP1_126P3_5CMP1_227P3_7CNTR0TXD128RESET2.Central Processing Unit (CPU)Figure 2.1 shows the CPU Registers. The CPU contains 13 registers. R0, R1, R2, R3, A0, A1, and FB configure a register bank. There are two sets of register bank.2.1Data Registers (R0, R1, R2, and R3)R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is analogous to R2R0.2.2Address Registers (A0 and A1)A0 is a 16-bit register for address register indirect addressing and address register relative addressing.It is also used for transfer, arithmetic and logic operations. A1 is analogous to A0. A1 can be combined with A0 and used as a 32-bit address register (A1A0).2.3Frame Base Register (FB)FB is a 16-bit register for FB relative addressing.2.4Interrupt Table Register (INTB)INTB is a 20-bit register that indicates the start address of an interrupt vector table.2.5Program Counter (PC)PC is 20 bits wide, indicates the address of the next instruction to be executed.2.6User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)The stack pointer (SP), USP, and ISP, are each 16 bits wide. The U flag of FLG is used to switch between USP and ISP.2.7Static Base Register (SB)SB is a 16-bit register for SB relative addressing.2.8Flag Register (FLG)FLG is an 11-bit register indicating the CPU state.2.8.1Carry Flag (C)The C flag retains a carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.2.8.2Debug Flag (D)The D flag is for debugging only. Set it to 0.2.8.3Zero Flag (Z)The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.2.8.4Sign Flag (S)The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.2.8.5Register Bank Select Flag (B)Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.2.8.6Overflow Flag (O)The O flag is set to 1 when the operation results in an overflow; otherwise to 0.2.8.7Interrupt Enable Flag (I)The I flag enables maskable interrupts.Interrupts are disabled when the I flag is set to 0, and are enabled when the I flag is set to 1. The I flag is set to 0 when an interrupt request is acknowledged.2.8.8Stack Pointer Select Flag (U)ISP is selected when the U flag is set to 0; USP is selected when the U flag is set to 1.The U flag is set to 0 when a hardware interrupt request is acknowledged or the INT instruction of software interrupt numbers 0 to 31 is executed.2.8.9Processor Interrupt Priority Level (IPL)IPL is 3 bits wide, assigns processor interrupt priority levels from level 0 to level 7.If a requested interrupt has higher priority than IPL, the interrupt is enabled.2.8.10Reserved BitIf necessary, set to 0. When read, the content is undefined.3.Memory3.1R8C/18 GroupFigure 3.1 is a Memory Map of R8C/18 Group. The R8C/18 Group has 1 Mbyte of address space from addresses 00000h to FFFFFh.The internal ROM area is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM is allocated addresses 0C000h to 0FFFFh.The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.The internal RAM is allocated higher addresses, beginning with address 00400h. For example, a 1-Kbyte internal RAM area is allocated addresses 00400h to 007FFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.3.2R8C/19 GroupFigure 3.2 is a Memory Map of R8C/19 Group. The R8C/19 group has 1 Mbyte of address space from addresses 00000h to FFFFFh.The internal ROM (program ROM) is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM area is allocated addresses 0C000h to 0FFFFh.The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.The internal ROM (data flash) is allocated addresses 02400h to 02BFFh.The internal RAM is allocated higher addresses, beginning with address 00400h. For example, a 1-Kbyte internal RAM area is allocated addresses 00400h to 007FFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.4.Special Function Registers (SFRs)An SFR (special function register) is a control register for a peripheral function. Tables 4.1 to 4.4 list the special function registers.Table 4.1SFR Information (1)(1)Address Register Symbol After reset0000h0001h0002h0003h0004h Processor Mode Register 0PM000h0005h Processor Mode Register 1PM100h0006h System Clock Control Register 0CM001101000b0007h System Clock Control Register 1CM100100000b0008h0009h Address Match Interrupt Enable Register AIER00h000Ah Protect Register PRCR00h000Bh000Ch Oscillation Stop Detection Register OCD00000100b000Dh Watchdog Timer Reset Register WDTR XXh000Eh Watchdog Timer Start Register WDTS XXh000Fh Watchdog Timer Control Register WDC00011111b0010h Address Match Interrupt Register 0RMAD000h0011h00h0012h X0h0013h0014h Address Match Interrupt Register 1RMAD100h0015h00h0016h X0h0017h0018h0019h001Ah001Bh001Ch Count Source Protection Mode Register CSPR00h001Dh001Eh INT0 Input Filter Select Register INT0F00h001Fh0020h High-Speed On-Chip Oscillator Control Register 0HRA000h0021h High-Speed On-Chip Oscillator Control Register 1HRA1When shipping0022h High-Speed On-Chip Oscillator Control Register 2HRA200h0023h002Ah002Bh002Ch002Dh002Eh002Fh0030h0031h Voltage Detection Register 1(2)VCA100001000b0032h Voltage Detection Register 2(2)VCA200h(3)01000000b(4) 0033h0034h0035h0036h Voltage Monitor 1 Circuit Control Register (2)VW1C0000X000b(3)0100X001b(4) 0037h Voltage Monitor 2 Circuit Control Register (5)VW2C00h0038h0039h003Ah003Bh003Ch003Dh003Eh003FhX: UndefinedNOTES:1.The blank regions are reserved. Do not access locations in these regions.2.Software reset, watchdog timer reset, and voltage monitor 2 reset do not affect this register.3.After hardware reset.4.After power-on reset or voltage monitor 1 reset.5.Software reset, watchdog timer reset, and voltage monitor 2 reset do not affect b2 and b3.Table 4.2SFR Information (2)Address Register Symbol After reset 0040h0041h0042h0043h0044h0045h0046h0047h0048h0049h004Ah004Bh004Ch004Dh Key Input Interrupt Control Register KUPIC XXXXX000b 004Eh Comparator Conversion Interrupt Control Register ADIC XXXXX000b 004Fh0050h Compare 1 Interrupt Control Register CMP1IC XXXXX000b 0051h UART0 Transmit Interrupt Control Register S0TIC XXXXX000b 0052h UART0 Receive Interrupt Control Register S0RIC XXXXX000b 0053h UART1 Transmit Interrupt Control Register S1TIC XXXXX000b 0054h UART1 Receive Interrupt Control Register S1RIC XXXXX000b 0055h0056h Timer X Interrupt Control Register TXIC XXXXX000b 0057h0058h Timer Z Interrupt Control Register TZIC XXXXX000b 0059h INT1 Interrupt Control Register INT1IC XXXXX000b 005Ah INT3 Interrupt Control Register INT3IC XXXXX000b 005Bh Timer C Interrupt Control Register TCIC XXXXX000b 005Ch Compare 0 Interrupt Control Register CMP0IC XXXXX000b 005Dh INT0 Interrupt Control Register INT0IC XX00X000b 005Eh005Fh0060h0061h0062h0063h0064h0065h0066h0067h0068h0069h006Ah006Bh006Ch006Dh006Eh006Fh0070h0071h0072h0073h0074h0075h0076h0077h0078h0079h007Ah007Bh007Ch007Dh007Eh007FhX: UndefinedNOTE:1.The blank regions are reserved. Do not access locations in these regions.Table 4.3SFR Information (3)Address Register Symbol After reset 0080h Timer Z Mode Register TZMR00h0081h0082h0083h0084h Timer Z Waveform Output Control Register PUM00h0085h Prescaler Z Register PREZ FFh0086h Timer Z Secondary Register TZSC FFh0087h Timer Z Primary Register TZPR FFh0088h0089h008Ah Timer Z Output Control Register TZOC00h008Bh Timer X Mode Register TXMR00h008Ch Prescaler X Register PREX FFh008Dh Timer X Register TX FFh008Eh Timer Count Source Setting Register TCSS00h008Fh0090h Timer C Register TC00h0091h00h0092h0093h0094h0095h0096h External Input Enable Register INTEN00h0097h0098h Key Input Enable Register KIEN00h0099h009Ah Timer C Control Register 0TCC000h009Bh Timer C Control Register 1TCC100h009Ch Capture, Compare 0 Register TM000h009Dh00h(2)009Eh Compare 1 Register TM1FFh009Fh FFh00A0h UART0 Transmit/Receive Mode Register U0MR00h00A1h UART0 Bit Rate Register U0BRG XXh00A2h UART0 Transmit Buffer Register U0TB XXh00A3h XXh00A4h UART0 Transmit/Receive Control Register 0U0C000001000b 00A5h UART0 Transmit/Receive Control Register 1U0C100000010b 00A6h UART0 Receive Buffer Register U0RB XXh00A7h XXh00A8h UART1 Transmit/Receive Mode Register U1MR00h00A9h UART1 Bit Rate Register U1BRG XXh00AAh UART1 Transmit Buffer Register U1TB XXh00ABh XXh00ACh UART1 Transmit/Receive Control Register 0U1C000001000b 00ADh UART1 Transmit/Receive Control Register 1U1C100000010b 00AEh UART1 Receive Buffer Register U1RB XXh00AFh XXh00B0h UART Transmit/Receive Control Register 2UCON00h00B1h00B2h00B3h00B4h00B5h00B6h00B7h00B8h00B9h00BAh00BBh00BCh00BDh00BEh00BFhX: UndefinedNOTES:1.The blank regions are reserved. Do not access locations in these regions.2.When the output compare mode is selected (the TCC13 bit in the TCC1 register = 1), the value is set to FFFF16.R8C/18 Group, R8C/19 Group 4. Special Function Registers (SFRs)Table 4.4SFR Information (4)(1)Address Register Symbol After reset00C0h A/D Register AD XXh00C1h00C2h00C3h00C4h00C5h00C6h00C7h00C8h00C9h00CAh00CBh00CCh00CDh00CEh00CFh00D0h00D1h00D2h00D3h00D4h A/D Control Register 2ADCON200h00D5h00D6h A/D Control Register 0ADCON000000XXXb00D7h A/D Control Register 1ADCON100h00D8h00D9h00DAh00DBh00DCh00DDh00DEh00DFh00E0h00E1h Port P1 Register P1XXh00E2h00E3h Port P1 Direction Register PD100h00E4h00E5h Port P3 Register P3XXh00E6h00E7h Port P3 Direction Register PD300h00E8h Port P4 Register P4XXh00E9h00EAh Port P4 Direction Register PD400h00EBh00ECh00EDh00EEh00EFh00F0h00F1h00F2h00F3h00F4h00F5h00F6h00F7h00F8h00F9h00FAh00FBh00FCh Pull-Up Control Register 0PUR000XX0000b00FDh Pull-Up Control Register 1PUR1XXXXXX0Xb00FEh Port P1 Drive Capacity Control Register DRR00h00FFh Timer C Output Control Register TCOUT00h01B3h Flash Memory Control Register 4FMR401000000b01B4h01B5h Flash Memory Control Register 1FMR11000000Xb01B6h01B7h Flash Memory Control Register 0FMR000000001b0FFFFh Optional Function Select Register OFS(Note 2) X: UndefinedNOTES:1.The blank regions, 0100h to 01B2h and 01B8h to 02FFh are all reserved. Do not access locations in these regions.2.The OFS register cannot be changed by a program. Use a flash programmer to write to it.5.Electrical CharacteristicsNOTES:1.V CC =2.7 to 5.5 V at T opr = -20 to 85 °C / -40 to 85 °C, unless otherwise specified.2.Typical values when average output current is 100 ms.Table 5.1Absolute Maximum RatingsSymbol ParameterCondition Rated Value Unit V CC Supply voltage V CC = AV CC -0.3 to 6.5V AV CC Analog supply voltage V CC = AV CC-0.3 to 6.5V V I Input voltage -0.3 to V CC +0.3V V O Output voltage -0.3 to V CC +0.3V P d Power dissipationT opr = 25°C300mW T opr Operating ambient temperature -20 to 85 / -40 to 85 (D version)°C T stgStorage temperature-65 to 150°CTable 5.2Recommended Operating ConditionsSymbol ParameterConditionsStandardUnit Min.Typ.Max.V CC Supply voltage 2.7− 5.5V AV CC Analog supply voltage −V CC −V V SS Supply voltage −0−V AV SS Analog supply voltage −0−V V IH Input “H” voltage 0.8V CC−V CC V V IL Input “L” voltage0−0.2V CC V I OH(sum)Peak sum output “H” current Sum of all pins I OH (peak)−−-60mA I OH(peak)Peak output “H” current −−-10mA I OH(avg)Average output “H” current −−-5mA I OL(sum)Peak sum output “L” currents Sum of all pins I OL (peak)−−60mA I OL(peak)Peak output “L” currents Except P1_0 to P1_3−−10mA P1_0 to P1_3Drive capacity HIGH −−30mA Drive capacity LOW−−10mA I OL(avg)Average output “L” currentExcept P1_0 to P1_3−−5mA P1_0 to P1_3Drive capacity HIGH −−15mA Drive capacity LOW −−5mA f (XIN)Main clock input oscillation frequency3.0 V ≤ V CC ≤ 5.5 V 0−20MHz 2.7 V ≤ V CC < 3.0 V 0−10MHzNOTES:1.V CC =2.7 to 5.5 V at T opr = -20 to 85 °C / -40 to 85 °C, unless otherwise specified.2.If f1 exceeds 10 MHz, divided f1 and ensure the comparator conversion operating clock frequency (φAD ) is 10 MHz or below.3.If AVcc is less than4.2 V, divided f1 and ensure the comparator conversion operating clock frequency (φAD ) is f1/2 or below.Table 5.3Comparator CharacteristicsSymbol ParameterConditionsStandardUnit Min.Typ.Max.−Resolution −−1Bit −Absolute accuracy φAD = 10 MHz (3)−−±20mV t conv Conversion time φAD = 10 MHz (3)1−−µs V ref Reference voltage 0−AV CC V V IA Analog input voltage0−AV CC V −Comparator conversion operating clock frequency (2)1−10MHzNOTES:1.V CC =2.7 to 5.5 V at T opr = 0 to 60 °C, unless otherwise specified.2.Definition of programming/erasure enduranceThe programming and erasure endurance is defined on a per-block basis.If the programming and erasure endurance is n (n = 100 or 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one. However, the same address must not be programmed more than once per erase operation (overwriting prohibited).3.Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).4.If emergency processing is required, a suspend request can be generated independent of this characteristic. In that case thenormal time delay to Suspend can be applied to the request.However, we recommend that a suspend request with an interval of less than 650 µs is only used once because, if the suspend state continues, erasure cannot operate and the incidence of erasure error rises.5.In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequentialaddresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. In addition, averaging the number of erase operations between block A and block B can further reduce the effective number of rewrites. It is also advisable to retain data on the erase count of each block and limit the number of erase operations to a certain number.6.If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erasecommand at least three times until the erase error does not occur.7.Customers desiring programming/erasure failure rate information should contact their Renesas technical supportrepresentative.8.The data hold time includes time that the power supply is off or the clock is not supplied.Table 5.4Flash Memory (Program ROM) Electrical CharacteristicsSymbol ParameterConditionsStandardUnit Min.Typ.Max.−Program/erase endurance (2)R8C/18 Group 100(3)−−times R8C/19 Group1,000(3)−−times −Byte program time −50400µs −Block erase time−0.49s t d(SR-SUS)Time delay from suspend request until suspend−−97+CPU clock × 6 cyclesµs −Interval from erase start/restart until following suspend request650−−µs −Interval from program start/restart until following suspend request0−−ns −Time from suspend until program/erase restart−−3+CPU clock × 4 cyclesµs −Program, erase voltage 2.7− 5.5V −Read voltage2.7− 5.5V −Program, erase temperature 0−60 °C −Data hold time (8)Ambient temperature = 55 °C20−−year。

瑞萨单片机启动文件介绍

瑞萨单片机启动文件介绍1.NC30介绍NC30的组件:nc30----------------编译驱动器cpp30---------------预处理器ccom30--------------编译器aopt30--------------汇编优化器sbauto--------------SB寄存器自动更新工具stkviewer & stk-----STK查看器与堆栈大小计算工具utl30---------------SBDATA声明及SPECIAL页函数声明工具mapview-------------映射查看器看下NC30处理流程:程序开发流程,生成X30文件的流程:以上就是编译器所做的工作和流程。

看了之后大家有了大概的了解。

具体的大家可以参看NC30编译器手册,待会会上传附件给大家下载。

2:启动程序介绍ncrt0.a30这个程序在程序启动或复位后立即运行,它主要执行下列处理:.设置SBDATA区.设置处理器的操作模式.初始化堆栈指针.初始化SB寄存器.初始化INTB寄存器.初始化NEAR数据区.初始化FAR数据区.初始化堆区.初始化标准I/O函数程序库.初始化FB寄存器.调用MAIN函数ncrt0.a30汇编文件,在建立工程的时候会自动生成。

以下附带详细注释,附件也可下载。

;***************************************************************************; C Compiler for R8C/Tiny, M16C/60,30,20,10; Copyright(C) 1999(2000-2006). Renesas Technology Corp.; and Renesas Solutions Corp., All rights reserved.;; ncrt0.a30 : Startup Program for M16C family;; $Date: 2006/11/22 04:13:23 $; $Revision: 1.1.4.1 $;***************************************************************************;---------------------------------------------------------------------; include files ;包含文件;---------------------------------------------------------------------.list OFF ;控制行输出数据输出到列表文件OFF:停止ON:开始.include nc_define.inc ;包含宏文件.include sect30.inc ;包含存储器映射文件.list ON;---------------------------------------------------------------------; BankSelect definition for 4M mode;---------------------------------------------------------------------; .glb __BankSelect;__BankSelect .equ 0BH;===================================================================== ; Interrupt section start ;中断段起始;---------------------------------------------------------------------.insf start,S,0.glb start.section interruptstart: ;复位后从这个标签开始运行;---------------------------------------------------------------------; after reset,this program will start ;复位后程序将启动;---------------------------------------------------------------------ldc #istack_top,isp ;设置istack指针(中断堆栈) ldc向专用寄存器ISP传递数据mov.b #02h,0ah ;保护寄存器PRCR PRC1=1 允许写PM0mov.b #00h,04h ;设置处理器模式PM0mov.b #00h,0ah ;关闭写保护.if __STACKSIZE__ != 0ldc #0080h,flg ;设置FLG寄存器IPL和其他状态FLG是16位标志寄存器堆栈指针选择USPldc #stack_top,sp ;设置堆栈指针.elseldc #0000h,flg.endifldc #data_SE_top,sb ;设置SB静态基址寄存器ldintb #__VECTOR_ADR__ ;向INTB寄存器传送指令,所以这里省了目标操作数intb;=====================================================================; NEAR area initialize. ;NEAR区初始化;---------------------- -----------------------------------------------; bss zero clear ;bss零清除;---------------------------------------------------------------------N_BZERO bss_SE_top,bss_SE ;清除NEAR bss段至零N_BZERO bss_SO_top,bss_SO ;N_BZERO清零宏定义N_BZERO bss_NE_top,bss_NE ;sect30.inc中有定义N_BZERO bss_NO_top,bss_NO;---------------------------------------------------------------------; initialize data section ;初始化数据段;---------------------------------------------------------------------N_BCOPY data_SEI_top,data_SE_top,data_SE ;将NEAR数据段和SBDA TA数据段的初始值转移到RAMN_BCOPY data_SOI_top,data_SO_top,data_SO ;N_BCOPY拷贝宏定义N_BCOPY data_NEI_top,data_NE_top,data_NE ;sect30.inc中有定义N_BCOPY data_NOI_top,data_NO_top,data_NO;=====================================================================; FAR area initialize. ;FAR区初始化;---------------------------------------------------------------------; bss zero clear ;bss零清除;---------------------------------------------------------------------.if __FAR_RAM_FLG__ != 0BZERO bss_FE_top,bss_FEBZERO bss_FO_top,bss_FO.endif;---------------------------------------------------------------------; initialize data section ;将FAR段数据段的初始值移到RAM中;---------------------------------------------------------------------.if __FAR_RAM_FLG__ != 0 ;从edata_EI(OI)段复制edata_E(O)段BCOPY data_FEI_top,data_FE_top,data_FEBCOPY data_FOI_top,data_FO_top,data_FOldc #stack_top,sp.stk -40.endif;===================================================================== ; heap area initialize ;堆区初始化;---------------------------------------------------------------------.if __HEAPSIZE__ != 0.glb __mnext.glb __msizemov.w #(heap_top&0FFFFH),__mnextmov.w #(heap_top>>16),__mnext+2mov.w #(__HEAPSIZE__&0FFFFH),__msizemov.w #(__HEAPSIZE__>>16),__msize+2.endif;===================================================================== ; Initialize standard I/O ;初始化标准I/O;---------------------------------------------------------------------.if __STANDARD_IO__ == 1.glb __init.call __init,Gjsr.a __init.endif;===================================================================== ; Call main() function ;调用MAIN函数;---------------------------------------------------------------------ldc #0h,fb ; for debuger 用于调试器.glb _mainjsr.a _main;===================================================================== ; exit() function ;推出函数;---------------------------------------------------------------------.glb _exit.glb $exit_exit: ; End program 结束程序$exit:jmp _exit.einsf;===================================================================== ; dummy interrupt function ;虚设的中断处理函数;---------------------------------------------------------------------.glb dummy_intdummy_int:reit.end;***************************************************************************; C Compiler for R8C/Tiny, M16C/60,30,20,10; Copyright(C) 1999(2000-2006). Renesas Technology Corp.; and Renesas Solutions Corp., All rights reserved.;***************************************************************************映射文件:sect30.inc.映射各个段.设置段的起始地址.定义堆栈和堆段的大小.设置中断向量表.设置固定向量表.宏定义;***************************************************************************; C Compiler for R8C/Tiny, M16C/60,30,20,10; Copyright(C) 1999(2000-2006). Renesas Technology Corp.; and Renesas Solutions Corp., All rights reserved.;; sect30.inc : section definition for M16C family;; $Date: 2007/01/09 04:38:46 $; $Revision: 1.1.4.1 $;***************************************************************************;===================================================================== ;; Arrangement of section ;段的排列;;---------------------------------------------------------------------; Near RAM data area ;Near RAM数据区;---------------------------------------------------------------------; SBDATA area.section data_SE,DATA.org 400Hdata_SE_top:.section bss_SE,DATA,ALIGNbss_SE_top:.section data_SO,DATAdata_SO_top:.section bss_SO,DATAbss_SO_top:; SBDATA area definition.glb __SB____SB__ .equ data_SE_top; near RAM area.section data_NE,DATA,ALIGNdata_NE_top:.section bss_NE,DATA,ALIGNbss_NE_top:.section data_NO,DATAdata_NO_top:.section bss_NO,DATAbss_NO_top:;--------------------------------------------------------------------- ; Stack area ;堆栈区;--------------------------------------------------------------------- .section stack,DATA,ALIGN.blkb __ISTACKSIZE__ ;.blkb分配一字节ram istack_top:.if __STACKSIZE__ != 0.blkb __STACKSIZE__stack_top:.endif;--------------------------------------------------------------------- ; heap section ;heap段;--------------------------------------------------------------------- .if __HEAPSIZE__ != 0.section heap,DATAheap_top:.blkb __HEAPSIZE__.endif;--------------------------------------------------------------------- ; Near ROM data area ;NEAR rom数据区;--------------------------------------------------------------------- .if __NEAR_ROM_FLG__ != 0.section rom_NE,ROMDATA,ALIGNrom_NE_top:.section rom_NO,ROMDATArom_NO_top:.endif;--------------------------------------------------------------------- ; Far RAM data area ;FAR RAM 数据区;--------------------------------------------------------------------- .if __FAR_RAM_FLG__ != 0.section data_FE,DATA.org 10000Hdata_FE_top:.section bss_FE,DATA,ALIGNbss_FE_top:.section data_FO,DATAdata_FO_top:.section bss_FO,DATAbss_FO_top:.endif;--------------------------------------------------------------------- ; Far ROM data area ;FAR ROM 数据;--------------------------------------------------------------------- .section rom_FE,ROMDATA.org __ROM_TOPADR__rom_FE_top:.section rom_FO,ROMDATArom_FO_top:;--------------------------------------------------------------------- ; Initial data of 'data' section ;far rom数据初始化;--------------------------------------------------------------------- .section data_SEI,ROMDATA,ALIGNdata_SEI_top:.section data_SOI,ROMDATAdata_SOI_top:.section data_NEI,ROMDATA,ALIGNdata_NEI_top:.section data_NOI,ROMDATAdata_NOI_top:.if __FAR_RAM_FLG__ != 0.section data_FEI,ROMDATA,ALIGNdata_FEI_top:.section data_FOI,ROMDATAdata_FOI_top:.endif;--------------------------------------------------------------------- ; Switch Table Section;--------------------------------------------------------------------- ; .section switch_table,ROMDATA;switch_table_top:;--------------------------------------------------------------------- ; code area ;代码区;--------------------------------------------------------------------- .section program,CODE,ALIGN.section interrupt,CODE,ALIGN.section program_S,CODE,ALIGN;---------------------------------------------------------------------; variable vector section ;变量向量段;---------------------------------------------------------------------.section vector,ROMDATA.org __VECTOR_ADR__.if 0.lword dummy_int ; vector 0 BRK.lword dummy_int ; vector 1.lword dummy_int ; vector 2.lword dummy_int ; vector 3.lword dummy_int ; vector 4 (for user) int3.lword dummy_int ; vector 5 (for user) timerB5.lword dummy_int ; vector 6 (for user) timerB4.lword dummy_int ; vector 7 (for user) timerB3.lword dummy_int ; vector 8 (for user) si/o4/int5.lword dummy_int ; vector 9 (for user) si/o3/int4.lword dummy_int ; vector 10 (for user) Bus collision detection .lword dummy_int ; vector 11 (for user) DMA0.lword dummy_int ; vector 12 (for user) DMA1.lword dummy_int ; vector 13 (for user) Key input interrupt.lword dummy_int ; vector 14 (for user) A-D.lword dummy_int ; vector 15 (for user) uart2 transmit.lword dummy_int ; vector 16 (for user) uart2 receive.lword dummy_int ; vector 17 (for user) uart0 transmit.lword dummy_int ; vector 18 (for user) uart0 receive.lword dummy_int ; vector 19 (for user) uart1 transmit.lword dummy_int ; vector 20 (for user) uart1 receive.lword dummy_int ; vector 21 (for user) timer A0.lword dummy_int ; vector 22 (for user) timer A1.lword dummy_int ; vector 23 (for user) timer A2.lword dummy_int ; vector 24 (for user) timer A3.lword dummy_int ; vector 25 (for user) timer A4.lword dummy_int ; vector 26 (for user) timer B0.lword dummy_int ; vector 27 (for user) timer B1.lword dummy_int ; vector 28 (for user) timer B2.lword dummy_int ; vector 29 (for user) int0.lword dummy_int ; vector 30 (for user) int1.lword dummy_int ; vector 31 (for user) int2.lword dummy_int ; vector 32 (for user or MR30).lword dummy_int ; vector 33 (for user or MR30).lword dummy_int ; vector 34 (for user or MR30).lword dummy_int ; vector 35 (for user or MR30).lword dummy_int ; vector 36 (for user or MR30).lword dummy_int ; vector 37 (for user or MR30).lword dummy_int ; vector 38 (for user or MR30).lword dummy_int ; vector 39 (for user or MR30).lword dummy_int ; vector 40 (for user or MR30).lword dummy_int ; vector 41 (for user or MR30).lword dummy_int ; vector 42 (for user or MR30).lword dummy_int ; vector 43 (for user or MR30).lword dummy_int ; vector 44 (for user or MR30).lword dummy_int ; vector 45 (for user or MR30).lword dummy_int ; vector 46 (for user or MR30).lword dummy_int ; vector 47 (for user or MR30) .lword dummy_int ; vector 48.lword dummy_int ; vector 49.lword dummy_int ; vector 50.lword dummy_int ; vector 51.lword dummy_int ; vector 52.lword dummy_int ; vector 53.lword dummy_int ; vector 54.lword dummy_int ; vector 55.lword dummy_int ; vector 56.lword dummy_int ; vector 57.lword dummy_int ; vector 58.lword dummy_int ; vector 59.lword dummy_int ; vector 60.lword dummy_int ; vector 61.lword dummy_int ; vector 62.lword dummy_int ; vector 63.endif;--------------------------------------------------------------------- ; fixed vector section ;固定向量段;--------------------------------------------------------------------- .section fvector,ROMDATA.org 0fffdcHUDI:.lword dummy_intOVER_FLOW:.lword dummy_intBRKI:.lword dummy_intADDRESS_MATCH:.lword dummy_intSINGLE_STEP:.lword dummy_intWDT:.lword dummy_intDBC:.lword dummy_intNMI:.lword dummy_intRESET:.lword start;===================================================================== ; ID code & ROM code protect //密码保护设置;---------------------------------------------------------------------; ID code check function.id "#FFFFFFFFFFFFFF"; ROM code protect control address; .protect 00H;===================================================================== ; Initialize Macro declaration //宏定义,ncrt0.30中有使用到;---------------------------------------------------------------------N_BZERO .macro TOP_,SECT_mov.b #00H,R0Lmov.w #(TOP_ & 0FFFFH),A1mov.w #sizeof SECT_,R3sstr.b.endmN_BCOPY .macro FROM_,TO_,SECT_mov.w #(FROM_ & 0FFFFH),A0mov.b #(FROM_ >> 16),R1Hmov.w #TO_,A1mov.w #sizeof SECT_,R3smovf.b.endmBZERO .macro TOP_,SECT_push.w #sizeof SECT_ >> 16push.w #sizeof SECT_ & 0ffffhpusha TOP_ >> 16pusha TOP_ & 0ffffh.stk 8.glb _bzero.call _bzero,Gjsr.a _bzero.endmBCOPY .macro FROM_ ,TO_ ,SECT_push.w #sizeof SECT_ >> 16push.w #sizeof SECT_ & 0ffffhpusha TO_ >> 16pusha TO_ & 0ffffhpusha FROM_ >> 16pusha FROM_ & 0ffffh.stk 12.glb _bcopy.call _bcopy,Gjsr.a _bcopy.endm;*************************************************************************** ; C Compiler for R8C/Tiny, M16C/60,30,20,10; Copyright(C) 1999(2000-2006). Renesas Technology Corp.; and Renesas Solutions Corp., All rights reserved.;***************************************************************************nc_define.inc头文件定义;------------------------------------------------------------------------; |; FILE :nc_define.inc |; DATE :Fri, Dec 18, 2009 |; DESCRIPTION :interrupt program. |; CPU GROUP :29 |; |; This file is generated by Renesas Project Generator (Ver.4.8). |; |;------------------------------------------------------------------------; Macro Symbol definition__NEAR_ROM_FLG__ .equ 0 ; NEAR ROM flag definition__FAR_RAM_FLG__ .equ 0 ; FAR RAM flag definition__STANDARD_IO__ .equ 0 ; STANDARD I/O flag definition__HEAPSIZE__ .equ 0300H ; HEEP SIZE definition__STACKSIZE__ .equ 0300H ; STACK SIZE definition__ISTACKSIZE__ .equ 0300H ; INTERRUPT STACK SIZE definition__VECTOR_ADR__ .equ 0ffd00H ; INTERRUPT VECTOR ADDRESS definition__ROM_TOPADR__ .equ 0F4000H ; ROM TOP ADDRESS definition__SPECIAL_PRG__ .equ 0f8000H ; Special page program address。

瑞萨芯片选型

SuperH RISC engine 族产品概要:SuperH是具有高性能价格比、小型化和高性能功耗比(MIPS/W)特性的嵌入式RISC单片机。

我们正在开发具有广泛的应用范围和多种功能的CPU内核,并提供有强大的产品阵容。

产品系列包含具有CPU内核、内部大容量快速擦写存储器和定时器、串行接口、AD转换器等外围功能的SH-2系列;具有能进行高速数据处理的CPU内核、高速缓冲存储器和MMU的SH-3系列或SH-4系列;具有全DSP功能和以多媒体处理/通信处理为主的CPU内核的SH2-DSP系列或SH3-DSP系列。

现在提供的产品还具有低功率模式、低功耗和小型化等许多特点。

改善了各种通用操作系统和开发工具,从而保证能实现更有效的开发。

主要应用•MPUo汽车导航系统、CIS、娱乐设备和多媒体设备。

o宽带路由器、防火墙、网络设备和因特网设备。

o小型打印机、直接打印机、POS终端、便携式终端和网络终端。

o DVC、DSC和图像处理设备等。

•MCUo空调、电冰箱和洗衣机。

o打印机、传真机和复印机。

o工业设备和机床。

o汽车引擎和动力转向系统。

.瑞萨MCU选型指南有想法吗?请使用我们的,为您寻找最合适的瑞萨产品。

Lineup:SH7780系列SH7780系列是搭载SH-4A CPU内核的高端SuperH处理器。

SH-4A的指令集是完全向上兼容的。

SH-4A的工作频率比已有的SH-4 CPU内核高的多。

并且SH-4A CPU内核具有支持单精度和双精度算术运算的FPU。

SH7722 | SH7723 | SH7724 | SH7730 | SH7731 | SH7763 | SH7764 | SH7780 | SH7781 | SH7785 | SH7786SH7450 系列SH7450系列高性能微控制器配有SH-4A CPU内核。

SH7450系列整合了大容量Flash存储器和SRAM,使其能够适用于汽车主动安全系统,如驱动支持。

51单片机C语言开发

sfr

sfr16

sbit

sbit将一个变量名与一个芯片内部RAM中的可寻址位相联系,或者与特殊功 能寄存器中的可寻址位相联系。例如 sfr P0 = 0x80; sbit P0_1 = P0^1, 这样,在以后的程序中可以用P0_1对P0口的1号引脚进行读/写操作。

Keil C 主界面

51单片机C语言简单开发 (伍建全 )

了解51单片机原理 51单片机并口输入、输出 51单片机中断处理程序 51单片机定时器、计数器使用

微型计算机

微型计算机 (PC)

什么是单片机?

单片机即单片微型计算机(Single-Chip Microcomputer), 又称单片机(Microcontroller),是把中央处理器、存储 器、定时/计数器(Timer/Counter)、各种输入输出接口 等都集成在一块集成电路芯片上的微型计算机。 与应用在个人电脑中的通用型微处理器相比,它更强调自 供应(不用外接硬件)和节约成本。它的最大优点是体积 小,可放在仪表内部,但存储量小,输入输出接口简单, 功能较低。由于其发展非常迅速,旧的单片机的定义已不 能满足,所以在很多应用场合被称为范围更广的微控制器; 由于单芯片微电脑常用于当控制器故又名single chip microcontroller,但是目前在中国大陆仍多沿用“单片机” 的称呼

C51编译器的扩展关键字

关键字 bit sbit sfr sfr16 data bdata idata pdata xdata code interrupt reentrant using 用 途 说 明 位标量声明 声明一个位标量或位类型的函数 位标量声明 声明一个可位寻址变量 特殊功能寄存器声明 声明一个特殊功能寄存器 特殊功能寄存器声明 声明一个16位的特殊功能寄存器 存储器类型说明 直接寻址的内部数据存储器 存储器类型说明 可位寻址的内部数据存储器 存储器类型说明 间接寻址的内部数据存储器 存储器类型说明 分页寻址的外部数据存储器 存储器类型说明 外部数据存储器 存储器类型说明 程序存储器 中断函数说明 定义一个中断函数 再入函数说明 定义一个再入函数 寄存器组定义 定义芯片的工作寄存器

瑞萨电子 MCU型号 速查手册

2010.09瑞萨电子M C U 型号速查手册QzROM 低功耗720、740工具R8C族及工具M16C R32C M16C族工具SuperH族及工具安全MCU 芯片封装说明78K V85078K、V850工具QzROM 13720族、740族开发工具介绍4低功耗6R8C族及其开发工具介绍23M16C族29M16C族R32C34M16C族开发工具介绍36SuperH RISC engine族及其开发工具介绍45安全MCU 78芯片封装说明5078K 65V8507578K、V850微控制器开发工具介绍瑞萨电子MCU 型号速查手册QzROM1QzROM 低功耗720、740工具78K、V850工具R8C族及工具SuperH族及工具M16C族工具安全MCU 78K V850芯片封装说明M16C R32C2QzROMM16C R32CM16C族工具安全MCU78K V850芯片封装说明720、740工具78K、V850工具QzROM低功耗R8C族及工具SuperH族及工具3720族、740族开发工具QzROM 低功耗720、740工具78K、V850工具R8C族及工具SuperH族及工具M16C族工具安全MCU 78K V850芯片封装说明M16C R32CM16C R32CM16C族工具安全MCU78K V850芯片封装说明720、740工具78K、V850工具QzROM低功耗R8C族及工具SuperH族及工具5低功耗QzROM 低功耗720、740工具78K、V850工具R8C族及工具SuperH族及工具M16C族工具安全MCU 78K V850芯片封装说明M16C R32C6R8C族1x系列R 5F 21254S D X X X S P U 010*********瑞萨新MCU代码器件区分ex)F:闪存瑞萨R8C族代码瑞萨R8C群代码ex)R8C/1B, R8C/25存储器变化(仅R8C系列)0:2KB 1:4KB 2:8KB 3:12KB 4:16KB5:24KB 6:32KB 7:48KB 8:64KBA:96KB C:128KB(-):标准版本S :低电压版本A :R8C/3x的新增功能代码2ex) J -40~85℃ 汽车K -40~125℃ 汽车D -40~85℃ 工业N或无标记 -20~85℃ 消费类电子ROM型号(仅用于出厂编程的MCU)FP:LQFP, SP:LSSOP, NP:QFNFA:LQFP, DD:SDIP, LG:FLGAU0:无铅产品,盘装或管装出货W4:无铅产品,卷带出货无标记:含铅产品,盘装或管装出货T4:含铅产品,卷带出货ES:工程样品12345678910R8C族MCU命名规则QzROM 低功耗720、740工具78K、V850工具R8C族及工具SuperH族及工具M16C族工具安全MCU 78K V850芯片封装说明M16C R32C7R8C族1x系列QzROM 低功耗720、740工具78K、V850工具R8C族及工具SuperH族及工具M16C族工具安全MCU 78K V850芯片封装说明M16C R32C8R8C族1x系列注:① R8C/1x芯片的ROM类型均为Flash。

瑞萨中国公司简介

7半导体,随着技术创新不断取得惊人的发展,凝聚着人类的梦想,推动着社会的发展。

现如今,从家用电器、移动电话、汽车、工业设备到航天火箭,半导体被广泛应用于各种电子设备中。

小小的芯片承接着我们的未来。

便捷的社会和舒适的生活无不体现着人类的智慧与力量。

并于此后,在享受着便利生活的同时,为了实现人类与地球共生的理想和建立物质生活更加丰富的社会远景,必须更多的考虑地球环境和人类生活所要求的安全性。

新生的瑞萨电子,能够迅速及时应对全世界各地客户的需求,以成为客户产品开发最值得信赖的合作伙伴为目标,积极推动MCU、系统LSI、模拟及功率半导体器件的事业发展,致力于提供最佳解决方案。

解决方案面向移动设备的So C模拟及功率器件功率器件3D[瑞萨电子在中国的销售·技术支持网点]瑞萨电子(上海)有限公司瑞萨电子(中国)有限公司瑞萨电子通过集成了睿智新技术的专业优势,努力成为能帮助全社会实现愿景并构筑未来的企业,瑞萨电子致力于创建一个人与自然和谐相处、共同繁荣的世界。

瑞萨电子将在发挥创造力和技术创新能力的基础上,最迅速的响应世界各地客户的需求,并力争发展成为一个强大的、成长型半导体厂商和值得信任的商业合作伙伴。

瑞萨电子株式会社 (英文名:Renesas Electronics Corporation )神奈川县川崎市中原区下沼部1753号东京都千代田区大手町二町目6番2号(日本大楼)1,532亿日元(约19亿美元)2002年11月1日(于2010年4月1日起开始营业)提供各种半导体的研究、开发、设计、制造、销售及服务42,800人(截至2012年3月31日)公司名总公司总公司办事处注册资本成立日期经营范围员工人数[瑞萨电子中国组织结构图][瑞萨电子株式会社的介绍][企业愿景][企业理念][公司概要]。

瑞萨单片机在电表上的应用

1路 64引脚 32.768KHz等待模式2.2uA —40。C至85。C

一137—

2009第十八届中国电工仪器仪表产业发展论坛暨展会

新技术新产品

16位单片机R5F3640D(M16C/64群) M16C/62,64系列,具有1MB的地址空间。最

大工作频率为25MHz。备有闪存版,内部闪存可以 在单电源下编程,支持双电源系统。

定时器

8位定时器lch(RB)

8位定时器lch(肛,R1℃功能)

16位定时器2ch(RD)

2通道 10位x 8通道 可编程I/O 看门狗定时器 封装 l路 52引脚O 65nⅦLQFP

32

低功耗特点 工作温度

7681CBI等待模式2uA(3V.RTC工作4uA)

2009第十八届中国电工仪器仪表产业发展论坛暨展会

Design of Intelligent Multi—rate Watt-hour Meter Based NEC MCU UPD78F0455

^hm能According

describes the

Io

on

the requimment of the latest standard for static payment mel盯for active ca“gy this paFr

本文链接:/Conference_7067048.aspx

定时器

8位定时器lch 8位定时器leh 8位定时器lch 16位定时器lch

UART

2通道 2通道2.85V。3.6V

28

模拟比较器 可编程I/O 看门狗定时器

1路 32引脚

32.768KHz

封装

低功耗特点 工作温度

—40。C至85。C

瑞萨单片机入门教程

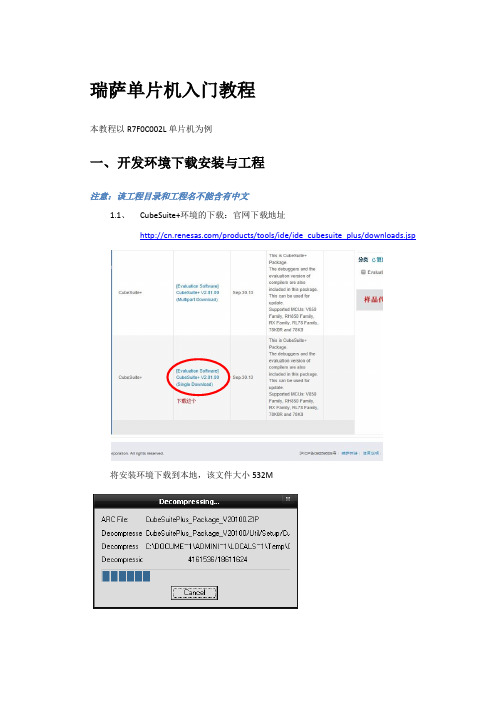

瑞萨单片机入门教程本教程以R7F0C002L单片机为例一、开发环境下载安装与工程注意:该工程目录和工程名不能含有中文1.1、CubeSuite+环境的下载:官网下载地址/products/tools/ide/ide_cubesuite_plus/downloads.jsp将安装环境下载到本地,该文件大小532M在安装过程中有提示需要填写注册码,请输入以下注册码,如果无效请联系供应商。

查看是否已经注册:在IDE环境中选择 Help->About后有下面窗口:注册码:67DCS-V3Q7L-XMGL9-FI6L9-EE1BJ该注册码有限制台数的,一旦注册了就会把MAC绑定,重装无需注册!当有以下报错时:请查看是否已经注册。

1.2、 按照一般的软件安装方法安装好IDE 环境,下面介绍IDE 环境的配置:1、 将DIF_RFP 文件夹下的Device_Custom 文件夹拷贝到安装目录下的C:\Program Files\Renesas Electronics\CubeSuite+下(这里是默认的安装目录,另外注意:DIF_RFP 中Readme_Device_Custom.txt 说将Device-_Custom文件夹拷贝到C:\Program Files\RenesasElectronics\CubeSuite+\Device 下,但是实际上不可以!)。

当配置成功以后会在芯片族里面多出R7F 系列的单片机,如下图示:2、 将DIF_RFP 文件夹下的RFP_R7F0C002L_V10000子目录下面的两个文件(Device_Custom 文件夹和Custom_Productlist.xml 文件)拷贝到安装目录下的C:\Program Files\Renesas Electronics\Programming Tools\Renesas Flash Programmer V2.01\Device 下(这里是默认安装路径)。

瑞萨单片机M16C, R8C 有效的编程技术(培训资料)

M16C族编程技巧(M3T-NC30WA 工具链)2005年2月M3T-NC30WA 特点•支持MCU M16C 族-M16C/60, 30, 20, 10, R8C/Tiny 系列.•性能(Performance) 可以减小ROM大小的辅助功能强大的提高代码效率的优化功能•存储器型号(Memory model) 支持每个变量的near/far限定词•扩展功能(Extended functions)支持嵌入式系统的#pragma指令 •附加工具(Attached tools)IDE -TM 和HEW, 结构汇编器(Structured assembler) 和模拟器(Simulator).M3T-NC30WA存储器分配(Memory allocation )near/far#pragma ADDRESS #pragma BITADDRESS #pragma SECTION #pragma STRUCTetc减小ROM 大小(Reducing ROM size )#pragma SBDATA #pragma SPECIAL #pragma JSRA/JSRW#pragma BIT UTLxx etc 其他#pragma INTERRUPT #pragma PARAMETER #pragma ASM/ENDASM #pragma INTCALLasm( ) etcRTOS#pragma ALMHANDLER #pragma CYCHANDLER #pragma INTHANDLER #pragma TASK提高性能!减小系统消耗(Reduce OS overhead )给不同系统分配存储器!#pragma 扩展功能(Extended Functions)NEAR 修饰符–000000H ~ 00FFFFH 区域FAR 修饰符–000000H ~0FFFFFH 区域每个变量都有Near 和far指定near/far默认ROM areaSFRRAM areanear RAM far ROMFFFF1Mbytesnear areafar areaint near i;int far j;注意: 程序已固定far 属性FFFF默认是NEAR 指针j i *i int * i ;k*k int far * k;FFFFint far * far j ;*j#pragma ADDRESS port 03ECH#pragma ADDRESS base 100H extern int base;#pragma ADDRESS base2 _base+2H extern int base2;#pragma ADDRESS base3 _base+4H extern int base4;不仅对I/O 变量,对RAM 中的变量也很方便.Same as#define base *(volatile int *)0x100#pragma 地址指定变量的绝对地址 可以被用作设定SFR 区#pragma INTERRUPT /B func()Using bank registersvoid func( void ){}R0FB R1R2A0R3A1将后寄存器切换到前寄存器R0FB R1R2A0R3A1R0FBR1R2A0R3A1SB将寄存器切换到后寄存器R0FB R1R2A0R3A1SB声明中断处理器(interrupt handler) /B 使中断处理加快#pragma INTERRUPT /E func() 允许中断(FSET I) 保存寄存器获得自动变量区 释放自动变量区 恢复寄存器 REITvoid func(void){}出口入口/E 允许多个中断支持可以通过下列方式指定中断向量表号#pragma INTERRUPT Vector number Function_nameOr#pragma INTERRUPT Function_name(vect= Vector number )使用编译选项–fmake_vector_table 自动生成变量中断表.#pragma INTERRUPT timerA0(vect=21)void timerA0(void){}.section __NC_rvector,ROMDATA .rvector 21,_timerA0asm function汇编语言可以被直接包含在C 程序中格式是asm(““). 例如: asm(“FSETI”); 使用“$$, $b, $@”来参考参数或自动变量.用户不需要考虑变量的存储类(storage class).asm(“mov.w R0,$@”, value );FB offsetSymbol Register-2[FB]_value R0对于变量:对于位字段:asm(“bset $b”, bit.b1 );Bit position,Symbol1,_bit可以在C 中编写长汇编源代码.int asmRoutine(int arg){return work;分配工作区供汇编代码使用.int work;将工作区的偏移(offset)设置在堆栈上asm (“在#pragma ASM 和#pragma ENDASM 之间编写长汇编源程序.#pragma ASMmov.w R0,work[FB]...#pragma ENDASM注意1 : 不要破坏asm 函数中的寄存器.int func(long arg){register int ret=0;#pragma ASMmov.l #00000000H,R2R0mov.l #_addr,A0mov.l #_addr2,A1mov.w _counter,R3rmpa.wmov.l R2R0,_result #pragma ENDASM………..return ret;}参考并修改寄存器保存寄存器恢复寄存器pushm R0,R2,R3,A0,A1popm R0,R2,R3,A0,A1注意2 : 不要写入会引起汇编源程序控制流混乱的转移(branch)指令。

ATmega16单片机中文技术资料

ATmega16单片机中文技术资料一、概述ATmega16是一款高性能、低功耗的8位微控制器,由Atmel公司推出。

它基于AVR增强型RISC结构,拥有丰富的外设资源和灵活的编程特性,广泛应用于工业控制、消费电子、通信设备等领域。

二、主要特性1. 内核:AVR增强型RISC结构,最高工作频率为16MHz。

2. 存储:16KB的程序存储器(Flash)、512B的EEPROM和1KB 的SRAM。

3. 外设接口:32个通用I/O口、8个通道的10位ADC、2个8位定时器/计数器、1个16位定时器/计数器、1个串行通信接口(USART)、1个串行外设接口(SPI)和1个两线接口(TWI)。

4. 工作电压:2.7V至5.5V,支持低功耗模式。

5. 封装:采用TQFP和PDIP封装,便于嵌入式系统设计。

三、引脚功能1. VCC:电源正极,接2.7V至5.5V电压。

2. GND:电源负极,接地。

3. PA0PA7:端口A,具有通用I/O、模拟输入和外围设备功能。

4. PB0PB7:端口B,具有通用I/O、JTAG接口和外围设备功能。

5. PC0PC7:端口C,具有通用I/O、模拟输入和外围设备功能。

6. PD0PD7:端口D,具有通用I/O和外围设备功能。

7. XTAL1/XTAL2:晶振输入/输出,用于外部晶振或陶瓷谐振器。

8. AVCC:模拟电源,为ADC和模拟电路提供电源。

10.RESET:复位输入,低电平有效。

四、编程与开发1. 编程语言:支持C语言和汇编语言编程。

2. 开发工具:可使用Atmel Studio、AVR Studio等集成开发环境进行程序编写、编译和调试。

3. 烧录方式:通过ISP、JTAG、HVPP等接口进行程序烧录。

本文档旨在为您提供ATmega16单片机的中文技术资料,帮助您更好地了解这款微控制器,为您的项目开发提供支持。

后续内容将详细介绍ATmega16的外设功能、编程方法及应用实例。

瑞萨单片机内部培训资料

0 1

10 100 1000 10000 100000

擦除/编程次数

擦除/编程次数

在擦除编程超过10K次后,擦除编程的时间会有明显变化, 但是擦除编程的特性及可靠性不会发生变化!

16 © 2010 Renesas Electronics Corporation. All rights reserved.

减少外部电路

✓ 高速、高精度内部振荡器 (外接晶振引脚可用作输入端口) ✓ 内部上电复位电路 ✓ 低电压检测电路 ✓ 数据闪存(可代替E2PROM)

[现有产品]

复位 电路

VCC RESET

GND

Vref MODE

EEPROM 调试 接口

串行写入器接口

[R8C/Tiny]

复位 电路

VCC

RESET POR / LVD

R8C/Tiny系列单片机的主要优点

代码效率高

强大的指令系统 ——总共89条指令 很多 单周期 指令(且使用频率非常高)

20 个(MOV, ADD, SUB等)

快速、 高效的 代码

8种寻址模式

4种单周期寻址模式 寄存器到寄存器

高效、优化的C编译器

寄存器到存储器

立即数到寄存器 立即数到存储器

(使用该功能时,主时钟频率须大于2MHz)

XIN 振荡器正常工作

内部振荡器

CPU

XIN

XIN 振荡器意外停止

内部振荡器

CPU

XIN

CPU时钟切换到内部振荡器

内部振荡器

CPU

XIN

10 © 2010 Renesas Electronics Corporation. All rights reserved.

瑞萨 r8c 2g群 硬件手册

RCJ09B0054-0100瑞萨单片机M16C 族/R8C/Tiny 系列本资料所记载的内容,均为本资料发行时的信息,瑞萨科技对于本资料所记载的产品或者规格可能会作改动,恕不另行通知。

请通过瑞萨科技的主页确认发布的最新信息。

Notes regarding these materialsNotes regarding these materials1. This document is provided for reference purposes only so that Renesas customers may select the appropriateRenesas products for their use. Renesas neither makes warranties or representations with respect to theaccuracy or completeness of the information contained in this document nor grants any license to anyintellectual property rights or any other rights of Renesas or any third party with respect to the information inthis document.2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arisingout of the use of any information in this document, including, but not limited to, product data, diagrams, charts,programs, algorithms, and application circuit examples.3. You should not use the products or the technology described in this document for the purpose of militaryapplications such as the development of weapons of mass destruction or for the purpose of any other militaryuse. When exporting the products or technology described herein, you should follow the applicable exportcontrol laws and regulations, and procedures required by such laws and regulations.4. All information included in this document such as product data, diagrams, charts, programs, algorithms, andapplication circuit examples, is current as of the date this document is issued. Such information, however, issubject to change without any prior notice. Before purchasing or using any Renesas products listed in thisdocument, please confirm the latest product information with a Renesas sales office. Also, please pay regularand careful attention to additional and different information to be disclosed by Renesas such as that disclosedthrough our website. ( )5. Renesas has used reasonable care in compiling the information included in this document, but Renesasassumes no liability whatsoever for any damages incurred as a result of errors or omissions in the informationincluded in this document.6. When using or otherwise relying on the information in this document, you should evaluate the information inlight of the total system before deciding about the applicability of such information to the intended application.Renesas makes no representations, warranties or guaranties regarding the suitability of its products for anyparticular application and specifically disclaims any liability arising out of the application and use of theinformation in this document or Renesas products.7. With the exception of products specified by Renesas as suitable for automobile applications, Renesasproducts are not designed, manufactured or tested for applications or otherwise in systems the failure ormalfunction of which may cause a direct threat to human life or create a risk of human injury or which requireespecially high quality and reliability such as safety systems, or equipment or systems for transportation andtraffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communicationtransmission. If you are considering the use of our products for such purposes, please contact a Renesassales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:(1) artificial life support devices or systems(2) surgical implantations(3) healthcare intervention (e.g., excision, administration of medication, etc.)(4) any other purposes that pose a direct threat to human lifeRenesas shall have no liability for damages arising out of the uses set forth in the above and purchasers whoelect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless RenesasTechnology Corp., its affiliated companies and their officers, directors, and employees against any and alldamages arising out of such applications.9. You should use the products described herein within the range specified by Renesas, especially with respectto the maximum rating, operating supply voltage range, movement power voltage range, heat radiationcharacteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions ordamages arising out of the use of Renesas products beyond such specified ranges.10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specificcharacteristics such as the occurrence of failure at a certain rate and malfunctions under certain useconditions. Please be sure to implement safety measures to guard against the possibility of physical injury, andinjury or damage caused by fire in the event of the failure of a Renesas product, such as safety design forhardware and software including but not limited to redundancy, fire control and malfunction prevention,appropriate treatment for aging degradation or any other applicable measures. Among others, since theevaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products orsystem manufactured by you.11. In case Renesas products listed in this document are detached from the products to which the Renesasproducts are attached or affixed, the risk of accident such as swallowing by infants and small children is veryhigh. You should implement safety measures so that Renesas products may not be easily detached from yourproducts. Renesas shall have no liability for damages arising out of such detachment.12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior writtenapproval from Renesas.13. Please contact a Renesas sales office if you have any questions regarding the information contained in thisdocument, Renesas semiconductor products, or if you have any other inquiries.关于利用本资料时的注意事项 1. 䌘 Ўњ䅽⫼ ḍ ⫼䗨䗝 䗖ⱘ ѻ ⱘ 㗗䌘 ˈ Ѣ 䌘 Ё 䆄䕑ⱘ ˈ 䴲ⴔ 㗙ϝ㗙ⱘⶹ䆚ѻ Ҫ 䆕 䖯㸠ⱘ 䇎DŽ2. Ѣ Փ⫼ 䌘 䆄䕑ⱘѻ ǃ ǃ㸼ǃ ǃㅫ⊩ Ҫ ⫼⬉䏃՟㗠 䍋ⱘ 㗙 ϝ㗙ⱘⶹ䆚ѻ Ҫ 䗴 ⢃ˈ ϡ ӏԩ䋷ӏDŽ3. ϡ㛑 䌘 䆄䕑ⱘѻ ⫼Ѣ 㾘⸈ ℺ ⱘ ㄝⳂⱘǃ џⳂⱘ Ҫⱘ 䳔⫼䗨 䴶DŽˈ 乏䙉 ⱘlj ∛ 䌌 ⊩NJ Ҫ ⱘⳌ ⊩Ҹ 㸠䖭ѯ⊩ҸЁ㾘 ⱘ 㽕㓁DŽ4. 䌘 䆄䕑ⱘѻ ǃ ǃ㸼ǃ ǃㅫ⊩ҹ Ҫ ⫼⬉䏃՟ㄝ Ў 䌘 㸠 ⱘ ˈ㛑 џ 䗮ⶹⱘ ϟˈ 䌘 䆄䕑ⱘѻ 㗙ѻ 㾘Ḑ䖯㸠 DŽ ҹ 䌁ф Փ⫼ⱘ ԧѻ П ˈ䇋џ ⱘ㧹Ϯに ⹂䅸 ⱘ 㒣 ⬭ 䗮䖛 Џ义()ㄝ ⱘ DŽ5. Ѣ 䌘 Ё 䆄䕑ⱘ ˈ Ӏ 䆕 ⠜ ⱘ㊒⹂ ˈԚϡ 䌘 ⱘ 䗄ϡ 㗠㟈Փ乒䙁 ㄝⱘӏԩⳌ 䋷ӏDŽ6. Փ⫼ 䌘 䆄䕑ⱘѻ ǃ ǃ㸼ㄝ ⼎ⱘ ǃ ǃㅫ⊩ Ҫ ⫼⬉䏃՟ ˈϡҙ㽕Փ⫼ⱘ 䖯㸠 ⣀䆘Ӌˈ䖬㽕 Ͼ㋏㒳䖯㸠 ⱘ䆘ӋDŽ䇋乒 㞾㸠䋳䋷ˈ䖯㸠 䗖⫼ⱘ DŽѢ 䗖⫼ϡ䋳ӏԩ䋷ӏDŽ7. 䌘 Ё 䆄䕑ⱘѻ 䴲䩜 ϛϔ ⦄ 䱰 䫭䇃䖤㸠 Ӯ 㚕 Ҏⱘ⫳ 㒭Ҏԧ ⱘ ǃ㋏㒳 ⾡ 㺙㕂 㗙䖤䕧Ѹ䗮⫼ⱘǃ ⭫ǃ➗⚻ ǃ㟾 ẄǃḌ㛑ǃ⍋ Ё㒻⫼ⱘ ㋏㒳ㄝ㗠䆒䅵 䗴ⱘ ⡍ Ѣ 䋼 䴴 㽕∖ 催ⱘ ㋏㒳ㄝ˄ ⫼Ѣ≑䔺 䴶ⱘѻ ⫼Ѣ≑䔺 䰸 ˅DŽ 㽕⫼ѢϞ䗄ⱘⳂⱘˈ䇋 џ ⱘ㧹Ϯに 䆶DŽ ˈ Ѣ⫼ѢϞ䗄Ⳃⱘ㗠䗴 ⱘ ㄝˈ ὖϡ䋳䋷DŽ8. 䰸Ϟ䗄 乍 ˈϡ㛑 䌘 Ё䆄䕑ⱘѻ ⫼Ѣҹϟ⫼䗨DŽ ⫼Ѣҹϟ⫼䗨㗠䗴 ⱘ ˈὖϡ䋳䋷DŽ1˅⫳ 㓈 㺙㕂DŽ2˅ỡ ѢҎԧՓ⫼ⱘ㺙㕂DŽ3˅⫼Ѣ⊏⭫˄ 䰸 䚼ǃ㒭㥃ㄝ˅ⱘ㺙㕂DŽ4˅ ҪⳈ Ҏⱘ⫳ ⱘ㺙㕂DŽ9. Փ⫼ 䌘 䆄䕑ⱘѻ ˈ Ѣ 乱 ǃ ⬉⑤⬉ ⱘ㣗 ǃ ⛁⡍ ǃ 㺙 ӊ Ҫ ӊ䇋㾘 ⱘ 䆕㣗 Փ⫼DŽ 䍙 њ 㾘 ⱘ 䆕㣗 Փ⫼ ˈ Ѣ⬅ℸ㗠䗴 ⱘ 䱰 ⦄ⱘџ ˈ ϡ ӏԩ䋷ӏDŽ10. ϔⳈ㟈 Ѣ 催ѻ ⱘ䋼䞣 䴴 ˈԚϔ㠀 䇈ˈ ԧѻ Ӯҹϔ ⱘὖ⥛ ⫳ 䱰ǃ 㗙⬅ѢՓ⫼ ӊϡ 㗠 ⦄䫭䇃䖤㸠ㄝDŽЎњ䙓 ⱘѻ ⫳ 䱰 㗙䫭䇃䖤㸠㗠 㟈Ҏ䑿џ ☿♒䗴 ⼒Ӯ ⱘ ˈ 㛑㞾㸠䋳䋷䖯㸠 ԭ䆒䅵ǃ䞛 ⚻ ㄪ 䖯㸠䰆ℶ䫭䇃䖤㸠ㄝⱘ 䆒䅵˄ ⹀ӊ 䕃ӊϸ 䴶ⱘ䆒䅵˅ҹ 㗕 ⧚ㄝˈ䖭 Ў ㋏㒳ⱘ 䆕DŽ⡍ ⠛ ⱘ䕃ӊˈ⬅Ѣ ⣀䖯㸠偠䆕 䲒ˈ ҹ㽕∖ 乒 䗴ⱘ 㒜ⱘ ㋏㒳Ϟ䖯㸠 Ẕ偠 DŽ11. 䌘 䆄䕑ⱘѻ Ң 䕑ԧ䆒 Ϟ ϟˈ 㛑䗴 䇃 ⱘ 䰽DŽ乒 ѻ 㺙乒 ⱘ䆒 Ϟ ˈ䇋乒 㞾㸠䋳䋷 ѻ 䆒㕂Ўϡ 㨑ⱘ 䆒䅵DŽ Ң乒 ⱘ䆒 Ϟ 㨑㗠䗴 џ ˈ ϡ ӏԩ䋷ӏDŽ12. ⱘџ к䴶䅸 ˈϡ 䌘 ⱘϔ䚼 㗙 䚼䕀䕑 㗙 DŽ13. 䳔㽕њ㾷 Ѣ 䌘 ⱘ䆺㒚 ˈ 㗙 Ҫ ⱘ䯂乬ˈ䇋 ⱘ㧹Ϯに 䆶DŽѢ ⫼ 䌘 ⱘ⊼ џ乍⊼ 㗗䆥 ˈ 义 䕑㣅 ⠜“Cautions” ℷ DŽ产品使用时的注意事项此处,对适用于所有单片机产品的“使用注意事项”进行了说明。

小电流接地系统单相接地保护装置

小电流接地系统单相接地保护装置中心议题:∙接地系统单相接地保护装置设计解决方案:∙采用单片机和DSP双CPU作为小电流接地系统单相接地故障检测的核心∙采用6片AD转换芯片,实现了36路信号同步采集∙采用LCD显示模块实现了很好的人机交互随着配电网的发展,小电流接地系统运行的可靠性越来越受到重视,针对小电流接地系统的各种保护装置也得到飞速发展。

目前,主要的保护装置都是由工控机和单片机实现的,而单片机在实现保护方面有体积小、成本低、安装方便、运行可靠等优点。

以前的很多产品都是利用接地故障时的稳态信息。

但是当小电流接地系统在发生单相接地故障时,稳态零序电流幅值较小,而暂态零序电流幅值较大,故基于暂态零序电流的故障选线方法更可靠。

配电网的线路繁多,结构复杂,采集的数据包括由TV来的8路电压量(两段母线的三相电压和零序电压)以及由零序TA来的各路零序电流。

对于这样多的数据采集、分析计算,并上传,单一的单片机是难以胜任的。

数字信号处理器(DSP)由于具有处理速度快,适合数字信号处理的特点,可以很好地解决数据采集和处理问题。

考虑到装置的控制功能,本装置采用单片机和DSP双CPU结构为核心。

小波分析在时频两域都具有良好的局部化性能,能对不同频率成分采用逐渐精细的采样步长,聚焦到信号的任意细节,这一特性非常适合分析电力系统中的暂态信号。

小波分析在信号的分解与重构、特征提取、信噪分离等方面的优点决定了它在电力系统谐波分析、奇异点的检测与消噪、设备的状态监测与故障诊断、继电保护、输电线路故障定位及负荷预测等领域都具有广阔的应用前景。

1装置的研制1.1总体方案设计硬件平台是软件算法的运行载体,是实现准确、高效选线的保障。

本文设计的选线装置采用双CPU。

即"DSP+单片机"的处理机构。

DSP作为运算CPU,负责信号采集、选线计算部分;单片机作为管理CPU,主要负责人机交互部分。

DSP处理器由于内部采用哈佛总线结构,指令是流水线操作,以及独立的硬件乘法器结构等,非常适合进行数字信号处理,进行实时的数据分析和监控。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

瑞萨电子M16C族系列单片机

致芯科技最具实力的芯片解密、IC解密、单片机解密等解密服务机构,致芯科技拥有多年的解密服务经验和超高水平的解密技术,一直从客户利益出发,为每位客户提供最科学最合理最低成本的解密方案与解密服务,深受客户的信赖与喜爱。

瑞萨电子M16C平台:M16C族是提供32/16位CISC单片机的强大平台,此平台具有高效率ROM编码、大范围EMI/EMS噪声对策、超低功耗、实际应用中的高速处理和各种完善的外围设备等特点。

该族为单体结构,具有管脚兼容性和外围功能兼容性,提供从低档到高档的各种芯片,应用领域广泛。

另外,低成本开发环境和程序修正功能将帮助用户缩短产品开发时间,大幅度降低整个系统的开发成本。

M16C族由以下系列构成:R32C/100系列、M32C/80系列、M16C/60系列、M16C/30系列、M16C/Tiny系列、M16C/20系列、M16C/10系列和R8C/Tiny系列。

M32C/84系列

M30840MC-XXXFP,M30840MC-XXXGP,M30840SFP ,M30840SGP,M30842MC-XXXGP,M3 0842SGP

M30843FHFP,M30843FHGP,M30843FJFP,M30843FJGP,M30843FWGP,M30843MW-XXXF P,M30843MW-XXXGP

M30845FHGP,M30845FJGP,M30845FWGP,M30845MW-XXXGP,M30840MCT-XXXGP,M308 42MCT-XXXGP

M30843FJTGP,M30843FJTGP,M30843MGT-XXXGP,M30843MGU-XXXGP,M30843MHT-XX XGP

M30843MHU-XXXGP,M30843MWT-XXXGP,M30843MWU-XXXGP,M30845FHUGP

M32C/85系列

M30853FHGP,M30853FJFP,M30853FJGP,M30853FWFP,M30853FWGP

M30853MW-XXXFP,M30853MW-XXXGP,M30855FHGP,M30855FJGP,M30855FWGP,M3085 5MW-XXXGP

M30853FHTGP,M30853FHUGP,M30853FJTGP,M30853FJUGP,M30853FWTGP,M30853MG T-XXXGP

M30853MGU-XXXGP,M30853MHT-XXXGPM30853MHU-XXXGPM30853MWT-XXXGP,M30853 MWU-XXXGP。