实验一 一位二进制全减器设计

实验一1位二进制全减器设计

实验一 1位二进制全减器设计实验一:1位二进制全减器设计一、实验目的本实验旨在通过硬件设计和编程,实现一个1位二进制全减器的设计。

通过本实验,希望学生能够深入理解二进制数的减法运算规则,掌握硬件电路的基本设计和调试方法,提高实践能力和编程技能。

二、实验原理二进制全减器是一种实现两个二进制数相减的逻辑电路。

在一个二进制全减器中,我们需要考虑两个输入位(被减数和减数)以及一个借位输入(来自低位的借位输出)。

根据这些输入,二进制全减器会生成一个输出位(差)和一个借位输出(向低位的借位)。

三、实验步骤1.确定设计方案:根据实验要求,选择合适的硬件设计和编程语言。

本实验中,我们采用Verilog语言进行编程,并使用FPGA(现场可编程门阵列)来实现硬件电路。

2.编写代码:根据二进制全减器的设计要求,编写Verilog代码。

代码应包括模块定义、输入输出端口声明、逻辑设计和时序控制等部分。

3.编译与仿真:将编写的Verilog代码进行编译,生成可被FPGA识别的二进制文件。

然后,使用仿真工具进行功能仿真,验证设计的正确性。

4.硬件调试:将生成的二进制文件下载到FPGA开发板上,进行硬件调试。

通过观察硬件电路的输出结果,验证全减器功能的正确性。

5.性能分析:对设计的全减器进行性能评估,包括运算速度、功耗、资源利用率等指标。

通过对比不同设计方案,分析优劣并提出改进意见。

四、实验结果与分析1.实验结果:通过本次实验,我们成功地设计并实现了一个1位二进制全减器。

在功能仿真和硬件调试中,均验证了该全减器的正确性。

2.结果分析:在设计过程中,我们充分考虑了电路的简洁性和高效性。

在满足设计要求的前提下,尽量减少了逻辑门的数量和复杂度。

这使得我们的全减器在资源利用率、运算速度和功耗等方面均表现出较好的性能。

五、结论与展望通过本次实验,我们成功地设计并实现了一个1位二进制全减器。

该全减器在功能仿真和硬件调试中均表现出良好的性能。

一位全减器word版本

实验一 1位二进制全减器设计一、实验目的1.熟悉Quartes II集成开发软件的使用;2.初步熟悉PH-1V型实验装置的使用;3 . 学习用原理图输入法和文本输入法进行简单的数字电路设计,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求1.采用原理图输入法和文本输入法分别实现,分层设计,底层由半减器(也用原理图输入法)和逻辑门组成;2.建立波形文件,并进行系统仿真,用软件验证设计结果;3. 在仿真正确的情况下,对1位二进制半加/减器分别下载到实验箱中做硬件测试三、实验原理及设计思路根据一位二进制全减器的工作原理,可得其真值表为(如下:cin表示低位向本位借位。

cout 表示本位向高位借位)ain bin cin cout sum0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 1 01 0 0 0 11 0 1 0 01 1 0 0 01 1 1 1 1由EDA教程中全加器的顶层设计描述及半加器调用可类比到全减器的设计,可由先对半减器进行描述,然后进行两次调用。

半减器的工作时的逻辑表达式为:so=a XOR b ;co=(NOT a)AND b四、实验程序(程序来源:EDA技术实验教程)LIBRARY IEEE ; ——或门逻辑描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY or2a ISPORT (a, b :IN STD_LOGIC;c : OUT STD_LOGIC );END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b ;END ARCHITECTURE one;LIBRARY IEEE; ——半减器描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_suber ISPORT (a, b : IN STD_LOGIC;co, so : OUT STD_LOGIC);END ENTITY h_suber;ARCHITECTURE fh1 OF h_suber isBEGINso <= a xor b ;co <= (not a )AND b ;END ARCHITECTURE fh1;LIBRARY IEEE; ——1位二进制全减器顶层设计描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_suber ISPORT (ain,bin,cin : IN STD_LOGIC;cout,sum : OUT STD_LOGIC );END ENTITY f_suber;ARCHITECTURE fd1 OF f_suber ISCOMPONENT h_suber ——调用半减器声明语句PORT ( a,b : IN STD_LOGIC;co,so : OUT STD_LOGIC);END COMPONENT ;COMPONENT or2a ——调用或门声明语句PORT (a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f : STD_LOGIC; ——定义3个信号作为内部的连接线BEGINu1 : h_suber PORT MAP(a=>ain,b=>bin,co=>d,so=>e); ——例化语句u2 : h_suber PORT MAP(a=>e, b=>cin,co=>f,so=>sum);u3 : or2a PORT MAP(a=>d, b=>f,c=>cout);END ARCHITECTURE fd1 ;五、实验步骤:1.打开Quartes II软件,建立工程文件,注意工程名要与实体名一致:2、打开QuartusII,选择菜单File->New->VHDL.File,建立vhdl文件,将以上程序输入并进行编译;3、建立波形文件,并进行系统仿真,注意设置仿真结束时间以及添加结点;4、输入信号波形Tools->Options->Waveform Editor,进行功能仿真Tools->Simulator Tools,在Simulator Mode选择Functional,仿真表生成后点击Start开始仿真,完成后点击Report结果如下图所示;5、引脚锁定,及设置流程对各管脚进行分配,将ain分配给53,bin分配给54,cin分配给55。

整理实验一-一位二进制全加器设计实验

整理人 尼克 实验一一位二进制全加器设计实验目录实验一Protel DXP 2004认识实验 (1)实验二两级阻容耦合三极管放大电路原理图设计 (1)实验三原理图元件库建立与调用 (3)实验四两级阻容耦合三极管放大电路PCB图设计 (5)实验五集成电路的逻辑功能测试 (7)实验六组合逻辑电路分析与设计 (12)实验七Quartus II 的使用 (17)实验八组合逻辑器件设计 (17)实验九组合电路设计 (25)实验一 Protel DXP 2004 认识实验一、实验目的1.掌握Prot e l DXP 2004 的安装、启动和关闭。

2.了解Protel DXP 2004 主窗口的组成和各部分的作用。

3.掌握Prot e l DXP 2004 工程和文件的新建、保存、打开。

二、实验内容与步骤1、Protel_DXP_2004 的安装(1)用虚拟光驱软件打开Protel_DXP_2004.iso 文件(2)运行setup\Setup.exe 文件,安装Protel DXP 2004(3) 运行破解程序后,点击“导入模版”,先导入一个ini文件模版(如果要生成单机版的License选择Unified Nexar-Protel License.ini;要生成网络版的License选择Unified Nexar-Protel Network License.ini),然后修改里面的参数:TransactorName=Your Name(将“Your Name”替换为你想要注册的用户名);SerialNumber=0000000(如果你只有一台计算机,那么这个可以不用修改,如果有两台以上的计算机且连成局域网,那么请保证每个License文件中的SerialNumber=为不同的值。

修改完成后点击“生成协议文件”,任意输入一个文件名(文件后缀为.alf)保存,程序会在相应目录中生成1个License文件。

点击“替换密钥”,选取DXP.exe (在DXP 2004安装目录里,默认路径为C:\Program Files\Altium2004\),程序会自动替换文件中的公开密钥。

实验一:一位二进制全减器设计

南昌大学实验报告学生姓名:刘志强学号: 6100409222 专业班级:电子091班实验类型:验证□综合□设计■创新□实验日期:实验成绩:实验一一位二进制全减器设计一、实验目的(1)掌握QuartusII的VHDL原理图设计和文本设计全过程;(2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求(1)设计一个二进制全减器,用分层设计方法,顶层为全减器,底层为半减器和逻辑门组成;(2)进行波形仿真,并分析仿真波形图;(3)下载测试全减法器是否正确。

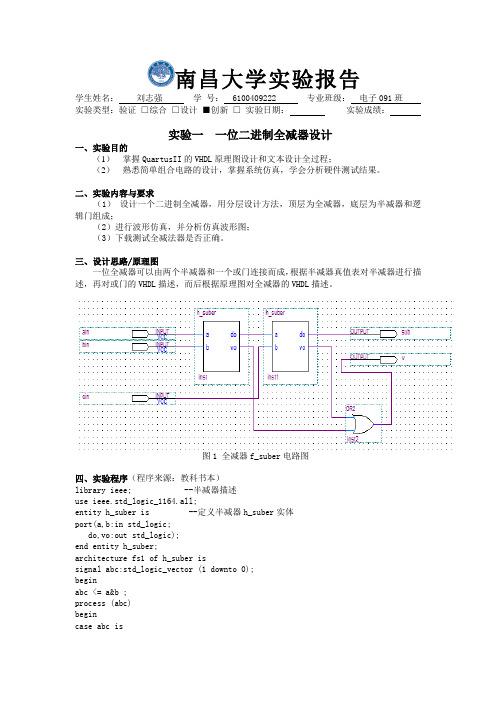

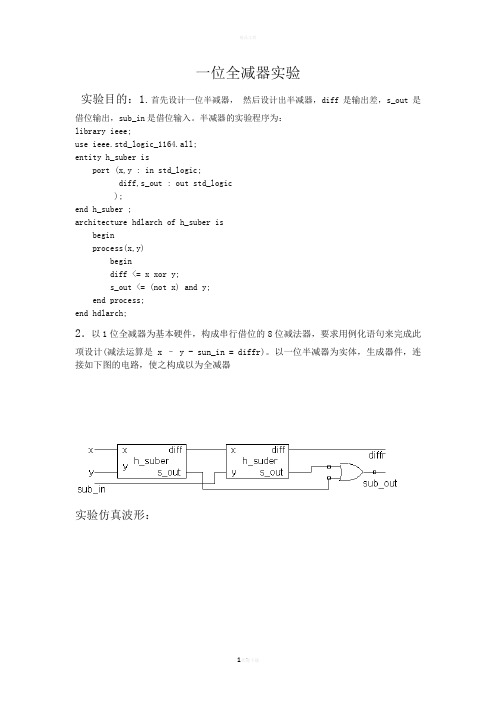

三、设计思路/原理图一位全减器可以由两个半减器和一个或门连接而成,根据半减器真值表对半减器进行描述,再对或门的VHDL描述,而后根据原理图对全减器的VHDL描述。

图1 全减器f_suber电路图四、实验程序(程序来源:教科书本)library ieee; --半减器描述use ieee.std_logic_1164.all;entity h_suber is --定义半减器h_suber实体port(a,b:in std_logic;do,vo:out std_logic);end entity h_suber;architecture fs1 of h_suber issignal abc:std_logic_vector (1 downto 0);beginabc <= a&b ;process (abc)begincase abc iswhen "00" => do<='0';vo<='0';when "01" => do<='1';vo<='1';when "10" => do<='1';vo<='0';when "11" => do<='0';vo<='0';when others => null;end case;end process;end architecture fs1;library ieee; --一位二进制全减器顶层设计描述use ieee.std_logic_1164.all;entity f_suber is --定义全减器f_suber实体port (ain,bin,cin:in std_logic;v,sub:out std_logic);end entity f_suber;architecture fs of f_suber iscomponent h_suber ---调用半减器声明语句port (a,b:in std_logic;do,vo:out std_logic);end component;component or2a --调用或逻辑门声明语句port (m,n:in std_logic;h:out std_logic);end component;signal e,f,g:std_logic; ---定义3个信号作为内部的连接线beginu1:h_suber port map(a=>ain,b=>bin,do=>e,vo=>f); ---例化语句u2:h_suber port map(a=>e,b=>cin,do=>sub,vo=>g);u3:or2a port map(m=>g,n=>f,h=>v);end architecture fs;五、实验步骤1. 利用Quartus II 7.2建立工程在file中打开【】→【】→在【】中选择存放的目录→【】f_suber要与顶层文件中entity f_suber相同→点击next→点击next→选择芯片→next完成;再在file下面点【】→【】→点击ok→编写程序→编译并保存在f_suber文件中(改动程序后,再保存,再编译)→管脚【】→【】→而后对芯片设置,即打开device→点【】→点【】与【】→选如【】与【】→选芯片→确定ok ;重新编译→点下载,后选【】硬件有“JTAG【】”和“ASP【】手动添加以扩展名为.pof的文件【】”两个接口其一(要看硬件接口),选中【】”→添加【】中的驱动程序→【】→点【】开始下载。

一位二进制全减器逻辑电路

一位二进制全减器逻辑电路1. 什么是二进制全减器?嘿,朋友们,今天我们要聊聊一个很酷的东西——二进制全减器。

这听起来可能有点儿复杂,但其实就是个简单的电路,可以帮助我们进行二进制的减法运算。

你知道的,就像你平时在计算机上做的那种,只不过它在背后默默地工作,像个低调的超级英雄。

全减器主要用于计算机电路里,特别是在处理器的算术逻辑单元(ALU)中,咱们可以把它想象成一位默默奉献的“计算小能手”。

说到减法,你可能会想起小学时的数学题:3减2等于多少?全减器也一样,只不过它的数字是二进制的。

咱们的全减器能处理两位二进制数的减法,哦,对了,二进制数就是0和1,简简单单。

假设我们要算1减0,嘿,这很容易,对吧?结果就是1。

但如果是0减1,那可就麻烦了,得借位。

不过,没关系,全减器就是来解决这些麻烦的。

2. 二进制全减器的工作原理2.1 输入与输出那么,全减器到底是怎么工作的呢?简单来说,它有三个输入和两个输出。

输入分别是被减数、减数和借位(也就是之前的那位借来的)。

输出呢,是差和新的借位。

就像你在做减法时,偶尔会碰到要借位的情况一样,这个小家伙也要处理借位问题。

想象一下,输入就像是在学校里,大家都在排队等着上课。

被减数就是那个大个子,减数是个小个子,借位就是那个总是要偷懒的朋友。

他们一起进入全减器,然后全减器就开始忙活了。

通过一些逻辑门电路,比如与门、或门和非门,全减器就能得出答案,就像老师把他们的分数都算出来一样。

2.2 逻辑门的神奇听到逻辑门,可能有人会觉得这就是一堆复杂的东西,但其实它们就像小小的开关。

与门只有在两个开关都打开时才会“点亮”;或门则只要有一个开关打开就行;非门就是那种总是跟别人相反的家伙。

通过这些门的组合,全减器能够处理不同的输入,最终得出正确的差和借位。

说起来,逻辑门的运用就像我们日常生活中的决策。

有时候你得综合考虑不同的因素才能做出最佳选择,比如晚上吃什么,既要看口味,也要考虑健康嘛。

一位二进制全加减器的设计

一位二进制全加减器的设计在咱们的生活中,数字无处不在,没错,不管是买东西还是算账,数字就是我们的好伙伴。

说到数字,大家一定听说过二进制。

二进制就像是数字的二重奏,只有0和1这两个小家伙,真是简单又有趣。

不过,今天我们不聊二进制的故事,而是聊聊它的一个超级英雄,二进制全加减器。

这家伙可是个了不起的角色,能够让我们轻松进行加法和减法,简直就像是厨房里的万能调料,随时随地为你解闷。

想象一下,你正在和朋友玩游戏,突然间需要计算得分,这时候二进制全加减器就像那救星般闪亮登场。

咱们先来说说加法吧。

二进制的加法其实跟咱们平常的加法差不多,不过就是多了点小规则。

比如说,0加0当然是0,0加1或者1加0就是1,1加1则会产生进位,变成0再加1,这个时候就像是变魔术一样,瞬间升华了。

把这简单的加法放在一起,嘿,整个过程简直就像是舞蹈,轻松而优雅。

再来看看减法。

哦,减法在二进制里也是大有可为。

想象一下,你手里有一块大蛋糕,想给朋友分,但是蛋糕不够,怎么办?这时候就需要用到借位的技巧。

二进制减法就像是抢夺蛋糕的小朋友,借位就是从旁边的小朋友那里借来一口,然后再继续分蛋糕。

这样看似复杂,但实际上只要理解规则,嘿,就能轻松搞定。

那好,咱们再深入一点,聊聊这个全加减器是怎么工作的。

它就像一个聪明的管家,负责所有的数字进出。

内部的结构就像一座精密的机器,采用逻辑门电路,真是科技的结晶。

这个小家伙有两部分,一部分是加法器,另一部分是减法器,它们就像两位默契的舞者,在舞台上完美配合。

每当有输入数字的时候,它们立刻就开始工作,快速而高效,仿佛时间都为它们停驻。

听到这里,大家可能会想,二进制全加减器有什么用呢?别急,咱们就来聊聊它的应用。

无论是计算机还是电子设备,都离不开这位全加减器。

想想看,咱们每天都在用手机,玩游戏,浏览网页,这些背后可都是二进制全加减器在默默奉献。

它就像一位无名英雄,虽然不显山露水,却是整个系统运作的基石。

说到这里,可能有人会觉得,哎呀,二进制这玩意儿真复杂。

VHDL之一位全减器

一位全减器实验实验目的:1.首先设计一位半减器,然后设计出半减器,diff是输出差,s_out是借位输出,sub_in是借位输入。

半减器的实验程序为:library ieee;use ieee.std_logic_1164.all;entity h_suber isport (x,y : in std_logic;diff,s_out : out std_logic);end h_suber ;architecture hdlarch of h_suber isbeginprocess(x,y)begindiff <= x xor y;s_out <= (not x) and y;end process;end hdlarch;2.以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是 x – y - sun_in = diffr)。

以一位半减器为实体,生成器件,连接如下图的电路,使之构成以为全减器实验仿真波形:四位全减器实验1.实验原理:(1)利用前面设计的全减器(一位全减器)生成元件;(2)建立新的原理图,完成4位全减器的设计;(3)进行波形仿真验证;2.实验仿真波形图:7段数码显示译码器设计1、实验目的:学习7段数码显示译码器设计、多层次设计方法、和总线数据输入方式的仿真,并进行电路板下载验证。

2、实验原理:7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA 或CPLD中实现。

本项实验很容易实现这一目的。

例2作为7段BCD码译码器的设计,输出信号LED7S的7位分别接如实验图2数码管的7个段,高位在左,低位在右。

例如当LED7S 输出为 "1101101" 时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,于是数码管显示“5”。

电子技术基础实验报告-全加减器设计

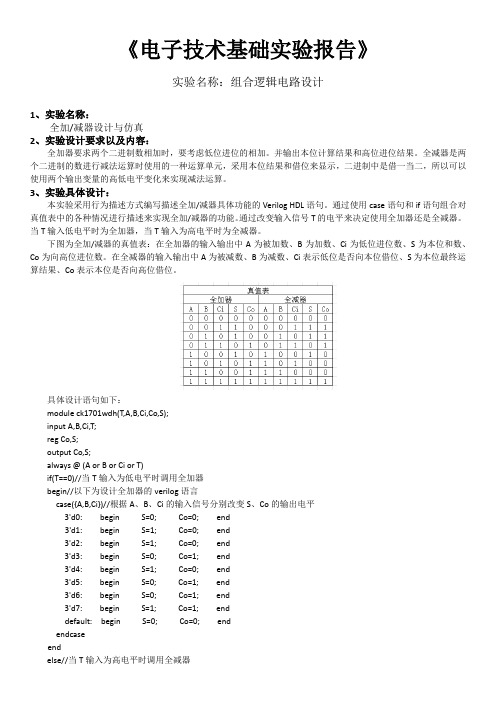

《电子技术基础实验报告》实验名称:组合逻辑电路设计1、实验名称:全加/减器设计与仿真2、实验设计要求以及内容:全加器要求两个二进制数相加时,要考虑低位进位的相加。

并输出本位计算结果和高位进位结果。

全减器是两个二进制的数进行减法运算时使用的一种运算单元,采用本位结果和借位来显示,二进制中是借一当二,所以可以使用两个输出变量的高低电平变化来实现减法运算。

3、实验具体设计:本实验采用行为描述方式编写描述全加/减器具体功能的Verilog HDL语句。

通过使用case语句和if语句组合对真值表中的各种情况进行描述来实现全加/减器的功能。

通过改变输入信号T的电平来决定使用全加器还是全减器。

当T输入低电平时为全加器,当T输入为高电平时为全减器。

下图为全加/减器的真值表:在全加器的输入输出中A为被加数、B为加数、Ci为低位进位数、S为本位和数、Co为向高位进位数。

在全减器的输入输出中A为被减数、B为减数、Ci表示低位是否向本位借位、S为本位最终运算结果、Co表示本位是否向高位借位。

具体设计语句如下:module ck1701wdh(T,A,B,Ci,Co,S);input A,B,Ci,T;reg Co,S;output Co,S;always @ (A or B or Ci or T)if(T==0)//当T输入为低电平时调用全加器begin//以下为设计全加器的verilog语言case({A,B,Ci})//根据A、B、Ci的输入信号分别改变S、Co的输出电平3'd0: begin S=0; Co=0; end3'd1: begin S=1; Co=0; end3'd2: begin S=1; Co=0; end3'd3: begin S=0; Co=1; end3'd4: begin S=1; Co=0; end3'd5: begin S=0; Co=1; end3'd6: begin S=0; Co=1; end3'd7: begin S=1; Co=1; enddefault: begin S=0; Co=0; endendcaseendelse//当T输入为高电平时调用全减器begin//以下为设计全减器的verilog语言case({A,B,Ci})//根据A、B、Ci的输入信号分别改变S、Co的输出电平3'd0: begin S=0; Co=0; end3'd1: begin S=1; Co=1; end3'd2: begin S=1; Co=1; end3'd3: begin S=0; Co=1; end3'd4: begin S=1; Co=0; end3'd5: begin S=0; Co=0; end3'd6: begin S=0; Co=0; end3'd7: begin S=1; Co=1; enddefault: begin S=0; Co=0; endendcaseendendmodule4、输入输出设计:(按键,数码管,发光管等说明)管脚分配如下(格式:输入/输出通道名:对应引脚名→开发板上对应开关名):信号输入Input: A:PIN_J6→SW[0], B:PIN_H5→ SW[1], Ci:PIN_H6→ SW[2], T:PIN_G4→ SW[3].信号输出Output: S:PIN_J2→LEDG[1], Co:PIN_J1→ LEDG[0].SW[]为拨动开关,LEDG[]为绿色发光二极管。

实验一 一位二进制全减器的设计

实验一、一位二进制全减器的设计一、实验目的:(1)掌握Quartus II 的VHDL 文本设计的全过程;(2)熟练和掌握EDA设计流程;熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果。

(3)学习PH-1V型实验装置上发光二极管和按键的使用方法。

二、实验内容与要求:(1)用文本方法实现半减器,再利用半减器完成全减器的设计,熟悉层次设计概念;(2)给出此项设计的仿真波形;(3)选择实验电路NO.1验证, 用发光管指示显示结果。

三、设计原理:全减器可以有2个半减器和1个或门组成。

(1)半减器真值表:Sub_out表示本位)四、实验程序:(1) 实验程序(程序来源:)(2)对全减器进行原理图编辑:五、实验步骤:1.建立工作库文件夹和编辑设计文件(1)在D盘下建立一个文件夹保存工程文件;(2)打开QuartusII,建立新的VHDL文件,再打开的页面下输入程序。

2.编译过程(1)输入完程序之后逐个编译(2)逐个编译无错之后进行全程编译3.系统仿真(1)建立新的波形激励文件(2)在波形编辑器窗口添加节点(3)通过Edit->End Time 来设定仿真结束时间(4)点击save保存(5)通过Tools下的Simulator Tools项进行仿真,然后观察输出波形。

4.引脚锁定(1)通过Assignment->Assignment Editor->Pin查找到所有的引脚(2)选择各个输入输出信号来锁定到不同引脚,进行全编译。

5.编程下载(1)选择Tools->Programmer菜单,点击Hardware Setup窗口完成硬件设置(2)点击Start开始编程下载六、仿真波形分析:波形分析:用波形与真值表进行比较即可。

有波形可以看出,100对应11,是对的。

再看111对应11也与理论相符。

引脚的锁定:x锁定为引脚60,y锁定为引脚61,Sub_in锁定为引脚63,Sub_out锁定为引脚169,diffr锁定为引脚167。

EDA实验一全减器

实验一 1位二进制全减器设计一、实验目的1. 熟悉EDA 技术开发流程;2. 熟悉Quartes II 集成开发软件的使用;3. 学习用原理图输入法和文本输入法进行简单设计;4. 熟悉简单组合电路设计,掌握系统仿真,学会分析硬件测试结果;5. 初步熟悉EDA 实验装置的使用。

二、实验内容与要求1.完成全减器的设计:分别使用原理图输入法和文本输入法设计一位二进制全减器,用分层设计方法,顶层为全减器,底层由半减器(也用原理图输入法)和逻辑门组成;2.进行波形仿真,并分析仿真波形图;3.下载测试减法器是否正确。

三、设计思路/原理图由课本P79:1位二进制全加器的设计可以仿照出1位二进制全减器的设计。

实验框图如真值表画出卡诺图并化简可得: Ca=M N ;Re=(M N)+(M ·N)。

选择相应组合逻辑器件可以构成半减器和全减器。

四、 实验程序:按照实验要求:底层半减器用原理图输入法,顶层为全减器,可知只需写出全减器和或门程序如下:(1)全减器程序:library ieee; --1位二进制全减器顶层设计描述 use ieee.std_logic_1164.all; entity f_suber isport (min, nin, lin : in std_logic; --减数、被减数和低位来的借位 cary, sub : out std_logic); --进位和结果end entity f_suber;architecture fs1 of f_suber iscomponent h_suber--对要调用的元件h_suber的界面端口进行定义port ( m, n: in std_logic;ca, re: out std_logic);end component;component or2a --对要调用的元件or2a的界面端口进行定义port (a, b: in std_logic;c:out std_logic);end component;signal g, h, y: std_logic;begins1 : h_suber port map (m=>min, n=>nin, ca=>g, re=>h);--例化一个1位二进制半减器s2 : h_suber port map (m=>h, n=>lin, ca=>y, re=>sub);--例化一个1位二进制半减器s3 : or2a port map (a=>g, b=>y, c=>cary); --例化一个或门end architecture fs1;(2)或门程序:library ieee;use ieee.std_logic_1164.all;entity or2a isport (a,b :in std_logic;c :out std_logic);end entity or2a;architecture one of or2a isbeginc<=a or b;end architecture one;五、实验步骤1.用原理图输入法设计半减器(1)打开Quartus II软件,进入编辑环境。

用74LS138和门电路设计1位二进制全减器

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图1.1所示)。

CO-—-向高位的借位; Y ———两位数之差;C I —-—来自低位的借位;

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7;

其逻辑图如下:

1

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图2.1所示)。

7

D1D0

A0

A1

A2S 152 m m

3,210代表亮,或是开关闭合;0代表灯灭;Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A。

课程设计位二进制全加器全减器

课程设计---位二进制全加器全减器————————————————————————————————作者: ————————————————————————————————日期:组合逻辑电路课程设计之——4位二进制全加器/全减器作者:姓名:周志敏学号:2907301001姓名:王光甫学号:2907301007姓名:沈俊楷学号:2907301004课程设计题目要求:使用74LS283构成4位二进制全加\全减器。

具体要求:1)列出真值表;2)画出逻辑图;3)用Verilog HDL进行仿真。

摘要加法器是数字系统中的基本逻辑器件。

例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面问题。

多为加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运行速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行加法器的资源占用差距也会越来越大。

本文将采用4位二进制并行加法器作为折中选择,所选加法器为74LS283,74LS283是4位二进制先行进位加法器,它只用了几级逻辑来形成和及进位输出,由其构成4位二进制全加器;而四位的全减器可以用加法器简单的改造而来。

采用Verilog HDL对四位的全加器-全减器进行仿真。

关键字74LS283,全加器,并行进位,串行进位,全减器,VerilogHDL仿真总电路设计一、硬件电路的设计该4位二进制全加器以74LS283(图1)为核心,采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

ﻩ 图11)全加器全加器是针对多于一位的操作数相加,必须提供位与位之间的进位而设计的一种加法器,具有广泛而重要的应用。

其除有加数位X 和Y ,还有来自低位的进位输入CIN ,和输出S(全加和)与CO UT(送给高位的进位),满足下面等式:CINY CIN X Y X COUT CINY X CIN Y X N CI Y X N CI Y X CIN Y X S ⋅+⋅+⋅=⋅⋅+⋅'⋅'+'⋅⋅'+'⋅'⋅=⊕⊕=其中,如果输入有奇数个1,则S 为1;如果输入有2个或2个以上的1,则COUT 为1。

一位全减器的设计

EDA技术实用教程

课题报告

课题名称:一位全减器的设计

院系:

专业:电子信息工程

组员:

设计流程:

一、一位半减器的设计

一位半减器程序如下; 其中x,y 是输入,diff 是输出差,s_out 是借位输出, sub_in 为借位输入。

library ieee;

use ieee.std_logic_1164.all; entity h_suber is

port (x,y : in std_logic; diff,s_out : out std_logic ); end h_suber;

architecture hdlarch of h_suber is begin process(x,y) begin

diff <= x xor y;s_out <= (not x) and y; end process; end hdlarch;

半减器逻辑表达式:

半减器真值表:

输入输出

x y diff s_sout

0000

0111

1010

1100半减器波形图如下:

半减器封装图:

二、一位全减器的设计

一位全减器设计结构图:sub_in为借位输入,clk是输入延迟信号用来消除仿真图中出现的毛刺现象

一位全减器逻辑表达式:

一位全减器真值表:

一位全减器波形图:

一位全减器封装图:。

全减器

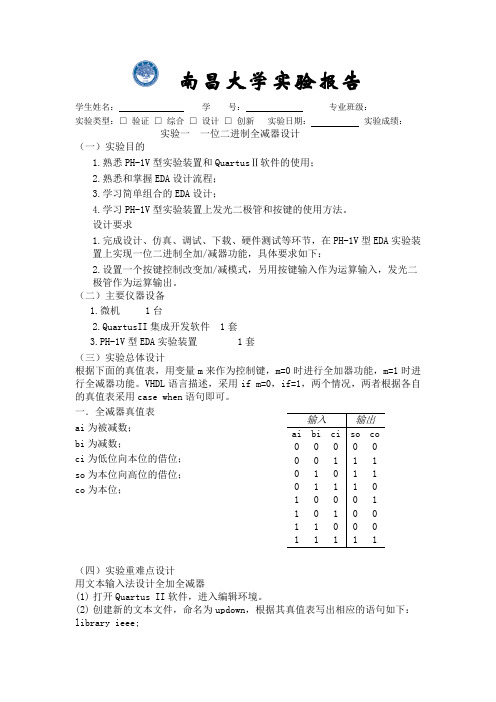

南昌大学实验报告学生姓名: 学 号: 专业班级: 实验类型:□ 验证 □ 综合 □ 设计 □ 创新 实验日期: 实验成绩:实验一 一位二进制全减器设计(一)实验目的1.熟悉PH-1V 型实验装置和Quartus Ⅱ软件的使用;2.熟悉和掌握EDA 设计流程;3.学习简单组合的EDA 设计;4.学习PH-1V 型实验装置上发光二极管和按键的使用方法。

设计要求1.完成设计、仿真、调试、下载、硬件测试等环节,在PH-1V 型EDA 实验装置上实现一位二进制全加/减器功能,具体要求如下:2.设置一个按键控制改变加/减模式,另用按键输入作为运算输入,发光二极管作为运算输出。

(二)主要仪器设备 1.微机1台2.QuartusII 集成开发软件 1套3.PH-1V 型EDA 实验装置1套(三)实验总体设计根据下面的真值表,用变量m 来作为控制键,m=0时进行全加器功能,m=1时进行全减器功能。

VHDL 语言描述,采用if m=0,if=1,两个情况,两者根据各自的真值表采用case when 语句即可。

一.全减器真值表 ai 为被减数; bi 为减数;ci 为低位向本位的借位; so 为本位向高位的借位; co 为本位;(四)实验重难点设计用文本输入法设计全加全减器(1) 打开Quartus II 软件,进入编辑环境。

(2) 创建新的文本文件,命名为updown ,根据其真值表写出相应的语句如下: library ieee;输入 输出 ai bi ci so co 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 0 0 11111use ieee.std_logic_1164.all;entity updown isport(ai,bi,ci,m:in std_logic;so,co:out std_logic);end entity updown;architecture one of updown issignal abc:std_logic_vector(2 downto 0);beginabc<=ai&bi&ci;process(abc)beginif m='0' thencase abc iswhen "000"=>so<='0';co<='0';when "001"=>so<='1';co<='0';when "010"=>so<='1';co<='0';when "011"=>so<='0';co<='1';when "100"=>so<='1';co<='0';when "101"=>so<='0';co<='1';when "110"=>so<='0';co<='1';when "111"=>so<='1';co<='1';when others=>null;end case;end if;if m='1' thencase abc iswhen "000"=>so<='0';co<='0';when "001"=>so<='1';co<='1';when "010"=>so<='1';co<='1';when "011"=>so<='1';co<='0';when "100"=>so<='0';co<='1';when "101"=>so<='0';co<='0';when "110"=>so<='0';co<='0';when "111"=>so<='1';co<='1';when others=>null;end case;end if;end process;end one;3.对照引脚绑定表,绑定好引脚,下载到实验芯片中,进行硬件测试。

EDA一位二进制全减器设计

实验一 1位二进制全减器设计一、实验目的1.熟悉EDA 技术开发流程;2.熟悉Quartes II 集成开发软件的使用;3.初步熟悉PH-1V 型实验装置的使用;4.学习用原理图输入法和文本输入法进行简单的数字电路设计。

二、实验要求1.用文本输入法和原理图输入法分别实现一位二进制全减器的设计。

2.进行时序波形仿真,并分析仿真波形图3.在仿真正确的情况下,对1位二进制全减器分别下载到实验箱中做硬件测试。

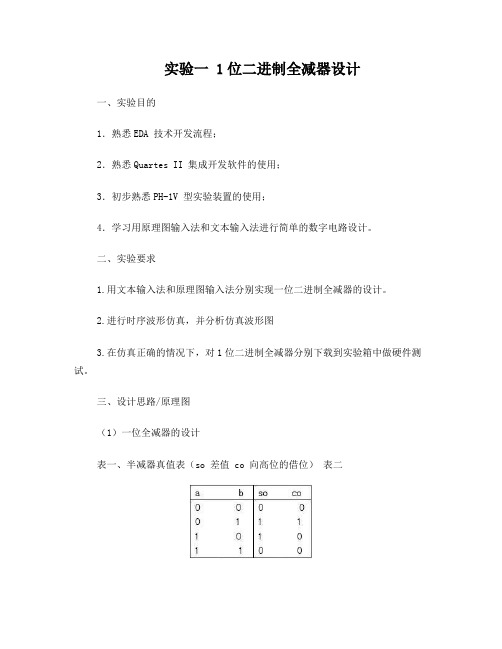

三、设计思路/原理图(1)一位全减器的设计表一、半减器真值表(so 差值 co 向高位的借位)表二表二、全减器真值表(cin 低位来的借位 cout 向高位的借位)根据半减器真值表可以用文本输入法(VHDL 语言)设计出半减器,,再根据全减器的真值表通过文本输入法(VHDL 语言)调用两个半减器构成一个全减器。

此外还可以通过原理图输入法设计出半减器,然后通过两个半减器和一个或门构成一个全减器。

实验原理图如下(1)由半减器真值表可画出其原理图如下:将半减器设计成可调用元件如下:h_sub insta bco so(2)由全减器的真值表可以画出原理图如下:四、实验程序(1)一位半减器文本描述 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_sub ISPORT(a,b:IN STD_LOGIC; co,so:OUT STD_LOGIC); END ENTITY h_sub;ARCHITECTURE fh1 OF h_sub is BEGINso<=NOT(a XOR (NOT b));co<=(NOT a)AND b; END ARCHITECTURE fh1; (2)或门逻辑描述 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a ISPORT(a,b:IN STD_LOGIC; c:OUT STD_LOGIC); END ENTITY or2a;ARCHITECTURE one OF or2a IS BEGIN c<=a OR b;END ARCHITECTURE one;ne;(3)一位二进制全减器顶层文件描述 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_sub ISPORT (ain,bin,cin:IN STD_LOGIC; cout,sub:OUT STD_LOGIC); END ENTITY f_sub;ARCHITECTURE fd1 OF f_sub ISCOMPONENT h_sub—调用半减器的声明语句PORT(a,b:IN STD_LOGIC;co,so:OUT STD_LOGIC);END COMPONENT;COMPONENT or2a—调用或门的声明语句PORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f:STD_LOGIC;BEGINu1:h_sub PORT MAP(a=>ain,b=>bin,co=>d,so=>e);--例化语句u2:h_sub PORT MAP(a=>e,b=>cin,co=>f,so=>sub);u3:or2a PORT MAP(a=>d,b=>f,c=>cout);END ARCHITECTURE fd1;五、实验步骤1、建立工作库文件和编辑设计文件(1)在D盘新建一个文件夹用来保存工程文件(2)打开QuartusⅡ8.0软件,选择菜单File->New->VHDL File,点击OK后在打开的界面下输入已经设计好的程序。

[数字电子技术及应用(第2版)习题答案第2单元习题答案

[数字电子技术及应用(第2版)习题答案第2单元习题答案自我检测题一、填空题2-1如果对键盘上108个符号进行二进制编码,则至少要 7 位二进制数码。

2-2共阳LED 数码管应由输出 低 电平的七段显示译码器来驱动点亮,而共阴LED 数码管应采用输出为 高 电平的七段显示译码器来驱动点亮。

2-3采用54LS138完成数据分配器的功能时,若把S 1作为数据输入端接D ,则应将使能端2S 接 低 电平,3S 接 低 电平。

2-4对N 个信号进行编码时,需要使用的二进制代码位数n 要满足条件 N ≤2n 。

二、选择题2-5一个8选1的数据选择器,其地址输入端有几个 B 。

A 、1B 、3C 、2D 、42-6可以用 B 、C 电路的芯片来实现一个三变量组合逻辑函数。

A 、编码器B 、译码器C 、数据选择器2-7要实现一个三变量组合逻辑函数,可选用 A 芯片。

A 、74LS138B 、54LS148C 、74LS147 三、判断题2-8 54/74LS138是输出低电平有效的3线-8线译码器。

( ✓ )2-9当共阳极LED 数码管的七段(a ~g )阴极电平依次为1001111时,数码管将显示数字1。

(✓ ) 练习题2-1试分析图题2-10所示各组合逻辑电路的逻辑功能。

A B C DYABY图题2-1解:(a)图,)⊕=,真值表如表题2-1(a)A⊕Y⊕B)((DC所示:表题2-1(a)(a)图为四变量奇校验器,当输入变量中有奇数个为1,输出为1。

(b)图CB A YC B A AB C B A AB Y ⊕⊕=⊕+=⊕•=21,)()(2-3试采用与非门设计下列逻辑电路: (1)三变量非一致电路;(2)三变量判奇电路(含1的个数); (3)三变量多数表决电路。

解:(1)设A 、B 、C 为输入变量,当输入不一致时输出为1,一致时为0,真值表如表题2-3(1)所示:表题2-3(1) A B C Y 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 111函数式为:ABC C B A ABC C B A Y •=+= 电路图如图题2-3(1)所示:(2)设A、B、C为输入变量,当输入奇数个1时输出为,否则为0,真值表如表题2-3(2)所示:表题2-3(2)A B C Y0 0 0 00 0 1 10 1 0 10 1 1 01 0 0 11 0 1 01 1 0 01 1 1 1函数式为:ABCBABCAY••+++=•=ABCCBABCACBACABC电路图如图题2-3(2)所示:(3)设A、B、C为输入变量(设“1”表示同意,“0”表示不同意),Y为输出变量(设“1”表示通过,“0”表示不通过),真值表如表题2-3(3)所示:表题2-3(3)A B C Y0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1函数式为:BC•=A+Y•=+++=+BCACBCABAABACBABCCABC电路图如图题2-3(3)所示:2-4有一个车间,有红、黄两个故障指示灯,用来表示三台设备的工作情况。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告

学生姓名:学号:专业班级:通信081

实验类型:□验证□综合□设计□创新实验日期:2010.10.15 实验成绩:

实验一一位二进制全减器设计

一、实验目的

(1)掌握QuartusII的VHDL原理图设计和文本设计全过程;

(2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果。

二、实验内容与要求

(1)设计一个二进制全减器,用分层设计方法,顶层为全减器,底层为半减器和逻辑门组成;

(2)进行波形仿真,并分析仿真波形图;

(3)下载测试全减法器是否正确。

三、设计思路/原理图

一位全减器可以由两个半减器和一个或门连接而成,根据半减器真值表对半减器进行描述,再对或门的VHDL描述,而后根据原理图对全减器的VHDL描述。

图1 全减器f_suber电路图

四、实验程序(程序来源:_________________________)

library ieee; --半减器描述

use ieee.std_logic_1164.all;

entity h_suber is --定义半减器h_suber实体

port(a,b:in std_logic;

do,vo:out std_logic);

end entity h_suber;

architecture fs1 of h_suber is

signal abc:std_logic_vector (1 downto 0);

begin

abc <= a&b ;

process (abc)

begin

case abc is

when "00" => do<='0';vo<='0';

when "01" => do<='1';vo<='1';

when "10" => do<='1';vo<='0';

when "11" => do<='0';vo<='0';

when others => null;

end case;

end process;

end architecture fs1;

library ieee; --一位二进制全减器顶层设计描述

use ieee.std_logic_1164.all;

entity f_suber is --定义全减器f_suber实体

port (ain,bin,cin:in std_logic;

v,sub:out std_logic);

end entity f_suber;

architecture fs of f_suber is

component h_suber ---调用半减器声明语句

port (a,b:in std_logic;

do,vo:out std_logic);

end component;

component or2a --调用或逻辑门声明语句

port (m,n:in std_logic;

h:out std_logic);

end component;

signal e,f,g:std_logic; ---定义3个信号作为内部的连接线

begin

u1:h_suber port map(a=>ain,b=>bin,do=>e,vo=>f); ---例化语句

u2:h_suber port map(a=>e,b=>cin,do=>sub,vo=>g);

u3:or2a port map(m=>g,n=>f,h=>v);

end architecture fs;

五、实验步骤

1.利用quartusII建立工程

在file中打开【】→【】→在【】中选

择存放的目录→【】f_suber要与顶层文件中entity f_suber相同→点击next→点击next→选择芯片→next完成;

再在file下面点【】→【】→点击ok→编写程序→编译

并保存在f_suber文件中(改动程序后,再保存,再编译)→管脚【】→

【】→而后对芯片设置,即打开device→点【】→点【】与【】→选如【】与【】→选芯片→确定ok ;

重新编译→点下载,后选【】硬件有“JTAG【】”和“ASP 【】手动添加以扩展名为.pof的文件【】”两个接口其一(要看硬件接口),选中【】”→添加【】中的驱动程序→【】

→点【】开始下载。

注:原理图输入法工程建立与文本输入法建立相似,而且原理图形与以前学习的Mutisim相同,这里不再多说。

2. 用quartusII创建仿真工程

在已有的工程中,在file下面点【】→【】OK→在任务栏【】中双击,来添加管脚→【】→【】OK然后设置一下输入引脚波形→保存一下→仿真【】→必要时还可以设置一下【】

中的【】改时间【】→再重新仿真一下。

六、仿真波形分析

下图为实验所得的波形图:

对实验所得的波形图作如上的标记,可以得到如下仿真信息表:

差值D的结果为A—B—C的值,与理论值一样借位输出V也与理论值一致;从波形图可以看出输出波形有一定的延时和毛刺,是因为经过元器件需要时间和冒险现象存在。

七、硬件测试

使用的芯片是EP1K00QC208-3。

ain、bin、cin分别连接引脚53(电平1)、54(电平2)、55(电平3),sub、v分别连接引脚167(LED1)、168(LED2);测试为:电平1、2、3分别为(低、低、低)、(低、低、高)、(低、高、低)、(低、高、高)、(高、低、低)、(高、低、高)、(高、高、高)、(高、高、高)对应的LED1、LED2分别为(灭、灭)、(亮、亮)、(亮、亮)、(灭、亮)、(亮、灭)、(灭、灭)、(灭、灭)、(亮、亮)。

八、实验小结

对全减器的设计是比较简单的,而且在对全减器编译、仿真和下载之前,我已对Quartus9.0进行了多次操作,已经熟练地掌握了利用QuartusII9.0建立工程和创建仿真等;通过此次试验,我可以向复杂的设计迈进,通过试验,一步一步地提高自己的设计能力、创新能力。

九、实验心得/实验体会

通过这个实验,掌握了利用QuartusII建立工程、创建仿真工程和编程下载;在第一次编译时,发现“or2a”没有定义,然后定义一下逻辑或门or2a,保存一下,重新编译通过;在第一次波形仿真后,改变输入波形和end time,保存,重新仿真,仿真后的波形没有变,之后才发现要改动Assignments下的setting-f_suber框中的Simulator Setting;在用原理图输入法设计时,底层用文本输入法创建半减器工程,顶层原理图连接之后,需要再在创建一个原理图工程,工程名是f_suber。