XilinxVivadozynq7000入门笔记剖析

Zynq学习笔记(基本设计流程)

4.设置boot模式。

输入0,1-9测试

5.将LED_Dimmer.BIN文件名字改为BOOT.BIN(后缀不用修改),再拷贝到SD卡中,并插入Zedboard。

6.设置boot模式。

5.配置PS时钟:CLKIN=33.3333(常用的)。CPU=666.6666;DDR_CLK=533.333.

CPU Clock Ratio=6:2:1,均为默认值。

设置外设时钟。

QSPI的模块内部有一个2分配的电路,应此想设置他的工作频率为100M,就需要将输入时钟设为200MHz。

SDIO(即SD卡的时钟),设为50MHz。

勾选USB0,28-39

勾选Ethernet0,改EMIO为MIO:16-27,打开“+”,勾选MDIO:52-53

添加SD 0 40-45, CD:47, WP:46

点开GPIO,勾选GPIO MIO,设置MIO的Direction:50-51为输入,MIO7只能是输出,其余为输入输出。若看不到,就向右拉移动条。

3.下面是main.c的具体设计步骤,附件为完整的程序,可以拷贝以节省时间。

4.点击system.mss,可以找到外设的驱动和例程,axi_gpio_1,Examples(点击);打开xgpio_example.c。

5.在main.c中从xgpio_example.c中拷贝并添加两个头文件。#include "xparameters.h";#include "xgpio.h"

11.往GPIO写0,灭灯。XGpio_DiscreteWrite(&Gpio, LED_CHANNEL, 0);

XilinxVivadozynq7000入门笔记剖析

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

Zynq7000系列之芯片引脚功能综述

Zynq7000系列之芯⽚引脚功能综述很多⼈做了很久的FPGA,知道怎么去给信号分配引脚,却对这些引脚的功能及其资源限制知之甚少;在第⼀章⾥对Zynq7000系列的系统框架进⾏了分析和论述,对Zynq7000系列的基本资源和概念有了⼤致的认识,然⽽要很好地进⾏硬件设计,还必须了解芯⽚的引脚特性,以确定其是否符合我们的选型要求,这些要求包括GTX引脚数⽬、select IO引脚数⽬、select IO引脚的资源配置情况、PS IO的数⽬及类型等。

1. Zynq7000系列引脚分类 Zynq7000系列引脚的分类是确定的,⽽各类引脚的数⽬则因芯⽚封装的不同⽽不同,(为了便于理解,本⽂所列引脚数⽬皆以XQ7Z045 FFG900封装为例,⽂章其他部分不再做出说明)其主要类型如下:FFG900引脚分类引脚个数备注PS IO128ARM处理系统的专⽤引脚Select IO362普通的FPGA引脚Configuration Pins InBank 017Jtag类的⼀些引脚GTX Pins16X4(16个通道,每通道两对差分引脚)⾼速串⾏收发引脚XADC Pins32模数转换引脚1.1. Configuration Pins In Bank 0Pin Name Type Direction DescriptionDONE_0Dedicated Bidirectional⾼有效,⾼代表配置完成INIT_B_0Dedicated Bidirectional低有效,表⽰配置存储器正在初始化PROGRAM_B_0Dedicated Input低有效,表⽰异步复位配置逻辑TCK_0Dedicated Input Jtag时钟信号TDI_0Dedicated Input Jtag数据输⼊TDO_0Dedicated Output Jtag数据输出TMS_0Dedicated Input Jtag模式选择CFGBVS_0Dedicated Input为bank0的配置引脚预选择电平标准,1表⽰bank0的供电电压为2.5或3.3;0表⽰bank0的供电电压为1.8 PUDC_B Multi-function Input上拉电阻配置引脚,配置SelectIO在配置阶段或上电后的其上拉电阻是否使能。

ZYNQ笔记(5):软中断实现核间通信

ZYNQ笔记(5):软中断实现核间通信 ZYNQ包括⼀个 FPGA 和两个 ARM,多个 ARM 核⼼相对独⽴的运⾏不同的任务,每个核⼼可能运⾏不同的操作系统或裸机程序,但是有⼀个主要核⼼,⽤来控制整个系统以及其他从核⼼的允许。

因此我们可以在 CPU0 和 CPU1 中独⽴跑不同的应⽤程序,发挥双核的⾮对称性架构的优势和性能。

从软件的⾓度来看,多核处理器的运⾏模式主要有三种: ① AMP(⾮对称多进程):多个核⼼相对独⽴的运⾏不同的任务,每个核⼼可能运⾏不同的操作系统或裸机程序,但是有⼀个主要核⼼,⽤来控制整个系统以及其它从核⼼的运⾏。

② SMP(对称多进程):⼀个操作系统同等的管理各个内核,例如 PC 机。

③ BMP(受约束多进程):与 SMP 类似,但开发者可以指定将某个任务仅在某个指定内核上执⾏默认情况下。

裸机程序 ZYNQ 仅运⾏⼀个 CPU,这⾥主要讲解 AMP 模式下,两个 CPU 同时运⾏的裸机程序开发⽅法。

⼀、核间中断原理(软中断SGI) 软中断的 ID 都是从0到15,并且都是上升沿触发,主要⽤于核间中断或者 CPU ⾃⼰中断⾃⼰。

中断函数如下:XScuGic_SoftwareIntr(&InterruptController, //指向GIC指针INTC_CPU0, //需要中断的CPU IDXSCUGIC_SPI_CPU0_MASK); //使能该CPU会接受中断⼆、ARM启动过程1.ARM ⾥有个 ROM,存储了⼀段程序,ROM起来后从 SD 卡读取数据2.启动 FSBL(First Boot Loader)第⼀启动项(有模板)3.加载 bit(FPGA配置程序),同时加载 elf(ARM应⽤程序),如果是操作系统则 elf 替换成 uBoot三、搭建软件 CPU0 和 CPU1 ⾮对称环境1.创建 amp_fsbl ⽤于⽣成烧写镜像的时候加载 core0 和 core1的代码。

Zynq-7000嵌入式多功能阻抗测试仪的设计与校准

Zynq-7000嵌入式多功能阻抗测试仪的设计与校准赵冬青; 逯宏超; 储成群【期刊名称】《《实验室研究与探索》》【年(卷),期】2019(038)009【总页数】5页(P99-103)【关键词】阻抗分析仪; 嵌入式系统; 三参数正弦拟合【作者】赵冬青; 逯宏超; 储成群【作者单位】中北大学仪器与电子学院太原030051【正文语种】中文【中图分类】TN7020 引言阻抗测量在电子器件的性能检测、传感器、仪器仪表、生物医学和国防领域有着广泛的应用。

在实验室中通常使用的RLC表测量的频率范围和阻抗范围都有限,而且测量精度低。

具体实践应用中,一般需要嵌入在便携测量系统或小型且简单的设备中,但这些设备测量频率和范围都有限,或者缺乏实验室阻抗分析仪的典型特征,例如宽范围的激励信号幅度,直流偏置测量等。

市场上定制的阻抗分析仪大多数是采用嵌入式微处理器控制专用的阻抗测量芯片AD5993[1] ,但是若要实现宽范围的频率和阻抗测量,就要增加外部电路来实现;例如:可变时钟发生器、电流-电压转化(Current-to-Voltage Converter,CVC)等,通过外加电路可以实现宽范围的频率和阻抗测量,同时也增加了电路的复杂性。

基于上述分析,本文提出了Zynq-7000的阻抗测试系统,该测试系统不包含任何专用的阻抗转换集成电路,它完全基于系统本身的A/DC和D/AC以及通用的仪表放大器、模拟电路配合来实现阻抗的测量。

1 硬件平台介绍和阻抗测量原理Zynq-7000FPGA系列是一款强大的全可编程(All Programmable)处理器,不同于传统的采用FPGA架构和ARM芯片,它是在FPGA内部集成了ARM的硬核处理器[2]。

用户可以创建基于AXI总线的IP核,实现软、硬件的协调设计。

Zynq-7000阻抗测试仪采用的主控芯片是XC7Z020clg484-2,它的ARM内核是两块独立的Cortex-A9处理器,最高时钟频率可达到1 GHz。

XilinxZYNQ-7000平台简介

XilinxZYNQ-7000平台简介平台介绍Zynq7000是赛灵思公司(Xilinx)推出的⾏业第⼀个可扩展处理平台Zynq系列。

旨在为视频监视、汽车驾驶员辅助以及⼯⼚⾃动化等⾼端嵌⼊式应⽤提供所需的处理与计算性能⽔平。

在2010年4⽉硅⾕举⾏的嵌⼊式系统⼤会上,赛灵思发布了可扩展处理平台的架构详情,这款基于⽆处不在的ARM处理器的SoC可满⾜复杂嵌⼊式系统的⾼性能、低功耗和多核处理能⼒要求。

赛灵思可扩展处理平台芯⽚硬件的核⼼本质就是将通⽤基础双ARMCortex-A9MPCore 处理器系统作为“主系统”,结合低功耗28nm⼯艺技术,以实现⾼度的灵活性、强⼤的配置功能和⾼性能。

由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的⼀致性,同时也⽅便⽇后本系列新产品的命名。

Zynq-7000系列的可编程逻辑完全基于赛灵思7系列FPGA架构来设计,可确保28nm系列器件的IP核、⼯具和性能100%兼容。

最⼩型的Zynq-7000、Zynq-7010和Zynq-7020均基于专门针对低成本和低功耗优化的Artix-7系列;较⼤型的Zynq-7030和Zynq-7040器件基于包括4⾄12个10.3Gbps收发器通道,可⽀持⾼速⽚外连接的中端Kintex-7系列。

所有四款产品均采⽤基于2个12位1MspsADC(模数转换器)模块的新型模拟混合信号模块。

Zynq®-7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上⾼度集成 CPU、DSP、ASSP 以及混合信号功能。

Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗性价⽐最⾼的全⾯可扩展的 SoC 平台,可充分满⾜您的独特应⽤需求。

ZYNQ7000开发平台用户手册说明书

文档版本控制目录文档版本控制 (2)一、开发板简介 (6)二、AC7Z020核心板 (8)(一)简介 (8)(二)ZYNQ芯片 (9)(三)DDR3 DRAM (11)(四)QSPI Flash (14)(五)时钟配置 (16)(六)电源 (17)(七)结构图 (18)(八)连接器管脚定义 (19)三、扩展板 (23)(一)简介 (23)(二)CAN通信接口 (24)(三)485通信接口 (24)(四)千兆以太网接口 (25)(五)USB2.0 Host接口 (27)(六)USB转串口 (28)(七)AD输入接口 (29)(八)HDMI输出接口 (30)(九)MIPI摄像头接口(仅AX7Z020使用) (32)(十)SD卡槽 (33)(十一)EEPROM (34)(十二)实时时钟 (34)(十三)温度传感器 (35)(十四)JTAG接口 (36)(十五)用户LED灯 (36)(十六)用户按键 (37)(十七)扩展口 (38)(十八)供电电源 (40)(十九)底板结构图 (41)芯驿电子科技(上海)有限公司 基于XILINX ZYNQ7000开发平台的开发板(型号: AX7Z020B )2022款正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ZYNQ7000 FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

核心板使用XILINX 的Zynq7000 SOC 芯片的解决方案,它采用ARM+FPGA SOC 技术将双核ARM Cortex-A9 和FPGA 可编程逻辑集成在一颗芯片上。

另外核心板上含有2片共512MB 高速DDR3 SDRAM 芯片和1片256Mb 的QSPI FLASH 芯片。

在底板设计上我们为用户扩展了丰富的外围接口,比如2路CAN 通信接口,2路485通信接口,2路XADC 输入接口, 1路千兆以太网接口,1路USB2.0 HOST 接口,1路HDMI输出接口,Uart 通信接口,SD 卡座,40针扩展接口等等。

AUMO ALINX ZYNQ-7000产品手册说明书

ZYNQ-7000产品手册ZYNQ-7000 Product Guide2023关于我们官方合作伙伴业务范围芯驿电子科技(上海)有限公司,成立于2012年,总部位于上海松江临港科技城,是一家车载智能产品和FPGA 技术方案公司,拥有“AUMO”和“ALINX”两大品牌,其中AUMO 品牌专注车载智能产品,ALINX 品牌专注于FPGA 产品和方案定制。

经历十年发展,公司产品已经远销海外30多个国家。

2018年,公司通过高新技术企业认证,并通过ISO9001质量体系认证;2019年,荣获上海市松江区九亭镇“科技创新奖”;2020年,荣获上海市“专精特新企业“称号;2021年,申请通过上海市科技型中小企业技术创新资金项目,通过了国家级科技型中小企业认定,并通过了高新技术企业认证复审;2022年获得上海市张江国家自主创新示范区专项发展资金并通过“上海市创新型中小企业”认证。

ALINX 是全球的FPGA 芯片龙头企业XILINX 官方合作伙伴,国内FPGA 芯片龙头企业紫光同创官方合作伙伴,同时作为百度AI 合作伙伴,为百度定制了国产AI飞桨系统的Edgeboard 系列边缘设备。

通过多年的研发投入,已经推出100多款FPGA SoM 模组和配套板卡,积累了1000多家企业批量用户,上万个独立开发者,市场占有率遥遥领先。

通过产品+定制化服务的经营方式,ALINX 将继续加大对产品研发和技术研究的投入,不断与垂直行业客户合作,聚焦高端设备领域,协助客户解决行业的技术难题。

主要聚焦于FPGA + AI 解决方案,FPGA 国产化,FPGA 开发套件, ALINX 自有品牌产品。

公司提供的设计解决方案涉及人工智能、自动驾驶、轨道交通、半导体、5G 通信、医疗设备、工业互联、仪器仪表、数据中心、机器视觉、视频图像处理等行业。

紫光同创国内唯一的FPGA 板卡官方合作伙伴,XILINX 官方重要合作伙伴,百度AI合作伙伴。

XILINX_zynq_详解(1)

XILINX_zynq_详解(1)Xinlix的FPGA确实做的是⼜⼤⼜强,接触FPGA有5、6年的时间,从没有详细的了解⼀下FPGA是什么?FPGA可以做什么?FPGA的溯源在哪⾥?FPGA的⼚商有哪些?FPGA的选型该怎么进⾏?FPGA在⼈⼯智能上会有什么发展前景?FPGA该如何学习?FPGA的着⼒点该在什么地⽅? 接着新开园的新鲜劲,做⼀下总结,因为涉及内容较多,为了能浅显易懂的介绍好各个问题,有必要也必须拉出⼀条主线来。

稍微⾛个神,为什么写博客?很多⼈在写,我个⼈意见,写博客不是⽬的,⽬的是能够将知识系统的总结⼀下。

在⽹络上泛泛的看来的东西,太杂太不系统,如果不整理⼀下、消化⼀下,可能还是没有⼀点进步,所以要写出来,总结下来。

好,来拉⼀条主线?什么是FPGA【定义】→FPGA的⼚家有哪些【选型】→FPGA是什么、FPGA可以做什么【应⽤】—————————————我是分隔符———————————————————————————①什么是FPGA? FPGA-Field Programmable Gate Array,现场可编程门阵列,它是在其他可编程器件,如PAL\GAL\CPLD的基础上进⼀步发展的产物,也是为ASIC(专⽤集成电路)领域中的⼀种半定制电路⽽出现的,克服了原有可编程器件门电路书有限的缺点,FPGA⼀般来说⽐ASIC(专⽤集成电路)的速度要慢,实现同样的功能⽐ASIC电路⾯积要⼤。

但是他们也有很多的优点⽐如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。

⼚商也可能会提供便宜的但是编辑能⼒差的FPGA。

因为这些有⽐较差的可编辑能⼒,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到⼀个类似于ASIC的芯⽚上。

另外⼀种⽅法是⽤CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)。

【摘⾃度娘】 看来很成功的产物,发展壮⼤的过程不可避免的会经历艰难困苦,FPGA也不例外,1985年的冬天,全球⾸款FPGA产品⽐我早2年出⽣了,起名:XC2064,诞⽣宣⾔:未来⼗年内每⼀个电⼦设备都将有⼀个可编程逻辑芯⽚!当时呱呱落地的它可能想不到,今天的它确实实现了这个理想。

Zynq-7000最小系统设计及无DDR3固化运行方法

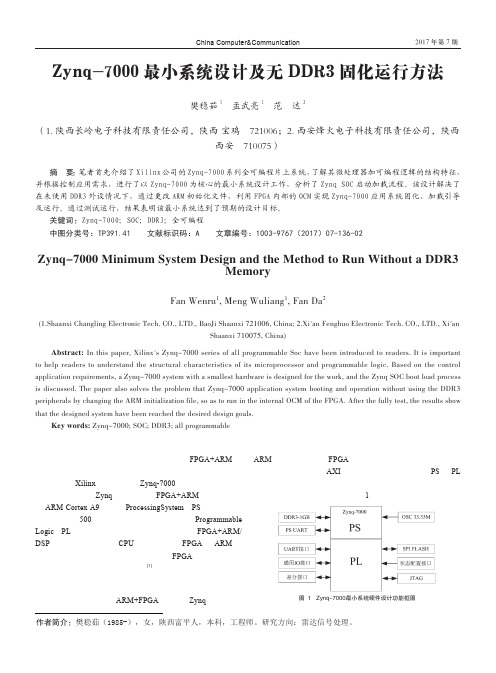

图1 Zynq-7000最小系统硬件设计功能框图樊稳茹(1985-),女,陕西富平人,本科,工程师。

研究方向:雷达信号处理。

2017年第7期信息与电脑China Computer&Communication软件开发与应用该最小系统PS部分结合用户应用程序用于实现控制功能,PL部分包括UART接口、时序产生、地址译码、片上存储和外设控制等逻辑功能模块。

主要的功能芯片为X7Z045、MT41K256M16HA、MAX3160E、MAX3096、MAX3045、W25Q128、ADG3308等,为了降低硬件成本,在满足使用需求的条件下,该最小系统设计时取消了图1中虚线框中的DDR3存储器。

2 基本启动配置流程分析Zynq是一个可扩展处理平台,简单地说就是有个FPGA 做外设的A9双核处理器,所以它的启动流程与FPGA完全不同,而与ARM处理器类似。

Zynq支持JTAG、NAND、Parallel NOR、QSPI以及SD卡等启动方式。

Zynq有效利用了片上的CPU来帮助配置,在没有外部JTAG的情况下,处理器系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置,内部的启动存储区(BootROM)和芯片配置单元可实现Zynq从BootROM主动启动或者从JTAG被动启动[2]。

与其他XILINX 7系列的器件不同的是,Zynq并不支持从PL端直接进行启动配置,Zynq的启动配置是分多级进行的,配置过程最少需要两步,但通常是按如下三个阶段进行。

阶段0(Stage0):简称BootROM,控制着整个芯片的初始化过程。

该部分代码是不可修改的,处理器核在上电或者热启动时自动执行这部分代码,并对外部的NAND、NOR、SD等外设控制器进行初始化,同时还负责将阶段1的启动镜像(FSBL镜像)加载到OCM(Zynq片上一个256K的RAM,但在FSBL运行前只能使用其中的192K,所以FSBL要小于192K),然后运行FSBL,FSBL镜像来源由板上MIO[5:3]引脚选择的启动方式决定。

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用

如何使用Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCVg p应用2013年9月11日© Copyright 2013 XilinxOpenCV简介机(p)机开源计算机视觉(OpenCV) 被广泛用于开发计算机视觉应用–包含2500多个优化的视频函数的函数库–专门针对台式机处理器和GPU进行优化–用户成千上万–无需修改即可在Zynq器件的ARM处理器上运行但是–利用OpenCV实现的高清处理经常受外部存储器的限制–存储带宽会成为性能瓶颈–存储访问会限制功耗效率Zynq All-programmable SOC是实现嵌入式计算机视觉应用的极好方法–性能高、功耗低实时计算机视觉应用计算机视觉应用实时分析功能高级驾驶员安全辅助车道或行人检测安防监视敌我识别高速物体检测用于工厂自动化的机器视觉非侵入式医疗成像技术肿瘤检测实时视频分析处理基于帧的基于像素的Pixel based 4Kx2K 特征处理与决策图像处理与特征提取Image processing and FeatureextractionF11080p F2 F3720p480…..480p每像素数百次运算每特性数10000次运算800万次处理x每帧100次运算= 数百亿次运算每秒处理数1000个特征= 数百万次运算实时视频分析的异构实现基于帧的基于像素的图像处理与特征Pixel based 4Kx2K特征处理与判定提取Image processing and Featureextraction F11080pF2F3软件域(ARM)硬件域(FPGA)720p480…..480p每像素数百次运算每特性数10000次运算800万次处理x 每帧100次运算= 数百亿次运算每秒处理数1000个特征= 数百万次运算赛灵思实时图像分析的实现:Zynq All Programmable SoC Programmable SoCFrame based Feature processing and 基于像素的图像处理与特征Pixel based 4Kx2KFeature processing and decision making提取基于帧的特征处理与判定Image processing and FeatureextractionF11080pF2F3720p480…..480p每像素数百次运算每特性数10000次运算1000800万次处理x 每帧100次运算= 数百亿次运算每秒处理数个特征= 数百万次运算Vivado:提高OpenCV应用的效率高清视频算法(每秒约1帧)的C语言仿真–高清视频(每小时1 帧)的RTL仿真实时FPGA实现方案高达60fpsZynq 视频参考设计架构DDR3DDR3外部存储器处理系统DDR 存储控制器SD 卡双核Cortex-A9硬化的外设S_AXI_GP 32b 位S_AXI_HP 64 位AXI4S AXI 互联AXI4 Stream IP 核HDMIHDMI视频输入Xylon 显示控制器HLS 生成的流水线AXI VDMA使用64位高性能端口实现对外部存储器的视频访问使用32位通用端口实现控制寄存器访问使用AXI4-Stream 实现的视频流以IP 为中心的设计流程更快速的IP生成与集成基于C 语言的IP 创建用户首选的系统集成环境C 、C++ 或SystemCDSP 系统生成器(System Generator)C 函数库•浮点math.h •定点VHDL V il •视频VHDL 或Verilog 以及软件驱动Vivado IP 集成器IP 子系统赛灵思IP 第三方IP Vivado RTL 集成用户IP在FPGA 设计中使用OpenCV纯集成的O CVO CV 图像文件读取OpenCV 应用OpenCV 应用OpenCV 参考加速的OpenCV 应用图像文件读取(OpenCV)(OImage penCV)OpenCV2AXIvideo 实时视频输入实时视频输入O CV 函数链AXIvideo2Mat模块O CV 函数链AXIvideo2Mat模块OpenCV HLS 视频库函数链Mat2AXIvideo可综合的OpenCVHLS 视频库函数链Mat2AXIvideo可综合的图像文件写入(OpenCV)AXIvideo2OpenCV 图像文件写入实时视频输出实时视频输出(OpenCV)DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)12345SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线集成的OpenCV 应用DDR3处理系统DDR 存储控制器DDR3DDR3 外部存储器实时视频输入12345SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设p HDMIHDMIXylon显示AXI VDMAAXI 互联实时视频输出视频输入y 控制器HLS 生成的流水线OpenCV 参考/软件执行DDR3图像文件读取处理系统DDR 存储控制器DDR3DDR3外部存储器12345(OImage penCV)OpenCV2AXIvideo SD卡双核Cortex-A9AXIvideo2MatCortex A9硬化的外设HLS 视频库函数链Mat2AXIvideoHDMIHDMIXylon 显示AXI VDMAAXI 互联AXIvideo2OpenCV图像文件写入视频输入y 控制器HLS 生成的流水线(OpenCV)OpenCV 参考/系统测试DDR3图像文件读取处理系统DDR 存储控制器DDR3DDR3外部存储器(OImage penCV)OpenCV2AXIvideo 12SD卡双核Cortex-A9AXIvideo2MatCortex A9硬化的外设HLS 视频库函数链Mat2AXIvideoHDMIHDMIXylon 显示AXI VDMAAXI 互联AXIvideo2OpenCV图像文件写入视频输入y 控制器HLS 生成的流水线(OpenCV)加速的OpenCV 应用DDR3处理系统DDR 存储控制器DDR3DDR3 外部存储器实时视频输入12SD卡双核Cortex-A9AXIvideo2Mat视频库函数链Cortex A9硬化的外设HLS Mat2AXIvideoHDMIHDMI视频输入Xylon显示AXI VDMAAXI 互联实时视频输出y 控制器HLS 生成的流水线OpenCV设计流程OpenCV模块A1)在台式机上开发OpenCV应用2)无需修改即可在ARM内核上运行OpenCV应OpenCV模块B用3)使用I/O函数抽象FPGA部分O CV 4)用可综合代码代替OpenCV函数调用5)运行HLS以生成FPGA加速器OpenCV模块C6)用FPGA加速器调用代替可综合代码调用OpenCV模块DOpenCV 应用的软硬划分opencv2AXIvideo OpenCV 模块AAXIvideo2HLSOpenCV 模块BHLS 模块BO CV HLS 模块C同步OpenCV模块C HLS2AXIvideoOpenCV 模块DAXIvideo2opencv综合OpenCV设计中的权衡OpenCV图像处理是基于存储器帧缓存而构建的–访问局部性较差-> 小容量高速缓存性能不足–架构比较复杂(出于性能考虑)-> 功耗更高–似乎足以满足很多应用的要求•分辨率或帧速率低•在更大的图像中对需要的特征或区域进行处理基于视频流的架构能提供高性能和低功耗–链条化的图像处理函数能减少外部存储器访问针对视频优化的行缓存和窗缓存比处理器高速缓存更简单–针对视频优化的行缓存和窗口缓存比处理器高速缓存更简单–可使用HLS中的数据流优化来实现–需要将代码转换为可综合的代码HLS视频库OpenCV函数不能直接通过HLS进行综合O C S–动态内存分配–浮点–假设图像在外部存储器中修改HLS视频库用于替换很多基本的OpenCV函数–与OpenCV具有相似的接口和算法–主要针对在FPGA架构中实现的图像处理函数–包含专门面向FPGA的优化•定点运算而非浮点运算•片上的行缓存和窗口缓存–不必精确到比特位赛灵思HLS 视频库2013.2AXI4-Stream IO 函数视频数据建模Li b ff ClWi d ClOpenCV 接口函数cvMat2AXIvideo AXIvideo2cvMat cvMat2hlsMat hlsMat2cvMat I lI 2AXI id AXI id 2I lI I lI 2hl M t hl M t2I lI AXIvideo2MatMat2AXIvideoLinebuffer Class Window Class 视频函数Duplicate MaxS Remap IplImage2AXIvideo AXIvideo2IplImage IplImage2hlsMat hlsMat2IplImage CvMat2AXIvideo AXIvideo2CvMat CvMat2hlsMathlsMat2CvMat AbsDiff AddSEqualizeHist Mean Resize AddWeighted Erode Merge Scale And FASTX MinSet Avg Filter2DMinMaxLoc Sobel AvgSdv GaussianBlur MinS Split Cmp HarrisMul SubRS CmpSHoughLines2NotSubS CornerHarris IntegralPaintMask SumCvtColor InitUndistortRectifyMap Range Threshold DilateMaxReduceZero如需了解函数的详情,敬请阅读HLS 用户指南UG 902视频库函数#include “hls video h”包含在hls 命名空间内的C++代码。

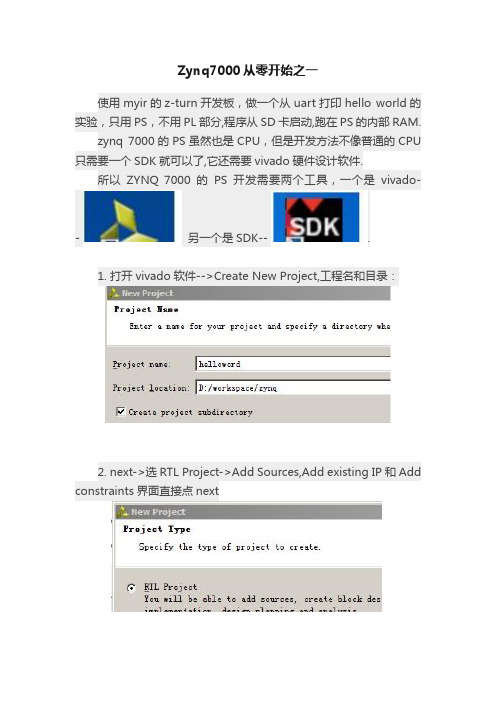

Zynq7000从零开始之一

Zynq7000从零开始之一使用myir的z-turn开发板,做一个从uart打印hello world的实验,只用PS,不用PL部分,程序从SD卡启动,跑在PS的内部RAM.zynq 7000的PS虽然也是CPU,但是开发方法不像普通的CPU 只需要一个SDK就可以了,它还需要vivado硬件设计软件.所以ZYNQ 7000的PS开发需要两个工具,一个是vivado-- 另一个是SDK-- .1. 打开vivado软件-->Create New Project,工程名和目录:2. next->选RTL Project->Add Sources,Add existing IP和Add constraints界面直接点next3. New Parts界面4. 添加IP,在Flow Navigator的IP Integrator下点Create Block DesignCreate Block Design如下,点OK在Diagram界面点击Add IP双击ZYNQ7 Processing System,添加CPU5. 设置CPU在Diagram界面点击Run Block Automation,不做修改,点Finish就可以。

在Diagram界面双击进入设置界面,我们把所有的接口去掉,只留下FIXED_IO.1> PS-PL Configuration->General->Enable Clock Resets->去掉FCLK_RESET0_N2> PS-PL Configuration->GP Master AXI Interface->去掉 MAXI GP0 interface3> Clock Configuration->PL Fabric Clocks->去掉FCLK_CLK04> DDR Congiguration->去掉Enable DDR5> 设置SD和UART引脚MIO Configuration->Bank1 IO Voltage选LVCMOS 1.8V.MIO Configuration->IO Peripherals->选上SD 0, SD 0的引脚配置:MIO Configuration->IO Peripherals->选上UART 1, UARRT 1的引脚配置:6. 点击OK返回Diagram界面, 把DDR接口删掉,配置之后的界面7. 生成设计文件右击system项->Generate Output Products->直接点Generate, 之后会提示文件生成成功.右击system项->Create HDL Wrapper选下面一项,点OK注意:如果重新修改了CPU配置,上面两个步骤一定要重新实行。

Xilinx-Zynq-7000-总结

Zc702基本系统的建立和运行

Zc702 基本系统的建立

Xilin ISE软件集成有Base Syetem Build(BSB) 处理系统创建 向导,来创建一个基于Zc702的嵌入式系统 打开Xilinx platform studio,选择BSB创建新工程,硬件 工程的名字必须是system.xpm

Zc702 基本系统的建立

配置PS外设,点zynq标签,弹出zynq7000的内部结构图,点击绿色部 分,即可配置相应选项

Zc702基本系统的建立和运行

Zc702 基本系统的建立

添加IP

双击IP Catalog里的IP,自动弹出配置对话框,配置完成,自动添加IP,点击Bus Interface,将列出工程中用到的所有IP

Zynq-7000平台的系统架构

Zynq7000平台简介

Zynq7000平台简介

Zynq-7000系统的处理系统:PS

PS: APU

两个Cortex A9 cpu NEON协处理器 L1=32KB,L2=512KB

Platform Dev. 256KB-RAM,128KB-ROM 定时器 中断控制器 …

PL和PS分开供电,可关断PL降低功耗;再次启动PL须重配,需根据码流大小计算配 置时间

PL的配置方式

对PL的配置可作为系统启动的一部分,或者在启动后的任何时候对其进行重配。 PL可以全部地重新配置或者部分动态地重新配置(PR)。

PR只配置PL的一部分。参考设计建议时分复用PL资源,如更新设计系数或算法模块等,类 似于动态地加载和卸载软件模块。

AXI_ACP

用于PL的一个加速一致性主端口。提供快速访问CPU,可选的与L1或L2缓存一致 性

ZYNQ笔记(3):GPIO的使用(MIO、EMIO)——led灯

ZYNQ笔记(3):GPIO的使⽤(MIO、EMIO)——led灯⼀、GPIO原理1.GPIO介绍 程序员通过软件代码可以独⽴和动态地对每个 GPIO 进⾏控制,使其作为输⼊、输出或中断。

(1)通过⼀个加载指令,软件可以读取⼀个 GPIO 组内所有 GPIO 的值。

(2)通过⼀个保存指令,将数据写到⼀个 GPIO 组内的⼀个或多个 GPIO 。

(3)在 ZYNQ-7000 SOC 内,GPIO 模块的控制寄存器和状态寄存器采⽤存储器映射⽅式,它的基地址为 0xE000_A000。

(4)每个GPIO都提供了可编程的中断。

通过软件程序代码可以实现:①读原始和屏蔽中断的状态;②可选的敏感性,包括电平敏感或边沿敏感。

2.MIO与EMIO的异同 MIO(multiuse I/O):多功能IO接⼝,属于Zynq的PS部分,Zynq7000 系列芯⽚有 54 个 MIO。

它们分配在 GPIO 的 Bank0 和 Bank1 上,这些引脚可以⽤在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上,每个引脚都同时具有多种功能,故叫多功能IO接⼝。

这些 IO 与 PS 直接相连。

不需要添加引脚约束,MIO 信号对 PL部分是透明的,不可见。

所以对 MIO 的操作可以看作是纯 PS 的操作。

GPIO 的控制和状态寄存器基地址为:0xE000_A000,我们 SDK 下软件操作底层都是对于内存地址空间的操作。

EMIO(extendable multiuse I/O):扩展MIO,依然属于Zynq的PS部分,只是连接到了PL上,再从PL的引脚连到芯⽚外⾯实现数据输⼊输出。

Zynq7000系列芯⽚有 64 个 EMIO,它们分配在 GPIO 的 Bank2 和 Bank3 上,当 MIO 不够⽤时,PS 可以通过驱动 EMIO 控制 PL 部分的引脚,EMIO 的使⽤相当于,是⼀个 PS + PL 的结合使⽤的例⼦。

Xilinx Vivado zynq7000提高笔记

1. Modelsim仿真1.添加modelsim路径:Tool >options>2. 安装编译仿真库使用modelSIm需要xilinx library被编译。

运行1:report_property [current_project]运行2:Tcl Commandcompile_simlib -helpcompile_simlib -simulator modelsim 或compile_simlib -simulator modelsim -arch all -language all或运行3:安装modelsim库到指定目录compile_simlib -directory D:/modeltech64_10.1c/Xilinx_lib -simulator modelsim3. Modelsim中添加xilinx安装的modelsim库目录:在编译完成库后,生成了一个modelsim.ini文件。

用记事本打开复制其安(需装目录信息到modelsim安装目录中modelsim自己的modelsim.ini文件中。

要去掉modesim.ini的只读特性)重启modelsim,库自动添加到软件中。

4.测试:modelsim10.1c se行为层:通过综合层:时序仿真,测试通过功能仿真,测试通过应用层:时序仿真,测试通过功能仿真,测试通过使用vivado 仿真工具更方便快捷5.Modelsim工程中添加仿真库的命令vopt zynq.tb_simulator_all +acc -o zz1 -L simprims_ver -L unisims_ver -L xilinxcorelib_ver glbl 仿真预编译为库名zynq.tb_simulator_all(后缀tb_simulator_all为仿真testbench文件),添加simprims_ver、unisims_ver、xilinxcorelib_ver、glbl库即可。

Xilinx Zynq 7000-总结

用鼠标点击配置界面上方的Main、Device Initialization、STDIO Connection、

Profile Options、Debugger Options和Common标签,查看这些标签界面下的,配 置内容。

点击运行配置界面下方的“RUN”按钮,运行程序。

23

主要内容

AXI_GP

四个通用接口(两主两从),每个位宽为32,可访问PS的DDR3控制器、PS的片上 RAM资源和其他从设备

AXI_ACP

用于PL的一个加速一致性主端口。提供快速访问CPU,可选的与L1或L2缓存一致 性

7

Zynq7000平台简介

Zynq-7000系统的互联资源

8

Zynq7000平台简介

在SDK主界面左侧的Project Explorer窗口下,右键选中peripheral_tests_0条目,点击 鼠标右键出现浮动菜单,在浮动菜单内选择Run As->Run Configurations…

出现运行配置界面。在该配置界面下,选择Xilinx C/C++ELF选项,点击鼠标右键,出 现浮动菜单,选择New。生成新的运行配置界面。

12

Zc702基本系统的建立和运行

Zc702 基本系统的建立

选择board为ZC702,next 去掉默认添加的IP, BTNs_5Bits、LEDs_8Bits 和SWs_8Bits,next 向导流程完成后,可以选择Generate Bitstream,来 获得下载到PL的位流码文件

5

Zynq7000平台简介

Zynq-7000系统的逻辑资源:PL

PL资源

Artix7 : 7z010、7z020 Kintex7:7z030、7z045、7z100

ZYNQ7000系列学习

ZYNQ7000系列学习

ZYNQ7000-系列知识学习

⼀、ZYNQ7000简介

ZYNQ7000是xilinx推出的具有ARM内核的FPGA芯⽚,可⽤于常见SOC开发。

基于此,通过学习ZYNQ7000的各种设置和开发,可以有效地提⾼对FPGA在SOC上的应⽤特点,为进⼀步使⽤FPGA实现相应的项⽬提供了基础。

⼆、ZYNQ7000的学习内容

学习ZYNQ7000,⼤部分学习的内容是如何实现ARM和FPGA间的通信、FPGA与外部的通信、ARM与外部的通信。

在ARM与FPGA都可以实现设计时,如何选择实现的⽅法也是需要在实际的项⽬中不断的体验。

作为新⼿,相应的软件⼯具的使⽤也是必要的。

还有⼀些其他的内容需要学习,这⾥就不⼀⼀列举。

三、使⽤的⼯具

软件开发⼯具:vivado2019-2,vitis开发平台

硬件测试平台:xc7z010clg400_1芯⽚及配套设备

参考资料:xilinx官⽅资料(ug585),正点原⼦学习视频,尤⽼师FPGA学习视频。

其他⽹络资源。

四、学习⽬标

在掌握相应开发技能的基础上,具备能够独⽴的完成每⼀个阶段的设计分析优化,初步掌握基于FPGA的SOC设计能⼒。

Zynq-7000“FPGA+ARM”架构的数字图像处理系统设计

敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第7期43Z y n q7000 F P G A+A R M 架构的数字图像处理系统设计王咏星,张国兵,宋俊霞(北京轩宇空间科技有限公司,北京100190)摘要:针对目前数字图像高帧频㊁高分辨率㊁大数据量的特点,本系统选取有丰富逻辑资源㊁具有高速并行运算能力和可重构能力的Z y n q7000系列产品,其 F P G A+A R M 的体系架构提高了数字图像处理系统前端图像的采集速度㊁方便了中端图像处理以及后端的显示㊂本文介绍了基于Z y n q7000的C a m e r a l i n k图像输入与采集㊁C a m e r a l i n k图像传输与存储和C a m e r a L i n k图像显示的数字图像处理系统的设计,并且详细介绍了各部分功能涉及的关键技术㊂经验证,本系统实时性高㊁体积小㊁性能稳定,实现了大数据量的图像采集与传输,目前已应用在实际的项目中㊂关键词:Z y n q7000;F P G A;A R M;图像处理系统中图分类号:T P274文献标识码:AD e s i g n o f D i g i t a l I m a g e P r o c e s s i n g S y s t e m P l a t f o r m B a s e d o n Z y n q7000F PG A+A R M A r c h i t e c t u r eW a n g Y o n g x i n g,Z h a n g G u o b i n g,S o n g J u n x i a(B e j i n g S u n W i s e S p a c e T e c h n o l o g y,B e j i n g100190,C h i n a)A b s t r a c t:I n v i e w o f t h e c h a r a c t e r i s t i c s o f h i g h f r a m e f r e q u e n c y,h i g h r e s o l u t i o n a n d l a r g e a m o u n t o f d a t a o f d i g i t a l i m a g e,t h e s y s t e m s e-l e c t s Z y n q7000s e r i e s p r o d u c t s w i t h r i c h l o g i c a l r e s o u r c e s,h i g h s p e e d p a r a l l e l c o m p u t i n g a b i l i t y a n d r e c o n f i g u r a b l e a b i l i t y.I t s"F P G A +A RM"a r c h i t e c t u r e i m p r o v e s t h e a c q u i s i t i o n s p e e d a t t h e f r o n t-e n d o f d i g i t a l i m a g e p r o c e s s i n g s y s t e m,f a c i l i t a t e s t h e i m a g e p r o c e s s i n g a t t h e m i d d l e-e n d a n d t h e d i s p l a y a t t h e b a c k-e n d.T h e d e s i g n o f d i g i t a l i m a g e p r o c e s s i n g s y s t e m b a s e d o n Z y n q7000f o r C a m e r a L i n k i m a g e i n p u t a n d a c q u i s i t i o n,C a m e r a L i n k i m a g e t r a n s m i s s i o n a n d s t o r a g e,a n d C a m e r a L i n k i m a g e d i s p l a y,a n d t h e k e y t e c h n o l o g i e s i n-v o l v e d i n e a c h f u n c t i o n a r e i n t r o d u c e d i n d e t a i l.I t h a s b e e n p r o v e d t h a t t h e s y s t e m h a s h i g h r e a l-t i m e p e r f o r m a n c e,s m a l l s i z e a n d s t a b l e p e r f o r m a n c e,a n d h a s r e a l i z e d t h e i m a g e a c q u i s i t i o n a n d t r a n s m i s s i o n o f l a r g e a m o u n t o f d a t a.I t h a s b e e n a p p l i e d i n p r a c t i c a l p r o j e c t a t p r e s e n t. K e y w o r d s:Z y n q7000;F P G A;A RM;i m a g e p r o c e s s i n g s y s t e m0引言近年来数字图像技术在工业生产㊁军事㊁生物医学㊁航空航天和通信等方面受到了极大的重视㊂随着集成电路工艺的高速发展,F P G A可编程逻辑器件在规模日益增大的同时成本也在逐渐下降,其中X i l i n x Z y n q7000系列产品就是一种全可编程片上系统(A l l P r o g r a mm a b l e S y s-t e m o n C h i p),它将A R M C o r t e x A9处理器和F P G A可编程逻辑资源进行集成,具有硬件和软件均可重新编程的特点,软硬件协同工作提高了设计的灵活性㊂数字图像处理的数据量大,对实时性要求严格,因此实时图像处理系统必须具有强大的运算能力,本系统就是基于Z y n q7000系列产品设计,并利用A X I(A d v a n c e d e X t e n s i b l e I n t e r f a c e)总线实现了A R M处理器与F P G A 的数据交换,即通过P S和P L软硬件协同工作㊂1系统结构及工作原理图像源产生的L V D S串行高速图像信号经过C a m e r-a L i n k芯片D S90C R286M T D后,按照C a m e r a L i n k接口协议转换成并行T T L信号,并将T T L信号输入至F P G A 接口㊂F P G A使用Z y n q7000系列的x c7z100f f g9002器件,在P L端进行采集与控制,在此过程中P L端将通过A X I总线将图像数据存储到D D R中,P S端在接收到图像中断信号时开始读取D D R中的图像数据,判断图像帧号是否连续,是否存在丢图现象,并将结果通过串口发送至上位机,同时P S将C a m e r a L i n k图像通过千兆以太网发送至上位机,上位机将图像显示出来㊂因此该数字图像处理系统主要分为三大部分,分别为基于Z y n q7000的44M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第7期w w w .m e s n e t .c o m .c nC a m e r a L i n k 图像输入与采集模块㊁C a m e r a L i n k 图像传输与存储模块㊁C a m e r a L i n k 图像显示㊂数字图像处理系统如图1所示㊂图1 数字图像处理系统图2 系统关键部分实现本系统接收帧频为50H z ㊁图像大小为1280ˑ960的C a m e r a L i n k 图像,针对数据量大㊁对实时性要求高的系统进行了设计与实现㊂2.1 C a m e r a L i n k 图像输入与采集模块C a m e r a L i n k 接口是由国家半导体试验室(N a t i o n a lI n s t r u m e n t s ,N I )于2000年推出的一种为解决视频数据输出和采集之间速度匹配问题的通信接口㊂它有三种传输模式:B a s e 模式㊁M e d i u m 模式和F u l l 模式㊂本系统只需使用一个C a m e r a L i n k 芯片,采用B a s e 模式㊂选用D S 90C R 286M T D C a m e r a L i n k 接口芯片,该芯片接收4对串行L V D S 差分数据信号和1对串行L V D S 差分时钟信号,输出28位数据信号和1位时钟信号,这28位数据包括24位图像数据和4位图像数据同步信号(L V A L ㊁F V A L 和D V A L ㊁S pa r e )㊂C a m e r a L i n k 图像采集就是根据C a m e r a L i n k 接口协议采集图像信息,图2为C a m e r a L i n k 图像输入的时序图㊂当检测到图像帧信号的下降沿(I m g _f v a l _n e g )或者接收完一幅图大小的b u r s t 长度的有效数据(b u r s t _d o w n )之后,开始设置D D R 的地址,并且将F I F O 中的数清除,紧接着根据L V A L ㊁F V A L 和D V A L 信号开始向F I F O 中写入数据(在此过程中加入行保护,确保每行写入固定的有效数据),当检测到图像帧信号的下降沿时,继续向F I F O 中写入16个填充数,写完后状态机重新回到I D L E 状态,等待接收下一幅图㊂在此过程中,第一幅图的接收用I m g _f v a l _n e g 信号触发,其余图用b u r s t _d o w n 信号触发,图3为图像接口时序的状态机图㊂图2 C a m e r a L i n k图像输入时序图图3 图像接口时序的状态机图2.2 C a m e r a L i n k 图像传输与存储模块Z y n q 7000芯片内部,P S 和P L 之间通过G P (通用接口)和H P (高性能接口)等多种A X I 接口进行实时数据交互㊂A X I 协议包含多种协议:A X I ㊁A X I _L i t e 和A X I 4_S t r e a m ㊂其中,A X I 4协议是基于b u r s t 的传输,适用于高性能㊁高带宽的系统设计㊂本系统分别使用了一个A X I _H P 端口和一个A X I _G P 端口完成C a m e r a L i n k 图像的传输㊂A X I _H P 端口通过一个互联矩阵A X I I n t e r c o n n e c t 0连接外设的主从设备,实现大数据量的传输,同时外设可通过A X I I n t e r -c o n n e c t 0访问A X I _H P 接口,进而访问D D R ;A X I _G P 端口通过一个互联矩阵A X I I n t e r c o n n e c t 1连接外设寄存器,传输数据量小的信息㊂图4为系统传输结构框图㊂接收图像时,P L 通过B a s e 模式访问D D R ,D D R 型号为M T 41K 256M 16R E 125,容量为1G B ,本系统使用2片16位D D R 3芯片构成32位的数据宽度㊂接收与采集模块将接收到的C a m e r a L i n k 图像数据写入到D D R 相应敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第7期45图4系统传输结构框图地址中㊂D D R开辟2片地址用于链接数据的乒乓存储,当P S接收到P L中断时,表示一幅图已经接收完成,便在D D R给定的地址中提取图像数据进行分析㊂向D D R中写入图像数据流程图如图5所示㊂当检测到设置地址标志寄存器为 1 时(s e t_b a s e_a d d r==1 b1),开始设置基地址,b u r s t长度计数器清零;当F I F O中的数据大于254个时(f i f o_c o u n t>=9 d254),开始向D D R中写入数据(f i f o_o u t_e n<=1 b1);当写够一个b u r s t长度的数据时(m00_a x i_b r e a d y==1 b1),b u r s t长度计数器加1(b u r s t_c n t <=b u r s t_c n t+1 b1),若s e t_b a s e_a d d r==1 b0,继续判断(m00_a x i_b r e a d y==1 b1),若是则继续加1,若s e t_ b a s e_a d d r==1 b1,则返回继续设置新的基地址,将b u r s t 长度计数器清零㊂2.3C a m e r a L i n k图像显示为了进一步测试接收图像是否正确,本系统设计了C a m e r a L i n k图像显示功能,使得测试结果更加简明直观㊂当P S接收到C a m e r a L i n k图像接收中断信号时,根据约定地址从D D R中取出图像数据,对图像的连续性进行判断,判断图像是否丢帧,通过串口将判断结果发送给上位机㊂同时通过千兆以太网将C a m e r a L i n k图像数据发送给上位机,上位机从串口接收到图像大小参数,从而对图像进行显示㊂3系统测试针对本系统的功能与性能测试,专门设计了一套测试设备,该测试设备对应本系统的C a m e r a L i n k图像输入模块设计了C a m e r a L i n k图像发送模块㊂C a m e r a L i n k图像发送模块模拟C a m e r a L i n k图像源,生成大小为1280ˑ960的黑白渐变图像,每个时钟生成两个像素,每个像素为一个字节,并且用帧号替代最后一个像素,F P G A输出图5向D D R中写入图像数据流程图的图像数据和时钟信号通过线路驱动器D S90C R285M T D X将其转换成串行的L V D S信号输入到F P G A中,经过C a m e r a L i n k图像采集㊁传输与存储模块后,P S端将接收到的图像数据通过网口发送给上位机,上位机根据从串口收到的图像信息将图像显示出来㊂经过2小时的连续测试,C a m e r a L i n k图像发送模块以20m s的帧频持续发送图像,图像均未出现丢帧现象,误码率为0,可证明该系统功能正确㊁性能稳定㊂图6和图7分别为上位机测试界面和C a m e r a L i n k接收图像㊂图6上位机测试界面50M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第7期w w w .m e s n e t .c o m .c n合柑橘的外观形状,采用圆形边界框代替传统矩形边界框,并以此改进了边框回归损失函数,不仅降低了运算量,还提升了柑橘检测精度㊂通过对比实验及嵌入树莓派的验证可知,S l i m Y O L O v 4算法具有内存开销小㊁检测精度高的特点,能够满足柑橘采摘的实际需要㊂未来,还将尝试加入更多的影响因素来完善此算法,并将其应用于柑橘采摘的机器人中㊂参考文献[1]卢军,桑农.变化光照下树上柑橘目标检测与遮挡轮廓恢复技术[J ].农业机械学报,2014,45(4):681,60.[2]岳有军,田博凯,王红君,等.基于改进M a s k R C N N 的复杂环境下苹果检测研究[J ].中国农机化学报,2019,40(10):128134.[3]H E K M ,G K I O X A R I G ,G I R S H I C K R ,e t a l .M a s k R C N N[C ]//P r o c e e d i n gs o f t h e 2017I E E E I n t e r n a t i o n a l C o n f e r e n c e o n C o m p u t e r V i s i o n .P i s c a t a w a y:I E E E ,2017:29802988.[4]B o c h k o v s k i y A ,W a n g C Y ,L i a o H Y M.Y O L O v 4:o pt i m a l s p e e d a n d a c c u r a c y o f o b j e c t d e t e c t i o n [J ].C o m pu t e r V i s i o n a n d P a t t e r n R e c o gn i t i o n ,2020,17(9):198215.[5]HA N K ,WA N G Y ,T I A N Q ,e t a l .G h o s t N e t :M o r e f e a t u r e sf r o m c h e a p o p e r a t i o n s [C ]//P r o c e e d i n gs o f t h e I E E E /C V F C o n f e r e n c e o n C o m p u t e r V i s i o n a n d P a t t e r n R e c o g n i t i o n ,2020:15801589.[6]Z h e n g Z ,W a n g P ,L i u W ,e t a l .D i s t a n c e I o U L o s s :F a s t e r a n d B e t t e r L e a r n i n g f o r B o u n d i n g B o x R e gr e s s i o n [C ]//A A A I C o n f e r e n c e o n A r t i f i c i a l I n t e l l i ge n c e ,2020.[7]S h u L ,L u Q ,H a if a ng Q ,e t a l .P a th a g g r e ga t i o n n e t w o r k f o r i n s t a n c e s e g m e n t a t i o n [C ]//I E E E C o n f e r e n c e o n C o m pu t e r V i s i o n a n d P a t t e r n R e c o g n i t i o n .S a l t L a k e C i t y:I E E E ,2018:87598768.[8]S a n d l e r M ,H o w a r d A ,Z h u M ,e t a l .M o b i l e n e t v 2:I n v e r t e dr e s i d u a l s a n d l i n e a r b o t t l e n e c k s [C ]//I E E E C o n f e r e n c e o nC o m p u t e r V i s i o n a n d P a t t e r n R e c o g n i t i o n .S a l t L a k e C i t y:I E E E ,2018:45104520.[9]L i u G ,N o u a z e J C ,T o u k o P L ,e t a l .Y O L O T o m a t o :A R o -b u s t A l g o r i t h m f o r T o m a t o D e t e c t i o n b a s e d o n Y O L O v 3[J ].S e n s o r s ,2020,20(7).[10]R e d m o n J ,F a r h a d i A.Y O L O v 3:a n i n c r e m e n t a l i m pr o v e -m e n t [C ]//I E E E C o n f e r e n c e o n C o m pu t e r V i s i o n a n d P a t -t e r n R e c o gn i t i o n ,2018:8995.韩进(教授),主要研究方向为嵌入式计算机控制㊁计算机系统结构㊁电子电路;舒媛(硕士研究生),主要研究方向为嵌入式系统技术㊁物联网软件技术㊂通信作者:韩进,s h n k 123@163.c o m㊂(责任编辑:薛士然 收稿日期:2021-02-22)图7 C a m e r a L i n k 接收图像4 结 语本文面向实时高速数字图像的采集和处理,运用模块化设计思想,基于Z y n q 7000数字图像处理系统实现了数字图像高速输入与采集㊁存储与传输和显示功能,并且设计了简易的验证平台㊂经过验证,本系统实时性高㊁体积小㊁性能稳定,可以实现大数据量的图像采集与传输,目前已应用在实际的项目中㊂参考文献[1]刘宏,符意德.基于Z y n q 芯片的图像处理系统平台设计[J ].计算机与现代化,2015(8):4347.[2]王珂.基于Z Y N Q 的高速图像采集处理平台设计与验证[D ].济南:山东大学,2016.[3]黄志超.基于C a m e r a l i n k 标准的D S P +F P G A 数字图像处理系统设计[J ].科技与管理,2012(7):152153.[4]陈炎斌,金钢.基于C a m e r a _L i n k 标准的高速实时数字图像处理系统设计[J ].现代科学仪器,2010(6):6163.[5]刘应盼.基于Z Y N Q 的图像采集处理系统设计与实现[D ].西安:西安电子科技大学,2019.[6]焦再强.基于Z y n q 7000的嵌入式数字图像处理系统设计与实现[D ].太原:太原理工大学,2012.[7]高媛,商远波.一种基于C a m e r a L i n k 的数字图像处理系统[J ].制导与引信,2017(38):2932.[8]杨晓安,罗杰,苏豪,等.基于Z y n q 7000高速图像采集与实时处理系统[J ].电子科技,2014(7):151154.[9]郭钊.嵌入式图像并行处理系统的研究与应用[D ].兰州:兰州理工大学,2014.通信作者:王咏星,78233164@q q.c o m ㊂(责任编辑:薛士然 收稿日期:2021-01-26)。

浅谈XilinxZYNQ-7000平台的应用【文尾有福利】

浅谈XilinxZYNQ-7000平台的应⽤【⽂尾有福利】Xilinx Zynq-7000 全可编程 SoC (AP SoC) 系列集成 ARM处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上⾼度集成 CPU、DSP、ASSP 以及混合信号功能。

Zynq-7000 器件配备双核ARM Cortex-A9 处理器,该处理器与基于28nm Artix-7 或 Kintex-7 的可编程逻辑集成,可实现优异的性能功耗⽐和最⼤的设计灵活性。

这种集成在⼀起的CPU与FPGA之间的通讯总线,通讯速度更快,信息传递结构更简单。

简单来说,就是Xilinx的这款芯⽚既能节省成本⼜能提⾼性能,还有这种好事?还真有,下⾯我来举个例⼦。

⿍阳(SIGLENT)SDS1000X-E系列以及电商专供SDS1000X-C系列超级荧光⽰波器2/4通道,最⾼带宽200MHz图1 SDS1000X-E(X-C)中集成了Zynq-7000SDS1000X-E(X-C)中采⽤的XC7Z020 SoC芯⽚,具有双核ARM Cortex-A9处理器(PS)+基于Artix-7架构的FPGA(PL),其中处理器部分⽀持的最⾼主频为866MHz,FPGA部分则包含85k逻辑单元、4.9Mb Block RAM和220个DSP Slice,并提供对常⽤外部存储器如DDR2/DDR3的⽀持,⾮常契合数字⽰波器中对数据进⾏采集、存储和数字信号处理的需求。

同时,Zynq-7000的PS(处理器系统)和PL(可编程逻辑)部分之间通过AXI⾼速总线互连,可以有效解决传统数字存储⽰波器中CPU与FPGA间数据传输的带宽瓶颈问题,有利于降低数字⽰波器的死区时间,提⾼波形捕获率。

⽤单⽚SoC芯⽚替代传统的CPU+FPGA的分⽴⽅案,也可以减少硬件布板⾯积,有利于将⾼性能处理系统向紧凑型的⼊门级⽰波器中集成。

数据采集与存储图2 ⽤Zynq-7000构架的SPO引擎SDS1000X-E(X-C)中采⽤的⾼速模-数转换(ADC)芯⽚,其数据接⼝为LVDS差分对形式,每对LVDS的速率为1Gbps。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

UART1映射到MIO[48:49] zedboardBank 0 IO Voltage:LVCMOS 3.3V zedboardBank 1 IO Voltage:LVCMOS 1.8V zedboardPS与PL电源部分是完全独立,但是无论什么时候有PL电源供电就必须有PS电源供电。

PS电源部分为DDR IO口独立供电,还为MIO的两个独立的分区Bank0与Bank1供电。

PS专用的信号pin汇总表2-2,注意,对于MIO pin允许的输入电压取决于slcr, MIO_PIN_xx[IO_Type]和[DisableRcvr] bits,约束条件被定义在Zynq-7000 AP SoC data sheets,超出限制的电压输入可能损坏输入buffer。

(2)核对IO配置,选择Zynq Block Design,注意UART1是否已经在IO特性中被连接。

注意勾上:GPIO,以使其它的MIO口能够作处理器的GPIO使用。

(3)General Setting常规设置:设置端口特性在Zynq Block Design中选择General Setting或在PS-PL Configuration中设置。

设置UART1 波特率。

(4)配置Memory和Clocks即使一个简单的Hello World程序被运行,一些不可缺少的PS elements也必须被配置,它包括DDR3 Memory(用来执行PS应用程序),另外系统时钟也必须被配置。

DDR3为zed board开发板上的IC25与IC26,MT41K128M16JT_125.Clock Configuration: 默认时钟频率与ZedBoard和MicroZed匹配:IO Peripheral CLocks被指定(SPI、QSPI、CAN、SMC、SDIO、ENET),选择后如何更改,例如SPI?如果不用FCLK_CLK0,可废除PL Fabric Clock,同时还需废除AXI connection to the PL,在PS-PL Configuration中的取消对GP Master AXI Tnterface的选择。

也可在PS-PL Configuration中取消对FCLK_RESET的选择。

SPI:时钟要求比cpu_1x频率111.1111Mhz更大,可设160Mhz,然后4分频为10Mhz使能DDR Configuration:必须设置为PCB使用的DDR设置。

因为使用2x16 DDR3配置,所以在DDR Controller Configuration中设置游戏的DRAM总线宽度为32bits。

DRAM Training必须全被使能和设置:write level,read gate,read data eye。

保存后完成最小系统设置:其中内部设置的UART1引脚内部设置,未显示出来,其实包含在了FIXED_IO。

展开FIXED_IO可查看被固定的IO口包含了哪些IO口:包含了含有串口UART1的MIO 口、处理器的时钟口......。

(5)完成IP 集成文件(bd文件)完成处理器配置后,为了便于bd文件作为工程的子模块,可以将bd文件例化为HDL文件。

展开design Sources,右键点击bd文件创建HDL wrapper。

再把HDL文件设为顶层文件或例化在其它工程中。

5.输出设计到SDK(software development kit)5.1 输出到SDK前先完成硬件设计在FLow Navigator中点击Generate Bitstream,如没有综合和实现,软件将自动综合布线后产生二进制文件。

Bitstream产生完成后,选择Open Implemented Design才能使能Vivado输出bitstream到SDK。

输出到SDK:File —>Export —>Export Hardware for SDK…5.2 输出到SDK后产生的文件产生文件夹hw_platform_0产生文件:System.xml,包含系统的地址映射ps7_init.c和ps7_init.h,包含ZYNQ processing system初始化代码和DDR,Clocks,PLL,MIO的初始化设置。

p s7_init.html,将初始化等设置以网页的格式显示出来。

?_wrapper.bit,implemented设计时,PL bitstream产生的二进制文件,用于初始化PL。

5.3 SDK中创建硬件级支持包(Board Support Package)常规默认设置即可点击完成后弹出支持包设置设置标准输入输出设备:stdin、stdout自动设置为uart_1,添加其他外设时可以更改。

设置驱动包:自动列出驱动,不需要的驱动选择‘none’5.4 新建Application Project,使用existing的Board Support Package5.5 一个软件工程包含了3个部分:硬件信息、驱动包、软件包5.6 运行调试程序右键点击Hello应用程序run as--->run configurations(1)选择Xilinx C/C++ Application(GDB)然后点击New图标。

(2)选择STDIO连接,连接到Console。

如不选择,则直接输出到串口上。

(3)编译完成,生成二进制elf文件。

点击Apply和Run,工具编译好下载elf文件到DDR。

JTAG模式:设置MIO2~6为000005.7 上电启动配置利用FSBL模板建立FSBL的boot程序(1)建立boot启动程序: 新建应用工程Application Project,选择FSBL模板。

应用要求xilffs library库支持,如未在建立Board Support Package 时选择该库,可右键点击standalone_bsp_0选择Board Support Package设置。

建立完成即可,默认设置。

输出在fsbl程序的Properties>C/C++ Build>Settings>ARM gcc compiler>添加两个符号:RSA_SUPPORT和FSBL_DEBUG_INFO(用于打开FSBL的输出,可选)>apply>ok。

(2)使用Xilinx Tools/Create Zynq Boot Image命令建立镜像文件。

首先在FSBL elf的Browse中选择Boot.elf,该文件会自动添加到下边的文件列表中。

然后添加Bitstream,在hw下;再添加LED_Dimmer.elf文件。

三者的顺序不能颠倒。

最后Create。

(需要先编译工程Project—>build all)。

在boot image partitions中添加bootloader类型的FSBL生成的.elf文件;添加hw_platform中的硬件.bit二进制文件; 添加软件工程生成的.elf文件;(3)使用xilinx-tool/Program Flash.选择qspi single,offset可以不填写内容。

Program.(4) 下载文件:QSPI—Flash对应.MSC文件,SD card对应.bin文件6 其它操作Zedboard Processing System配置:最重要的外设配置是boot device,ZYNQ允许使用QSPI、NOR/NAND、SD Card。

QSPI:QSPI固定使用MIO[1-6,8], 其中MIO8为feedback clk, 通常应勾选上。

如果有灵感QSPI,选择Dual配置。

注意:SRAM/NOR/NAND Flash接口不能被配置,是因为ZYNQ PS仅仅允许一个存储器接口。

USB0:MIO28-39,LVCMOS1.8V以太网ENET0:MIO[16-27], LVCMOS 1.8V MDIO——MIO[52-53]SDCARD: SD0——MIO[40-45]; CD=MIO47; WP=MIO46预设为Zedboard默认值:Presets—>Zedboard设置PS PLL CLocks:有三个PLL-ARM,DDR和IO,每一个在Zedboard上都使用同样的输入参考时钟33.3333MHz。

PLL输出设定好后可以更改为整数倍的其它时钟。

例如:ARM PLL——1333.33MHz(33.333MHz*40)DDR PLL——1600MHz(33.333Mhz*48)或1066.667MHz(33.3333*32)QSPI可设置为200MHzPS能够驱动4个不同时钟频率给PL例如:7 绑定PL管脚管脚约束PS部分使用的I/O直接由软件配置,综合后可在I/O Planning中直接查看。